SANYO LC322271T-80, LC322271T-70, LC322271M-80, LC322271M-70, LC322271J-80 Datasheet

...

Ordering number : EN*5085A

CMOS LSI

LC322271J, M, T-70/80

2 MEG (131072 words × 16 bits) DRAM

Fast Page Mode, Byte Write

Preliminary

Overview

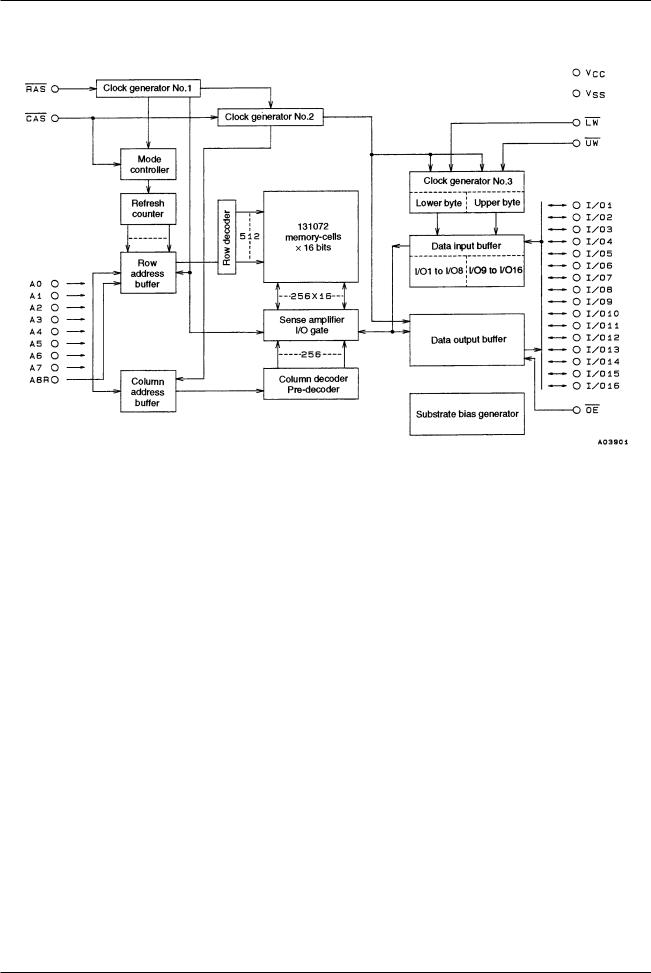

The LC322271J, M and T is a CMOS dynamic RAM operating on a single 5 V power source and having a 131072 words × 16 bits configuration. Equipped with large capacity capabilities, high speed transfer rates and low power dissipation, this series is suited for a wide variety of applications ranging from computer main memory and expansion memory to commercial equipment.

Address input utilizes a multiplexed address bus which permits it to be enclosed in a compact plastic package of SOJ 40-pin, SOP 40-pin, and TSOP 44-pin . Refresh rates are within 8 ms with 512 row address (A0 to A7, A8R) selection and support Row Address Strobe (RAS)-only refresh, Column Address Strobe (CAS)-before-RAS refresh and hidden refresh settings. There are functions such as fast page mode, read-modify-write and byte write. The pin assignment follows the JEDEC 1 M DRAM (65536 words × 16 bits, 1CAS/2WE) standard.

Features

•131072 words × 16 bits configuration.

•Single 5 V ± 10% power supply.

•All input and output (I/O) TTL compatible.

•Supports fast page mode, read-modify-write and byte write.

•Supports output buffer control using early write and Output Enable (OE) control.

•8 ms refresh using 512 refresh cycles.

•Supports RAS-only refresh, CAS-before-RAS refresh and hidden refresh.

•Follows the JEDEC 1 M DRAM (65536 words × 16 bits, 1CAS/2WE) standard.

•RAS access time/column address time/CAS access time/cycle time/power dissipation

• Package: |

|

SOJ 40-pin |

(400 mil) plastic package : LC322271J |

SOP 40-pin |

(450 mil) plastic package: LC322271M |

TSOP 44-pin (400 mil) plastic package : LC322271T

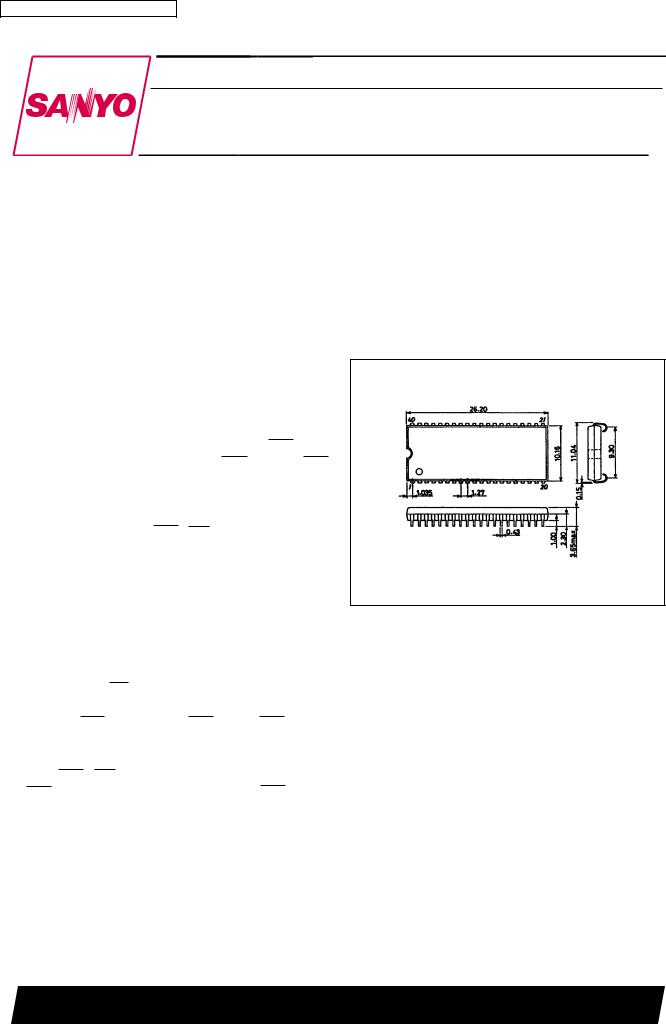

Package Dimensions

unit: mm

3200-SOJ40

[LC322271J]

SANYO: SOJ40

|

|

|

Parameter |

|

LC322271J, M, T |

|||

|

|

|

|

|

|

|||

|

|

|

|

|

-70 |

|

-80 |

|

|

|

|

|

|

|

|

||

|

|

|

access time |

70 ns |

|

80 ns |

||

RAS |

|

|||||||

|

|

|

|

|

|

|

||

Column address access time |

35 ns |

|

45 ns |

|||||

|

|

|

|

|

|

|

||

|

20 ns |

|

30 ns |

|||||

|

CAS |

access time |

|

|||||

|

|

|

|

|

|

|

||

Cycle time |

130 ns |

|

150 ns |

|||||

|

|

|

|

|

|

|

|

|

Power dissipation (max.) |

During operation |

688 mW |

|

633 mW |

||||

|

|

|

|

|||||

During standby |

5.5 mW (CMOS level)/11 mW (TTL level) |

|||||||

|

|

|

|

|||||

SANYO Electric Co.,Ltd. Semiconductor Bussiness Headquarters

TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110-0005 JAPAN

32896HA (OT)/33195TH (OT) No. 5085-1/29

LC322271J, M, T-70/80

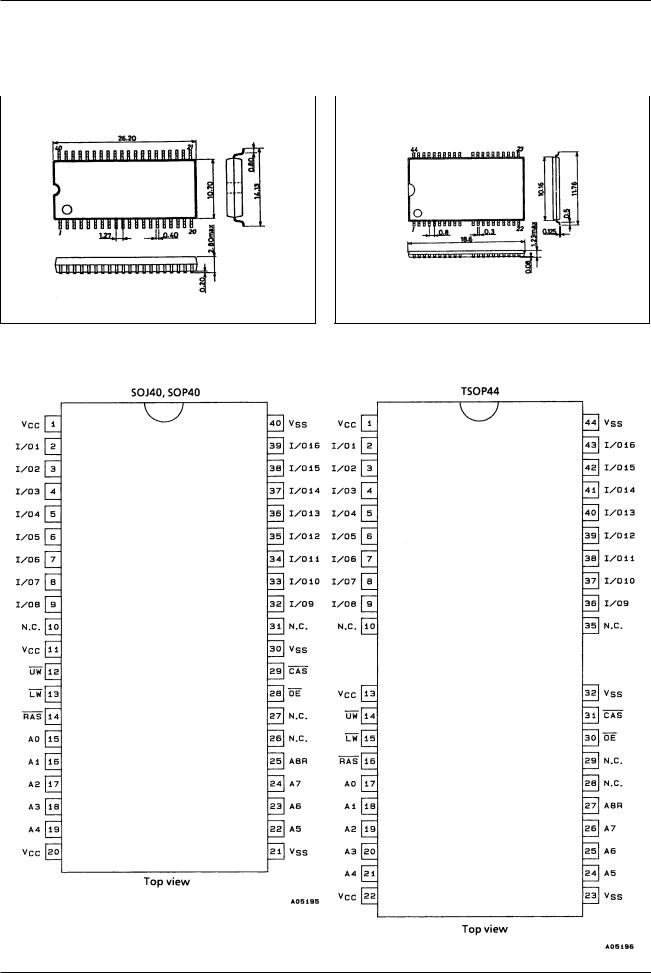

Package Dimensions

unit: mm |

unit: mm |

|||||

3195-SOP40 |

3207-TSOP44 |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

[LC322271M] |

[LC322271T] |

||||

|

|

|

|

|

|

|

SANYO: SOP40 |

SANYO: TSOP44 (TYPE II) |

Pin Assignments

No. 5085-2/29

LC322271J, M, T-70/80

Block Diagram

Specifications

Absolute Maximum Ratings

Parameter |

Symbol |

Ratings |

Unit |

Note |

||

|

|

|

|

|

|

|

Maximum supply voltage |

VCC max |

–1.0 to +7.0 |

V |

1 |

||

Input voltage |

VIN |

–1.0 to +7.0 |

V |

1 |

||

Output voltage |

VOUT |

–1.0 to +7.0 |

V |

1 |

||

Allowable power dissipation |

LC322271J, M |

Pd max |

800 |

mW |

1 |

|

|

|

|||||

LC322271T |

700 |

|||||

|

|

|

|

|||

|

|

|

|

|

|

|

Output short-circuit current |

IOUT |

50 |

mA |

1 |

||

Operating temperature range |

Topr |

0 to +70 |

°C |

1 |

||

|

|

|

|

|

||

Storage temperature range |

Tstg |

–55 to +150 |

°C |

1 |

||

|

|

|

|

|

|

|

Note: 1. Stresses greater than the above listed maximum values may result in damage to the device.

No. 5085-3/29

LC322271J, M, T-70/80

DC Recommended Operating Ranges at Ta = 0 to +70°C

|

|

Parameter |

Symbol |

min |

typ |

max |

Unit |

Note |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Power supply voltage |

VCC |

4.5 |

5.0 |

5.5 |

V |

2 |

|||||||

Input high level voltage |

VIH |

2.4 |

|

6.5 |

V |

2 |

|||||||

Input low level voltage |

VIL |

–1.0* |

|

+0.8 |

V |

2 |

|||||||

|

|

|

|

|

|

|

|

|

|||||

(A0 to A7, A8R, |

RAS, |

CAS, UW, |

LW, |

OE) |

|

||||||||

Input low level voltage (I/O1 to I/O16) |

VIL |

–0.5* |

|

+0.8 |

V |

2 |

|||||||

Note: 2. All voltages are referenced to VSS.

*: –2.0 V when pulse width is less than 20 ns.

DC Electrical Characteristics at Ta = 0 to +70°C, VCC = 5 V ± 10%

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LC322271J, M, T |

|

|

|

||

|

|

|

|

|

Parameter |

Symbol |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Conditions |

|

-70 |

-80 |

|

Unit |

Note |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

min |

|

max |

min |

|

max |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Operating current |

ICC1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

RAS, CAS, address cycling: tRC = tRC min |

|

|

125 |

|

|

115 |

mA |

3, 4, 5 |

|||||||||||||||||||||||

(Average current during operation) |

|

|

|

|

|

|||||||||||||||||||||||||||

Standby current |

ICC2 |

|

|

|

|

|

|

|

|

= VIH |

|

|

2 |

|

|

2 |

mA |

|

||||||||||||||

|

RAS |

= |

|

CAS |

|

|

|

|

|

|

||||||||||||||||||||||

|

|

|

-only refresh current |

ICC3 |

|

|

cycling, |

|

|

= VIH: tRC = tRC min |

|

|

125 |

|

|

115 |

mA |

3, 5 |

||||||||||||||

|

RAS |

|

RAS |

|

CAS |

|

|

|

|

|||||||||||||||||||||||

Fast page mode current |

ICC4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

RAS |

|

= VIL, |

CAS, |

address cycling: tPC = tPC min |

|

|

115 |

|

|

90 |

mA |

3, 4, 5 |

|||||||||||||||||||

Standby current |

ICC5 |

|

|

|

= |

|

|

= VCC – 0.2 V |

|

|

1 |

|

|

1 |

mA |

|

||||||||||||||||

|

RAS |

CAS |

|

|

|

|

|

|||||||||||||||||||||||||

|

|

-before- |

|

refresh current |

ICC6 |

|

|

|

|

|

cycling: tRC = tRC min |

|

|

125 |

|

|

115 |

mA |

3 |

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||

|

CAS |

RAS |

|

RAS, |

CAS |

|

|

|

|

|||||||||||||||||||||||

Input leakage current |

IIL |

|

0 V ≤ VIN ≤ 6.5 V, pins other than test pin = 0 V |

–10 |

|

+10 |

–10 |

|

+10 |

µA |

|

|||||||||||||||||||||

Output leakage current |

IOL |

|

DOUT disable, 0 V ≤ VOUT ≤ 5.5 V |

–10 |

|

+10 |

–10 |

|

+10 |

µA |

|

|||||||||||||||||||||

Output high level voltage |

VOH |

|

IOUT = –2.5 mA |

2.4 |

|

|

2.4 |

|

|

V |

|

|||||||||||||||||||||

Output low level voltage |

VOL |

|

IOUT = 2.1 mA |

|

|

0.4 |

|

|

0.4 |

V |

|

|||||||||||||||||||||

Note: 3. All current values are measured at minimum cycle rate. Since current flows immoderately, if cycle time is longer than shown here, current value becomes smaller.

4.ICC1 and ICC4 are dependent on output loads. Maximum values for ICC1 and ICC4 represent values with output open.

5.Address change is less than or equal to one time during RAS = VIL. Concerning ICC4, it is less than or equal to one time during 1 cycle (tPC).

AC Electrical Characteristics at Ta = 0 to +70°C, VCC = 5 V ± 10% (Notes 6, 7 and 8)

|

|

|

|

|

|

|

|

|

Parameter |

Symbol |

|

-70 |

|

-80 |

Unit |

Note |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

min |

|

max |

min |

|

max |

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Random read, write cycle time |

tRC |

130 |

|

|

150 |

|

|

ns |

|

||||||||||

|

Read-write/read-modify-write cycle time |

tRWC |

190 |

|

|

200 |

|

|

ns |

|

||||||||||

|

Fast page mode cycle time |

tPC |

45 |

|

|

55 |

|

|

ns |

|

||||||||||

|

Fast page mode read-write/read-modify-write cycle time |

tPRWC |

95 |

|

|

100 |

|

|

ns |

|

||||||||||

|

|

|

|

|

|

|

|

|

|

tRAC |

|

|

70 |

|

|

80 |

ns |

9, 14, 15 |

||

|

|

|

|

RAS |

access time |

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

CAS access time |

tCAC |

|

|

20 |

|

|

30 |

ns |

9, 14 |

||||||||||

|

Column address access time |

tAA |

|

|

35 |

|

|

45 |

ns |

9, 15 |

||||||||||

|

|

|

|

|

|

|

tCPA |

|

|

40 |

|

|

50 |

ns |

9 |

|||||

|

|

|

CAS |

precharge access time |

|

|

|

|

||||||||||||

|

Output low-impedance time from |

|

low |

tCLZ |

0 |

|

|

0 |

|

|

ns |

9 |

||||||||

CAS |

|

|

|

|

||||||||||||||||

|

Output buffer turn-off delay time |

tOFF |

0 |

|

20 |

0 |

|

20 |

ns |

10 |

||||||||||

|

Rise, fall time |

tT |

3 |

|

50 |

3 |

|

50 |

ns |

|

||||||||||

|

|

|

|

precharge time |

tRP |

50 |

|

|

60 |

|

|

ns |

|

|||||||

RAS |

|

|

|

|

|

|||||||||||||||

|

|

|

tRAS |

70 |

|

10000 |

80 |

|

10000 |

ns |

|

|||||||||

|

|

RAS |

pulse width |

|

|

|

||||||||||||||

|

|

pulse width for fast page mode cycle only |

tRASP |

70 |

|

100000 |

80 |

|

100000 |

ns |

|

|||||||||

|

RAS |

|

|

|

||||||||||||||||

Continued on next page.

No. 5085-4/29

LC322271J, M, T-70/80

Continued from preceding page.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Parameter |

|

|

-70 |

|

-80 |

Unit |

Note |

||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||

Symbol |

min |

|

max |

min |

|

max |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

hold time |

tRSH |

20 |

|

|

30 |

|

|

ns |

|

||||||||||||||||||||||||||||||||||||||||||||||||||||

RAS |

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

hold time |

tCSH |

70 |

|

|

80 |

|

|

ns |

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

CAS |

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

pulse width |

tCAS |

20 |

|

10000 |

30 |

|

10000 |

ns |

|

||||||||||||||||||||||||||||||||||||||||||||||||||||

CAS |

|

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

to |

|

|

|

|

|

|

delay time |

tRCD |

25 |

|

50 |

25 |

|

50 |

ns |

14 |

|||||||||||||||||||||||||||||||||||||||||||||||

|

RAS |

CAS |

|

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

to column address delay time |

tRAD |

17 |

|

35 |

17 |

|

35 |

ns |

15 |

||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

RAS |

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

to |

|

|

|

|

|

|

precharge time |

tCRP |

10 |

|

|

10 |

|

|

ns |

|

||||||||||||||||||||||||||||||||||||||||||||||

|

|

CAS |

RAS |

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

precharge time |

tCP |

10 |

|

|

10 |

|

|

ns |

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

CAS |

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Row address setup time |

tASR |

0 |

|

|

0 |

|

|

ns |

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Row address hold time |

tRAH |

12 |

|

|

12 |

|

|

ns |

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Column address setup time |

tASC |

0 |

|

|

0 |

|

|

ns |

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Column address hold time |

tCAH |

15 |

|

|

20 |

|

|

ns |

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

Column address hold time referenced to |

RAS |

|

tAR |

50 |

|

|

60 |

|

|

ns |

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Column address to |

|

|

|

|

|

|

|

|

|

lead time |

tRAL |

40 |

|

|

45 |

|

|

ns |

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||

|

RAS |

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Read command setup time |

tRCS |

0 |

|

|

0 |

|

|

ns |

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

Read command hold time referenced to |

CAS |

|

tRCH |

0 |

|

|

0 |

|

|

ns |

11 |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Read command hold time referenced to |

|

|

|

|

tRRH |

0 |

|

|

0 |

|

|

ns |

11 |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

RAS |

|

|

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Write command hold time |

tWCH |

15 |

|

|

15 |

|

|

ns |

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Write command hold time referenced to |

|

|

|

|

tWCR |

50 |

|

|

60 |

|

|

ns |

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

RAS |

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Write command pulse width |

tWP |

15 |

|

|

15 |

|

|

ns |

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

Write command to |

RAS |

|

|

|

|

lead time |

tRWL |

25 |

|

|

25 |

|

|

ns |

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Write command to |

|

|

|

|

|

|

|

|

|

lead time |

tCWL |

20 |

|

|

20 |

|

|

ns |

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||

|

CAS |

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Data input setup time |

tDS |

0 |

|

|

0 |

|

|

ns |

12 |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Data input hold time |

tDH |

15 |

|

|

20 |

|

|

ns |

12 |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

Data input hold time referenced to |

RAS |

|

|

|

tDHR |

50 |

|

|

60 |

|

|

ns |

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Refresh time |

tREF |

|

|

8 |

|

|

8 |

ms |

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Write command setup time |

tWCS |

0 |

|

|

0 |

|

|

ns |

13 |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

to |

|

|

|

|

|

|

|

|

|

|

delay time |

tCWD |

50 |

|

|

50 |

|

|

ns |

13 |

|||||||||||||||||||||||||||||||||||||||||||||

|

CAS |

|

|

UW, |

|

|

LW |

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

to |

|

|

|

|

|

|

|

delay time |

tRWD |

100 |

|

|

100 |

|

|

ns |

13 |

||||||||||||||||||||||||||||||||||||||||||||||||

|

RAS |

UW, |

LW |

|

|

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||

|

Column address to |

|

UW, |

|

LW |

delay time |

tAWD |

65 |

|

|

65 |

|

|

ns |

13 |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||

|

CAS |

precharge UW, |

|

LW |

delay time for fast page mode |

tCPWD |

70 |

|

|

70 |

|

|

ns |

13 |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

cycle only |

|

|

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tCSR |

10 |

|

|

10 |

|

|

ns |

|

|||||||||||||||||||||||||||||||||||

|

CAS setup time for CAS-before-RAS |

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tCHR |

15 |

|

|

15 |

|

|

ns |

|

|||||||||||||||||||||||||||||||||||||

|

CAS hold time for CAS-before-RAS |

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||||||

|

RAS |

|

precharge |

CAS |

active time |

tRPC |

10 |

|

|

10 |

|

|

ns |

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

precharge time for |

|

|

|

|

|

|

|

|

tCPT |

40 |

|

|

40 |

|

|

ns |

|

|||||||||||||||||||||||||||||||||||||||||||||||||||

|

CAS |

CAS-before-RAS counter test |

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

hold time referenced to |

|

|

|

|

tROH |

15 |

|

|

15 |

|

|

ns |

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

RAS |

OE |

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

tOEA |

|

|

20 |

|

|

25 |

ns |

9 |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

OE |

access time |

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

delay time |

tOED |

15 |

|

|

15 |

|

|

ns |

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

OE |

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

tOEZ |

0 |

|

|

0 |

|

15 |

ns |

10 |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

OE |

output buffer turn-off delay time |

|

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

tOEH |

20 |

|

|

20 |

|

|

ns |

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

OE |

command hold time |

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Data input to |

|

|

|

delay time |

tDZC |

0 |

|

|

0 |

|

|

ns |

16 |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

CAS |

|

|

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Data input to |

OE |

delay time |

tDZO |

0 |

|

|

0 |

|

|

ns |

16 |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Masked write setup time |

tMCS |

0 |

|

|

0 |

|

|

ns |

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Masked write hold time referenced to |

RAS |

|

tMRH |

0 |

|

|

0 |

|

|

ns |

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Masked write hold time referenced to |

CAS |

|

tMCH |

0 |

|

|

0 |

|

|

ns |

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

No. 5085-5/29

LC322271J, M, T-70/80

Input/Output Capacitance at Ta = 25°C, f = 1 MHz, VCC = 5 V ± 10%

Parameter |

Symbol |

min |

max |

Unit |

Note |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Input capacitance (A0 to A7, A8R, |

|

|

|

|

|

|

|

|

|

|

CIN |

|

7 |

pF |

|

RAS, |

|

CAS, |

|

UW, |

|

LW, |

OE) |

|

|

||||||

Input/Output capacitance (I/O1 to I/O16) |

CI/O |

|

7 |

pF |

|

||||||||||

Note: 6. An initial pause of 200 µs is required after power-up followed by eight RAS-only refresh cycles before proper device operation is achieved. In case of using refresh counter, a minimum of eight CAS-before-RAS refresh cycles instead of eight RAS-only refresh cycles are required.

7.Measured at tT = 5 ns.

8.When measuring input signal timing, VIH (min) and VIL (max) are used for reference points. In addition, rise and fall time are defined between VIH and VIL.

9.Measured using an equivalent of 50 pF and one standard TTL loads.

10.tOFF (max) and tOEZ (max) are defined as the time until output voltage can no longer be measured when output switches to a high impedance condition.

11.Operation is guaranteed if either tRRH or tRCH is satisfied.

12.These parameters are measured from the falling edge of CAS for an early-write cycle, and from the falling edge of UW and LW for a read- write/read-modify-write cycle.

13.tWCS, tCWD, tRWD, tAWD and tCPWD are not restrictive operating parameters for memory in that they specify the operating mode. If tWCS ≥ tWCS (min), the cycle switches to an early-write cycle and output pins switch to high impedance throughout the cycle.

If tCWD ≥ tCWD (min), tRWD ≥ tRWD (min), tAWD ≥ tAWD (min) and tCPWD ≥ tCPWD (min) for fast page mode cycle only, the cycle switches to a read-write/read-modify-write cycle and data output equal information in the selected cells. If neither of the above timings are satisfied, output pins

are in an undefined state.

14.tRCD (max) is not a restrictive operating parameter but instead represents the point at which the access time tRAC (max) is guaranteed. If tRCD ≥ tRCD (max), access time is determined according to tCAC.

15.tRAD (max) is not a restrictive operating parameter but instead represents the point at which the access time tRAC (max) is guaranteed. If tRAD ≥ tRAD (max), access time is determined according to tAA.

16.Operation is guaranteed if either tDZC or tDZO i s satisfied.

No. 5085-6/29

LC322271J, M, T-70/80

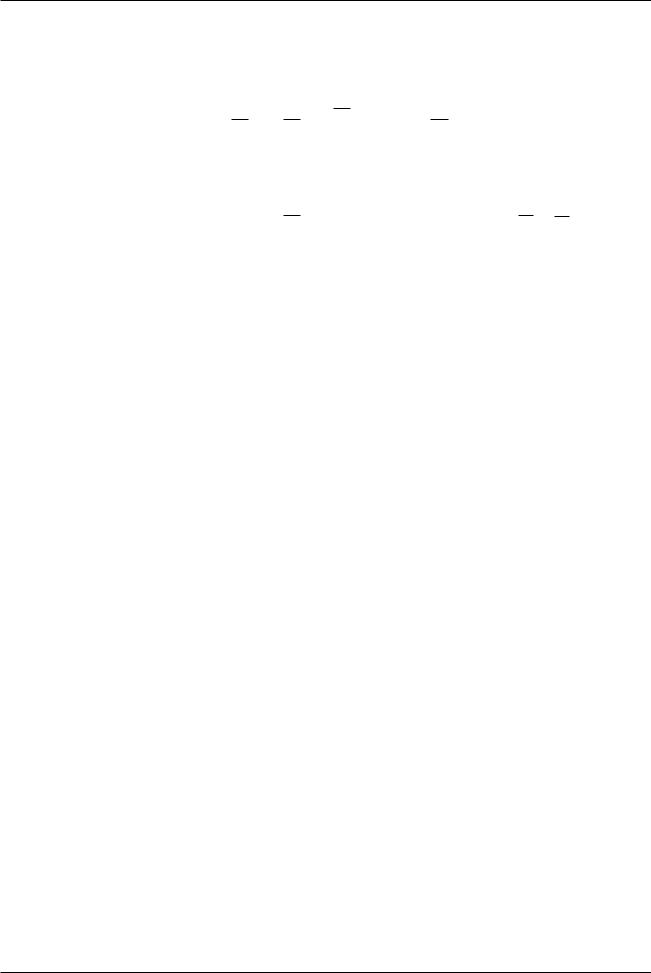

Timing Chart

Read Cycle

No. 5085-7/29

LC322271J, M, T-70/80

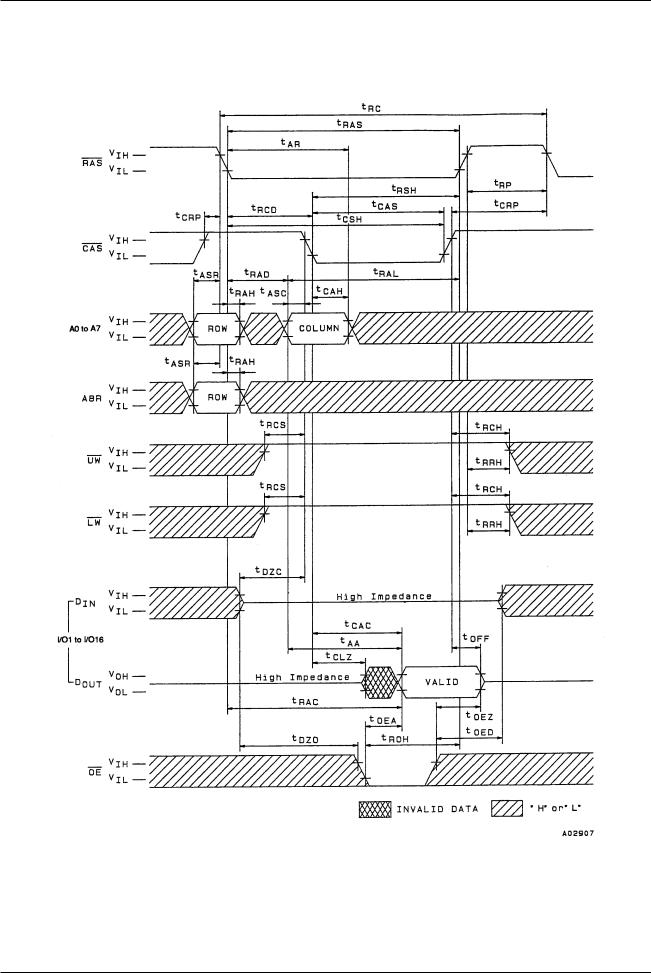

Early Write Cycle

No. 5085-8/29

LC322271J, M, T-70/80

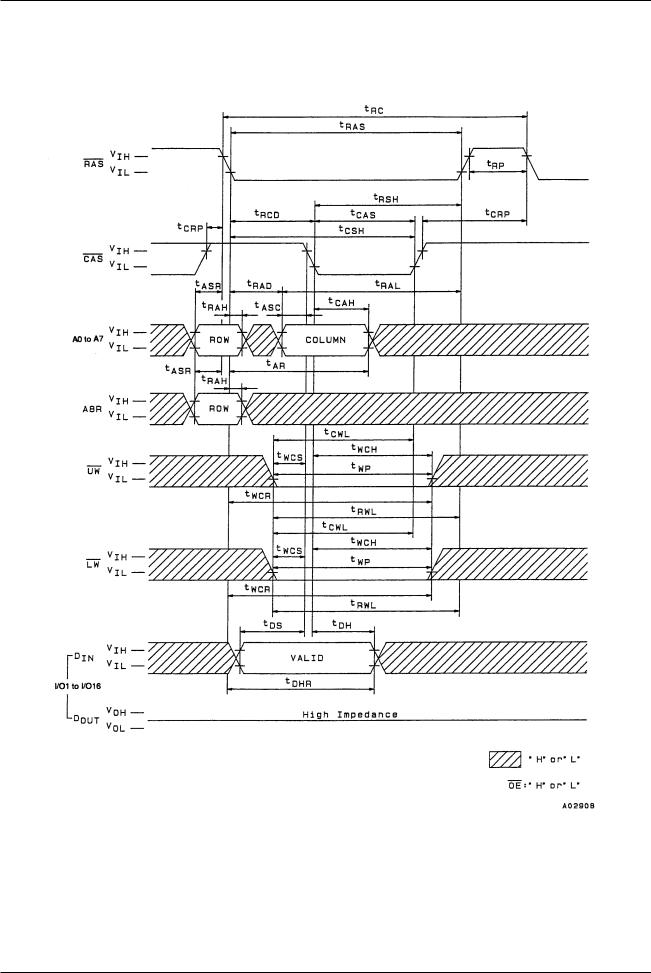

Upper Byte Early Write Cycle

No. 5085-9/29

Loading...

Loading...