Motorola SG3527AN, SG3525ADW, SG3525AN Datasheet

Order this document by SG3525A/D

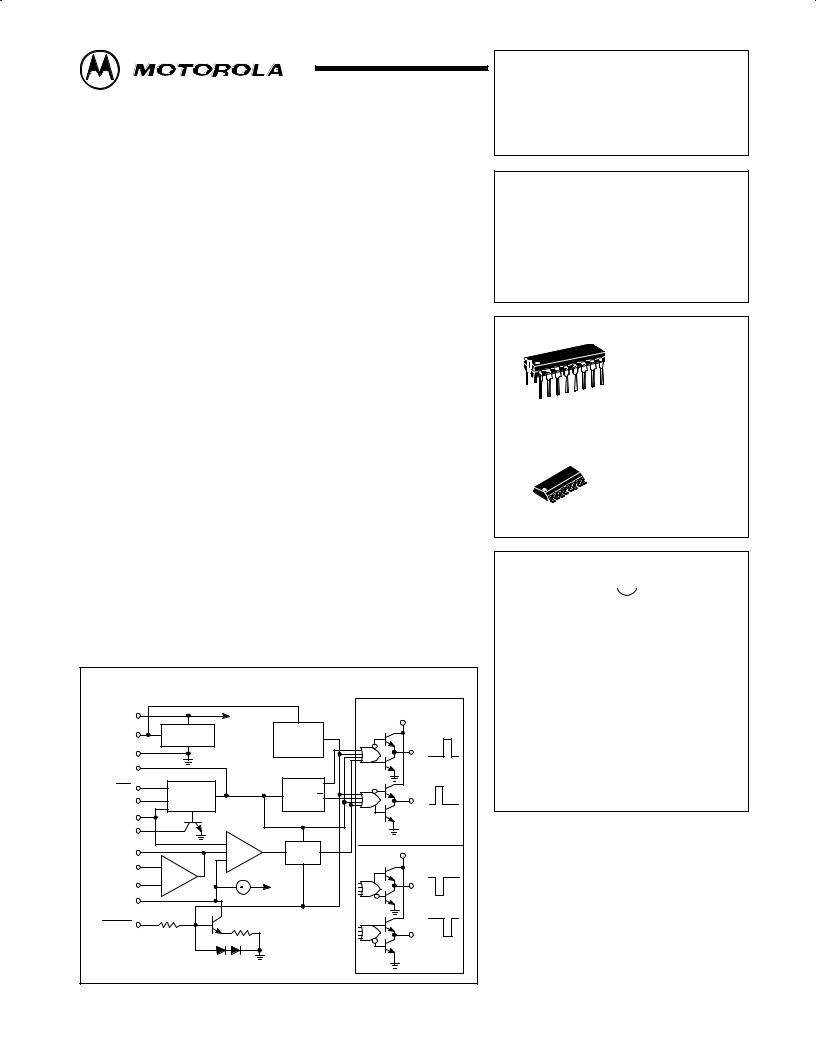

Pulse Width

Modulator Control Circuits

The SG3525A, SG3527A pulse width modulator control circuits offer improved performance and lower external parts count when implemented for controlling all types of switching power supplies. The on±chip +5.1 V reference is trimmed to ±1% and the error amplifier has an input common±mode voltage range that includes the reference voltage, thus eliminating the need for external divider resistors. A sync input to the oscillator enables multiple units to be slaved or a single unit to be synchronized to an external system clock. A wide range of deadtime can be programmed by a single resistor connected between the CT and Discharge pins. These devices also feature built±in soft±start circuitry, requiring only an external timing capacitor. A shutdown pin controls both the soft±start circuitry and the output stages, providing instantaneous turn off through the PWM latch with pulsed shutdown, as well as soft±start recycle with longer shutdown commands. The under voltage lockout inhibits the outputs and the changing of the soft±start capacitor when VCC is below nominal. The output stages are totem±pole design capable of sinking and sourcing in excess of 200 mA. The output stage of the SG3525A features NOR logic resulting in a low output for an off±state while the SG3527A utilized OR logic which gives a high output when off.

•8.0 V to 35 V Operation

•5.1 V ± 1.0% Trimmed Reference

•100 Hz to 400 kHz Oscillator Range

•Separate Oscillator Sync Pin

•Adjustable Deadtime Control

•Input Undervoltage Lockout

•Latching PWM to Prevent Multiple Pulses

•Pulse±by±Pulse Shutdown

•Dual Source/Sink Outputs: ±400 mA Peak

|

|

Representative Block Diagram |

|

||||

Vref |

16 |

|

|

|

|

|

VC |

15 |

|

To Internal |

|

|

|

13 |

|

VCC |

Reference |

Circuitry |

Under± |

|

|

|

|

|

|

|

|

Output A |

|||

12 |

Regulator |

|

Voltage |

|

|

||

Ground |

|

|

Lockout |

|

NOR |

11 |

|

|

|

|

|

|

|||

4 |

|

|

|

|

|

||

OSC Output |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Sync |

3 |

|

|

|

Q |

|

|

6 |

|

|

F/F |

|

|

||

Oscillator |

|

|

|

|

|||

RT |

|

Q |

NOR |

14 |

|||

|

|

|

|||||

5 |

|

|

|

||||

CT |

|

|

|

|

|

Output B |

|

|

|

|

|

|

|

||

7 |

|

|

|

|

|

|

|

Discharge |

|

|

|

|

|

|

|

|

|

|

R |

|

SG3525A Output Stage |

||

|

9 |

|

+ |

|

|||

|

|

S |

|

||||

|

|

|

|

13 |

|||

Compensation |

|

|

± PWM |

Latch |

|

|

|

|

1 |

±Error |

± |

|

|

|

VC |

INV. Input |

|

|

|

|

|||

2 |

50μA |

S |

|

|

Output A |

||

Noninv. Input |

+Amp |

|

|

|

|

|

|

8 |

|

VREF |

|

OR |

11 |

||

CSoft±Start |

|

|

|

|

|

|

|

|

|

|

|

|

|

Output B |

|

|

10 |

5.0k |

|

|

|

|

|

Shutdown |

5.0k |

|

|

|

|

||

|

|

|

|

OR |

14 |

||

|

|

|

|

|

|||

|

|

|

|

|

|

||

|

|

|

|

|

|

|

SG3527A |

|

|

|

|

|

|

|

Output Stage |

SG3525A

SG3527A

PULSE WIDTH MODULATOR

CONTROL CIRCUITS

SEMICONDUCTOR

TECHNICAL DATA

|

N SUFFIX |

|

PLASTIC PACKAGE |

16 |

CASE 648 |

|

1 |

|

|

DW SUFFIX |

|

|

PLASTIC PACKAGE |

16 |

|

CASE 751B |

|

(SO±16L) |

|

|

1 |

|

|

|

PIN CONNECTIONS

Inv. Input |

|

|

|

|

|

Vref |

||||

1 |

|

|

|

16 |

||||||

Noninv. Input |

|

|

|

|

|

VCC |

||||

2 |

|

|

|

15 |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

Sync |

3 |

|

|

|

14 |

Output B |

|||

OSC. Output |

|

|

|

|

|

VC |

||||

4 |

|

|

|

13 |

||||||

|

CT |

|

|

|

|

|

Ground |

|||

|

5 |

|

|

|

12 |

|||||

|

RT |

|

|

|

|

|

Output A |

|||

|

6 |

|

|

|

11 |

|||||

Discharge |

|

|

|

|

|

|

|

|

||

7 |

|

|

|

10 |

Shutdown |

|||||

Soft±Start |

|

|

|

|

|

Compensation |

||||

8 |

|

|

|

9 |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(Top View) |

|

|

|

|||

ORDERING INFORMATION

|

Operating |

|

Device |

Temperature Range |

Package |

|

|

|

SG3525AN |

|

Plastic DIP |

|

TA = 0° to +70°C |

|

SG3525ADW |

SO±16L |

|

SG3527AN |

|

Plastic DIP |

|

|

|

Motorola, Inc. 1996 |

Rev 2 |

SG3525A SG3527A

MAXIMUM RATINGS (Note 1)

Rating |

Symbol |

Value |

Unit |

|

|

|

|

Supply Voltage |

VCC |

+40 |

Vdc |

Collector Supply Voltage |

VC |

+40 |

Vdc |

Logic Inputs |

|

±0.3 to +5.5 |

V |

|

|

|

|

Analog Inputs |

|

±0.3 to VCC |

V |

Output Current, Source or Sink |

IO |

±500 |

mA |

Reference Output Current |

Iref |

50 |

mA |

Oscillator Charging Current |

|

5.0 |

mA |

|

|

|

|

Power Dissipation (Plastic & Ceramic Package) |

PD |

|

mW |

TA = +25°C (Note 2) |

|

1000 |

|

TC = +25°C (Note 3) |

|

2000 |

|

Thermal Resistance Junction±to±Air |

RθJA |

100 |

°C/W |

Thermal Resistance Junction±to±Case |

RθJC |

60 |

°C/W |

Operating Junction Temperature |

TJ |

+150 |

°C |

Storage Temperature Range |

Tstg |

±55 to +125 |

°C |

Lead Temperature (Soldering, 10 seconds) |

TSolder |

+300 |

°C |

NOTES: 1. Values beyond which damage may occur. |

|

|

|

2. Derate at 10 mW/°C for ambient temperatures above +50°C. |

|

|

|

3. Derate at 16 mW/°C for case temperatures above +25°C. |

|

|

|

RECOMMENDED OPERATING CONDITIONS

Characteristics |

Symbol |

Min |

Max |

Unit |

|

|

|

|

|

Supply Voltage |

VCC |

8.0 |

35 |

Vdc |

Collector Supply Voltage |

VC |

4.5 |

35 |

Vdc |

Output Sink/Source Current |

IO |

|

±100 |

mA |

(Steady State) |

|

0 |

|

|

(Peak) |

|

0 |

±400 |

|

|

|

|

|

|

Reference Load Current |

Iref |

0 |

20 |

mA |

Oscillator Frequency Range |

fosc |

0.1 |

400 |

kHz |

Oscillator Timing Resistor |

RT |

2.0 |

150 |

kΩ |

Oscillator Timing Capacitor |

CT |

0.001 |

0.2 |

μF |

Deadtime Resistor Range |

RD |

0 |

500 |

Ω |

Operating Ambient Temperature Range |

TA |

0 |

+70 |

°C |

APPLICATION INFORMATION

Shutdown Options (See Block diagram, front page)

Since both the compensation and soft±start terminals (Pins 9 and 8) have current source pull±ups, either can readily accept a pull±down signal which only has to sink a maximum of 100 μA to turn off the outputs. This is subject to the added requirement of discharging whatever external capacitance may be attached to these pins.

An alternate approach is the use of the shutdown circuitry of Pin 10 which has been improved to enhance the available shutdown options. Activating this circuit by applying a positive signal on Pin 10 performs two functions: the PWM

latch is immediately set providing the fastest turn±off signal to the outputs; and a 150 μA current sink begins to discharge the external soft±start capacitor. If the shutdown command is short, the PWM signal is terminated without significant discharge of the soft±start capacitor, thus, allowing, for example, a convenient implementation of pulse±by±pulse current limiting. Holding Pin 10 high for a longer duration, however, will ultimately discharge this external capacitor, recycling slow turn±on upon release.

Pin 10 should not be left floating as noise pickup could conceivably interrupt normal operation.

2 |

MOTOROLA ANALOG IC DEVICE DATA |

SG3525A SG3527A

ELECTRICAL CHARACTERISTICS (VCC = +20 Vdc, TA = Tlow to Thigh [Note 4], unless otherwise noted.)

Characteristics |

Symbol |

Min |

Typ |

Max |

Unit |

||||

|

|

|

|

|

|

|

|

|

|

REFERENCE SECTION |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Reference Output Voltage (TJ = +25°C) |

|

Vref |

|

|

|

5.00 |

5.10 |

5.20 |

Vdc |

Line Regulation (+8.0 V ≤ VCC ≤ +35 V) |

Regline |

± |

10 |

20 |

mV |

||||

Load Regulation (0 mA ≤ IL ≤ 20 mA) |

Regload |

± |

20 |

50 |

mV |

||||

Temperature Stability |

|

Vref/ |

|

T |

± |

20 |

± |

mV |

|

Total Output Variation |

|

Vref |

4.95 |

± |

5.25 |

Vdc |

|||

Includes Line and Load Regulation over Temperature |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Short Circuit Current |

|

ISC |

|

|

|

± |

80 |

100 |

mA |

(Vref = 0 V, TJ = +25°C) |

|

|

|

|

|

|

|

|

|

Output Noise Voltage (10 Hz ≤ f ≤ 10 kHz, TJ = +25°C) |

|

Vn |

|

|

|

± |

40 |

200 |

μVrms |

Long Term Stability (TJ = +125°C) (Note 5) |

|

S |

|

|

|

± |

20 |

50 |

mV/khr |

OSCILLATOR SECTION (Note 6, unless otherwise noted.) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Initial Accuracy (TJ = +25°C) |

|

|

|

|

|

± |

±2.0 |

±6.0 |

% |

Frequency Stability with Voltage |

|

fosc |

± |

±1.0 |

±2.0 |

% |

|||

(+8.0 V ≤ VCC ≤ +35 V) |

|

|

|

|

|

|

|

|

|

D VCC |

|

|

|

|

|||||

Frequency Stability with Temperature |

|

fosc |

|

± |

±0.3 |

± |

% |

||

|

|

D |

T |

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

Minimum Frequency (RT = 150 kΩ, CT = 0.2 μF) |

|

fmin |

|

|

|

± |

50 |

± |

Hz |

Maximum Frequency (RT = 2.0 kΩ, CT = 1.0 nF) |

|

fmax |

400 |

± |

± |

kHz |

|||

Current Mirror (IRT = 2.0 mA) |

|

|

|

|

|

1.7 |

2.0 |

2.2 |

mA |

Clock Amplitude |

|

|

|

|

|

3.0 |

3.5 |

± |

V |

|

|

|

|

|

|

|

|

|

|

Clock Width (TJ = +25°C) |

|

|

|

|

|

0.3 |

0.5 |

1.0 |

μs |

Sync Threshold |

|

|

|

|

|

1.2 |

2.0 |

2.8 |

V |

|

|

|

|

|

|

|

|

|

|

Sync Input Current (Sync Voltage = +3.5 V) |

|

|

|

|

|

± |

1.0 |

2.5 |

mA |

|

|

|

|

|

|

|

|

|

|

ERROR AMPLIFIER SECTION (VCM = +5.1 V) |

|

|

|

|

|

|

|

|

|

Input Offset Voltage |

|

VIO |

|

|

|

± |

2.0 |

10 |

mV |

Input Bias Current |

|

IIB |

|

|

|

± |

1.0 |

10 |

μA |

Input Offset Current |

|

IIO |

|

|

|

± |

± |

1.0 |

μA |

DC Open Loop Gain (RL ≥ 10 MΩ) |

|

AVOL |

60 |

75 |

± |

dB |

|||

Low Level Output Voltage |

|

VOL |

|

|

|

± |

0.2 |

0.5 |

V |

High Level Output Voltage |

|

VOH |

3.8 |

5.6 |

± |

V |

|||

Common Mode Rejection Ratio (+1.5 V ≤ VCM ≤ +5.2 V) |

CMRR |

60 |

75 |

± |

dB |

||||

Power Supply Rejection Ratio (+8.0 V ≤ VCC ≤ +35 V) |

|

PSRR |

50 |

60 |

± |

dB |

|||

PWM COMPARATOR SECTION |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

Minimum Duty Cycle |

DCmin |

± |

± |

0 |

% |

||||

Maximum Duty Cycle |

DCmax |

45 |

49 |

± |

% |

||||

Input Threshold, Zero Duty Cycle (Note 6) |

|

Vth |

|

|

|

0.6 |

0.9 |

± |

V |

Input Threshold, Maximum Duty Cycle (Note 6) |

|

Vth |

|

|

|

± |

3.3 |

3.6 |

V |

Input Bias Current |

|

IIB |

|

|

|

± |

0.05 |

1.0 |

μA |

NOTES: 4. Tlow = 0° for SG3525A, 3527A Thigh = +70°C for SG3525A, 3527A

5.Since long term stability cannot be measured on each device before shipment, this specification is an engineering estimate of average stability from lot to lot.

6.Tested at fosc = 40 kHz (RT = 3.6 kΩ, CT = 0.01 μF, RD = 0Ω).

MOTOROLA ANALOG IC DEVICE DATA |

3 |

|

Loading...

Loading...