Motorola SN54LS107AJ, SN74LS107AD, SN74LS107AN Datasheet

DUAL JK NEGATIVE EDGE-TRIGGERED FLIP-FLOP

The SN54/74LS107A is a Dual JK Flip-Flop with individual J, K, Direct Clear and Clock Pulse inputs. Output changes are initiated by the HIGH-to-LOW transition of the clock. A LOW signal on CD input overrides the other inputs and makes the Q output LOW.

The SN54 /74LS107A is the same as the SN54/74LS73A but has corner power pins.

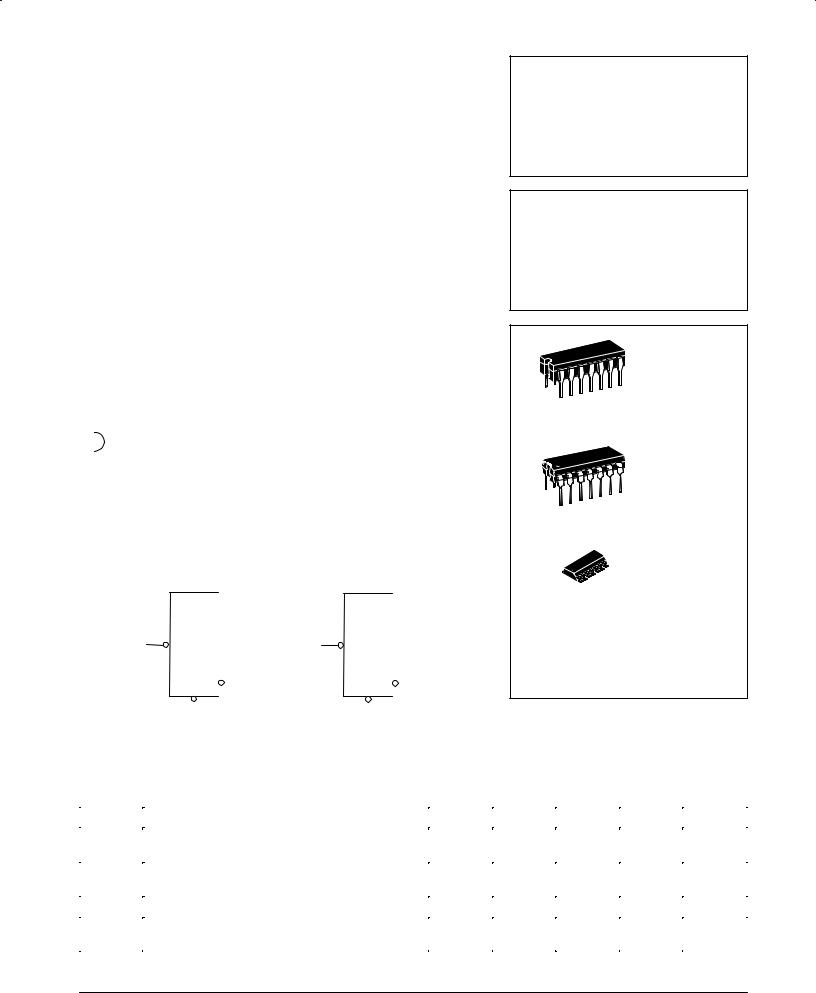

CONNECTION DIAGRAM DIP (TOP VIEW)

|

VCC |

CD1 |

CP1 |

|

K2 |

|

CD2 |

CP2 |

|

J2 |

|||||||

|

14 |

|

13 |

|

12 |

|

11 |

|

10 |

|

9 |

|

8 |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

NOTE: |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

The Flatpak version has the |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

same pinouts (Connection |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Diagram) as the Dual In-Line |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Package. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

2 |

|

3 |

|

4 |

|

5 |

|

6 |

|

7 |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

J1 |

Q1 |

Q1 |

|

K1 |

|

Q2 |

Q2 |

GND |

||||||||

LOGIC SYMBOL

|

|

|

|

1 |

|

|

|

|

|

|

|

|

2 |

|

|

|

|

||

1 |

|

|

J |

|

Q |

|

|

3 |

8 |

|

|

J |

|

Q |

|

|

5 |

||

|

|

|

|

|

|

|

|

|

|

||||||||||

12 |

|

|

CP |

|

|

|

|

|

|

9 |

|

|

CP |

|

|

|

|

|

|

4 |

|

|

K |

|

Q |

|

|

|

2 |

|

|

|

K |

|

Q |

|

|

|

|

|

|

|

|

CD |

|

|

|

|

11 |

|

|

|

CD |

|

6 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

13 |

|

|

|

|

|

|

|

|

10 |

|

|

|

|

||

|

|

|

|

|

|

|

|

|

VCC = PIN 14 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

GND |

= PIN 7 |

|

|

|

|

|

|

|

|

|

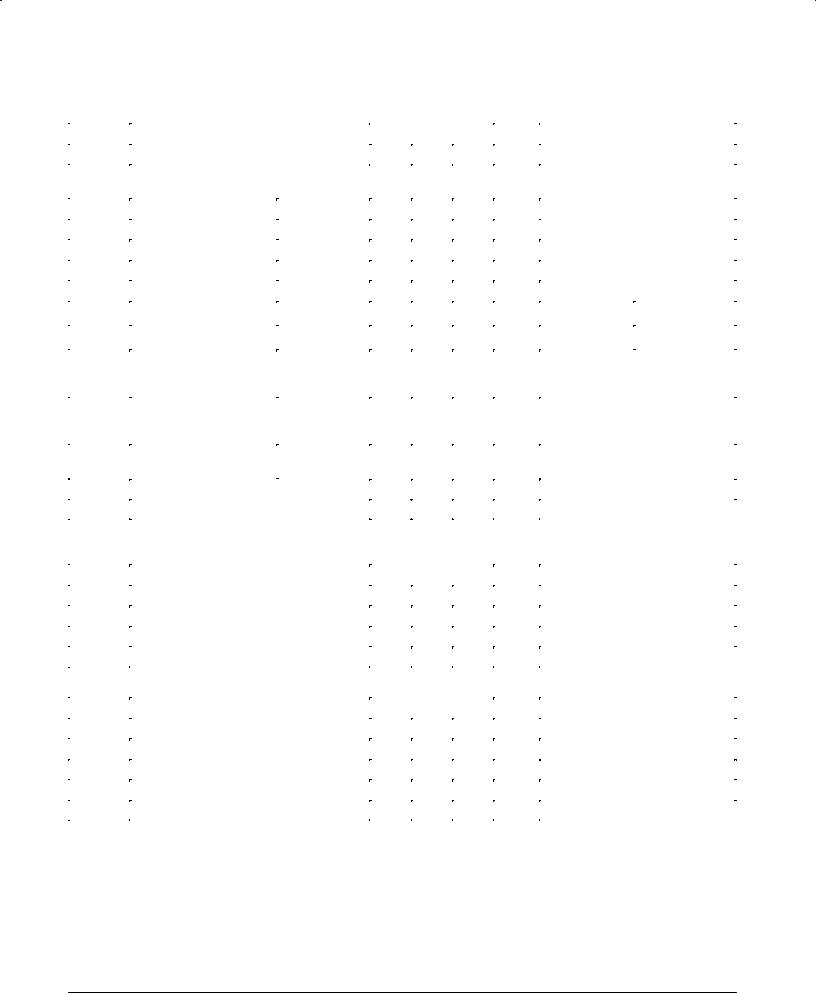

SN54/74LS107A

DUAL JK NEGATIVE

EDGE-TRIGGERED FLIP-FLOP

LOW POWER SCHOTTKY

|

|

|

J SUFFIX |

|

|

|

CERAMIC |

|

|

|

CASE 632-08 |

14 |

1 |

|

|

|

|

|

|

|

|

|

N SUFFIX |

|

|

|

PLASTIC |

14 |

|

|

CASE 646-06 |

|

|

|

|

|

1 |

|

|

|

|

|

D SUFFIX |

|

14 |

|

SOIC |

|

|

CASE 751A-02 |

|

|

|

1 |

|

|

|

|

ORDERING INFORMATION

SN54LSXXXJ Ceramic

SN74LSXXXN Plastic

SN74LSXXXD SOIC

GUARANTEED OPERATING RANGES

Symbol |

Parameter |

|

Min |

Typ |

Max |

Unit |

|

|

|

|

|

|

|

VCC |

Supply Voltage |

54 |

4.5 |

5.0 |

5.5 |

V |

|

|

74 |

4.75 |

5.0 |

5.25 |

|

|

|

|

|

|

|

|

TA |

Operating Ambient Temperature Range |

54 |

± 55 |

25 |

125 |

°C |

|

|

74 |

0 |

25 |

70 |

|

|

|

|

|

|

|

|

IOH |

Output Current Ð High |

54, 74 |

|

|

± 0.4 |

mA |

IOL |

Output Current Ð Low |

54 |

|

|

4.0 |

mA |

|

|

74 |

|

|

8.0 |

|

|

|

|

|

|

|

|

FAST AND LS TTL DATA

5-177

SN54/74LS107A

DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE (unless otherwise specified)

|

|

|

|

Limits |

|

|

|

|

|

|

|

|

|

|

|

|

|

Symbol |

Parameter |

|

Min |

Typ |

Max |

Unit |

Test Conditions |

|

|

|

|

|

|

|

|

|

|

VIH |

Input HIGH Voltage |

|

2.0 |

|

|

V |

Guaranteed Input HIGH Voltage for |

|

|

|

|

All Inputs |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VIL |

Input LOW Voltage |

54 |

|

|

0.7 |

V |

Guaranteed Input LOW Voltage for |

|

74 |

|

|

0.8 |

All Inputs |

|

|||

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

VIK |

Input Clamp Diode Voltage |

|

|

± 0.65 |

± 1.5 |

V |

VCC = MIN, IIN = ±18 mA |

|

VOH |

Output HIGH Voltage |

54 |

2.5 |

3.5 |

|

V |

VCC = MIN, IOH = MAX, VIN = VIH |

|

74 |

2.7 |

3.5 |

|

V |

or VIL per Truth Table |

|||

|

|

|

||||||

|

|

54, 74 |

|

0.25 |

0.4 |

V |

I = 4.0 mA |

VCC = VCC MIN, |

VOL |

Output LOW Voltage |

|

|

|

|

|

OL |

VIN = VIL or VIH |

74 |

|

0.35 |

0.5 |

V |

IOL = 8.0 mA |

|||

|

|

|

per Truth Table |

|||||

|

|

J, K |

|

|

20 |

|

|

|

|

|

Clear |

|

|

60 |

μA |

VCC = MAX, VIN = 2.7 V |

|

IIH |

Input HIGH Current |

Clock |

|

|

80 |

|

|

|

|

|

|

|

|

|

|

||

J, K |

|

|

0.1 |

|

|

|

||

|

|

|

|

|

|

|

||

|

|

Clear |

|

|

0.3 |

mA |

VCC = MAX, VIN = 7.0 V |

|

|

|

Clock |

|

|

0.4 |

|

|

|

|

|

|

|

|

|

|

|

|

IIL |

Input LOW Current |

J, K |

|

|

± 0.4 |

mA |

VCC = MAX, VIN = 0.4 V |

|

Clear and Clock |

|

|

± 0.8 |

|||||

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

IOS |

Short Circuit Current (Note 1) |

|

± 20 |

|

±100 |

mA |

VCC = MAX |

|

ICC |

Power Supply Current |

|

|

|

6.0 |

mA |

VCC = MAX |

|

Note 1: Not more than one output should be shorted at a time, nor for more than 1 second.

AC CHARACTERISTICS (TA = 25°C, VCC = 5.0 V)

|

|

|

Limits |

|

|

|

|

|

|

|

|

|

|

Symbol |

Parameter |

Min |

Typ |

Max |

Unit |

Test Conditions |

|

|

|

|

|

|

|

fMAX |

Maximum Clock Frequency |

30 |

45 |

|

MHz |

VCC = 5.0 V |

tPLH |

Propagation Delay, |

|

15 |

20 |

ns |

|

|

CL = 15 pF |

|||||

|

|

|

|

|||

tPHL |

Clock to Output |

|

15 |

20 |

ns |

|

AC SETUP REQUIREMENTS (TA = 25°C, VCC = 5.0 V)

|

|

|

Limits |

|

|

|

|

|

|

|

|

|

|

Symbol |

Parameter |

Min |

Typ |

Max |

Unit |

Test Conditions |

|

|

|

|

|

|

|

tW |

Clock Pulse Width |

20 |

|

|

ns |

|

tW |

Clear Pulse Width |

25 |

|

|

ns |

VCC = 5.0 V |

ts |

Setup Time |

20 |

|

|

ns |

|

|

|

|

||||

th |

Hold Time |

0 |

|

|

ns |

|

FAST AND LS TTL DATA

5-178

Loading...

Loading...