AMD Advanced Micro Devices AM29F100T-120DWI1, AM29F100T-120DWE1, AM29F100T-120DWC1, AM29F100T-120DTI1, AM29F100T-120DTE1 Datasheet

...

SUPPLEMENT

Am29F100 Known Good Die

1 Megabit (128 K x 8-Bit/64 K x 16-Bit)

CMOS 5.0 Volt-only, Boot Sector Flash Memory—Die Revision 1

DISTINCTIVE CHARACTERISTICS

■Single power supply operation

—5.0 V ± 10% for read, erase, and program operations

—Simplifies system-level power requirements

■High performance

—120 ns maximum access time

■Low power consumption

—20 mA typical active read current for byte mode

—28 mA typical active read current for word mode

—30 mA typical program/erase current

—25 μA typical standby current

■Flexible sector architecture

—One 16 Kbyte, two 8 Kbyte, one 32 Kbyte, and one 64 Kbyte sectors (byte mode)

—One 8 Kword, two 4 Kword, one 16 Kword, and one 32 Kword sectors (word mode)

—Any combination of sectors can be erased

—Supports full chip erase

■Top or bottom boot block configurations available

■Sector protection

—Hardware-based feature that disables/reenables program and erase operations in any combination of sectors

—Sector protection/unprotection can be implemented using standard PROM programming equipment

—Temporary Sector Unprotect feature allows insystem code changes in protected sectors

■Embedded Algorithms

—Embedded Erase algorithm automatically pre-programs and erases the chip or any combination of designated sector

—Embedded Program algorithm automatically programs and verifies data at specified address

■Minimum 100,000 program/erase cycles guaranteed

■Compatible with JEDEC standards

—Pinout and software compatible with

single-power-supply flash

—Superior inadvertent write protection

■Data Polling and Toggle Bits

—Provides a software method of detecting program or erase cycle completion

■Ready/Busy pin (RY/BY#)

—Provides a hardware method for detecting program or erase cycle completion

■Erase Suspend/Erase Resume

—Suspends an erase operation to read data from, or program data to, a sector that is not being erased, then resumes the erase operation

■Hardware RESET# pin

—Hardware method of resetting the device to reading array data

■Tested to datasheet specifications at temperature

■Quality and reliability levels equivalent to standard packaged components

Publication# 21235 Rev: B Amendment/0

Issue Date: January 1998

S U P P L E M E N T

GENERAL DESCRIPTION

The Am29F100 in Known Good Die (KGD) form is a 1 Mbit, 5.0 Volt-only Flash memory. AMD defines KGD as standard product in die form, tested for functionality and speed. AMD KGD products have the same reliability and quality as AMD products in packaged form.

Am29F100 Features

The Am29F100 is a 1 Mbit, 5.0 Volt-only Flash memory organized as 131,072 bytes or 65,536 words. Wordwide data appears on DQ0-DQ15; byte-wide data on DQ0-DQ7. The device is designed to be programmed in-system with the standard system 5.0 Volt VCC supply. A 12.0 volt VPP is not required for program or erase operations. The device can also be programmed or erased in standard EPROM programmers.

To eliminate bus contention the device has separate chip enable (CE#), write enable (WE#) and output enable (OE#) controls.

The device requires only a single 5.0 volt power supply for both read and write functions. Internally generated and regulated voltages are provided for the program and erase operations.

The device is entirely command set compatible with the

JEDEC single-power-supply Flash standard. Commands are written to the command register using standard microprocessor write timings. Register contents serve as input to an internal state machine that controls the erase and programming circuitry. Write cycles also internally latch addresses and data needed for the programming and erase operations. Reading data out of the device is similar to reading from other Flash or EPROM devices.

Device programming occurs by executing the program command sequence. This invokes the Embedded Program algorithm—an internal algorithm that automatically times the program pulse widths and verifies proper cell margin.

Device erasure occurs by executing the erase command sequence. This invokes the Embedded Erase algorithm—an internal algorithm that automatically preprograms the array (if it is not already programmed) before executing the erase operation. During erase, the

device automatically times the erase pulse widths and verifies proper cell margin.

The host system can detect whether a program or erase operation is complete by observing the RY/BY# pin, or by reading the DQ7 (Data# Polling) and DQ6 (toggle) status bits. After a program or erase cycle has been completed, the device is ready to read array data or accept another command.

The Erase Suspend feature enables the system to put erase on hold for any period of time to read data from, or program data to, a sector that is not being erased.

The sector erase architecture allows memory sectors to be erased and reprogrammed without affecting the data contents of other sectors. The device is erased when shipped from the factory.

The hardware data protection measures include a low VCC detector automatically inhibits write operations during power transitions. The hardware sector protection feature disables both program and erase operations in any combination of the sectors of memory, and is implemented using standard EPROM programmers. The temporary sector unprotect feature allows in-system changes to protected sectors.

The hardware RESET# pin terminates any operation in progress and resets the internal state machine to reading array data. The RESET# pin may be tied to the system reset circuitry. A system reset would thus also reset the device, enabling the system microprocessor to read the boot-up firmware from the Flash memory.

The system can place the device into the standby mode. Power consumption is greatly reduced in this mode.

AMD’s Flash technology combines years of Flash memory manufacturing experience to produce the highest levels of quality, reliability, and cost effectiveness. The device electrically erases all bits within a sector simultaneously via Fowler-Nordheim tunneling. The bytes are programmed one byte at a time using the EPROM programming mechanism of hot electron injection.

ELECTRICAL SPECIFICATIONS

Refer to the Am29F100 data sheet, document number 18926, for full electrical specifications on the Am29F100.

2 |

Am29F100 Known Good Die |

|

S U P P L E M E N T |

|

PRODUCT SELECTOR GUIDE |

|

|

|

|

|

Family Part Number |

|

Am29F100 KGD |

|

|

|

Speed Option (VCC = 5.0 V ± 10%) |

|

-120 |

|

|

|

Max Access Time, tACC (ns) |

|

120 |

|

|

|

Max CE# Access, tCE (ns) |

|

120 |

|

|

|

Max OE# Access, tOE (ns) |

|

50 |

|

|

|

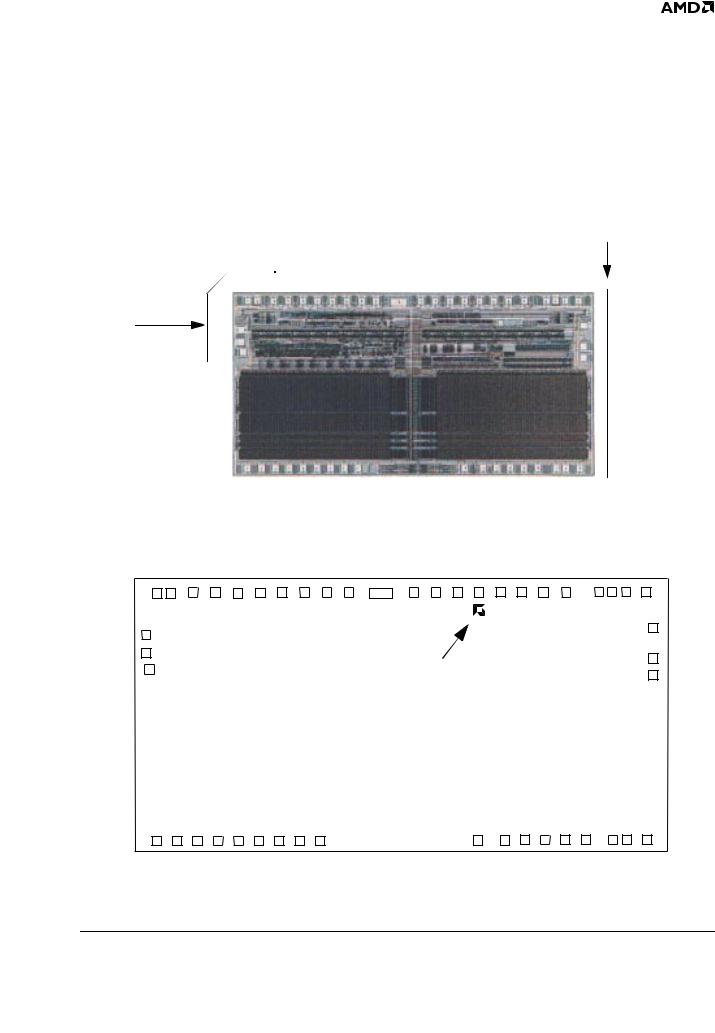

DIE PHOTOGRAPH |

|

|

|

|

Orientation relative |

|

|

to leading edge of |

|

|

tape and reel |

Orientation relative to top left corner of Gel-Pak

DIE PAD LOCATIONS

11 10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

47 |

46 |

45 |

44 |

43 |

42 |

41 |

40 |

39 38 37 36 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

35

12

13 |

34 |

|

14 |

AMD logo location |

33 |

|

|

15 16 |

17 |

18 |

19 |

20 |

21 |

22 |

23 |

24 |

25 |

26 |

27 |

28 |

29 |

30 31 32 |

Am29F100 Known Good Die |

3 |

Loading...

Loading...