Mitsubishi M5M29FT800FP-12, M5M29FT800FP-10, M5M29FT800FP, M5M29FB800VP-80, M5M29FB800VP-12 Datasheet

...

MITSUBISHI LSIs

M5M29FB/T800FP,VP,RV-80,-10,-12

May 1997 , Rev.6.1

8,388,608-BIT (1048,576-WORD BY 8-BIT / 524,288-WORD BY16-BIT)

CMOS 3.3V-ONLY, BLOCK ERASE FLASH MEMORY

1

MITSUBISHI LSIs

DESCRIPTION

The MITSUBISHI M5M29FB/T800FP, VP, RV are 3.3V-only high speed 8,388,608-bit CMOS boot block Flash Memories suitable for

mobile and personal computing, and communication products. The M5M29FB/T800FP, VP, RV are fabricated by CMOS technology for

the peripheral circuits and DINOR(Divided bit line NOR) architecture for the memory cells, and are available in 44pin SOP or 48pin

TSOP(I).

FEATURES

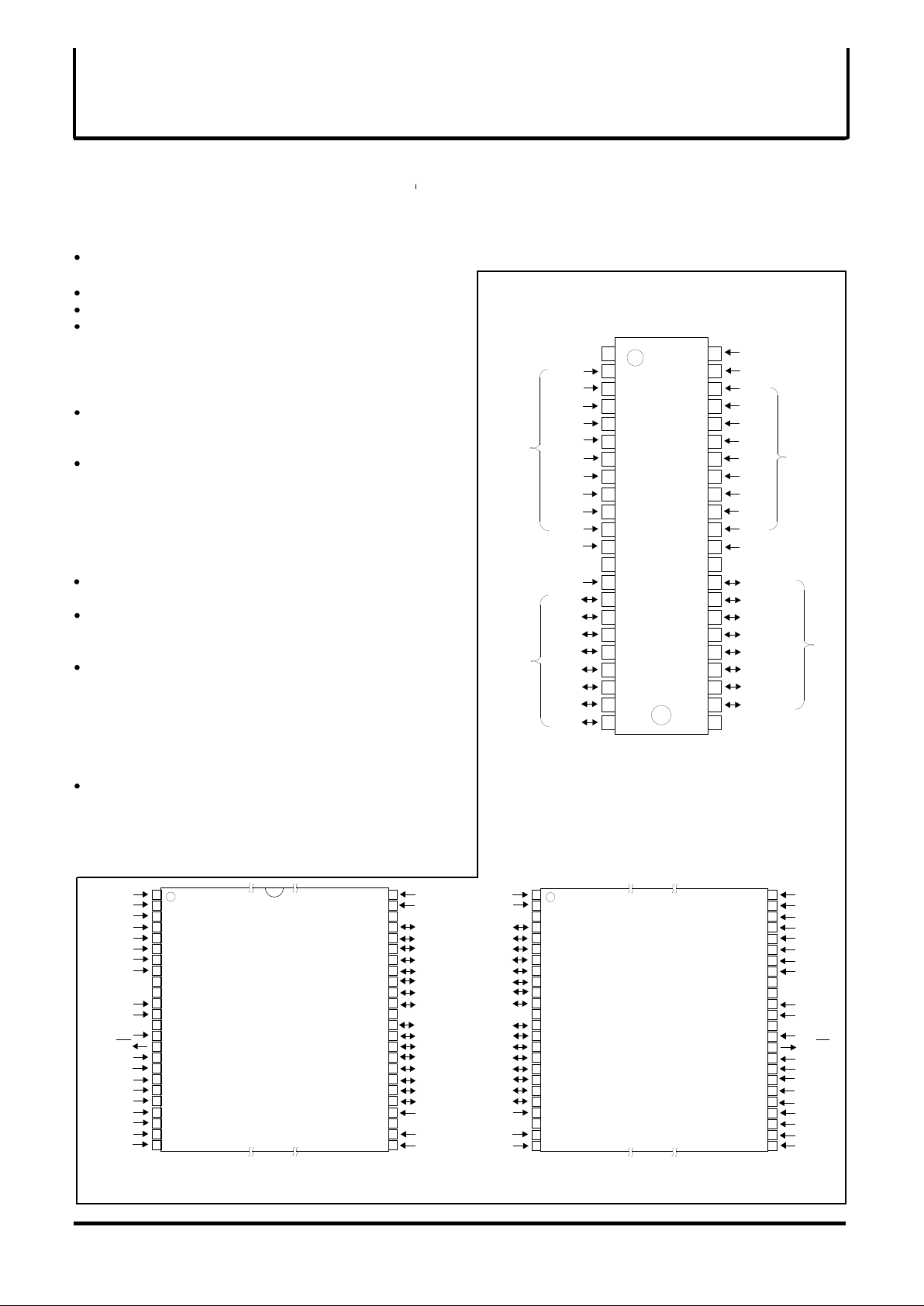

PIN CONFIGURATION (TOP VIEW)

Organization 524,288 word x 16bit

1,048,576 word x 8 bit

Supply voltage ................................ VCC = 3.3V±0.3V

Access time 80/100/120ns (Max)

Power Dissipation

Read 108 mW (Max.)

Program/Erase 144 mW (Max.)

Standby 0.72 mW (Max.)

Deep power down mode 3.3µW (typ.)

Auto program

Program Time 7.5ms (typ.)

Program Unit 128word

Auto Erase

Erase time 50 ms (typ.)

Erase Unit

Boot Block 8Kword / 16Kbyte x 1

Parameter Block 4Kword / 8Kbyte x 2

Main Block 16Kword / 32Kbyte x 1

32Kword / 64Kbyte x 15

Program/Erase cycles 100Kcycles

Boot Block

M5M29FB800 Bottom Boot

M5M29FT800 Top Boot

Other Functions

Software Command Control

Selective Block Lock

Erase Suspend/Resume

Program Suspend/Resume

Status Register Read

Sleep

Package

48-Lead, 12mmx 20mm TSOP (type-I)

44-Lead SOP

8,388,608-BIT (1048,576-WORD BY 8-BIT / 524,288-WORD BY16-BIT)

CMOS 3.3V-ONLY, BLOCK ERASE FLASH MEMORY

M5M29FB/T800FP,VP,RV-80,-10,-12

1

NC : NO CONNECTION

RV(Reverse bend): 48P3R-COutline 48pin TSOP type-I (12 X 20mm)

VP(Normal bend): 48P3R-B

This product is compatible with HN29WB/T800 by Hitachi Ltd.

1

2

3

4

5

6

7

8

9

10

44

43

42

41

40

38

37

35

11

12

34

33

39

36

13 32

14

31

15 30

16 29

M5M29FB/T800FP

17 28

18 27

19 26

20 25

Outline 600mil 44-pin SOP

(FP: 44P2A-A)

21 24

22

23

.................................

..............................

.......................

.......................

.......................

.................................

.................................

........................

.............................

.................................

...........................

.................................

.......................

.......................

.......................

A15

A12

A10

DQ5

DQ12

A8

A13

A14

DQ4

/WE

A9

VCC

GND

A16

/RP

DQ13

A11

DQ6

DQ7

DQ14

DQ15/A-1

/BYTE/CE

A7

A5

A4

DQ0

DQ1

DQ2

DQ3

A3

A2

A1

A17

A18

DQ11

DQ10

DQ9

DQ8

/OE

GND

A0

A6

ADDRESS

INPUTS

ADDRESS

INPUTS

CHIP ENABLE

INPUT

BYTE ENABLE

INPUT

RESET/

POWER DOWN

INPUT

WRITE ENABLE

INPUT

DATA

INPUTS/

OUTPUTS

DATA

INPUTS/

OUTPUTS

OUTPUT ENABLE

INPUT

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

A18

A17

A16

RY/BY

NC

A11

A10

M5M29FB/T800VP

A15

/CE

17

18

19

20

28

27

26

25

DQ0

A0

21

22

23

24

48

47

46

45

A13

A12

A14

GND

/OE

A9

A8

NC

NC

/RP

A7

A6

A5

A4

A1

A2

A3

/WE

/BYTE

DQ8

DQ1

DQ9

DQ2

VCC

GND

DQ10

DQ3

DQ11

DQ4

DQ12

DQ5

DQ13

DQ6

DQ14

DQ7

DQ15/A-1

/WP

APPLICATION

Code Storage PC BIOS

Digital Cellular Phone/Telecommunication

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

RY/BY

M5M29FB/T800RV

A15

17

18

19

20

28

27

26

25

21

22

23

24

48

47

46

45

A14

GND

A18

A17

A7

A6

A5

A4

A1

A2

A3

NC

/RP

A11

A10

A9

A8

NC

NC

A13

A12

/WE

/CE

DQ0

A0

/OE

DQ8

DQ1

DQ9

DQ2

/WP

VCC

GND

DQ10

DQ3

DQ11

DQ4

DQ12

DQ5

DQ13

DQ6

DQ14

DQ7

DQ15/A-1

A16

/BYTE

NC

...........................

...........................

.......................................

MITSUBISHI LSIs

M5M29FB/T800FP,VP,RV-80,-10,-12

May 1997 , Rev.6.1

8,388,608-BIT (1048,576-WORD BY 8-BIT / 524,288-WORD BY16-BIT)

CMOS 3.3V-ONLY, BLOCK ERASE FLASH MEMORY

2

FUNCTION

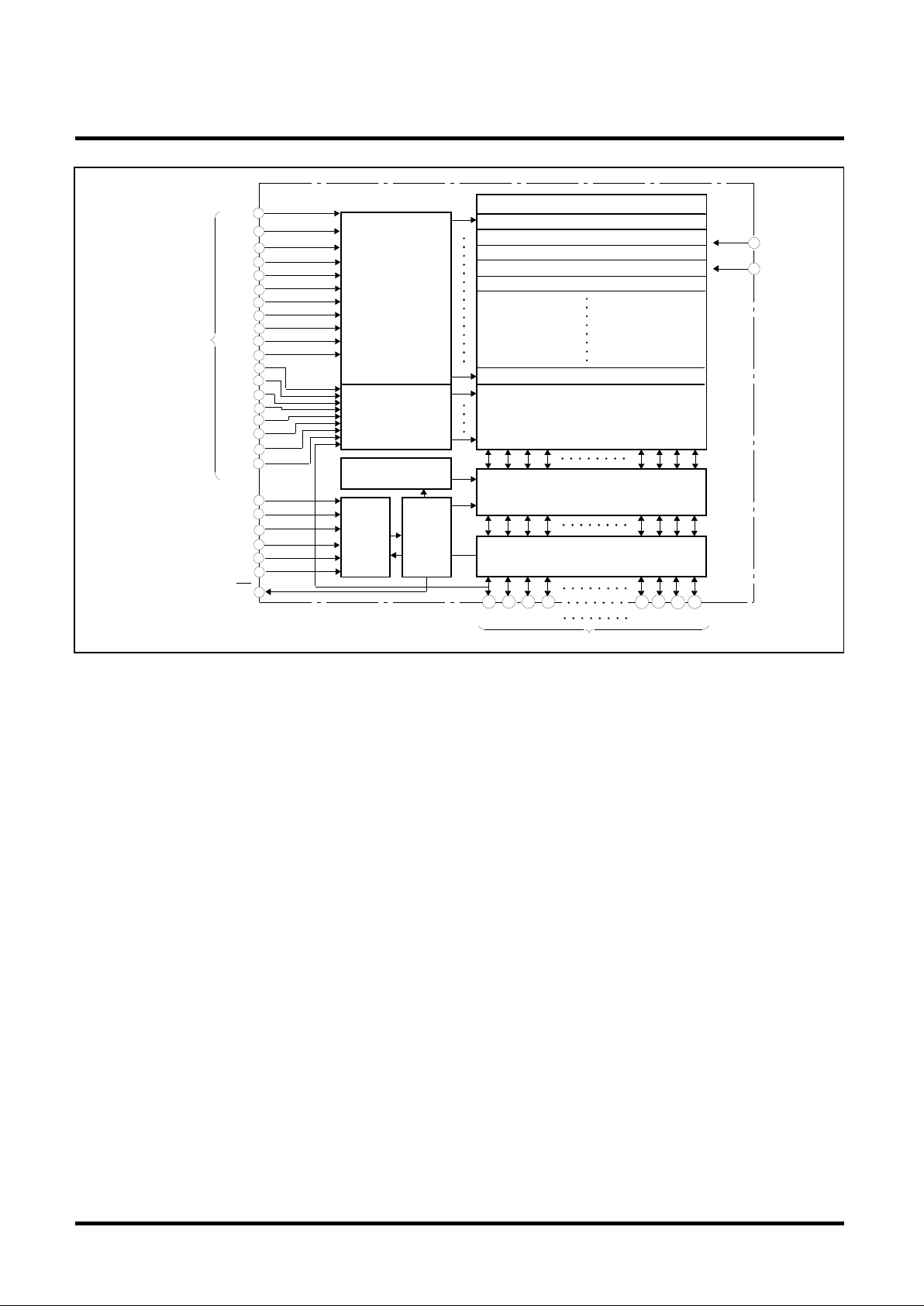

BLOCK DIAGRAM

Deep Power-Down

When /RP is at VIL, the device is in the deep powerdown

mode and its power consumption is substantially low. During

read modes, the memory is deselected and the data

input/output are in a high-impedance(High-Z) state. After

return from powerdown, the CUI is reset to Read Array , and

the Status Register is cleared to value 80H.

During block erase or program modes, /RP low will abort

either operation. Memory array data of the block being altered

become invalid.

X-DECODER

Y-DECODER

Y-GATE / SENSE AMP.

INPUT/OUTPUT

BUFFERS

/CE

/OE

/WE

VCC (3.3V)

GND (0V)

DATA INPUTS/OUTPUTS

The M5M29FB/T800FP,VP,RV includes on-chip program/erase

control circuitry. The Write State Machine (WSM) controls block

erase and page program operations. Operational modes are

selected by the commands written to the Command User Interface

(CUI). The Status Register indicates the status of the WSM and

when the WSM successfully completes the desired program or

block erase operation.

A Deep Powerdown mode is enabled when the /RP pin is at GND,

minimizing power consumption.

Read

The M5M29FB/T800FP,VP,RV has three read modes, which

accesses to the memory array, the Device Identifier and the Status

Register. The appropriate read command are required to be

written to the CUI. Upon initial device powerup or after exit from

deep powerdown, the M5M29FB/T800 automatically resets to read

array mode. In the read array mode, low level input to /CE and

/OE, high level input to /WE and /RP, and address signals to the

address inputs (A0-A18) output the data of the addressed location

to the data input/output(D0-15).

Write

Writes to the CUI enables reading of memory array data, device

identifiers and reading and clearing of the Status Register. They

also enable block erase and program. The CUI is written by

bringing /WE to low level, while /CE is at low level and /OE is at

high level. Address and data are latched on the earlier rising edge

of /WE and /CE. Standard micro-processor write timings are used.

D15/A-1D14D13D12

D2 D1

D0

D3

/WP

/RP

MULTIPLEXER

CUI WSM

STATUS / ID REGISTER

128 WORD PAGE BUFFER

Main Block 32KW

Standby

When /CE is at VIH, the device is in the standby mode and its

power consumption is reduced. Data input/output are in a

high-impedance(High-Z) state. If the memory is deselected during

block erase or program, the internal control circuits remain active

and the device consume normal active power until the operation

completes.

RY/BY

READY/BUSY OUTPUT

A18

A17

A16

A15

A14

A13

A12

A11

A10

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

Main Block 32KW

Main Block 16KW

Parameter Block2 4KW

Parameter Block1 4KW

Boot Block 8KW

ADDRESS

INPUTS

/BYTE

CHIP ENABLE INPUT

OUTPUT ENABLE INPUT

WRITE ENABLE INPUT

WRITE PROTECT INPUT

RESET/POWER DOWN INPUT

BYTE ENABLE INPUT

Output Disable

When /OE is at VIH, output from the devices is disabled.

Data input/output are in a high-impedance(High-Z) state.

MITSUBISHI LSIs

M5M29FB/T800FP,VP,RV-80,-10,-12

May 1997 , Rev.6.1

8,388,608-BIT (1048,576-WORD BY 8-BIT / 524,288-WORD BY16-BIT)

CMOS 3.3V-ONLY, BLOCK ERASE FLASH MEMORY

3

SOFTWARE COMMAND DEFINITIONS

The device operations are selected by writing specific software

command into the Command User Interface.

Read Array Command (FFH)

The device is in Read Array mode on initial device powerup and

after exit from deep powerdown, or by writing FFH to the

Command User Interface. The device remains in Read Array

mode until the other commands are written.

Read Device Identifier Command (90H)

Though PROM programmers can normally read device identifier

codes by raising A9 to VID, multiplexing high voltage onto address

lines is not desired for micro-processor system. It is an other

means to read device identifier codes that Read Device Identifier

Code Command(90H) is written to the command latch. Following

the command write, the manufacturer code and the device code

can be read from address 0000H and 0001H, respectively.

Read Status Register Command (70H)

The Status Register is read after writing the Read Status Register

command of 70H to the Command User Interface.

The contents of Status Register are latched on the later falling

edge of /OE or /CE. So /CE or /OE must be toggled every status

read.

Clear Status Register Command (50H)

The Erase Status and Program Status bits are set to "1"s by the

Write State Machine and can only be reset by the Clear Status

Register command of 50H. These bits indicates various failure

conditions.

DATA PROTECTION

The M5M29FB/T800 provides selectable block locking of memory

blocks. Each block has an associated nonvolatile lock-bit which

determines the lock status of the block. In addition, the

M5M29FB/T800 has a master Write Protect pin (WP) which

prevents any modifications to memory blocks whose lock-bits are

set to "0", when /WP is low. When /WP is high or /RP is VHH, all

blocks can be programmed or erased regardless of the state of

the lock-bits, and the lock-bits are cleared to "1" by erase.

Power Supply Voltage

When the power supply voltage (Vcc) is less than 2.2V, the device

is set to the Read-only mode.

A delay time of 2 us is required before any device operation is

initiated. The delay time is measured from the time Vcc reaches

Vccmin (3.0V).

During power up, /RP=GND is recommended. Falling in Busy

status is not recommended for possibility of damaging the device.

Block Erase / Confirm Command (20H/D0H)

Automated block erase is initiated by writing the Block Erase

command of 20H followed by the Confirm command of D0H. An

address within the block to be erased is required. The WSM

executes iterative erase pulse application and erase verify

operation.

Page Program Commands(41H)

Page Program allows fast programming of 128words of data.

Writing of 41H initiates the page program operation. From 2nd

cycle to 129th cycle write data must be serially inputted. Address

A6-0 have to be incremented from 00H to 7FH. After completion

of data loading, the WSM controls the program pulse application

and verify operation.

Basically re-program must not be done on a page which has

already programmed.

Suspend/Resume Command (B0H/D0H)

Writing the Suspend command of B0H during block erase

operation interrupts the block erase operation and allows read out

from another block of memory. Writing the Suspend command of

B0H during program operation interrupts the program operation

and allows read out from another block of memory. The device

continues to output Status Register data when read, after the

Suspend command is written to it. Polling the WSM Status and

Suspend Status bits will determine when the erase operation or

program operation has been suspended. At this point, writing of

the Read Array command to the CUI enables reading data from

blocks other than that which is suspended. When the Resume

command of D0H is written to the CUI, the WSM will continue with

the erase or program processes.

MITSUBISHI LSIs

M5M29FB/T800FP,VP,RV-80,-10,-12

May 1997 , Rev.6.1

8,388,608-BIT (1048,576-WORD BY 8-BIT / 524,288-WORD BY16-BIT)

CMOS 3.3V-ONLY, BLOCK ERASE FLASH MEMORY

4

1) X at RY/BY is VOL or VOH(Hi-Z).

*The RY/BY is an open drain output pin and indicates status of the internal WSM. When low,it indicates that the WSM is Busy performing an operation.

A pull-up resistor of 10K-100K Ohms is required to allow the RY/BY signal to transition high indicating a Ready WSM condition.

2) X can be VIH or VIL for control pins.

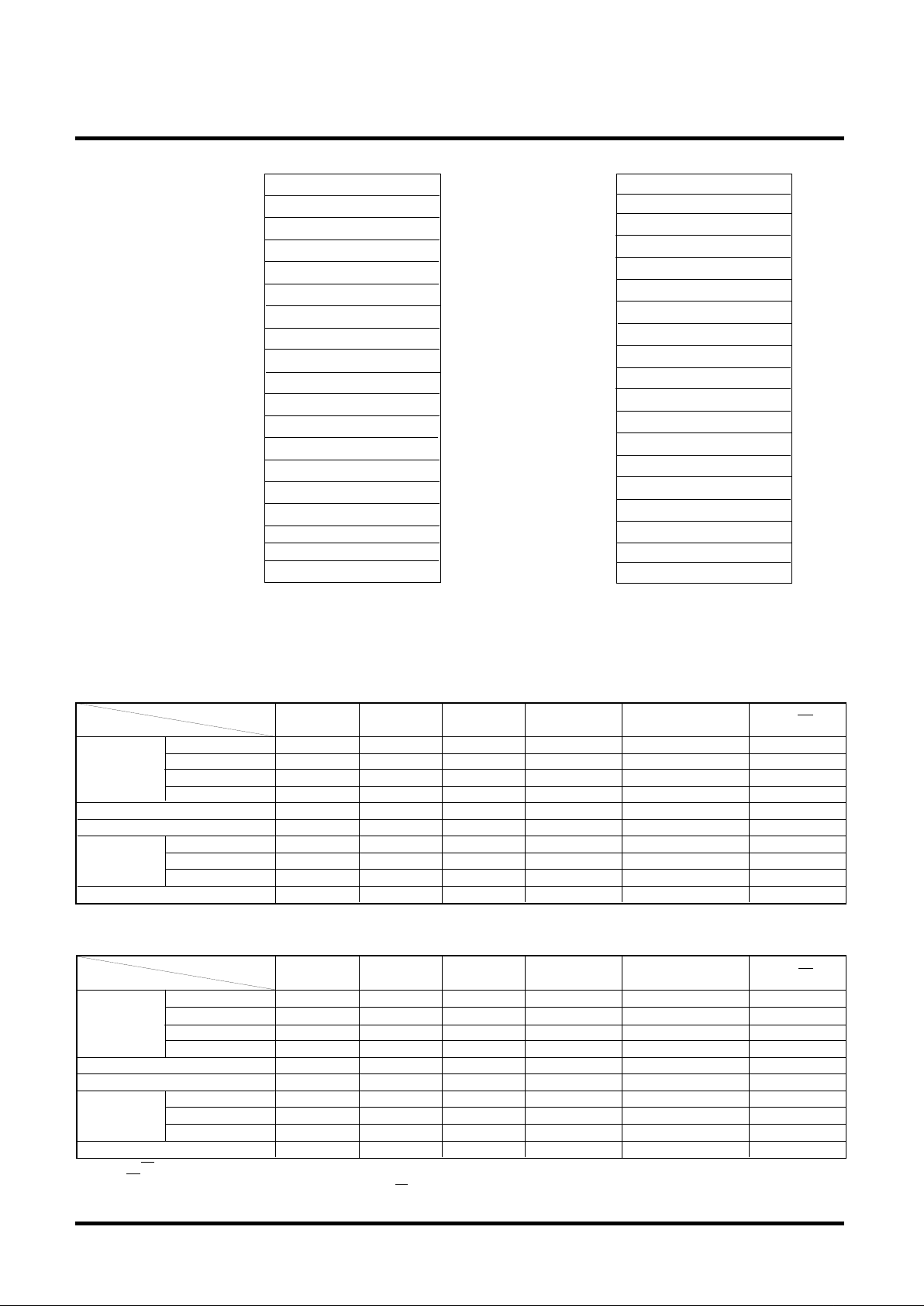

BUS OPERATIONS

32Kword MAIN BLOCK

32Kword MAIN BLOCK

32Kword MAIN BLOCK

32Kword MAIN BLOCK

32Kword MAIN BLOCK

32Kword MAIN BLOCK

32Kword MAIN BLOCK

32Kword MAIN BLOCK

32Kword MAIN BLOCK

32Kword MAIN BLOCK

32Kword MAIN BLOCK

32Kword MAIN BLOCK

32Kword MAIN BLOCK

32Kword MAIN BLOCK

32Kword MAIN BLOCK

16Kword MAIN BLOCK

4Kword PARAMETER BLOCK

4Kword PARAMETER BLOCK

8Kword BOOT BLOCK

M5M29FB800 Memory Map

8Kword BOOT BLOCK

32Kword MAIN BLOCK

32Kword MAIN BLOCK

32Kword MAIN BLOCK

32Kword MAIN BLOCK

32Kword MAIN BLOCK

32Kword MAIN BLOCK

32Kword MAIN BLOCK

32Kword MAIN BLOCK

32Kword MAIN BLOCK

32Kword MAIN BLOCK

32Kword MAIN BLOCK

32Kword MAIN BLOCK

32Kword MAIN BLOCK

32Kword MAIN BLOCK

16Kword MAIN BLOCK

4Kword PARAMETER BLOCK

4Kword PARAMETER BLOCK

32Kword MAIN BLOCK

M5M29FT800 Memory Map

78000H-7FFFFH

70000H-77FFFH

68000H-6FFFFH

60000H-67FFFH

58000H-5FFFFH

50000H-57FFFH

48000H-4FFFFH

40000H-47FFFH

38000H-3FFFFH

30000H-37FFFH

28000H-2FFFFH

20000H-27FFFH

18000H-1FFFFH

10000H-17FFFH

08000H-0FFFFH

04000H-07FFFH

03000H-03FFFH

02000H-02FFFH

00000H-01FFFH

F0000H-FFFFFH

E0000H-EFFFFH

D0000H-DFFFFH

C0000H-CFFFFH

B0000H-BFFFFH

A0000H-AFFFFH

90000H-9FFFFH

80000H-8FFFFH

70000H-7FFFFH

60000H-6FFFFH

50000H-5FFFFH

40000H-4FFFFH

30000H-3FFFFH

20000H-2FFFFH

10000H-1FFFFH

08000H-0FFFFH

06000H-07FFFH

04000H-05FFFH

00000H-03FFFH

A-1-A18(Bytemode)A0-A18(Wordmode)

7E000H-7FFFFH

7D000H-7DFFFH

7C000H-7CFFFH

78000H-7BFFFH

70000H-77FFFH

68000H-6FFFFH

60000H-67FFFH

58000H-5FFFFH

50000H-57FFFH

48000H-4FFFFH

40000H-47FFFH

38000H-3FFFFH

30000H-37FFFH

28000H-2FFFFH

20000H-27FFFH

18000H-1FFFFH

10000H-17FFFH

08000H-0FFFFH

00000H-07FFFH

FC000H-FFFFFH

FA000H-FBFFFH

F8000H-F9FFFH

F0000H-F7FFFH

E0000H-EFFFFH

D0000H-DFFFFH

C0000H-CFFFFH

B0000H-BFFFFH

A0000H-AFFFFH

90000H-9FFFFH

80000H-8FFFFH

70000H-7FFFFH

60000H-6FFFFH

50000H-5FFFFH

40000H-4FFFFH

30000H-3FFFFH

20000H-2FFFFH

10000H-1FFFFH

00000H-0FFFFH

A-1-A18(Bytemode)A0-A18(Wordmode)

x8 ( Bytemode) x16 ( Wordmode) x8 ( Bytemode) x16 ( Wordmode)

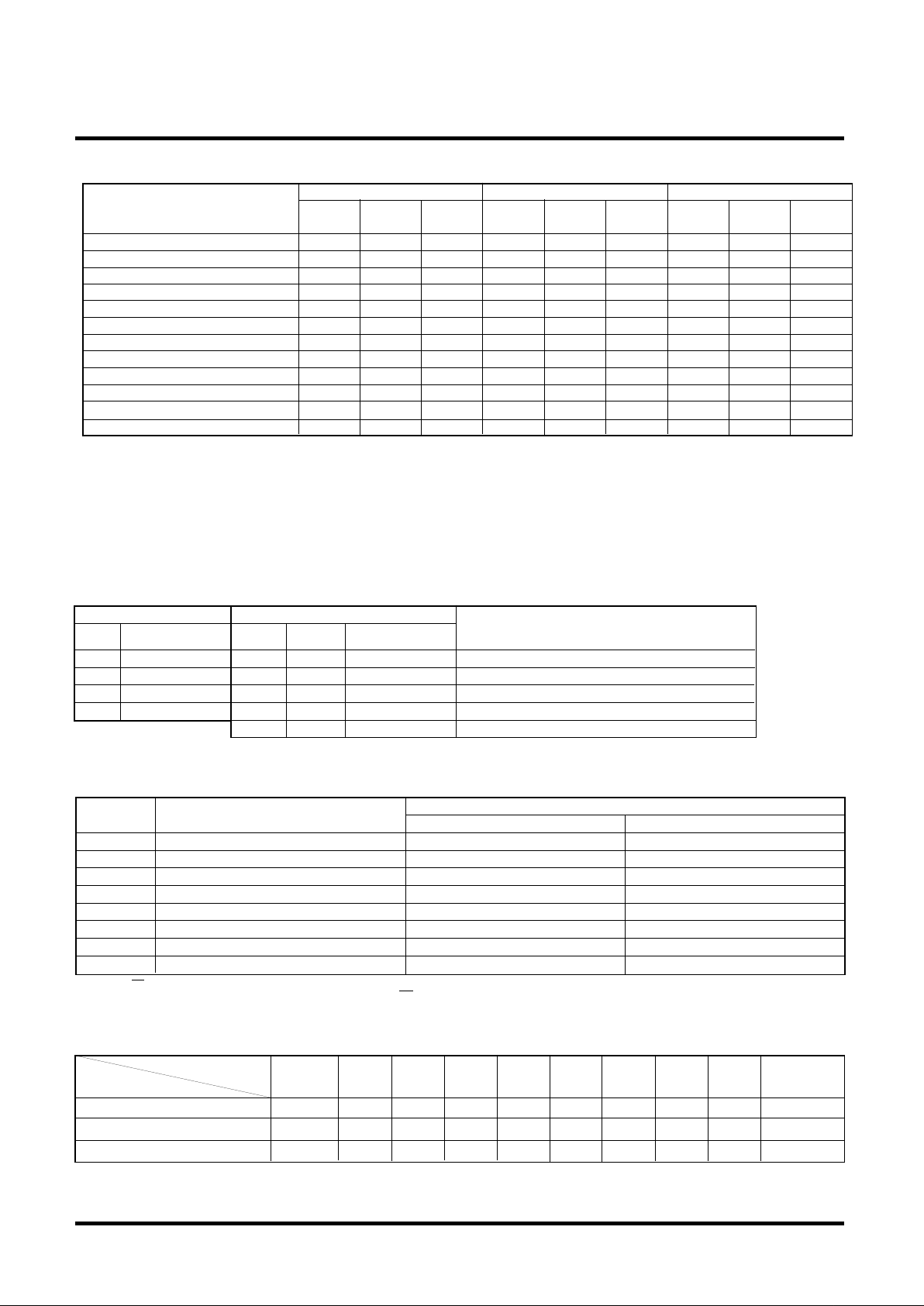

1)

Mode

Array

Status Register

Identifier Code

Stand by

Program

Erase

Write

Read

Pins

/CE /OE /WE

VIL

VIL

VIL

VIL

VIH

VIL

VIL

VIL

VIL

VIL

VIH

X

VIH

VIH

VIH

VIH

VIH

VIH

X

VIL

VIL

Data out

Status Register Data

Identifier Code

Hi-Z

Hi-Z

Command/Data in

Command

Output disable

Deep Power Down

Others

/RP

VIH

VIH

VIH

VIH

VIH

VIH

VIH

RY/BY

VOH (Hi-Z)

X

X

X

X

X

X

VIL VIH

X

VIL

X Hi-Z

VIH

VIL

XCommand

Bus Operations for Word-Wide Mode (/BYTE=VIH)

DQ0-15

2)

VIH

Lock Bit Status VIL VIL

VIH

Lock Bit Data (DQ6) X

VOH (Hi-Z)

VOH (Hi-Z)

1)

Mode

Array

Status Register

Identifier Code

Stand by

Program

Erase

Write

Read

Pins

/CE /OE /WE

DQ0-7

VIL

VIL

VIL

VIL

VIH

VIL

VIL

VIL

VIL

VIL

VIH

X

VIH

VIH

VIH

VIH

VIH

VIH

X

VIL

VIL

Data out

Status Register Data

Identifier Code

Hi-Z

Hi-Z

Command/Data in

Command

Output disable

Deep Power Down

Others

/RP

VIH

VIH

VIH

VIH

VIH

VIH

VIH

RY/BY

X

X

X

X

X

X

VIL

VIH

X

VIL

X Hi-Z

VIH

VIL

X

Command

Bus Operations for Byte-Wide Mode (BYTE=VIL)

2)

Lock Bit Status

VIL VIL

VIH

VIH

Lock Bit Data (DQ6)

X

VOH (Hi-Z)

VOH (Hi-Z)

VOH (Hi-Z)

MITSUBISHI LSIs

M5M29FB/T800FP,VP,RV-80,-10,-12

May 1997 , Rev.6.1

8,388,608-BIT (1048,576-WORD BY 8-BIT / 524,288-WORD BY16-BIT)

CMOS 3.3V-ONLY, BLOCK ERASE FLASH MEMORY

5

BLOCK LOCKING

D6 provides Lock Status of each block after writing the Read Lock Status command (71H).

In case of TSOP package, /WP pin must not be switched during performing Read / Write operations or WSM Busy (WSMS = 0).

/RP

/WP Lock Bit(Internally)

VIL

VHH

VIH

VIH

VIH

X

X

VIL

VIL

VIH

X

X

X

0

1

Write Protection Provided

All Blocks Locked (Deep Power Down Mode)

Blocks Locked (Depend on Lock Bit Data)

All Blocks UnLocked

Blocks Unlocked (Depend on Lock Bit Data)

All Blocks Unlocked

STATUS REGISTER

Status

Erase Status

Program Status

Definition

Symbol

(D5)

(D4)

Write State Machine Status

(D7)

(D6)

Reserved

(D1)

(D0)

(D3)

Reserved(D2)

"1" "0"

Ready Busy

Suspended Operation in Progress / Completed

Error Successful

Error Successful

- -

- -

SR.5

SR.4

SR.7

SR.6

SR.1

SR.0

SR.3

SR.2

Block Status after Program

Device Sleep Status

Device in Sleep

Suspend Status

DEVICE IDENTIFIER CODE

Code

Manufacturer Code

Pins

Hex. Data

1CH

D0

0

A0

VIL

D1

0

D2

1

D3

1

D4

1

D5

0

D6

0

D7

0

Device Code (-T)

5DH0VIH

1

1 1

1

0

1

0

Device Code (-B)

5EH

0VIH 11

1

10

1

0

In the word-wide mode, the same data as D7-0 is read out from D15-8.

A9 = VHH Mode : A9 = 11.5V~13.0V Set A9 to VHH min.200ns before falling edge of /CE in ready status. Min.200ns after return to VIH ,device can't be accessed.

A1~A8, A10~A18, /CE,/OE = VIL, /WE = VIH

D15/A-1 = VIL (/BYTE = L)

*The RY/BY is an open drain output pin and indicates status of the internal WSM. When low,it indicates that the WSM is Busy performing an operation.

A pull-up resistor of 10K-100K Ohms is required to allow the RY/BY signal to transition high indicating a Ready WSM condition.

Error Successful

Device Not in Sleep

*D3 indicates the block status after the page programming. When D3 is "1", the page has the over-programed cell . If over-program occures, the device is block

fail. However if D3 is "1", please try the block erase to the block. The block may revive.

SOFTWARE COMMAND DEFINITION

Command List

Read Array

FFHXWrite

3rd bus cycle1st bus cycle 2nd bus cycle

Command

AddressMode Data AddressMode Data AddressMode Data

Device Identifier

90H

XWrite

ID

IARead

Read Status Register

70HXWrite SRDXRead

Clear Status Register

50H

XWrite

Page Program XWrite

WD0

Write41H

XWrite

WA0

Write

WD1WA1Write

Block Erase / Confirm

20H

XWrite

D0H

BA

Write

Suspend

B0H

XWrite

Resume

71H

XWrite

2)

3)

5)

6)

4)

Read Lock Bit Status

Lock Bit Program / Confirm

Erase All Unlocked Blocks

Write

Write

X

X A7H

77H

D0H

Write

Read

BA

BA

X D0H

D0H

DQ6

2)

(D7-0)(D7-0)(D7-0)

1) In the word-wide mode, upper byte data (D8-D15) is ignored.

2) IA=ID Code Address : A0=VIL (Manufacturer's Code) : A0=VIH (Device Code), ID=ID Code,

/BYTE =VIL : A-1, A1-A18 = VIL, /BYTE =VIH : A1-A18 = VIL

3) SRD = Status Register Data

4) WA=Write Address, WD=Write Data.

/BYTE =VIL : Write Address and Write Data must be provided sequentially from 00H to FFH for A-1-A6.

Page size is 256Byte (256byte x 8bit), /BYTE =VIH : Write Address and Write Data must be provided

sequentially from 00H to 7FH for A0-A6. Page size is 128word (128word x 16bit).

5) BA = Block Address ( Addresses except Block Address mest be VIH.)

6) DQ6 provides Block Lock Status, DQ6 = 1 : Block Unlock, DQ6 = 0 : Block Locked.

7) Sleep command (F0H) put the device into the sleep mode after completing the current operation. The active current is reduced to deep power -down levels.

The Read Array command (FFH) must be written to get the device out of sleep mode.

4)

4)

Sleep

Write

X F0H

7)

/RP

VIL

VHH

VIH

VIH

Lock Bit(Internally)

X

X

0

1

SOP Package

TSOP Package

Loading...

Loading...