SONY KE-42TS2E, KE-42TS2E-2U Service Manual

KE-42TS2U/42TS2E

PANEL MODULE SERVICE MANUAL

UC Model

AEP Model

PDP Module Name |

UK Model |

|

|

FPF42C128127UB-73 |

HK Model |

|

|

FLAT PANEL COLOR TV

Contents

Outline

1.1 |

Out view |

|

|

1.2 |

Feature |

|

|

1.3 |

Specification |

|

|

1.3.1 |

Functional specification |

|

|

1.3.2 |

Display quality |

|

|

1.3.3 |

Interface specification |

|

|

Notes on safe handling of the plasma display

2.1 Notes to follow during servicing

Name and Function

3.1 Configuration

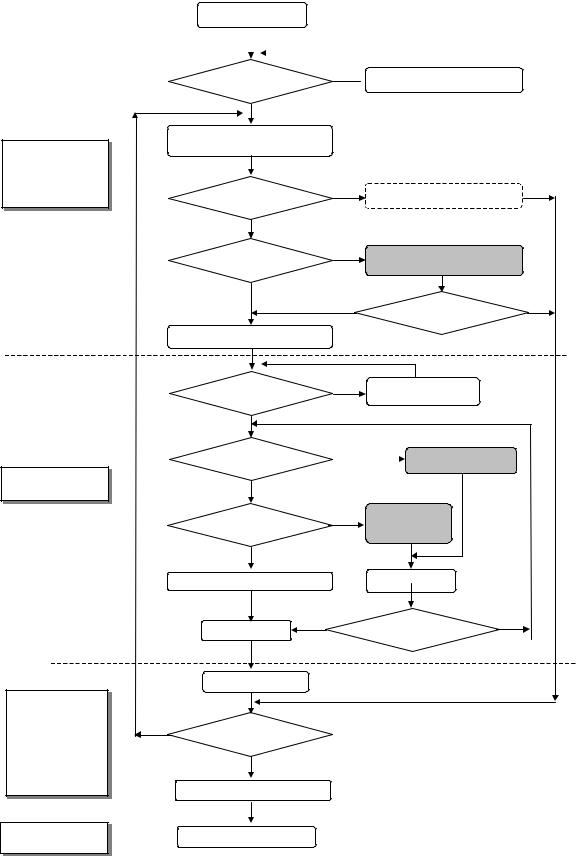

3.2Block Diagrams

3.2.1 Signal Diagrams

3.3.2Power Diagrams

3.3Function

3.5Protection function

Problem analysis

4.1 Outline of Repair Flow

4.2Outline of PDP Module Repair Flow

4.3Checking the Product Requested for Repair

4.4Operation Test Procedure

4.5Fault Symptom

4.6Failure analysis procedure

4.6.1 Procedure of no screen Power supply

4.6.2Vertical line Vertical bar analysis procedure

4.6.3Horizontal line Horizontal bar

4.7Failure Analysis Using a personal computer

4.7.1 Connection a Computer

4.7.2Preparation a Computer

4.7.3Problem Analysis procedure

DISASSEMBLE AND ASSEMBLING

5.1 Disassemble Diagrams

5.2X-SUS CIRCUIT BOARD REMOVING MANUAL

5.3Y-SUS CIRCUIT BOARD REMOVING MANUAL

5.4ADDRESS-BUS Left CIRCUIT BOARD REMOVING MANUAL

5.5ADDRESS-BUS Right CIRCUIT BOARD REMOVING MANUAL

5.6LOGIC CIRCUIT BOARD REMOVING MANUAL

5.7CIRCUIT BOARD REMOVING MANUAL

5.8Panel chassis Replacement Procedure

Checking and adjustment

6.1 Check Adjustment list

6.2Check Adjustment

6.2.1 Check Adjustment Procedure

6.2.2Parameter adjustment

6.2.3Operation and performance check

6.2.4Heat-running test

6.2.5LOGIC CIRCUIT BOARD Data transfer

6.2.6Accumulation time reset

6.2.7Shipment setting

The parts Information

Out line

The module is a plasma display module which can be designed in there is no fan in addition to a general feature of the plasma display such as a flat type, lightness, and high-viewing-angle and terrestrial magnetism.

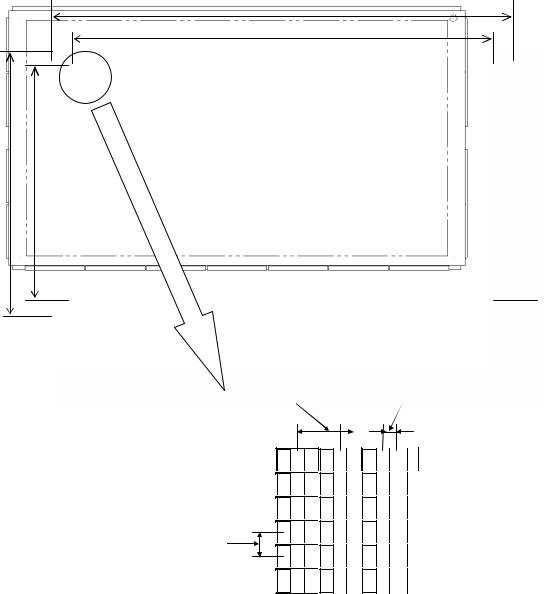

Out view

994

921.6

585 |

522.24 |

Pixel pitch(horizontal) |

Subpixel pitch(horizontal) |

0.90mm |

0.30mm |

Pixelpitch(Vertical) |

0.51 mm |

R G B R G B R G B

R G B R G B R G B

R G B R G B R G B

R G B R G B R G B

R G B R G B R G B

R G B R G B R G B

Feature

For high definition television by ALIS methodFor FAN Less design(Low consumption electric powerFlat type Lightness

Customizing of module equipped with communication function

1

Specification

Functional specification

|

Item |

NO |

|

Specification |

|

|

|

x |

x |

x |

|||

|

|

|

||||

Externals |

Module size |

1 |

994×585×66mm |

← |

← |

|

|

Weight |

2 |

18kg |

|

← |

← |

Display |

Display size |

3 |

921.60×522.24mm |

← |

← |

|

panel |

|

|

(42inch: 16:9) |

|

|

|

|

Resolution |

4 |

1024×1024 pixel |

← |

← |

|

|

Pixel pitch |

5 |

0.90(H)×0.51(V)mm |

← |

← |

|

|

Sub pixel pitch |

6 |

0.30(H)×0.51(V)mm |

← |

← |

|

Color |

Grayscale(standard) |

9 |

RGB each color |

← |

← |

|

|

|

|

256 Grayscale |

|

|

|

BrightNess |

White(display load |

11 |

140cd/ |

|

← |

|

|

Ratio 100%) |

|

|

|

|

|

|

White(display load |

12 |

700cd/ |

|

← |

(1000) cd/ |

|

Ratio 1%, standard) |

|

|

|

|

|

|

|

|

|

|

|

|

Chromaticity |

(x,y) white 10% |

14 |

(0.300,0.290) |

← |

(0.300,0.300) |

|

Coordinates |

|

|

|

|

|

|

Contrast |

Contrast in Darkroom 60Hz |

15 |

400:1 |

|

← |

(1000:1) |

Data signal |

Video signal |

16 |

LVDS(8bit) |

|

← |

← |

|

(RGB each color) |

|

|

|

|

|

|

Dot clock max |

17 |

52MHz |

|

← |

← |

|

|

|

|

|

|

|

Sync Signal |

Horizontal Sync Signal max |

18 |

50KHz(LVDS) |

|

← |

← |

|

Vertical Sync Signal |

19 |

50Hz±1.9 60±1.7Hz(LVDS) |

← |

← |

|

Powersupply |

Input voltage/current |

20 |

100-120/200-240VAC |

+3.3/+5/+75-90/+50 |

← |

|

|

|

|

4.5/2.0A |

50/60Hz |

-70VDC 0.05/6/4/2A |

|

|

Standby electric power max |

21 |

1W |

|

|

|

Noise |

Shade noise at 18dB(A) or |

22 |

25dB(A)orless |

← |

← |

|

|

less |

|

|

|

|

|

Guarantee |

Temperature(operation) |

23 |

0 45 |

|

← |

← |

environment |

Temperature(storage) |

24 |

0 45 |

|

← |

← |

|

Humidity(operation) |

25 |

20 85%RH(no condensation) |

← |

← |

|

|

Humidity(storage) |

26 |

20 80%RH(no condensation) |

← |

← |

|

It is made to give priority when there is a delivery specification according to the customer.

Display quality specification

|

|

|

|

|

|

|

|

|

Item |

NO |

Specification |

|

|

|

|

x |

x |

x |

||

|

|

|

|

|||

Non-lighting |

Total number subpixel |

1 |

15 or less |

← |

← |

|

cell defect |

Density subpixel/c |

2 |

2 or less |

← |

← |

|

|

|

|

|

However,1 continuousness or less |

|

|

|

|

Size H×V subpixel |

3 |

1×2 or less, Or 2×1 or less |

← |

← |

Non-extinguis |

Total number(subpixel) |

4 |

6 or less each color 2 or less |

← |

← |

|

hing |

cell |

Density subpixel/c |

5 |

Each color 2 cells max |

← |

← |

defect |

|

|

|

However,1 continuousness or less |

|

|

Flickering |

Flickering lighting cell |

6 |

5 or less |

← |

← |

|

cell defect |

defect sub pixel/c |

|

|

|

|

|

|

|

Flickering |

7 |

Number on inside of Non-extinguishing |

← |

← |

|

|

non-extinguishing cell |

|

cell defect |

|

|

|

|

defect |

|

|

|

|

High intensity |

Twice or more bright point |

8 |

|

← |

← |

|

cell defect |

|

|

|

|

|

|

Brightness |

White block of 10% load |

9 |

20 or less |

← |

← |

|

variation |

|

[9 point] |

|

|

|

|

|

|

In area adjacent 20mm |

10 |

10 or less |

← |

← |

|

|

[White] |

|

|

|

|

Color |

|

White block of 10% load |

11 |

Average±0.015 |

← |

← |

variation |

|

[9 point] |

|

Average±0.015 |

|

|

It is made to give priority when there is a delivery specification according to the customer.

2

Interface Specification

|

No |

|

|

Item |

|

|

Signal Name |

|

Number |

|

|

|

|

Form |

|

|

Content of definition |

|

|||||

|

|

|

|

|

|

of |

|

I/O |

|

|

|

|

|

||||||||||

|

. |

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

signals |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Differential serial data |

||||

|

|

|

|

|

|

|

|

RXIN0- |

1 |

|

|

|

|

|

|

|

|

signal. |

|

|

|

||

|

|

|

|

|

|

|

|

RXIN0+ |

1 |

|

|

|

|

|

|

|

|

Input video and timing |

|

|

|||

|

|

|

|

|

|

|

Reflection |

RXIN1- |

1 |

|

|

|

|

LVDS |

|

signals after differential |

|||||||

|

|

|

|

|

|

|

signal |

RXIN1+ |

1 |

|

Input |

|

Diff- |

|

serial conversion using a |

||||||||

|

|

|

|

|

|

|

Timing |

RXIN2- |

1 |

|

|

erent |

|

dedicated transceiver. |

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

Signal |

RXIN2+ |

1 |

|

|

|

|

ial |

|

The serial data signal is |

|||||||

|

|

|

|

|

|

|

|

RXIN3- |

1 |

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

transmitted seven times |

|

|

|||||

|

|

|

|

|

|

|

|

RXIN3+ |

1 |

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

faster than the base |

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

signal |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Differential clock |

|

|

||

|

|

|

Display |

|

|

|

|

|

|

|

|

|

|

|

|

|

signal. |

|

|

|

|||

|

|

data |

|

|

|

|

|

|

|

|

|

|

|

|

|

Input the clock signal |

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LVDS |

|

after differential |

|

|

||||

|

|

|

|

|

|

|

Clock |

RXCLKIN- |

1 |

|

Input |

|

Diff- |

|

conversion using a |

|

|

||||||

|

|

|

|

|

|

|

RXCLKIN+ |

1 |

|

|

erent |

|

dedicated transceiver. |

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ial |

|

The clock signal is |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

transmitted at the same |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

speed as the base |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

signal. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Low :LVDS receiver |

|

|

||

|

|

|

|

|

|

|

Power down |

PDWN |

1 |

|

Input |

|

LVTTL |

|

|

outputs are all L. |

|||||||

|

|

|

|

|

|

|

Signal |

|

|

|

High:Input signals are |

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

active. |

|

|

|

|

|

|

|

|

|

|

SDA |

1 |

|

I/O |

|

|

|

|

|

I2C bus serial data |

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

communication signal. |

|||||||||

|

|

|

|

|

|

|

Communication |

|

|

|

|

|

|

|

LVTTL |

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Communication with the |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

C) |

|

||||||||

|

|

|

|

|

|

|

|

SCL |

1 |

|

I/O |

|

(I |

|

control MPU of this |

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

product is enabled. |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Low |

power |

consumption |

||

|

|

|

|

|

|

|

|

CPUGO |

1 |

|

Input |

|

LVTTL |

|

mode of the control MPU |

||||||||

|

|

|

|

|

|

|

|

|

|

|

of |

this |

product |

is |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

released. |

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

“High” |

|

|

|

|||

|

|

|

|

Communi |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

This |

product |

is |

||||

|

|

|

|

cation/ |

|

|

PDPGO |

1 |

|

Input |

|

LVTTL |

|

||||||||||

|

|

|

|

|

|

|

|

|

started. |

|

|

|

|||||||||||

|

|

|

|

Control |

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(CPUGO=“High” Effective) |

||||||

|

|

|

|

|

|

|

Control |

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

It changes into "Low" → |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

"High" when this product |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

enters the undermentioned |

||||

|

|

|

|

|

|

|

|

IRQ |

1 |

|

Output |

|

LVTTL |

|

state. |

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

Vcc/Va/Vs output |

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

decrease |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Circuit abnormality |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

detection |

|

|

|

|

3

LVDS Signal Definition and Function

A video signal (display data signal and control signal) is converted from parallel data to serial data with the LVDS transmitter and further converted into four sets of differential signals before input to this product.

These signals are transmitted seven times faster than dot clock signals.

The dot clock signal is converted into one set of differential signals by the transmitter before input to this product.

The LVDS signal definition and function are summarized below:

|

Signal name |

|

Symbol |

|

Number of |

|

Signal definition and function |

|

|

|

|

|

signals |

|

|

|

|

|

RXIN0- |

|

|

|

Display data signal |

|

|

|

|

|

|

||

|

|

|

RXIN0+ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

RXIN1- |

|

|

|

Display data signal |

|

|

|

|

|

|

||

|

|

|

RXIN1+ |

|

|

|

|

|

Video signal |

|

|

|

|

|

|

|

Timing signal |

|

RXIN2- |

|

|

|

Display data signal Sync Signal Control signal |

|

Transmission line |

|

|

|

|

||

|

|

RXIN2+ |

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

RXIN3- |

|

|

|

Display data signal Control signal |

|

|

|

|

|

|

||

|

|

|

RXIN3+ |

|

|

|

|

|

|

|

|

|

|

|

|

|

Clock transmission line |

|

RXCLKIN- |

|

|

|

Clock signal |

|

|

|

|

|

|||

|

|

|

RXCLKIN+ |

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4

Video Signal Definition and Function

The table below summarizes the definitions and functions of input video signals before LVDS conversion.

|

|

|

|

|

|

|

|

|

|

Number |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Item |

|

|

Signal name |

|

|

of |

|

|

Input/ |

|

|

Signal definition and function |

|

|

|||||||||||||||

|

|

|

|

|

signal |

|

|

output |

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

s |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Original |

|

|

|

DATA-R |

8 |

|

|

|

|

|

Display data signal |

|

|||||||||||||||||

|

|

Video signal |

|

|

|

|

|

|

R7/G7/B7 is the highest intensity bit. |

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||

|

Display |

|

|

DATA-G |

8 |

|

|

Input |

|

|

||||||||||||||||||||

|

|

(digital RGB) |

|

|

|

|

R0/G0/B0 is the lowest intensity |

|

||||||||||||||||||||||

|

signal |

|

|

DATA-B |

8 |

|

|

|

|

|||||||||||||||||||||

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

bit. |

|

||||||||||||||||||||

|

(before |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Display data timing signal: Data are |

|

|||||||||||||||

|

LVDS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

Data Clock |

|

|

|

|

|

|

|

Input |

|

read when DCLK is low. DCLK is |

|

|||||||||||||||||

|

transmit |

|

|

DCLK |

|

|

|

|

||||||||||||||||||||||

|

|

|

|

|

|

continuously input. |

|

|||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

|

tance) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

Horizontal |

_____ |

|

|

|

|

|

|

|

|

|

Regulates one horizontal line of data: |

|

||||||||||||||

|

|

|

|

|

|

1 |

|

|

Input |

|

Begins control of the next screen when |

|

||||||||||||||||||

|

|

|

|

sync signal |

|

Hsync |

|

|

|

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

Hsync is lowered. |

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Screen starts up control timing signal |

|

|||||||||||||

|

|

|

|

Vertical sync |

_____ |

|

|

|

|

|

|

|

|

|

Begins control of the next screen whe |

|

||||||||||||||

|

|

|

|

|

|

1 |

|

|

Input |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

Vsync is lowered. |

|

|||||||||||||||||||||

|

|

|

|

signal |

|

Vsync |

|

|

|

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

Input the same frequency in both |

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

odd-numbered and even-numbered fields. |

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

This signal specifies the display |

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

field. |

|

|||||||||||||

|

|

|

|

Parity signal |

|

PARITY |

1 |

|

|

Input |

|

H: Odd-numbered field |

|

|||||||||||||||||

|

|

|

|

|

|

|

|

L: Even-numbered field |

|

|||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Parity signal should be alternated in |

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

every Vsync cycle. |

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Display period timing signal. |

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

H indicates the display period and L |

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

indicates the non display period. |

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Note: |

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Set this timing properly like |

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

followings, as is used internally for |

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

signal processing. |

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Set the blanking period so that the |

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

number of effective display data items |

|

|||||||||||||

|

|

|

|

Blanking |

|

|

|

|

|

|

|

|

|

|

|

in one horizontal period is 852. |

|

|||||||||||||

|

|

|

|

|

|

|

|

1 |

|

|

Input |

|

Set the number of blanking signals in |

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

signal |

|

BLANK |

|

|

|

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

one vertical period to 512, which is |

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

one half the number of effective scan |

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

lines. |

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

If the BLANK changes when the |

Vsync |

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

frequency is switched, the screen |

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

display may be disturbed or brightness |

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

may change. |

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

The screen display is restored to the |

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

normal state later when the BLANK |

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

length is constant again. |

|

|||||||||||||

This product does not correspond to the progressive display mode by the parity signal fixation. When the parity signal is fixed, this product is reversed arbitrarily internally and used.

5

Connector Specifications

The connector specification is shown below. Please do not connect anything with the terminal NC.

Signal connector CN1: DF13-20DP-1.25 V (tin-plated) (Maker: HIROSE DENKI)

Pin No. |

Signal name |

Pin No. |

Signal name |

|

|

|

|

|

|

|

|

1 |

RXIN0- |

2 |

GND |

|

|

|

|

3 |

RXIN0+ |

4 |

SCL |

|

|

|

|

5 |

RXIN1- |

6 |

GND |

|

|

|

|

7 |

RXIN1+ |

8 |

SDA |

|

|

|

|

9 |

RXIN2- |

10 |

GND |

|

|

|

|

11 |

RXIN2+ |

12 |

CPUGO |

|

|

|

|

13 |

RXCLKIN- |

14 |

PDPGO |

|

|

|

|

15 |

RXCLKIN+ |

16 |

IRQ |

|

|

|

|

17 |

RXIN3- |

18 |

PDWN |

|

|

|

|

19 |

RXIN3+ |

20 |

GND |

|

|

|

|

[Conforming connector] |

Housing: DF13-20DS-1.25C |

|

Contact: DF13-2630SCF |

Power Source Connectors Only UB-01 Type |

|

Power input connector |

Power supply output connector for system |

CN61:B06P-VH |

CN62:B03P-VH |

(Maker: JST) |

(Maker: JST) |

Pin No. |

Symbol |

|

|

|

AC(L) |

|

|

|

N.C |

|

|

|

AC(N) |

|

|

|

N.C |

|

|

|

N.C |

|

|

|

F.G |

|

|

Pin No. |

Symbol |

|

|

|

V |

|

N.C |

|

|

|

GND |

|

|

[Conforming connector]

Housing:VHR-03N(or M)

[Conforming connector] |

Contact:SVH-21T-P1.1 |

|

|

Housing:VHR-06N(or M) |

|

Contact:SVH-21T-P1.1 |

|

Power supply output connector for system CN63:B5B-XH-A

(Maker: JST)

Pin No. |

Symbol |

|

Vpr1 |

|

|

|

N.C. |

|

|

|

Vpr2 |

|

|

|

N.C. |

|

|

|

GND |

|

|

[Conforming connector]

Housing:XHP-5

Contact:SXH-001T-P0.6

6

Power Source Connectors |

|

|

|

(a)Power supply output |

(b)Power supply output |

(c)Power supply output |

|

connector for system |

connector for system |

connector for system |

|

CN6: B6B-PH-SM3-TB(JST)

Pin No. |

Symbol |

|

|

1 |

Vpr2 |

|

|

2 |

N.C. |

|

|

3 |

GND |

|

|

4 |

GND |

|

|

5 |

N.C. |

|

|

6 |

Vcc |

|

|

[Conforming connector] Housing PHR-6 Contact SPH-002T-P0.5L

(d)Power supply output connector for system

|

CN23: B10P-VH(JST) |

|

CN33: B9PS-VH(JST) |

|||

|

|

|

|

|

|

|

|

Pin No. |

Symbol |

|

Pin No. |

Symbol |

|

|

|

|

|

|

|

|

|

1 |

Va |

|

1 |

Vcc |

|

|

|

|

|

|

|

|

|

2 |

N.C. |

|

2 |

GND |

|

|

|

|

|

|

|

|

|

3 |

Vcc |

|

3 |

GND |

|

|

|

|

|

|

|

|

|

4 |

GND |

|

4 |

GND |

|

|

|

|

|

|

|

|

|

5 |

GND |

|

5 |

GND |

|

|

|

|

|

|

|

|

|

6 |

GND |

|

6 |

N.C. |

|

|

|

|

|

|

|

|

|

7 |

N.C. |

|

7 |

Vs |

|

|

|

|

|

|

|

|

|

8 |

Vs |

|

8 |

Vs |

|

|

|

|

|

|

|

|

|

9 |

Vs |

|

9 |

Vs |

|

|

|

|

|

|

|

|

|

10 |

Vs |

[Conforming connector] |

|||

|

|

|

||||

|

|

|

||||

[Conforming connector] |

|

Housing VHR-9N |

||||

|

Contact SVH-21T-P1.1 |

|||||

Housing VHR-10N |

|

|||||

Contact SVH-21T-P1.1 |

|

|

|

|

||

(e)Power supply output connector for system

CN42: S7B-PH-SM3-TB(JST) |

CN52: S7B-PH-SM3-TB(JST) |

||||

|

|

|

|

|

|

Pin No. |

Symbol |

|

Pin No. |

Symbol |

|

1 |

Va |

|

1 |

Va |

|

|

|

|

|

|

|

2 |

N.C. |

|

2 |

N.C. |

|

|

|

|

|

|

|

3 |

N.C. |

|

3 |

N.C. |

|

|

|

|

|

|

|

4 |

GND |

|

4 |

GND |

|

|

|

|

|

|

|

5 |

GND |

|

5 |

GND |

|

|

|

|

|

|

|

6 |

N.C. |

|

6 |

N.C. |

|

|

|

|

|

|

|

7 |

Vcc |

|

7 |

Vcc |

|

|

|

|

|

|

|

[Conforming connector] |

[Conforming connector] |

Housing PHR-7 |

Housing PHR-7 |

Contact SPH-002T-P0.5L |

Contact SPH-002T-P0.5L |

(f)Power supply output |

|

connector for system |

|

CN7: 00 6200 520 330 000 [ZIF Right Angle Connector](kyousera elco)

Pin No. |

Symbol |

Pin No. |

Symbol |

1 |

N.C. |

11 |

GND |

|

|

|

|

2 |

N.C. |

12 |

Vra |

|

|

|

|

3 |

N.C. |

13 |

GND |

|

|

|

|

4 |

N.C. |

14 |

Vrs |

|

|

|

|

5 |

GND |

15 |

GND |

|

|

|

|

6 |

VSAGO |

16 |

Iak |

|

|

|

|

7 |

GND |

17 |

GND |

|

|

|

|

8 |

VCEGO |

18 |

Vak |

|

|

|

|

9 |

GND |

19 |

GND |

|

|

|

|

10 |

PFCGO |

20 |

Vsk |

|

|

|

|

7

2.Notes on safe handling of the plasma display

2. 1 Notes to follow during servicing

The work procedures shown with the Note indication are important for ensuring the safety of the product and the servicing work. Be sure to follow these instructions.

Before starting the work, secure a sufficient working space.

At all times other than when adjusting and checking the product, be sure to turn OFF the main POWER switch and disconnect the power cable from the power source of the display (jig or the display itself) during servicing.

To prevent electric shock and breakage of PC board, start the servicing work at least 30 seconds after the main power has been turned off. Especially when installing and removing the power supply PC board and the SUS PC board in which high voltages are applied, start servicing at least 2 minutes after the main power has been turned off.

While the main power is on, do not touch any parts or circuits other than the ones specified.

The high voltage power supply block within the PDP module has a floating ground. If any connection other than the one specified is made between the measuring equipment and the high voltage power supply block, it can result in electric shock or activation of the leakage-detection circuit breaker.

When installing the PDP module in, and removing it from the packing carton, be sure to have at least two persons perform the work while being careful to ensure that the flexible printed-circuit cable of the PDP module does not get caught by the packing carton.

When the surface of the panel comes into contact with the cushioning materials, be sure to confirm that there is no foreign matter on top of the cushioning materials before the surface of the panel comes into contact with the cushioning materials. Failure to observe this precaution may result in the surface of the panel being scratched by foreign matter.

When handling the circuit PC board, be sure to remove static electricity from your body before handling the circuit PC board.

Be sure to handle the circuit PC board by holding the such large parts as the heat sink or transformer. Failure to observe this precaution may result in the occurrence of an abnormality in the soldered areas.

Do not stack the circuit PC boards.

Failure to observe this precaution may result in problems resulting from scratches on the parts, the deformation of parts, and short-circuits due to residual electric charge.

Routing of the wires and fixing them in position must be done in accordance with the original routing and fixing configuration when servicing is completed.

All the wires are routed far away from the areas that become hot (such as the heat sink). These wires are fixed in position with the wire clamps so that the wires do not move, thereby ensuring that they are not damaged and their materials do not deteriorate over long periods of time.

Therefore, route the cables and fix the cables to the original position and states using the wire clamps.

Perform a safety check when servicing is completed.

Verify that the peripherals of the serviced points have not undergone any deterioration during servicing. Also verify that the screws, parts and cables removed for servicing purposes have all been returned to their proper locations in accordance with the original setup.

8

Name and Function

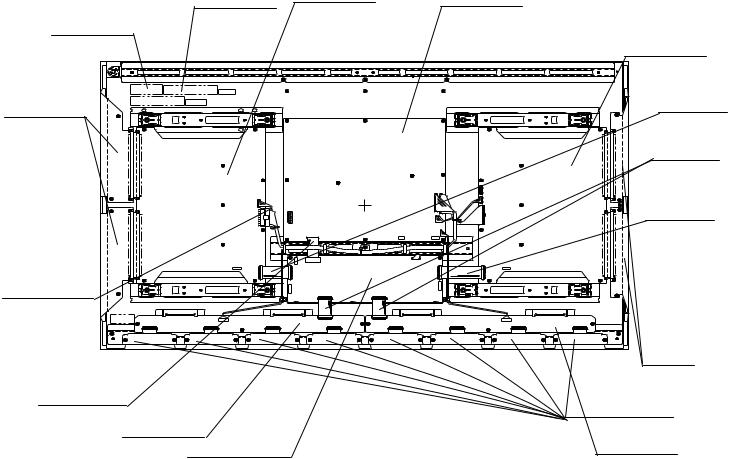

Configuration

|

Product label |

Y-SUS board |

PSU board *1 |

|

|

|||

|

|

|

|

|

|

|

||

Panel chassis |

|

|

|

|

|

|

|

|

Serial Id label |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

X-SUS board |

|

|

|

|

|

|

|

|

Signal |

Scan module |

|

|

|

|

|

|

|

cable |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Signal |

|

|

|

|

|

|

|

|

cable |

|

|

|

|

|

|

|

|

Signal |

|

|

|

|

|

|

|

|

cable |

Ps cable |

|

|

|

|

|

|

|

|

ADM1 |

ADM2 |

ADM3 |

ADM4 |

ADM5 |

ADM6 |

ADM7 |

ADM8 |

XBB |

|

||||||||

PSU |

|

|

|

|

|

|

|

|

Signal |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Address module(ADM) |

|

ABUSL board

LOGIC board |

ABUSR board |

|

The figure shows the article number in the parts information table of clause 7.

*1:Power supply(jig)

9

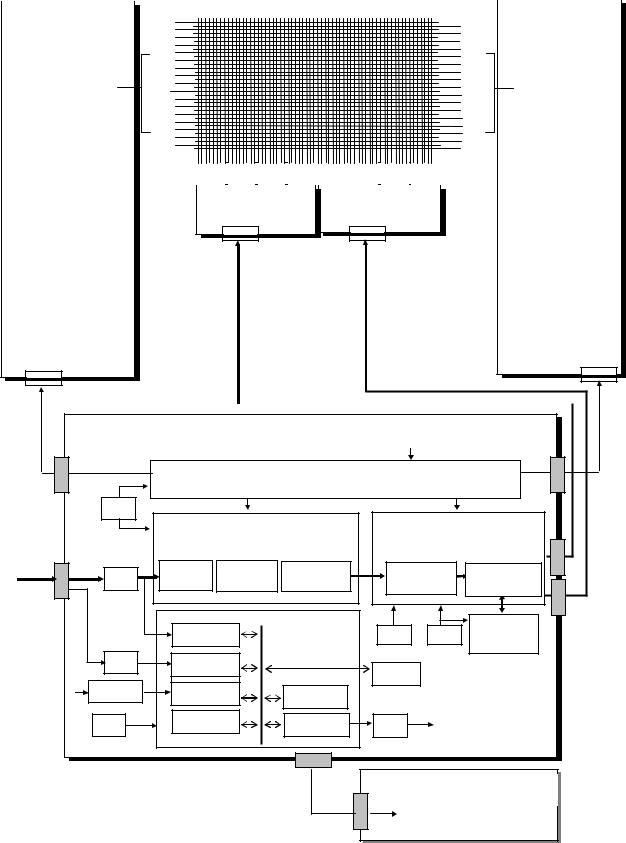

Block Diagrams

|

signal Diagrams |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

Y-SUS B. |

|

|

|

S |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

X |

|

|

|

X-SUS |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

X-SUS |

|

|

||

|

|

|

|

|

|

|

|

D |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

B |

|

|

|

|

|

||

|

|

Y-SUS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

EVEN SW |

|

|

|||||

|

|

EVEN SW |

|

|

|

M |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

B |

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

X-SCAN |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Y-SCAN |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

EVEN SW |

|

|

||

|

|

EVEN SW |

|

|

|

|

S |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

X |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

X-SUS |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

Y-SUS |

|

|

|

|

D |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

B |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ODD SW |

|

|

||||

|

|

ODD SW |

|

|

|

|

M |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

B |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

X-SCAN |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Y-SCAN |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ODD SW |

|

|

|

|

|

ODD SW |

|

|

|

|

|

|

|

ADM1 |

ADM2 |

ADM3 |

ADM4 |

ADM5 |

ADM6 |

ADM7 |

ADM8 |

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

ABUSL B |

|

ABUSR B. |

|

|

|

|

|

|

|

POS |

|

|

|||||||

|

|

POS /NEG |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

RESET |

|

|

|||

|

|

RESET SW |

|

|

|

|

|

|

|

|

CN51 |

|

CN41 |

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

CN31 |

CN21 |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LOGIC B. |

|

TIMMING |

||

|

|

|

|

|

|

|

|

|

|

|

|

CN3 |

|

|

CN2 |

SCAN CONTROLLER

|

OSC |

|

|

|

|

|

|

|

|

|

|

24MHz |

DATA PROCESSOR |

DATA CONVERTER |

|

||||||

|

|

|

||||||||

SIGNAL |

CN1 |

|

|

|

|

|

|

|

|

|

INPUT |

γ comp. |

RGB |

DITHER |

|

|

|

|

CN5 |

||

LVDS |

SUB FIELD |

MEMORY |

||||||||

|

|

|||||||||

|

|

GAIN |

/ERR |

|

PRC. |

|

CONTROLLER |

|

||

|

|

|

|

|

|

|

|

|

||

|

|

|

|

MPU |

|

|

|

|

CN4 |

|

|

|

V-SYNC cont. |

OSC |

|

OSC |

FRAME |

|

|||

|

|

|

|

MEMORY |

|

|||||

|

|

|

|

|

|

|

|

|

||

|

2C |

. |

|

|

40MHz |

80MHz |

|

|

||

|

|

|

EEPROM |

|

|

|

||||

|

|

|

|

|

|

|

|

|||

|

Analog Sw |

ailure DET. |

APC cont. |

|

|

Vrs |

|

|

||

|

|

|

|

|

|

|

|

|

||

|

OSC |

FLASH |

|

|

D/A |

|

Vra |

|

|

|

|

|

|

Vrw |

|

|

|||||

|

|

|

|

|

|

|||||

|

10MHz |

|

|

|

|

|

Vrx |

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

CN7 |

|

|

|

PSU B. |

|

|

|

|

|

|

|

CN69 |

|

|

*1 |

|

|

|

|

|

|

|

PFCgo |

|

|

|||

|

*1:Power supply(jig) |

|

|

Vsago |

|

|

|

|||

|

|

|

Vcego |

|

|

|

||||

|

|

|

|

10 |

|

|

|

|

|

|

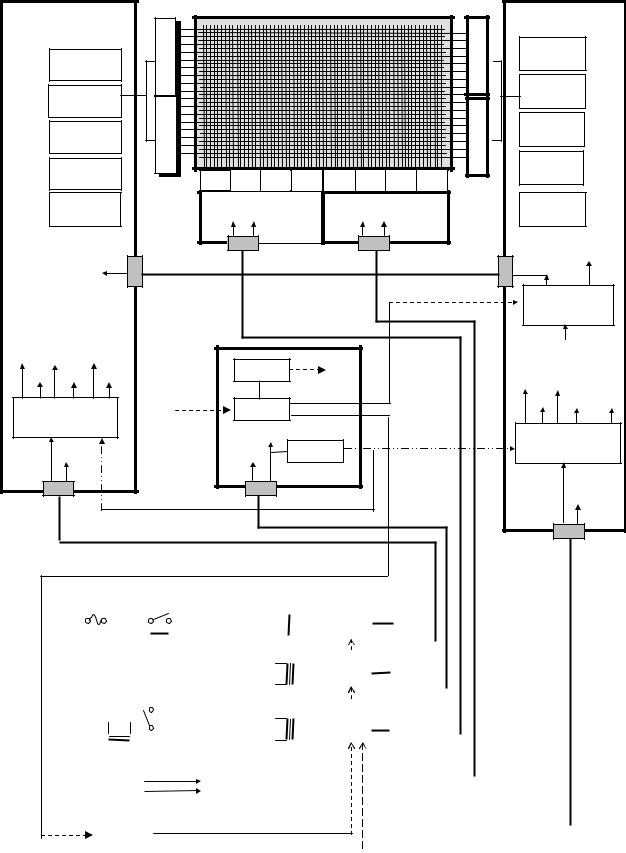

Power Diagrams |

|

|

|

|

|

|

|

|

|

|

|

||||

|

Y-SUS B. |

S |

|

|

|

|

|

|

|

X |

X-SUS |

|

|

||

|

|

|

|

|

|

|

|

|

|

X-SUS |

|

|

|||

|

Y-SUS |

D |

|

|

|

|

|

|

|

B |

|

|

|||

|

|

|

|

|

|

|

|

EVEN SW |

|

||||||

|

EVEN SW |

M |

|

|

|

|

|

|

|

B |

|

||||

|

Y-SCAN |

|

|

|

|

|

|

|

|

|

X-SCAN |

|

|||

|

|

|

|

|

|

|

|

|

|

EVEN SW |

|

||||

|

EVEN SW |

S |

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

X |

|

|

|

|

|||

|

Y-SUS |

|

|

|

|

|

|

|

X-SUS |

|

|

||||

|

D |

|

|

|

|

|

|

|

B |

ODD SW |

|

||||

|

ODD SW |

M |

|

|

|

|

|

|

|

B |

|

||||

|

Y-SCAN |

|

|

|

|

|

|

|

|

|

X-SCAN |

|

|||

|

|

|

|

|

|

|

|

|

|

ODD SW |

|

||||

|

ODD SW |

ADM1 |

ADM2 ADM3 |

ADM4 ADM5 |

ADM6 |

ADM7 |

ADM8 |

|

|||||||

|

POS/NEG |

|

|

ABUSL B |

|

|

|

ABUSR B. |

POS |

|

|

||||

|

RESET SW |

Vcc 5V |

Va 60V |

|

Vcc 5V |

Va 60V |

|

RESET SW |

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

Va |

|

|

Vx |

|

|

|

|

|

|

CN52 |

|

|

|

|

CN42 |

|

|

|

|

|

|

Vw |

180V |

CN32 |

|

|

|

|

|

CN22 |

|

|

45V |

|

||

|

Vb |

–5V |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

Vxwgo |

|

DC/DC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

CONVERTER |

|

||

YFVCC1 YFVCC2 |

FVE5H |

|

|

|

|

|

|

|

|

|

|

Vs 60V |

|

||

5V |

5V |

18V |

|

|

|

|

Vra |

|

|

|

|

|

|

|

|

YFVE1 |

YFVE2 |

VE |

|

|

D/A |

|

Vrs |

|

|

|

|

XFVCC1 |

XFVCC2 |

|

|

18V |

18V |

17V |

|

|

|

Vrw |

|

|

|

|

|

||||

CPUgo |

|

|

|

|

|

|

|

5V |

5V |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

Vrx |

|

|

|

|

XFVE1 |

XFVE2 |

VE |

||

|

|

|

PDPgo |

|

|

|

|

|

|

|

|||||

DC/DC |

|

|

|

|

|

|

|

|

|

18V |

|

18V |

17V |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

CONVERTER |

|

|

Vcc 5V |

|

|

|

|

|

|

|

DC/DC |

|

|||

|

|

|

|

|

|

|

|

|

|

RST |

|

|

|||

|

|

|

|

|

|

rst |

|

|

|

|

CONVERTER |

|

|||

Vcc 5V |

Vs 80V |

|

|

Vpr2 3.3V |

|

|

|

|

|

|

|||||

|

|

|

|

|

LOGIC B. |

|

|

|

Vcc 5V |

|

|

||||

CN33 |

|

|

|

|

CN6 |

|

|

|

|

|

|

|

Vs 80V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CN23 |

|

|

|

|

|

10A |

|

|

|

|

|

|

|

|

|

380V |

|

|

|

|

|

|

|

|

|

55V |

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

PFC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Va |

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

AC100 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

240V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CN61 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Vsago |

|

|

|

CN65 |

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

5V |

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Vcc |

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Servce |

|

|

|

|

|

|

|

|

|

|

|

|

Vcego |

80V |

|

|

CN68 |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SW |

|

|

|

|

|

|

|

|

|

|

|

|

Vs |

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

PFCgo |

Vpr2 |

3.3V |

|

|

|

CN67 |

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

5/3.3V |

|

|

|

|

|

|

|

|

|

CN66 |

|||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

Vsago |

Vpr1 |

|

5V |

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

control |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CN64 |

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

PFCgo |

|

|

|

|

|