Texas Instruments AM26C32QD, AM26C32MWB, AM26C32MJB, AM26C32MFKB, AM26C32IN Datasheet

...

|

AM26C32C, AM26C32I, AM26C32M |

||||||||

|

QUADRUPLE DIFFERENTIAL LINE RECEIVERS |

||||||||

|

SLLS104F ± DECEMBER 1990 ± REVISED APRIL 1998 |

||||||||

|

|

|

|

|

|

|

|

||

D Meet or Exceed the Requirements of ANSI |

AM26C32C, AM26C32I . . . D OR N PACKAGE |

||||||||

EIA/TIA-422-B, EIA/TIA-423-B, and ITU |

AM26C32M . . . J OR W PACKAGE |

||||||||

Recommendation V.10 and V.11 |

|

|

(TOP VIEW) |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

D Low Power, ICC = 10 mA Typ |

1B |

|

1 |

16 |

|

|

VCC |

||

|

|

|

|||||||

D ± 7-V Common-Mode Range With ± 200-mV |

1A |

|

2 |

15 |

|

|

4B |

||

Sensitivity |

1Y |

|

3 |

14 |

|

|

4A |

||

D Input Hysteresis . . . 60 mV Typ |

G |

|

4 |

13 |

|

|

4Y |

||

D tpd = 17 ns Typ |

2Y |

|

5 |

12 |

|

|

G |

|

|

2A |

|

6 |

11 |

|

|

3Y |

|||

D Operate From a Single 5-V Supply |

|

|

|

|

|

|

|

|

|

2B |

|

7 |

10 |

|

|

3A |

|||

D 3-State Outputs |

|

|

|

||||||

GND |

|

8 |

9 |

|

|

3B |

|||

|

|

|

|||||||

DInput Fail-Safe Circuitry

DImproved Replacements for AM26LS32

|

FK PACKAGE |

description |

(TOP VIEW) |

|

The AM26C32C, AM26C32I, and AM26C32M are quadruple differential line receivers for balanced or unbalanced digital data transmission. The enable function is common to all four receivers and offers a choice of active-high or active-low input. The 3-state outputs permit connection directly to a bus-organized system. Fail-safe design specifies that if the inputs are open, the outputs are always high.

The AM26C32 is manufactured using a BiCMOS process, which is a combination of bipolar and CMOS transistors. This process provides the high voltage and current of bipolar with the low power of CMOS to reduce the power consumption to about one-fifth that of the standard AM26LS32 while maintaining ac and dc performance.

|

1A |

1B |

NC |

CC |

4B |

|

|

V |

|

||||

1Y |

3 |

2 |

1 |

20 19 |

4A |

|

4 |

|

|

|

18 |

||

G |

5 |

|

|

|

17 |

4Y |

NC |

6 |

|

|

|

16 |

NC |

2Y |

7 |

|

|

|

15 |

G |

2A |

8 |

|

|

|

14 |

3Y |

|

9 |

10 11 12 13 |

|

|||

|

2B |

GND |

NC |

3B |

3A |

|

NC ± No internal connection

The AM26C32C is characterized for operation from 0°C to 70°C. The AM26C32I is characterized for operation from ±40°C to 85°C. The AM26C32M is characterized for operation from ±55°C to 125°C.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright 1998, Texas Instruments Incorporated

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

1 |

AM26C32C, AM26C32I, AM26C32M QUADRUPLE DIFFERENTIAL LINE RECEIVERS

SLLS104F ± DECEMBER 1990 ± REVISED APRIL 1998

FUNCTION TABLE (each receiver)

DIFFERENTIAL |

ENABLES |

OUTPUT |

|||

INPUT |

|

|

|

||

G |

G |

||||

|

|||||

|

|

||||

|

|

|

|

||

VID ≥ VIT+ |

H |

X |

H |

||

X |

L |

H |

|||

|

|||||

|

|

|

|

||

VIT± < VID < VIT+ |

H |

X |

? |

||

X |

L |

? |

|||

|

|||||

|

|

|

|

||

VID ≤ VIT± |

H |

X |

L |

||

X |

L |

L |

|||

|

|||||

|

|

|

|

||

X |

L |

H |

Z |

||

|

|

|

|

|

|

H = high level, L = low level, X = irrelevant

Z = high impedance (off), ? = indeterminate

logic symbol²

|

G |

4 |

|

≥ 1 |

EN |

|

|

||||

|

12 |

|

|

||||||||

|

|

|

|

|

|

|

|

|

|||

G |

|

||||||||||

|

|

|

|

|

|

|

|

||||

2 |

|

|

|

|

|

|

|

|

|||

1A |

|

|

|

|

|

|

3 |

1Y |

|||

|

|

|

|

|

|

||||||

|

|

|

|

|

|

||||||

|

|

|

|

|

|

||||||

|

|

|

|

|

|

||||||

1B |

1 |

|

|

|

|

||||||

|

|

|

|

|

|

|

|

||||

2A |

6 |

|

|

|

|

|

|

5 |

2Y |

||

|

|

|

|

|

|

||||||

2B |

7 |

|

|

|

|

||||||

|

|

|

|

|

|

|

|

||||

3A |

10 |

|

|

|

|

11 |

3Y |

||||

|

|

|

|

||||||||

3B |

9 |

|

|

|

|

|

|

|

|

||

4A |

14 |

|

|

|

|

13 |

4Y |

||||

|

|

|

|

|

|

||||||

4B |

15 |

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

||||

² This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

Pin numbers shown are for the D, J, N, and W packages.

2 |

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

AM26C32C, AM26C32I, AM26C32M

QUADRUPLE DIFFERENTIAL LINE RECEIVERS

SLLS104F ± DECEMBER 1990 ± REVISED APRIL 1998

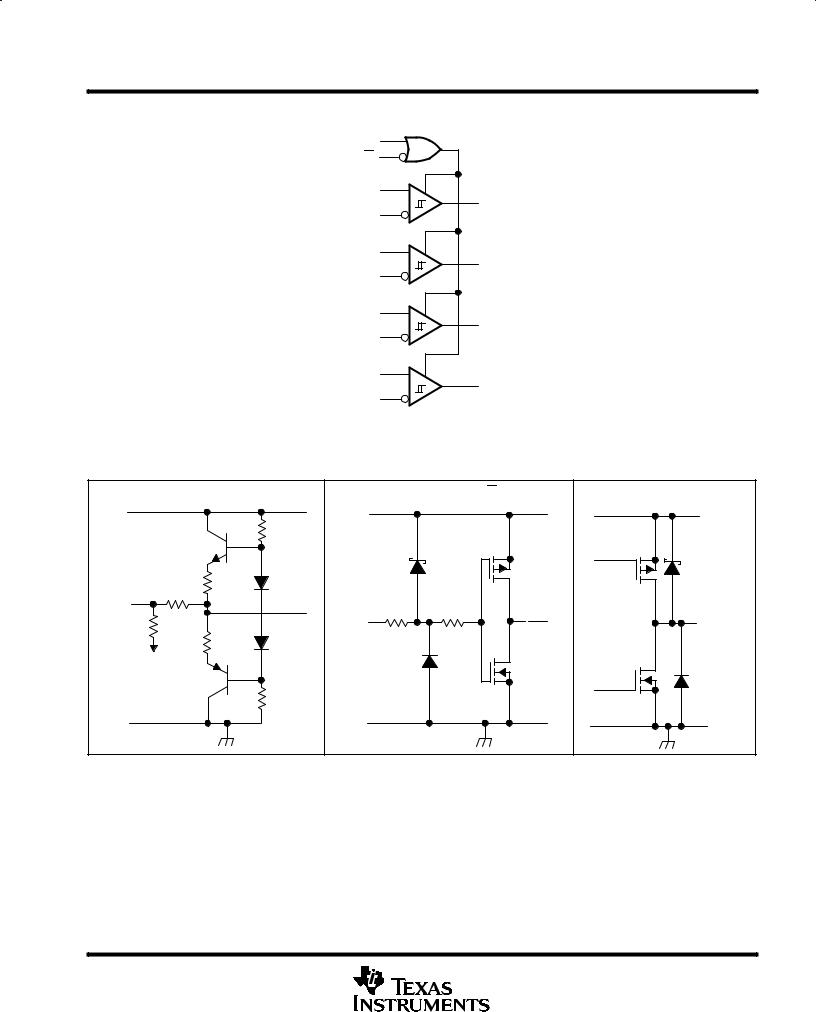

logic diagram (positive logic)

G |

4 |

|

|

G |

12 |

|

|

1A |

2 |

3 |

1Y |

|

1 |

||

|

|

||

1B |

|

|

|

2A |

6 |

5 |

2Y |

|

7 |

||

|

|

||

2B |

|

|

|

3A |

10 |

11 |

|

|

9 |

3Y |

|

3B |

|

||

|

|

4A 14

13 4Y

4B 15

Pin numbers shown are for the D, J, N, and W packages.

schematics

EQUIVALENT OF A OR B INPUT

VCC

17 kΩ |

1.7 kΩ |

|

NOM |

||

NOM |

||

|

||

Input |

|

|

288 kΩ |

|

|

NOM |

1.7 kΩ |

|

VCC(A) |

NOM |

|

|

||

or |

|

|

GND(B) |

|

|

GND |

|

EQUIVALENT OF G OR G INPUT

VCC

Input

GND

TYPICAL OF ALL OUTPUTS

VCC |

Output |

GND |

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

3 |

Loading...

Loading...