Texas Instruments 74ACT11139PWR, 74ACT11139PWLE, 74ACT11139N, 74ACT11139DR, 74ACT11139D Datasheet

74ACT11139 DUAL 2-LINE TO 4-LINE DECODER/DEMULTIPLEXER

SCAS175A ± SEPTEMBER 1991 ± REVISED APRIL 1996

DInputs Are TTL-Voltage Compatible

DDesigned Specifically for High-Speed Memory Decoders and Data Transmission Systems

DIncorporates Two Enable Inputs to Simplify Cascading and/or Data Reception

DFully Synchronous Operation for Counting

DCenter-Pin VCC and GND Configurations Minimize High-Speed Switching Noise

DEPIC (Enhanced-Performance Implanted CMOS) 1- m Process

D, N, OR PW PACKAGE

(TOP VIEW)

1Y1 |

|

1 |

16 |

|

1Y0 |

||

|

|

||||||

1Y2 |

|

2 |

15 |

|

1A |

||

|

|

||||||

1Y3 |

|

3 |

14 |

|

1B |

||

|

|

||||||

|

|

|

|

|

|

|

|

GND |

|

4 |

13 |

|

1G |

|

|

2Y0 |

|

5 |

12 |

|

VCC |

||

|

|

||||||

|

|

|

|

||||

2Y1 |

|

6 |

11 |

|

2G |

||

2Y2 |

|

7 |

10 |

|

2A |

||

|

|

||||||

2Y3 |

|

8 |

9 |

|

2B |

||

|

|

||||||

|

|

|

|

|

|

|

|

D500-mA Typical Latch-Up Immunity at

125°C

DPackage Options Include Plastic Small-Outline (D) and Thin Shrink Small-Outline (PW) Packages, and Standard Plastic 300-mil DIPs (N)

description

The 74ACT11139 is designed for use in high-performance memory-decoding or data-routing applications that require very short propagation delay times. In high-performance memory systems, this decoder is used to minimize the effects of system decoding.

The 74ACT11139 is composed of two individual 2-line to 4-line decoders in a single package. The active-low enables (1G or 2G) can be used as data lines in demultiplexing applications. This decoder/demultiplexer features fully buffered inputs, each of which represents only one normalized load to its driving circuit.

The 74ACT11139 is characterized for operation from ±40°C to 85°C.

FUNCTION TABLE

|

|

INPUTS |

|

|

OUTPUTS |

|

|

|

|

|

|

|

|

|

|

|

|

B |

A |

Y0 |

Y1 |

Y2 |

Y3 |

|

G |

||||||

|

|

|

|

|

|

|

|

|

H |

X |

X |

H |

H |

H |

H |

|

L |

L |

L |

L |

H |

H |

H |

|

L |

L |

H |

H |

L |

H |

H |

|

L |

H |

L |

H |

H |

L |

H |

|

L |

H |

H |

H |

H |

H |

L |

|

|

|

|

|

|

|

|

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

EPIC is a trademark of Texas Instruments Incorporated.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright 1996, Texas Instruments Incorporated

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

1 |

74ACT11139

DUAL 2-LINE TO 4-LINE DECODER/DEMULTIPLEXER

SCAS175A ± SEPTEMBER 1991 ± REVISED APRIL 1996

logic symbol²

15 |

|

DMUX |

0 |

16 |

|||||

|

|

|

|

1Y0 |

|||||

1A |

|

1 |

|

0 |

|

|

1 |

||

|

|

||||||||

14 |

|

G |

|

|

1 |

1Y1 |

|||

|

3 |

|

|||||||

1B |

2 |

|

|

|

|

2 |

|||

|

|

13 |

|

|

|

|

2 |

1Y2 |

|

1G |

|

|

|

|

|

|

3 |

3 |

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

1Y3 |

|

10 |

|

|

|

|

|

5 |

|||

|

|

|

|

|

|||||

|

|

|

|

|

2Y0 |

||||

2A |

|

|

|

|

|

|

6 |

||

|

|

|

|

|

|

||||

9 |

|

|

|

|

|

2Y1 |

|||

2B |

|

|

|

|

|

7 |

|||

|

|

11 |

|

|

|

|

|

2Y2 |

|

2G |

|

|

|

|

|

|

|

8 |

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

2Y3 |

|

|

|

|

|

|

|

|

|

|

² This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

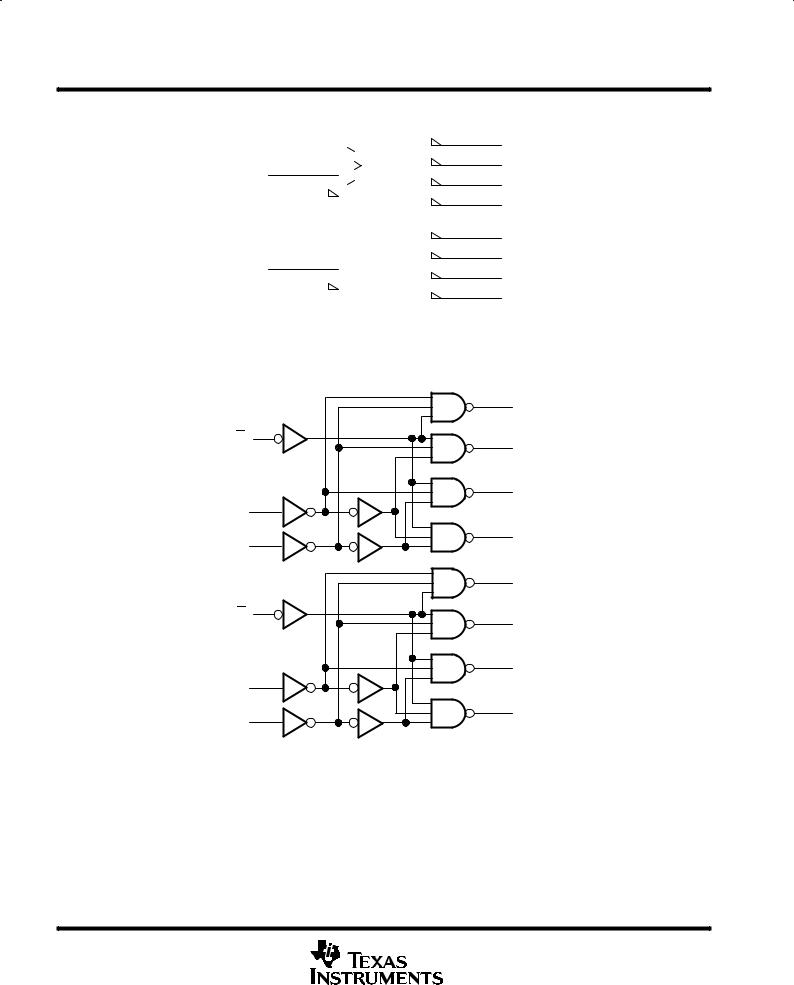

logic diagram (positive logic)

|

|

16 |

|

|

1Y0 |

1G |

13 |

1 |

|

||

|

|

|

|

|

1Y1 |

|

|

2 |

|

15 |

1Y2 |

1A |

|

|

|

|

|

|

14 |

3 |

1B |

1Y3 |

|

|

|

|

|

|

5 |

|

|

2Y0 |

2G |

11 |

6 |

|

||

|

|

|

|

|

2Y1 |

|

|

7 |

|

10 |

2Y2 |

2A |

|

|

|

|

|

|

9 |

8 |

2B |

2Y3 |

|

|

|

2 |

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

Loading...

Loading...