Philips HEF4094BU, HEF4094BTS, HEF4094BT, HEF4094BPB, HEF4094BP Datasheet

...

DATA SH EET

Product specification

File under Integrated Circuits, IC04

January 1995

INTEGRATED CIRCUITS

HEF4094B

MSI

8-stage shift-and-store bus register

For a complete data sheet, please also download:

•The IC04 LOCMOS HE4000B Logic

Family Specifications HEF, HEC

•The IC04 LOCMOS HE4000B Logic

Package Outlines/Information HEF, HEC

January 1995 2

Philips Semiconductors Product specification

8-stage shift-and-store bus register

HEF4094B

MSI

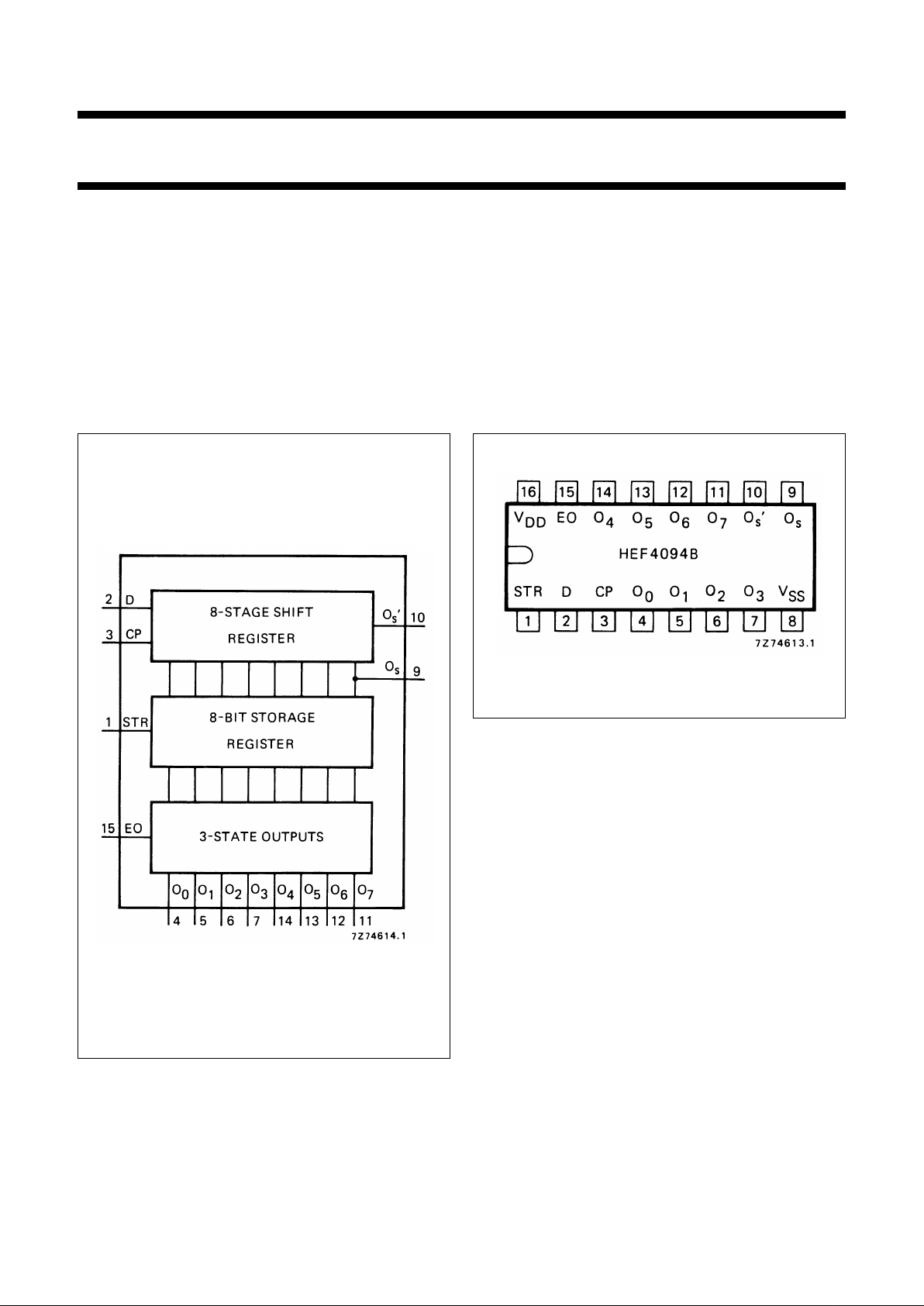

DESCRIPTION

The HEF4094B is an 8-stage serial shift register having a

storage latch associated with each stage for strobing data

from the serial input to parallel buffered 3-state outputs

O

0

to O

7

. The parallel outputs may be connected directly

to common bus lines. Data is shifted on positive-going

clock transitions. The data in each shift register stage is

transferred to the storage register when the strobe (STR)

input is HIGH. Data in the storage register appears at the

outputs whenever the output enable (EO) signal is HIGH.

Two serial outputs (O

s

and O’

s

) are available for cascading

a number of HEF4094B devices. Data is available at O

s

on

positive-going clock edges to allow high-speed operation

in cascaded systems in which the clock rise time is fast.

The same serial information is available at O’

s

on the next

negative-going clock edge and provides cascading

HEF4094B devices when the clock rise time is slow.

Fig.1 Functional diagram.

PINNING

FAMILY DATA, I

DD

LIMITS category MSI

See Family Specifications

HEF4094BP(N): 16-lead DIL; plastic

(SOT38-1)

HEF4094BD(F): 16-lead DIL; ceramic (cerdip)

(SOT74)

HEF4094BT(D): 16-lead SO; plastic

(SOT109-1)

( ): Package Designator North America

D data input EO output enable input

CP clock input O

s

, O’

s

serial outputs

STR strobe input O

0

to O

7

parallel outputs

Fig.2 Pinning diagram.

January 1995 3

Philips Semiconductors Product specification

8-stage shift-and-store bus register

HEF4094B

MSI

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

_white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader. white to force landscape pages to be ...

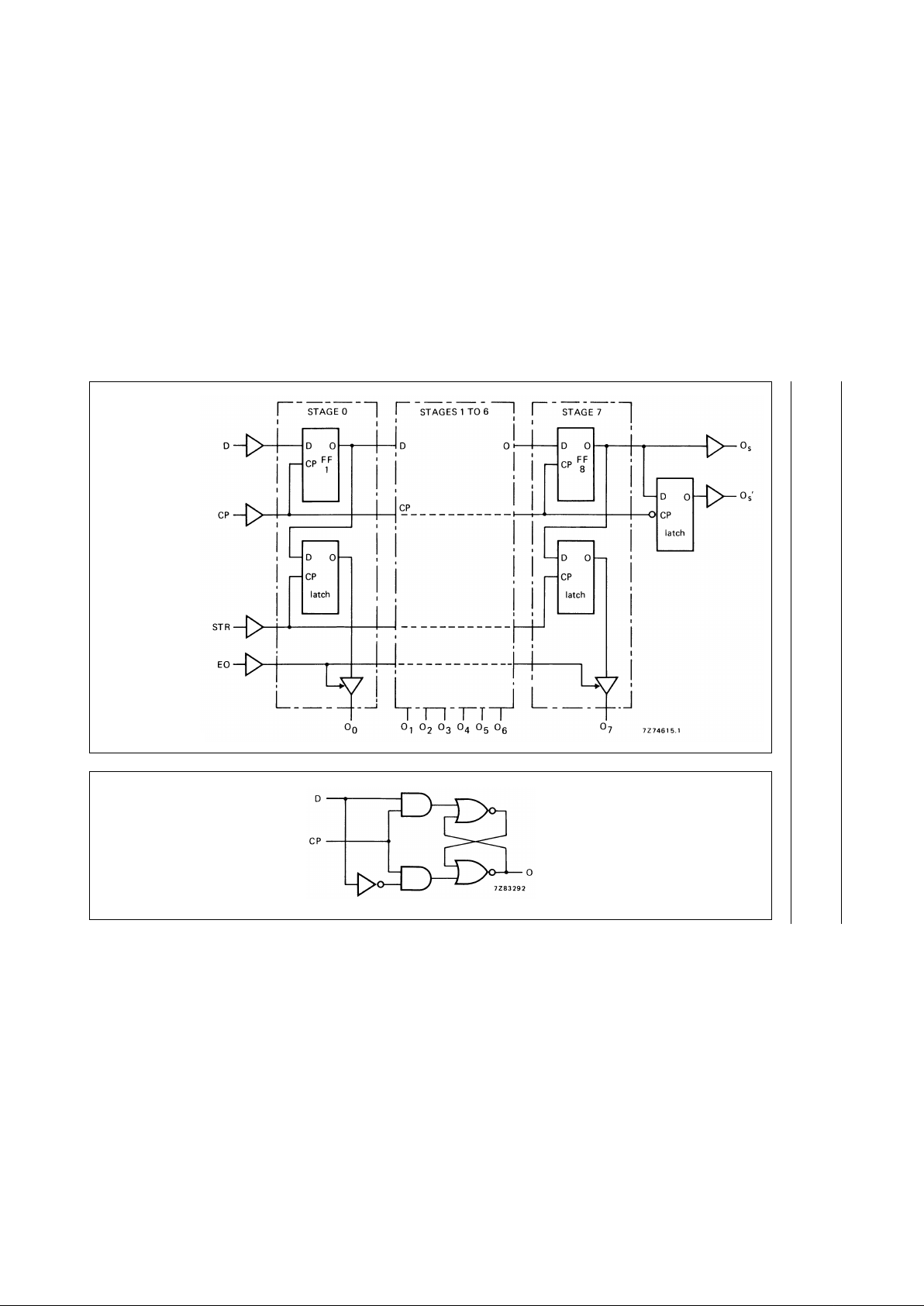

Fig.3 Logic diagram.

Fig.4 One D-latch.

Loading...

Loading...