Philips HEF4053BU, HEF4053BT, HEF4053BPB, HEF4053BP, HEF4053BD Datasheet

INTEGRATED CIRCUITS

DATA SHEET

For a complete data sheet, please also download:

∙The IC04 LOCMOS HE4000B Logic Family Specifications HEF, HEC

∙The IC04 LOCMOS HE4000B Logic Package Outlines/Information HEF, HEC

HEF4053B MSI

Triple 2-channel analogue multiplexer/demultiplexer

Product specification |

|

January 1995 |

|||||

File under Integrated Circuits, IC04 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Philips Semiconductors |

Product specification |

|

|

Triple 2-channel analogue |

HEF4053B |

multiplexer/demultiplexer |

MSI |

|

|

|

|

DESCRIPTION

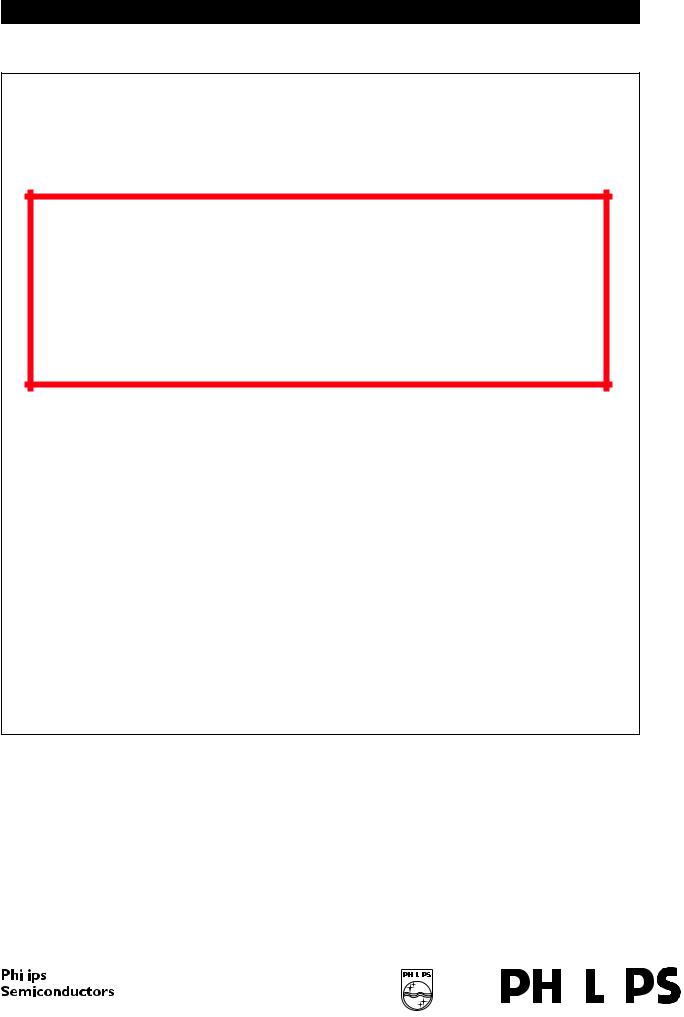

The HEF4053B is a triple 2-channel analogue multiplexer/demultiplexer with a common enable input (E). Each multiplexer/demultiplexer has two independent inputs/outputs (Y0 and Y1), a common input/output (Z), and select inputs (Sn). Each also contains two-bidirectional analogue switches, each with one side connected to an independent input/output (Y0 and Y1) and the other side connected to a common input/output (Z).

With E LOW, one of the two switches is selected (low impedance ON-state) by Sn. With E HIGH, all switches are in the high impedance OFF-state, independent of SA to SC.

VDD and VSS are the supply voltage connections for the

digital control inputs (SA to SC and E).

The VDD to VSS range is 3 to 15 V. The analogue inputs/outputs (Y0, Y1 and Z) can swing between VDD as a

positive limit and VEE as a negative limit. VDD−VEE may not exceed 15 V.

For operation as a digital multiplexer/demultiplexer, VEE is connected to VSS (typically ground).

Fig.1 Functional diagram.

FAMILY DATA, IDD LIMITS category MSI

See Family Specifications

January 1995 |

2 |

Philips Semiconductors |

Product specification |

|

|

Triple 2-channel analogue |

HEF4053B |

multiplexer/demultiplexer |

MSI |

|

|

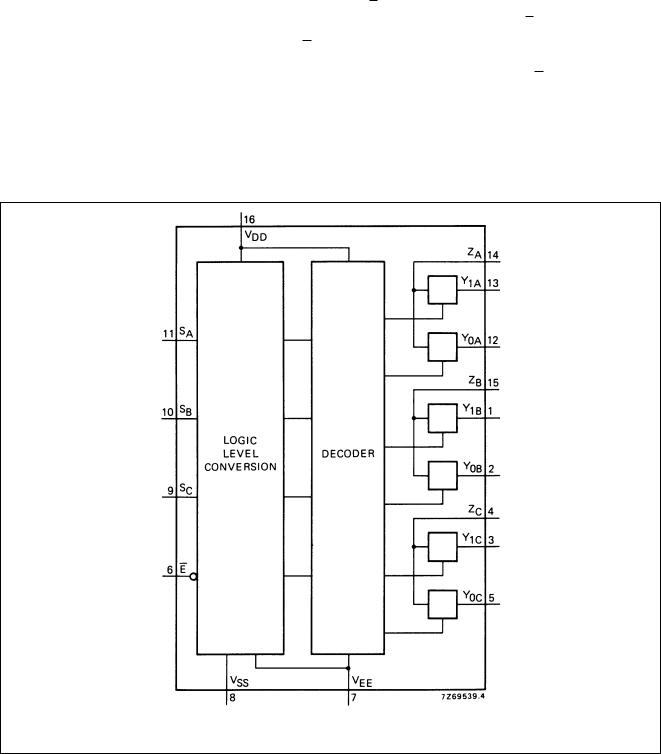

Fig.2 Pinning diagram.

HEF4053BP(N): 16-lead DIL; plastic

(SOT38-1)

HEF4053BD(F): 16-lead DIL; ceramic (cerdip)

(SOT74)

HEF4053BT(D): 16-lead SO; plastic

(SOT109-1)

( ): Package Designator North America

PINNING |

|

|

|

|||||

|

Y0A to Y0C |

independent inputs/outputs |

||||||

|

Y1A to Y1C |

independent inputs/outputs |

||||||

|

SA to SC |

select inputs |

|

|||||

|

|

|

|

|

enable input (active LOW) |

|||

|

E |

|

|

|

|

|||

|

ZA to ZC |

common inputs/outputs |

||||||

FUNCTION TABLE |

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

INPUTS |

|

|

CHANNEL |

|

|

|

|

|

|

|

|

|

ON |

|

|

|

E |

|

Sn |

|

||

|

|

|

|

|

|

|||

|

|

|

L |

|

L |

|

Y0n−Zn |

|

|

|

|

L |

|

H |

|

Y1n−Zn |

|

|

|

H |

|

X |

|

none |

||

|

|

|

|

|

|

|

|

|

Notes

1.H = HIGH state (the more positive voltage) L = LOW state (the less positive voltage) X = state is immaterial

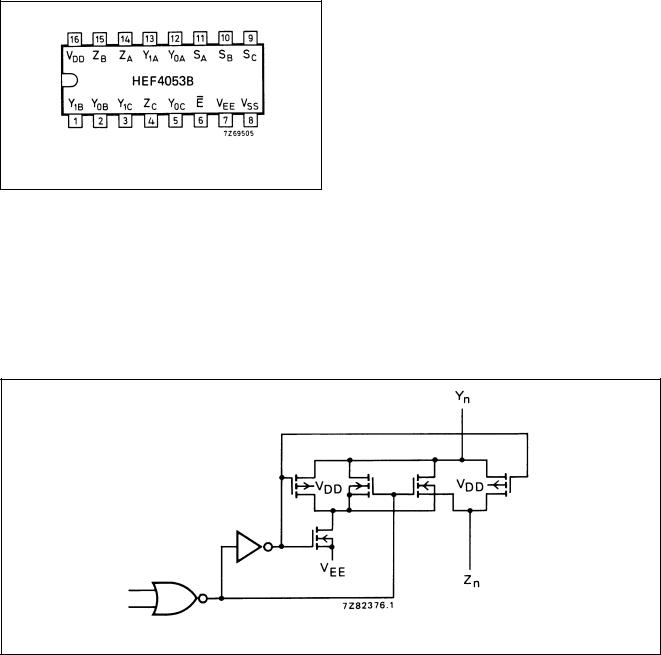

Fig.3 Schematic diagram (one switch).

RATINGS

Limiting values in accordance with the Absolute Maximum System (IEC 134)

Supply voltage (with reference to VDD) |

VEE |

−18 to + 0,5 V |

Note

1.To avoid drawing VDD current out of terminal Z, when switch current flows into terminals Y, the voltage drop across the bidirectional switch must not exceed 0,4 V. If the switch current flows into terminal Z, no VDD current will flow out of terminals Y, in this case there is no limit for the voltage drop across the switch, but the voltages at Y and Z may not exceed VDD or VEE.

January 1995 |

3 |

Loading...

Loading...