Fairchild LM555, NE555, SA555 service manual

!

www.fairchildsemi.com

LM555/NE555/SA555

Single Timer

Features |

Description |

|

||

• |

High Current Drive Capability (200mA) |

The LM555/NE555/SA555 is a highly stable controller |

||

• |

Adjustable Duty Cycle |

capable of producing |

accurate timing pulses. With a |

|

• |

Temperature Stability of 0.005%/° C |

monostable operation, the |

time delay is controlled by one |

|

• |

Timing From Sec to Hours |

external resistor and one capacitor. With an astable |

||

• |

Turn off Time Less Than 2 Sec |

operation, the frequency and duty cycle are accurately |

||

Applications |

controlled by two external resistors and one capacitor. |

|||

|

|

|

||

8-DIP |

|

|

||

• |

Precision Timing |

|

|

|

|

|

|

||

• |

Pulse Generation |

|

|

|

• |

Time Delay Generation |

1 |

|

|

• |

Sequential Timing |

8-SOP |

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

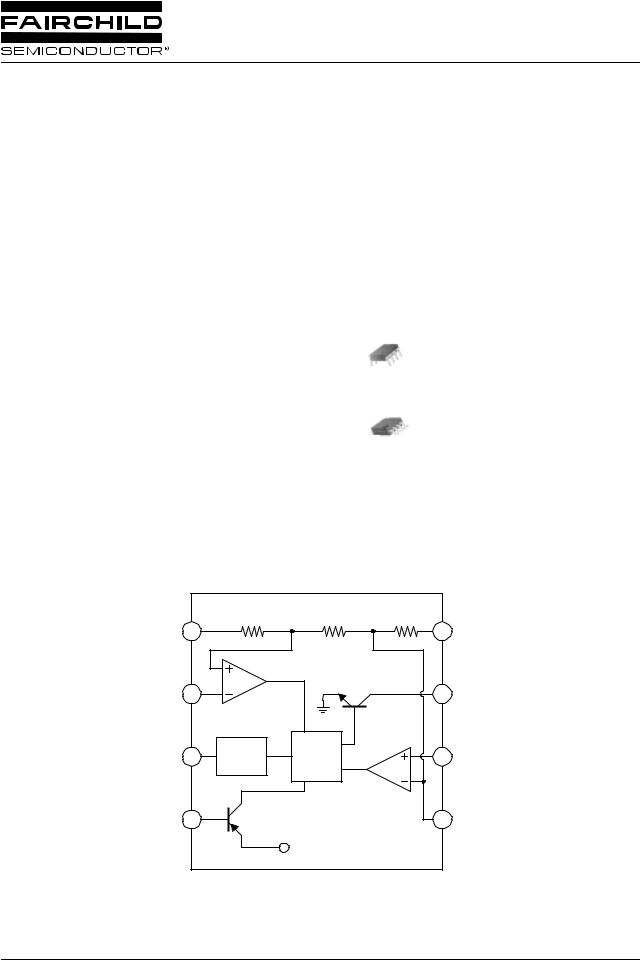

Internal Block Diagram

GND |

|

R |

R |

R |

Vcc |

1 |

|

|

8 |

||

Trigger |

|

Comp. |

Discharging Tr. |

Discharge |

|

2 |

|

|

7 |

||

Output |

3 |

OutPut |

F/F |

6 |

Threshold |

Stage |

|||||

|

|

|

|

Comp. |

|

Reset |

4 |

|

|

5 |

Control |

|

|

|

Vref |

|

Voltage |

Rev. 1.0.3

©2002 Fairchild Semiconductor Corporation

LM555/NE555/SA555

Absolute Maximum Ratings (TA = 25° C)

Parameter |

Symbol |

Value |

Unit |

Supply Voltage |

VCC |

16 |

V |

|

|

|

|

Lead Temperature (Soldering 10sec) |

TLEAD |

300 |

° C |

|

|

|

|

Power Dissipation |

PD |

600 |

mW |

Operating Temperature Range |

|

|

° C |

LM555/NE555 |

TOPR |

0 ~ +70 |

|

SA555 |

|

-40 ~ +85 |

|

Storage Temperature Range |

TSTG |

-65 ~ +150 |

° C |

2

LM555/NE555/SA555

Electrical Characteristics

(TA = 25° C, VCC = 5 ~ 15V, unless otherwise specified)

Parameter |

Symbol |

Conditions |

Min. |

Typ. |

Max. |

Unit |

||

|

|

|

|

|

|

|

|

|

Supply Voltage |

VCC |

|

- |

4.5 |

- |

16 |

V |

|

Supply Current (Low Stable) (Note1) |

ICC |

VCC = 5V, RL = ∞ |

- |

3 |

6 |

mA |

||

|

|

|

|

|

|

|||

VCC = 15V, RL = ∞ |

- |

7.5 |

15 |

mA |

||||

|

|

|||||||

|

|

|

|

|

|

|

|

|

Timing Error (Monostable) |

|

|

|

|

|

|

|

|

Initial Accuracy (Note2) |

ACCUR |

|

|

- |

1.0 |

3.0 |

% |

|

Drift with Temperature (Note4) |

RA = 1kΩ |

to100kΩ |

||||||

∆ t/∆ T |

|

50 |

|

ppm/° C |

||||

Drift with Supply Voltage (Note4) |

C = 0.1µ F |

|

|

|

||||

∆ t/∆ VCC |

|

|

0.1 |

0.5 |

%/V |

|||

|

|

|

|

|||||

Timing Error (Astable) |

ACCUR |

|

|

- |

|

|

|

|

Intial Accuracy (Note2) |

RA = 1kΩ |

to 100kΩ |

2.25 |

- |

% |

|||

|

||||||||

Drift with Temperature (Note4) |

∆ t/∆ T |

C = 0.1µ F |

|

|

150 |

|

ppm/° C |

|

Drift with Supply Voltage (Note4) |

∆ t/∆ VCC |

|

|

|

0.3 |

|

%/V |

|

Control Voltage |

VC |

VCC = 15V |

9.0 |

10.0 |

11.0 |

V |

||

|

|

|

|

|

|

|||

VCC = 5V |

|

2.6 |

3.33 |

4.0 |

V |

|||

|

|

|

||||||

|

|

|

|

|

|

|

||

Threshold Voltage |

VTH |

VCC = 15V |

- |

10.0 |

- |

V |

||

|

|

|

|

|

|

|||

VCC = 5V |

|

- |

3.33 |

- |

V |

|||

|

|

|

||||||

Threshold Current (Note3) |

ITH |

|

- |

- |

0.1 |

0.25 |

µ A |

|

|

|

|

|

|

|

|

|

|

Trigger Voltage |

VTR |

VCC = 5V |

|

1.1 |

1.67 |

2.2 |

V |

|

|

|

|

|

|

|

|||

VCC = 15V |

4.5 |

5 |

5.6 |

V |

||||

|

|

|||||||

Trigger Current |

ITR |

VTR = 0V |

|

|

0.01 |

2.0 |

µ A |

|

Reset Voltage |

VRST |

|

- |

0.4 |

0.7 |

1.0 |

V |

|

|

|

|

|

|

|

|

|

|

Reset Current |

IRST |

|

- |

|

0.1 |

0.4 |

mA |

|

|

|

|

|

|

|

|

||

|

|

VCC = 15V |

|

|

|

|

||

|

|

ISINK = 10mA |

- |

0.06 |

0.25 |

V |

||

Low Output Voltage |

VOL |

ISINK = 50mA |

|

0.3 |

0.75 |

V |

||

|

|

VCC = 5V |

|

- |

0.05 |

0.35 |

V |

|

|

|

ISINK = 5mA |

||||||

|

|

|

|

|

|

|||

|

|

VCC = 15V |

|

|

|

|

||

|

|

ISOURCE = 200mA |

|

12.5 |

- |

V |

||

High Output Voltage |

VOH |

ISOURCE = 100mA |

12.75 |

13.3 |

|

V |

||

|

|

VCC = 5V |

|

2.75 |

3.3 |

- |

V |

|

|

|

ISOURCE = 100mA |

||||||

|

|

|

|

|

|

|||

Rise Time of Output (Note4) |

tR |

|

- |

- |

100 |

- |

ns |

|

Fall Time of Output (Note4) |

tF |

|

- |

- |

100 |

- |

ns |

|

|

|

|

|

|

|

|

|

|

Discharge Leakage Current |

ILKG |

|

- |

- |

20 |

100 |

nA |

|

|

|

|

|

|

|

|

|

|

Notes:

1.When the output is high, the supply current is typically 1mA less than at VCC = 5V.

2.Tested at VCC = 5.0V and VCC = 15V.

3.This will determine the maximum value of RA + RB for 15V operation, the max. total R = 20MΩ , and for 5V operation, the max. total R = 6.7MΩ.

4.These parameters, although guaranteed, are not 100% tested in production.

3

LM555/NE555/SA555

Application Information

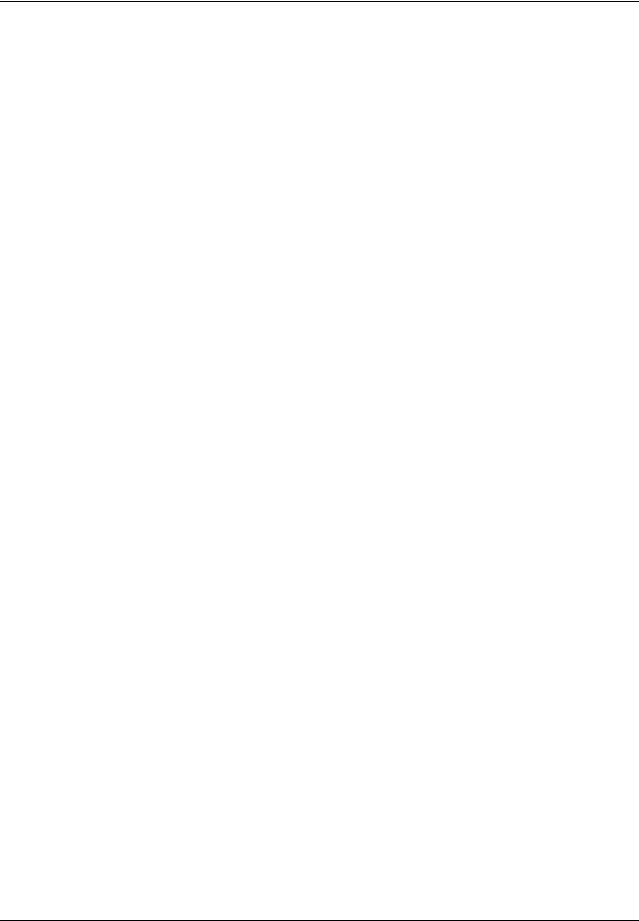

Table 1 below is the basic operating table of 555 timer:

|

Table 1. Basic Operating Table |

|

|

||

|

|

|

|

|

|

Threshold Voltage |

Trigger Voltage |

Reset(PIN 4) |

Output(PIN 3) |

Discharging Tr. |

|

(Vth)(PIN 6) |

(Vtr)(PIN 2) |

(PIN 7) |

|||

|

|

||||

|

|

|

|

|

|

Don't care |

Don't care |

Low |

Low |

ON |

|

Vth > 2Vcc / 3 |

Vth > 2Vcc / 3 |

High |

Low |

ON |

|

Vcc / 3 < Vth < 2 Vcc / 3 |

Vcc / 3 < Vth < 2 Vcc / 3 |

High |

- |

- |

|

Vth < Vcc / 3 |

Vth < Vcc / 3 |

High |

High |

OFF |

|

When the low signal input is applied to the reset terminal, the timer output remains low regardless of the threshold voltage or the trigger voltage. Only when the high signal is applied to the reset terminal, the timer's output changes according to threshold voltage and trigger voltage.

When the threshold voltage exceeds 2/3 of the supply voltage while the timer output is high, the timer's internal discharge Tr. turns on, lowering the threshold voltage to below 1/3 of the supply voltage. During this time, the timer output is maintained low. Later, if a low signal is applied to the trigger voltage so that it becomes 1/3 of the supply voltage, the timer's internal discharge Tr. turns off, increasing the threshold voltage and driving the timer output again at high.

1. Monostable Operation

|

|

|

+Vcc |

|

4 |

8 |

RA |

Trigger |

RESET |

Vcc |

7 |

TRIG |

DISCH |

||

2 |

|

|

|

|

|

THRES |

6 |

3 |

OUT |

CONT |

C1 |

|

GND |

5 |

|

|

|

|

|

RL |

1 |

|

C2 |

Figure 1. Monoatable Circuit

|

102 |

|

|

|

|

|

|

|

|

|

101 |

|

|

Ω |

|

|

|

|

|

|

|

|

|

Ω |

Ω |

|

Ω |

|

|

|

|

|

|

=1k |

Ω |

|

|||

|

|

|

|

10k |

k |

0M |

|

||

|

|

|

|

00 |

M |

|

|||

|

|

|

R |

A |

|

1 |

1 |

|

|

Capacitance(uF) |

|

|

|

|

1 |

|

|

||

100 |

|

|

|

|

|

|

|

|

|

10-1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

10-2 |

|

|

|

|

|

|

|

|

|

10-3 |

|

|

|

|

|

|

|

|

|

10-5 |

10-4 |

10-3 |

|

10-2 |

10-1 |

100 |

101 |

102 |

Time Delay(s)

Figure 2. Resistance and Capacitance vs. Time delay(td)

Figure 3. Waveforms of Monostable Operation

4

LM555/NE555/SA555

Figure 1 illustrates a monostable circuit. In this mode, the timer generates a fixed pulse whenever the trigger voltage falls below Vcc/3. When the trigger pulse voltage applied to the #2 pin falls below Vcc/3 while the timer output is low, the timer's internal flip-flop turns the discharging Tr. off and causes the timer output to become high by charging the external capacitor C1 and setting the flip-flop output at the same time.

The voltage across the external capacitor C1, VC1 increases exponentially with the time constant t=RA*C and reaches 2Vcc/3 at td=1.1RA*C. Hence, capacitor C1 is charged through resistor RA. The greater the time constant RAC, the longer it takes for the VC1 to reach 2Vcc/3. In other words, the time constant RAC controls the output pulse width.

When the applied voltage to the capacitor C1 reaches 2Vcc/3, the comparator on the trigger terminal resets the flip-flop, turning the discharging Tr. on. At this time, C1 begins to discharge and the timer output converts to low.

In this way, the timer operating in the monostable repeats the above process. Figure 2 shows the time constant relationship based on RA and C. Figure 3 shows the general waveforms during the monostable operation.

It must be noted that, for a normal operation, the trigger pulse voltage needs to maintain a minimum of Vcc/3 before the timer output turns low. That is, although the output remains unaffected even if a different trigger pulse is applied while the output is high, it may be affected and the waveform does not operate properly if the trigger pulse voltage at the end of the output pulse remains at below Vcc/3. Figure 4 shows such a timer output abnormality.

Figure 4. Waveforms of Monostable Operation (abnormal)

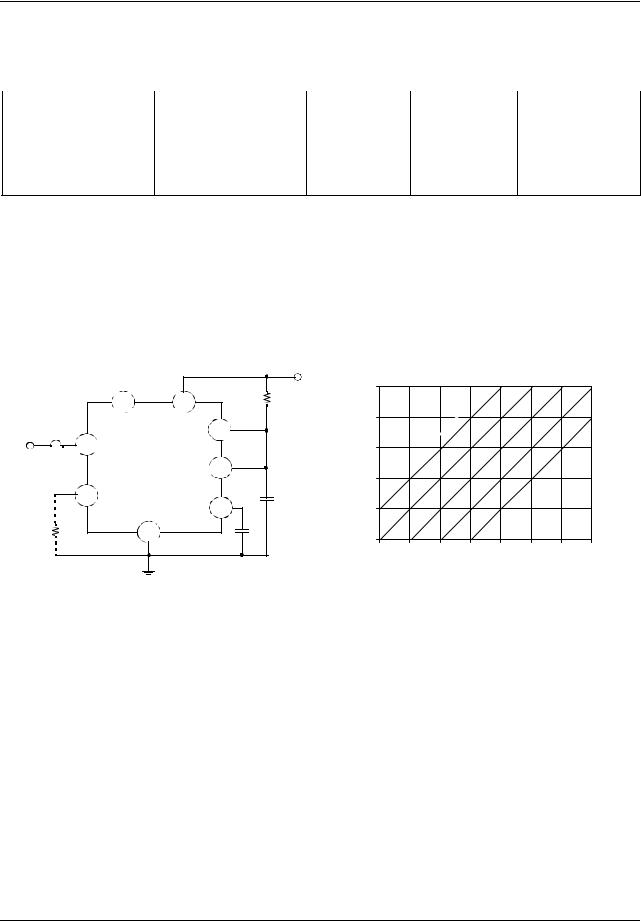

2. Astable Operation

|

|

|

+Vcc |

|

4 |

|

RA |

|

8 |

|

|

|

RESET |

Vcc |

7 |

2 |

TRIG |

DISCH |

|

|

RB |

||

|

|

|

|

|

|

THRES |

6 |

3 |

OUT |

CONT |

C1 |

|

GND |

5 |

|

|

|

|

|

RL |

1 |

|

C2 |

Figure 5. Astable Circuit

|

100 |

|

|

|

|

|

|

|

|

|

|

|

(RA+2RB) |

|

|

|

10 |

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

k |

|

|

|

|

|

|

|

Ω |

|

|

|

|

|

|

|

1 |

|

|

|

Capacitance(uF) |

|

|

|

0k |

|

|

|

1 |

|

|

Ω |

|

|

|

|

|

|

10 |

|

|

|

||

|

|

|

|

|

|

||

|

|

|

0 |

|

|

|

|

|

|

|

k |

|

|

|

|

|

|

|

Ω |

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

M |

|

|

|

||

0.1 |

|

|

Ω |

|

|

|

|

|

1 |

|

|

|

|

||

|

|

|

|

|

|

||

|

|

0M |

|

|

|

|

|

|

|

Ω |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0.01 |

|

|

|

|

|

|

|

1E-3 |

|

|

|

|

|

|

|

100m |

1 |

10 |

100 |

1k |

10k |

100k |

|

|

|

|

Frequency(Hz) |

|

|

|

Figure 6. Capacitance and Resistance vs. Frequency

5

Loading...

Loading...