Fairchild FSL206MR service manual

June 2012

FSL206MR

Green Mode Fairchild Power Switch (FPS™)

Features

Internal Avalanche-Rugged SenseFET: 650V

Precision Fixed Operating Frequency: 67kHz

No-Load <150mW at 265VAC without Bias Winding; <25mW with Bias Winding for FSL206MR, <30mW with Bias Winding for FSL206MRBN

No Need for Auxiliary Bias Winding

Frequency Modulation for Attenuating EMI

Line Under-Voltage Protection (LUVP)

Pulse-by-Pulse Current Limiting

Low Under-Voltage Lockout (UVLO)

Ultra-Low Operating Current: 300µA

Built-In Soft-Start and Startup Circuit

Various Protections: Overload Protection (OLP), Over-Voltage Protection (OVP), Thermal Shutdown (TSD), Abnormal Over-Current Protection (AOCP) Auto-Restart Mode for All Protections

Applications

SMPS for STB, DVD, and DVCD Player

SMPS for Auxiliary Power

Related Resources

Fairchild Power Supply WebDesigner – Flyback Design and Simulation – In Minutes at No Expense

AN-4137 — Design Guidelines for Offline Flyback Converters Using FPS™

AN-4141 — Troubleshooting and Design Tips for Fairchild Power Switch (FPS™) Flyback Applications

AN-4147 — Design Guidelines for RCD Snubber of Flyback

AN-4150 — Design Guidelines for Flyback Converters Using FSQ-Series Fairchild Power Switch (FPS™)

Description

The FSL206MR integrated Pulse-Width Modulator (PWM) and SenseFET is specifically designed for highperformance offline Switched-Mode Power Supplies (SMPS) with minimal external components. This device integrates high-voltage power regulators that combine an avalanche-rugged SenseFET with a Current-Mode PWM control block.

The integrated PWM controller includes: 7.8V regulator for no bias winding, Under-Voltage Lockout (UVLO) protection, Leading-Edge Blanking (LEB), an optimized gate turn-on/turn-off driver, EMI attenuator, Thermal Shutdown (TSD) protection, temperature-compensated precision current sources for loop compensation, and fault-protection circuitry such as; Overload Protection (OLP), Over-Voltage Protection (OVP), Abnormal OverCurrent Protection (AOCP), and Line Under-Voltage Protection (LUVP). During startup, the FSL206MR offers good soft-start performance.

The internal high-voltage startup switch and the BurstMode operation with very low operating current reduce the power loss in Standby Mode. As a result, it is possible to reach power loss of 150mW with no-bias winding and 25mW (for FSL206MR) or 30mW (for FSL206MRBN) with bias winding at no-load condition when the input voltage is 265VAC.

(FPS™) Switch Power Fairchild Mode Green — FSL206MR

© 2011 Fairchild Semiconductor Corporation |

www.fairchildsemi.com |

FSL206MR • Rev. 1.0.4 |

|

Ordering Information

|

|

|

|

|

|

Output Power Table(1) |

|

||

Part |

Operating |

|

|

Packing |

|

|

230VAC |

|

85 ~ |

Top Mark |

PKG |

|

|

(2) |

|

265VAC |

|||

Number |

Temperature |

Method |

Current |

RDS(ON),MAX |

±15% |

|

|||

|

|

Open |

|

Open |

|||||

|

|

|

|

|

Limit |

|

|

||

|

|

|

|

|

|

|

Frame(3) |

|

Frame(3) |

FSL206MRN |

|

FSL206MR |

8-DIP |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

FSL206MRL |

-40 ~ 115°C |

8-LSOP |

Rail |

0.6A |

19Ω |

12W |

|

7W |

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

FSL206MRBN |

|

L206MRB |

8-DIP |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Notes:

1.The junction temperature can limit the maximum output power.

2.230VAC or 100/115VAC with doubler. The maximum power with CCM operation.

3.Maximum practical continuous power in an open-frame design at 50°C ambient.

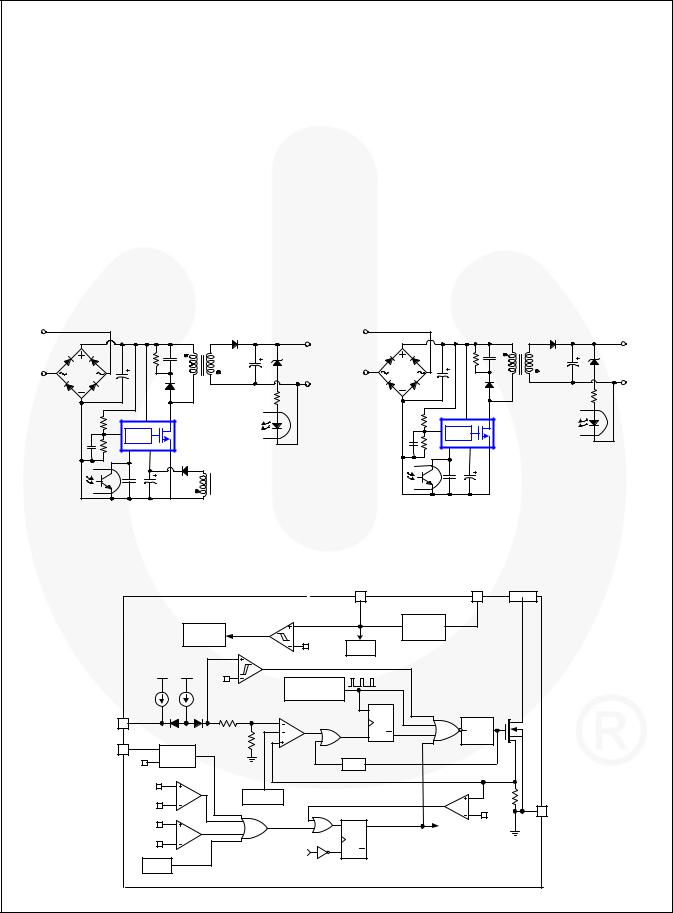

Application Diagram |

|

|

|

AC |

|

AC |

|

IN |

DC |

IN |

DC |

|

|

||

|

OUT |

|

OUT |

|

VSTR |

Drain |

|

VSTR |

Drain |

LS |

PWM |

|

LS |

PWM |

|

|

|

|

|||

|

|

|

|

|

|

VFB |

VCC |

GND |

VFB |

VCC |

GND |

|

|

|

(a) With Bias Winding |

(b) Without Bias Winding |

Figure 1. Typical Application

Internal Block Diagram

Figure 2. Internal Block Diagram

(FPS™) Switch Power Fairchild Mode Green — FSL206MR

© 2011 Fairchild Semiconductor Corporation |

www.fairchildsemi.com |

FSL206MR • Rev. 1.0.4 |

2 |

Pin Configuration

Figure 3. Pin Configuration

Pin Definitions

Pin # |

Name |

Description |

|

|

|

|

|

1 |

GND |

Ground. SenseFET source terminal on primary side and internal control ground. |

|

|

|

Positive Supply Voltage Input. Although connected to an auxiliary transformer winding, |

|

2 |

VCC |

current is supplied from pin 5 (VSTR) via an internal switch during startup (see Internal Block |

|

Diagram section). It is not until VCC reaches the UVLO upper threshold (8V) that the internal |

|||

|

|

||

|

|

startup switch opens and device power is supplied via the auxiliary transformer winding. |

|

|

|

Feedback Voltage. Non-inverting input to the PWM comparator, with a 0.11mA current source |

|

3 |

VFB |

connected internally and a capacitor and opto-coupler typically connected externally. There is a |

|

delay while charging external capacitor CFB from 2.4V to 5V using an internal 2.7μA current |

|||

|

|

source. This delay prevents false triggering under transient conditions, but allows the protection |

|

|

|

mechanism to operate under true overload conditions. |

|

4 |

LS |

Line Sense Pin. This pin is used to protect the device when the input voltage is lower than the |

|

rated input voltage range. If this pin is not used, connect to ground. |

|||

|

|

||

|

|

Startup. Connected to the rectified AC line voltage source. At startup, the internal switch |

|

5 |

VSTR |

supplies internal bias and charges an external storage capacitor placed between the VCC pin |

|

and ground. Once VCC reaches 8V, all internal blocks are activated. After that, the internal high- |

|||

|

|

||

|

|

voltage regulator (HV REG) turns on and off irregularly to maintain VCC at 7.8V. |

|

6, 7, 8 |

Drain |

Drain. Designed to connect directly to the primary lead of the transformer and capable of |

|

switching a maximum of 650V. Minimizing the length of the trace connecting these pins to the |

|||

|

|

transformer decreases leakage inductance. |

(FPS™) Switch Power Fairchild Mode Green — FSL206MR

© 2011 Fairchild Semiconductor Corporation |

www.fairchildsemi.com |

FSL206MR • Rev. 1.0.4 |

3 |

Absolute Maximum Ratings

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only. TA = 25°C unless otherwise specified.

Symbol |

Parameter |

Min. |

Max. |

Unit |

|

|

|

|

|

VSTR |

VSTR Pin Voltage |

-0.3 |

650.0 |

V |

VDS |

Drain Pin Voltage |

-0.3 |

650.0 |

V |

VCC |

Supply Voltage |

|

26 |

V |

VLS |

LS Pin Voltage |

-0.3 |

Internally Clamped |

V |

Voltage(4) |

||||

VFB |

Feedback Voltage Range |

-0.3 |

Internally Clamped |

V |

Voltage(4) |

||||

IDM |

Drain Current Pulsed(5) |

|

1.5 |

A |

EAS |

Single-Pulsed Avalanche Energy(6) |

|

11 |

mJ |

PD |

Total Power Dissipation |

|

1.3 |

W |

TJ |

Operating Junction Temperature |

-40 |

+150 |

°C |

TA |

Operating Ambient Temperature |

-40 |

+125 |

°C |

TSTG |

Storage Temperature |

-55 |

+150 |

°C |

ESD |

Human Body Model, JESD22-A114 |

|

4 |

KV |

Charged Device Model, JESD22-C101 |

|

2 |

||

|

|

|

Notes:

4.VFB is clamped by internal clamping diode (13V ICLAMP_MAX < 100μA). After shutdown, before VCC reaching VSTOP, VSD < VFB < VCC.

5.Repetitive rating: pulse-width limited by maximum junction temperature.

6.L=21mH, starting TJ=25°C.

Thermal Impedance

TA=25°C unless otherwise specified.

Symbol |

Parameter |

Value |

Unit |

|

|

|

|

θJA |

Junction-to-Ambient Thermal Impedance(7) |

93 |

°C/W |

Notes:

7.JEDEC recommended environment, JESD51-2 and test board, JESD51-10 with minimum land pattern for 8DIP and JESD51-3 with minimum land pattern for 8LSOP.

(FPS™) Switch Power Fairchild Mode Green — FSL206MR

© 2011 Fairchild Semiconductor Corporation |

www.fairchildsemi.com |

FSL206MR • Rev. 1.0.4 |

4 |

Electrical Characteristics

TA = 25°C unless otherwise specified.

Symbol |

Parameter |

Condition |

Min. |

Typ. |

Max. |

Unit |

||

|

|

|

|

|

|

|

|

|

SenseFET Section |

|

|

|

|

|

|

|

|

BVDSS |

Drain-Source Breakdown Voltage |

VCC = 0V, ID = 250µA |

|

650 |

|

|

V |

|

IDSS |

Zero Gate Voltage Drain Current |

VDS = 650V, VGS = 0V |

|

|

|

50 |

µA |

|

VDS = 520V, VGS = 0V, TA = 125°C(8) |

|

|

250 |

µA |

||||

|

|

|

|

|||||

RDS(ON) |

Drain-Source On-State Resistance(9) |

VGS = 10V, ID = 0.3A |

|

|

14 |

19 |

Ω |

|

CiSS |

Input Capacitances |

VGS = 0V, VDS = 25V, f = 1MHz |

|

162 |

|

pF |

||

COSS |

Output Capacitance |

VGS = 0V, VDS = 25V, f = 1MHz |

|

14.9 |

|

pF |

||

CRSS |

Reverse Transfer Capacitance |

VGS = 0V, VDS = 25V, f = 1MHz |

|

2.7 |

|

pF |

||

tr |

Rise Time |

VDS = 325V, ID = 0.5A, RG = 25Ω |

|

6.1 |

|

ns |

||

tf |

Fall Time |

VDS = 325V, ID = 0.5A, RG = 25Ω |

|

43.6 |

|

ns |

||

Control Section |

|

|

|

|

|

|

|

|

fOSC |

Switching Frequency |

VFB = 4V, VCC = 10V |

|

61 |

67 |

73 |

KHz |

|

∆fOSC |

Switching Frequency Variation |

-25°C < TJ < 85°C |

|

|

±5 |

±10 |

% |

|

fM |

Frequency Modulation(8) |

|

|

|

|

±3 |

|

KHz |

DMAX |

Maximum Duty Cycle |

VFB = 4V, VCC = 10V |

|

66 |

72 |

78 |

% |

|

DMIN |

Minimum Duty Cycle |

VFB = 0V, VCC = 10V |

|

0 |

0 |

0 |

% |

|

VSTART |

UVLO Threshold Voltage |

VFB = 0V, VCC Sweep |

|

7 |

8 |

9 |

V |

|

VSTOP |

After Turn On |

|

6 |

7 |

8 |

V |

||

|

|

|||||||

IFB |

Feedback Source Current |

VFB= 0V, VCC = 10V |

|

90 |

110 |

130 |

µA |

|

tS/S |

Internal Soft-Start Time |

VFB = 4V, VCC = 10V |

|

10 |

15 |

20 |

ms |

|

Burst Mode Section |

|

|

|

|

|

|

|

|

VBURH |

Burst-Mode HIGH Threshold Voltage |

VCC = 10V, |

|

FSL206MR |

0.66 |

0.83 |

1.00 |

V |

|

|

|

|

|

|

|||

|

FSL206MRB |

0.40 |

0.50 |

0.60 |

V |

|||

|

|

VFB Increase |

|

|||||

VBURL |

Burst-Mode LOW Threshold Voltage |

VCC = 10V, |

|

FSL206MR |

0.59 |

0.74 |

0.89 |

V |

VFB Decrease |

|

FSL206MRB |

0.28 |

0.35 |

0.42 |

V |

||

|

|

|

||||||

HYSBUR |

Burst-Mode Hysteresis |

|

|

FSL206MR |

|

90 |

|

mV |

|

|

|

|

|

|

|

||

|

|

FSL206MRB |

|

150 |

|

mV |

||

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

Protection Section |

|

|

|

|

|

|

|

|

ILIM |

Peak Current Limit |

VFB = 4V, di/dt = 300mA/µs, |

0.54 |

0.60 |

0.66 |

A |

||

VCC = 10V |

|

|||||||

|

|

|

|

|

|

|

||

tCLD |

Current Limit Delay(8) |

|

|

|

|

100 |

|

ns |

VSD |

Shutdown Feedback Voltage |

VCC = 10V |

|

4.5 |

5.0 |

5.5 |

V |

|

IDELAY |

Shutdown Delay Current |

VFB = 4V |

|

2.1 |

2.7 |

3.3 |

µA |

|

tLEB |

Leading-Edge Blanking Time(8) |

|

|

|

250 |

|

|

ns |

VAOCP |

Abnormal Over-Current Protection(8) |

|

|

|

|

0.7 |

|

V |

VOVP |

Over-Voltage Protection |

VFB = 4V, VCC Increase |

|

23.0 |

24.5 |

26.0 |

V |

|

VLS_OFF |

Line-Sense Protection On to Off |

VFB = 3V, VCC = 10V, VLS Decrease |

1.9 |

2.0 |

2.1 |

V |

||

VLS_ON |

Line-Sense Protection Off to On |

VFB = 3V, VCC = 10V, VLS Increase |

1.4 |

1.5 |

1.6 |

V |

||

TSD |

Thermal Shutdown Temperature(8) |

|

|

|

125 |

135 |

150 |

°C |

HYSTSD |

TSD Hysteresis Temperature(8) |

|

|

|

|

60 |

|

°C |

Continued on the following page…

(FPS™) Switch Power Fairchild Mode Green — FSL206MR

© 2011 Fairchild Semiconductor Corporation |

www.fairchildsemi.com |

FSL206MR • Rev. 1.0.4 |

5 |

Loading...

Loading...