ZILOG Z90211, Z90212, Z90213, Z90218, Z90219 Datasheet

PRELIMINARY CUSTOMER PROCUREMENT SPECIFICATION

1

Z90219/213/212/211/218 1

Z8® DIGITAL TELEVISION

CONTROLLERS

FEATURES

|

|

ROM |

RAM* |

I/O |

Voltage |

|

Device |

(KB) |

(Bytes) |

Lines |

Range |

|

|

|

|

|

|

|

Z90211 |

16 (OTP) |

237 |

20 |

4.5V to 5.5V |

Z90218 |

8 |

237 |

20 |

4.5V to 5.5V |

|

Z90212 |

12 |

237 |

20 |

4.5V to 5.5V |

|

Z90213 |

16 |

237 |

20 |

4.5V to 5.5V |

|

Z90219 |

32 (ext.) |

237 |

N/A |

4.5V to 5.5V |

|

|

|

|

|

|

|

Note: OTP and Z9021x products under development

Z8-Based CMOS Microcontroller for Consumer Television, Cable Box, and Satellite Receiver Applications.

■42-Pin SDIP Package

■Z8® Microcontroller Core at 6 MHz

■Mask ROM sizes Available in 8, 12 and 16 Kbytes

■Eleven Pulse Width Modulators

■On-Chip Infrared (IR) Capture Registers

■Four Channel 3-bit Analog-to-Digital Converter

■Twenty General Purpose I/O Pins

■I2C Serial Communication Port)

On Screen Display (OSD) Section

■Supports Displays up to 10 rows by 24 Columns with 256 Characters

■Character Cell Resolution of 14 Pixels by 18 Scan lines

■Variable Inter-row Spacing from 0-15 Horizontal Scan Lines

■Foreground and Background Colors Fully Programmable by Character

GENERAL DESCRIPTION

The Z9021x Digital Television Controller (DTC) family is Zilog’s latest and most powerful Z8-based DTC product offering. These parts feature larger system RAM and ROM options, together with a host of new features including a new color palette system, flexible inter-row spacing, higher character cell resolution, background mesh effect, dedicated I.R. capture registers, on-chip Analog-to-Digital conversion, and a hardware Master mode I2C interface. The familiar Z8 core in combination with these advanced features makes the Z9021x family an ideal choice for low to midrange televisions in both PAL and NTSC markets.

The Z9021x family consists of two basic device types; Z9020x and Z9021x. The only difference between the two types is the presence of a hardware I2C serial communication port and half-tone OSD circuitry on the Z9021x family. Of course I2C communication is supported on the Z9020x family in software with the dedication of any two I/O pins to the task.

The Z9021x family takes full advantage of the Z8’s expanded register file space to offer greater flexibility in On Screen Display creation.

CP96TEL2400 |

P R E L I M I N A R Y |

1 |

Z90219/213/212/211 |

|

Z8® Digital Television Controllers |

Zilog |

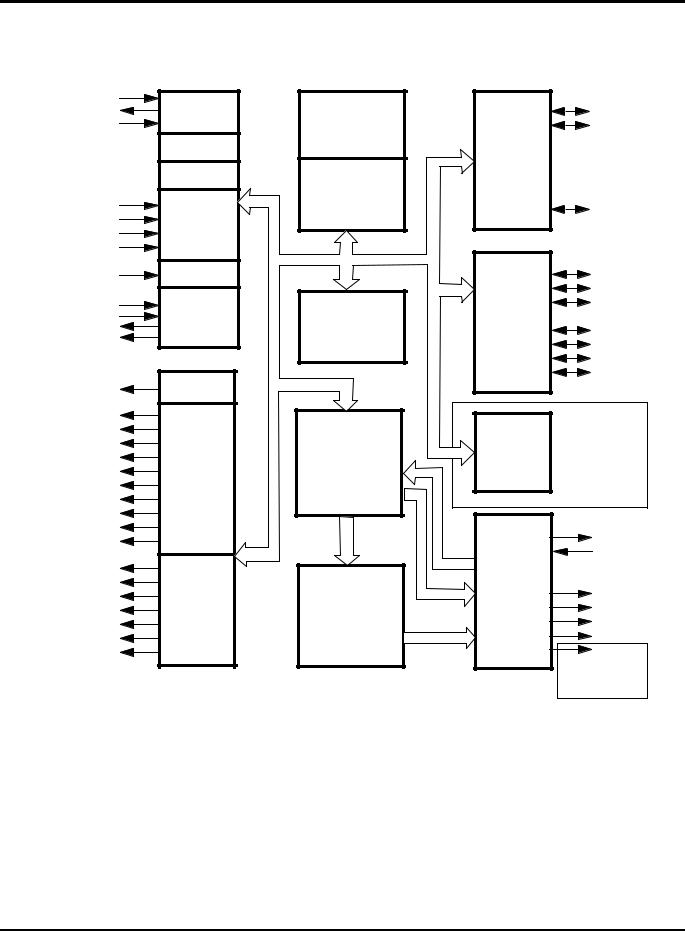

BLOCK DIAGRAM

XTAL1 |

Oscillator |

|

XTAL2 |

WDT |

|

/RESET |

RESET |

|

|

Counter |

|

|

Timer |

|

|

Counter |

|

|

Timer |

|

ADC0 |

|

|

ADC1 |

3-bit |

|

ADC2 |

ADC |

|

ADC3 |

|

|

IRIN |

IR |

|

|

Counter |

|

P30 |

Port3 |

|

P31 |

||

P34 |

|

|

P35 |

|

|

PWM11 |

PWM 11 |

|

(14-bit) |

||

|

||

PWM1 |

|

|

PWM2 |

|

|

PWM3 |

|

|

PWM4 |

PWM 1 |

|

PWM5 |

to |

|

PWM6 |

PWM 10 |

|

PWM7 |

(6-bit) |

|

PWM8 |

||

|

||

PWM9 |

|

|

PWM10 |

|

|

P1 |

|

|

P2 |

|

|

P3 |

Output |

|

P4 |

||

Port |

||

P5 |

||

|

||

P6 |

|

|

P7 |

|

8/12/16K Byte

Program ROM

Z8 CPU

Core

Register File

256 Byte

Character RAM 240 by 11-bit & 10 by 8-bit

Character ROM

9K by 7-bit

P20

P21

P22 Port2

P22 Port2

P23

P23

P24

P24

P25

P25

P26 P27

P26 P27

P40

P41

P42 Port4

P43

P43

P44

P45

P46 P47

SCLK0 I2C

SCLK0 I2C

SDATA0

SDATA0

Interface  SCLK1

SCLK1

SDATA1

SDATA1

Z9021x ONLY

OSDX1

OSDX2 On Screen  HSync

HSync

Display  VSync

VSync

R

G

B VBlank

HLFTN

Z9021x ONLY

Figure 1. Functional Block Diagram

2 |

P R E L I M I N A R Y |

CP96TEL2400 |

|

|

|

|

|

|

|

|

Z90219/213/212/211 |

Zilog |

|

|

|

|

|

|

|

Z8® Digital Television Controllers |

PIN IDENTIFICATION |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

PWM11/P7 |

|

1 |

42 |

|

|

P27/SDATA1 |

||

|

|

|||||||

PWM6/P6 |

|

|

|

|

|

|

|

P26/SCLK1 |

|

|

|

|

|

|

|

||

PWM5/P5 |

|

|

|

|

|

|

|

P25/SDATA0 |

|

|

|

|

|

|

|

||

PWM4/P4 |

|

|

|

|

|

|

|

P24/SCLK0 |

|

|

|

|

|

|

|

||

PWM3/P3 |

|

|

|

|

|

|

|

P23 |

|

|

|

|

|

|

|

||

PWM2/P2 |

|

|

|

|

|

|

|

P22 |

|

|

|

|

|

|

|

||

PWM1/P1 |

|

|

|

|

|

|

|

IRIN |

|

|

|

|

|

|

|

||

P40 |

|

|

|

|

|

|

|

P21 |

|

|

|

|

|

|

|

||

P34/ADC3 |

|

|

|

|

|

|

|

VCC |

|

|

|

|

|

|

|

||

P35/ADC2 |

|

|

|

|

|

|

|

/RESET |

|

|

|

|

|

|

|

||

P41/ADC1 |

|

|

|

Z9021x |

|

|

|

XTAL2 |

|

|

|

(Top View) |

|

|

|

||

P31/ADC0 |

|

|

|

|

|

|

XTAL1 |

|

|

|

|

|

|

|

|

||

AGND |

|

|

|

|

|

|

|

GND |

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

||

P42 |

|

|

|

|

|

|

|

OSDX2 |

|

|

|

|

|

|

|

||

P43 |

|

|

|

|

|

|

|

OSDX1 |

|

|

|

|

|

|

|

||

P30 |

|

|

|

|

|

|

|

VSYNC |

|

|

|

|

|

|

|

||

P44/PWM7 |

|

|

|

|

|

|

|

HSYNC |

|

|

|

|

|

|

|

||

P45/PWM8 |

|

|

|

|

|

|

|

VBLANK |

|

|

|

|

|

|

|

||

P46/PWM9 |

|

|

|

|

|

|

|

R |

|

|

|

|

|

|

|

||

P47/PWM10 |

|

|

21 |

22 |

|

|

G |

|

|

|

|

|

|||||

P20/HLFTN |

|

|

|

B |

||||

|

|

|||||||

|

|

|

|

|

|

|

|

|

CP96TEL2400 |

P R E L I M I N A R Y |

3 |

Loading...

Loading...