ZILOG Z8932320FEC, Z8932320FSC, Z8932320VEC, Z893232YFSC, Z8932320VSC Datasheet

...

|

P R E L I M I N A R Y |

Z89323/373/393 |

|

|

16-BIT DIGITAL SIGNAL PROCESSORS |

||

|

|

|

|

PRELIMINARY

CUSTOMERPROCUREMENTSPECIFICATION

Z89323/373/393

16-BITDIGITAL SIGNALPROCESSORS

FEATURES

|

DSP ROM |

OTP |

DSP RAM |

Max Core |

Device |

(K Words) |

(K Words) |

(Words) |

MIPS |

|

|

|

|

|

Z89323 |

8 |

|

512 |

2 0 |

Z89373 |

|

8 |

512 |

1 6 |

Z89393 |

64* |

|

512 |

2 0 |

Package |

44-Pin |

68-Pin 44-Pin 80-Pin 100-Pin |

||

Device |

PLCC |

PLCC |

QFP |

QFP QFP |

|

|

|

|

|

Z89323 |

|

|

|

|

Z89373 |

|

|

|

|

Z89393 |

|

|

|

|

* External |

|

|

|

|

|

|

|

■ |

Operating Temperature Ranges: |

On-Board Peripherals |

|||||

|

|

0°C to +70°C (Standard) |

|

|

|

||

|

–40°C to +85°C (Extended) |

|

■ |

4-Channel, 8-Bit Analog to Digital Converter (A/D) |

|||

■ 4.5- to 5.5-Volt Operating Range |

■ |

On-Board Serial Peripheral Interface (SPI) |

|||||

DSP Core |

|

|

|

■ |

Up to 40 Bits of Programmable I/O |

||

■ 20 MIPS @ 20 MHz, 16-Bit Fixed Point DSP |

■ |

Two Channels of Programmable |

|||||

|

|

|

|

|

|

|

Pulse Width Modulators (PWM) |

■ |

50 ns Instruction Cycle Time |

|

|

|

|||

|

|

|

|

|

|

■ Three General-Purpose Timer/Counters |

|

■ |

Single-Cycle Multiply and ALU Operations |

|

|

||||

|

|

|

|

|

|

■ Two Watch-Dog Timers (WDT) |

|

■ |

Two |

Internal |

Data Buses and |

Address Generators |

|

|

|

|

|

|

|

|

|

■ |

Programmable PLL |

■ |

Six |

Register |

Address |

Pointers |

|

|

|

|

|

|

|

|

|

■ Three Vectored Interrupts Servicing Eight |

|

■ |

Optimized Instruction |

Set (30 |

Instructions) |

|

Interrupt Sources |

||

|

|

|

|

|

|

■ |

Power-Down and Power-On Reset |

GENERAL DESCRIPTION

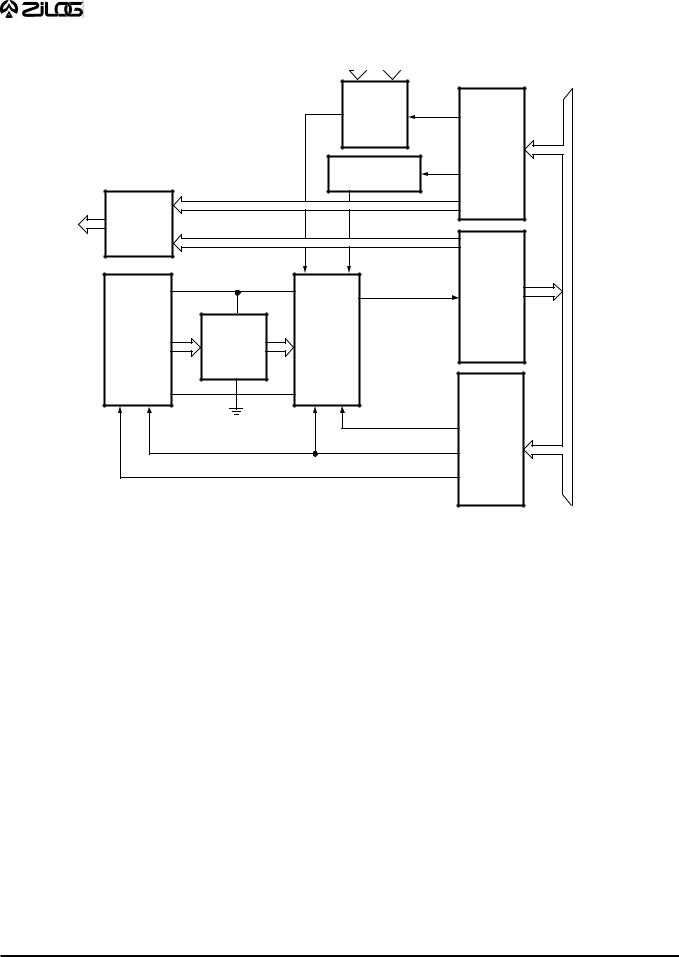

The Z89323/373/393 DSP family of products builds on Zilog's first generation Z893XX DSP core, integrating several peripherals especially well suited for cost-effective voice, telephony, and control applications.

These DSP devices feature a modified Harvard architecture supported by one program bus and two on-chip data buses. This bus structure is supported by two address generators and six register pointers to ensure that the 20 MIPS DSP CPU is continually active.

The Z893X3 DSP family is designed to provide a complete DSP and control system on a single chip. By integrating

various peripherals, such as a high-speed 4-channel, 8-bit A/D, an SPI, three timers with PWM and WDT support, the Z893X3 family provides a compact system solution and reduces overall system cost.

To support a wide variety of development needs, the Z893X3 DSP product family features the cost-effective Z89323 with 8 Kwords of on-chip ROM, and the Z89373, a 16-MIPS OTP version of the Z89323, ideal for prototypes and early production builds. For systems requiring more than 8 Kwords of program memory, the Z89393 device can address up to 64 Kwords of external program memory.

DS95DSP0101 Q4/95 |

1 |

P R E L I M I N A R Y |

Z89323/373/393 |

16-BIT DIGITAL SIGNAL PROCESSORS |

GENERAL DESCRIPTION (Continued)

The Z893X3 DSP family is 100 percent source and objectcode compatible with the existing Z89321/371/391 devices, providing users, who can benefit from increased integration and reduced system cost, an easy migration path from one DSP product to the next.

Notes:

All Signals with a preceding front slash, "/", are active Low, e.g., B//W (WORD is active Low); /B/W (BYTE is active Low, only).

Power connections follow conventional descriptions below:

Connection Circuit Device

Throughout this specification, references to the Z89323 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||||

|

|

|

Power |

|

|

|

|

|

VCC |

|

|

|

|

|

|

VDD |

|||||||||||||||||||||||||||||||||||||||||||||||||||

device applies equally to the Z89373 and Z89393, unless |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||

otherwise |

specified. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Ground |

|

|

|

|

|

GND |

|

|

|

|

|

|

VSS |

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Program |

|

Data RAM0 |

|

|

|

|

|

|

|

Data RAM1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ROM/OTP |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Port 0 |

|||||||||||||||||||||

PD0-15 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

8192x16 |

|

|

256x16 |

|

|

|

|

|

|

256x16 |

|

|

16-Bit |

|

|

|

|

|

|

|

|

|

|

|

/EXTEN |

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Program |

|

|

|

|

|

|

|

|

|

|

|

||||

PA0-15 |

|

|

|

|

|

|

PDATA |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

I/O |

|

|

|

|

|

|

|

|

|

|

|

EA0-2 |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

EXT0-15/P00-15 |

||||

|

|

|

|

|

|

|

|

|

PADDR |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DDATA |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

/DS |

||||

|

|

|

/PAZ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

WAIT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

RD//WR |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

XDATA |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P0 |

P0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AN0 |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P1 |

P1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

8-Bit |

|

|

|

|

|

|

|

|

|

AN1 |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

X |

|

|

|

|

Y |

|

|

|

|

|

|

|

|

P2 |

P2 |

|

|

|

|

|

|

|

|

|

A/D |

|

|

|

|

|

|

|

|

|

|

AN2 |

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AN3 |

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Multiplier |

|

|

|

|

|

|

|

DP0-3 |

DP4-6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

HALT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Port 1 |

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

/ROMEN |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P |

|

|

|

|

|

|

|

|

|

ADDR |

ADDR |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P10-17 |

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

GEN0 |

GEN1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

or |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

/RES |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Shifter |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

8-Bit I/O |

|

|

|

|

|

|

INT2 |

||||||||||||

|

|

|

CLKI |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CLKOUT |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SIN |

|

|

|

CLKO |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

Program |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SOUT |

|||||

|

|

|

AGND |

|

|

|

|

|

|

|

|

Arithmetic |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SK |

||||||||||||||

|

|

|

|

|

|

Control |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

Logic Unit |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

Unit |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SS |

|||||||||||||

ANVCC |

|

|

|

|

|

|

|

|

|

|

(ALU) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

UI0-1 |

||||||||||||||

|

|

|

VALO |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

16-Bit Timer, |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Counter |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Port 2 |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

VALI |

|

|

|

|

|

|

|

|

|

|

|

|

Accumulator |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P20-27 |

|||||||||||

|

|

|

VSS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

16-Bit Timer, |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

or |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Counter, PWM |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

VDD |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

8-Bit I/O |

|

|

|

|

|

|

UI2 |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

16-Bit Timer, |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

UO0-2 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Counter, PWM |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

INT0-1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SPI |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Port 3 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4 Inputs |

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P30-33 |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4 Outputs |

|

|

|

|

|

|

P34-37 |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

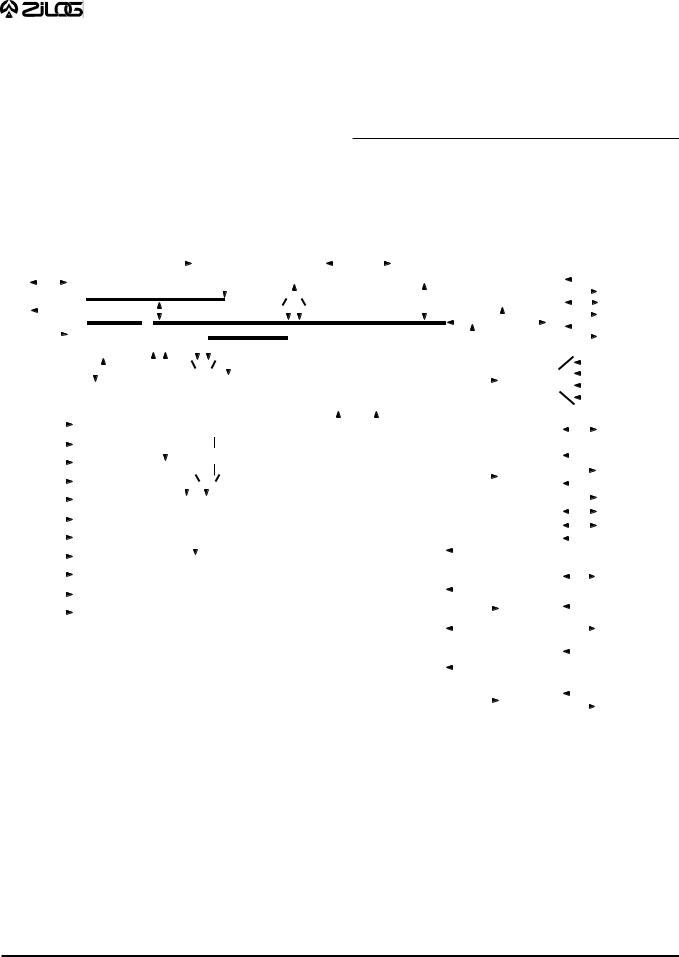

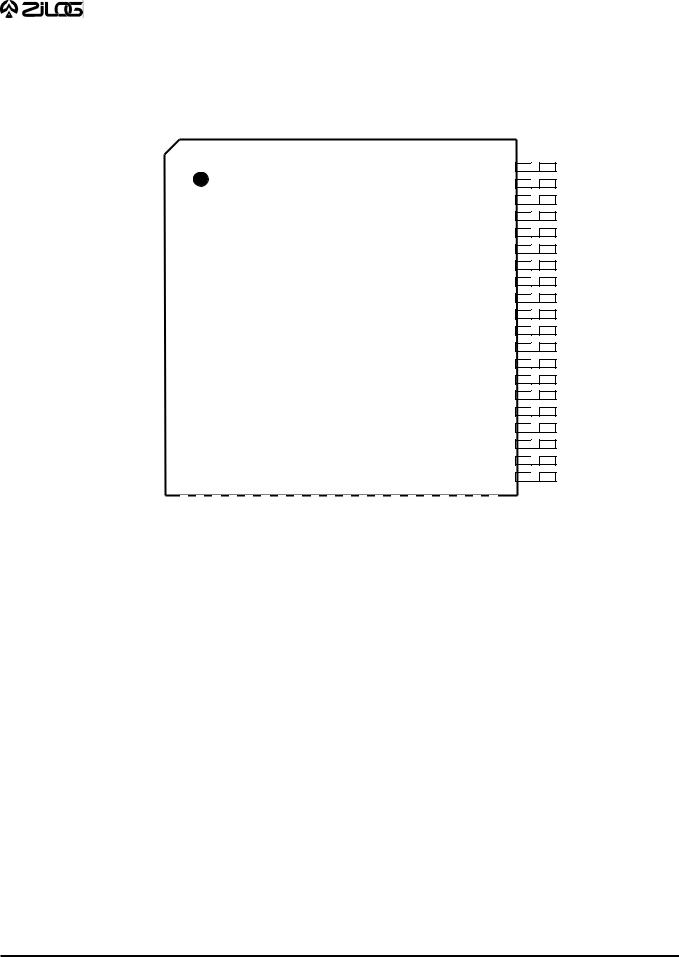

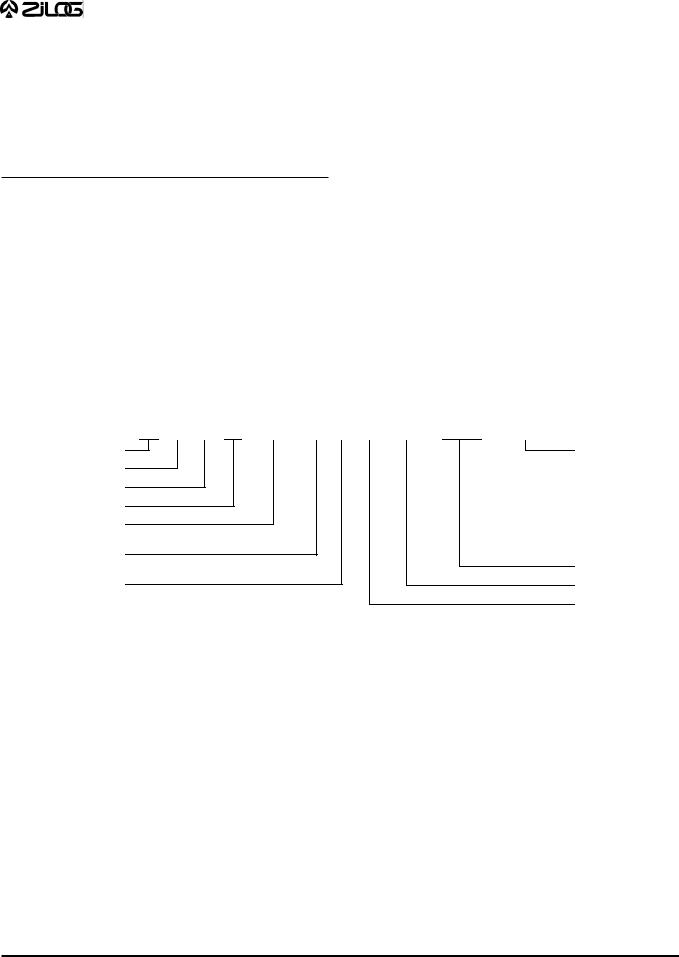

Figure 1. Z893X3 Functional Block Diagram

2 |

DS95DSP0101 Q4/95 |

|

P R E L I M I N A R Y |

|

|

Z89323/373/393 |

||||||||||

|

|

|

16-BIT DIGITAL SIGNAL PROCESSORS |

|||||||||||

PIN DESCRIPTION |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

EXT15/P015 |

VSS |

EXT14/P014 |

EXT13/P013 |

EXT12/P012 |

P20/INT0 |

VSS |

EXT2/P02 |

EXT1/P01 |

EXT0/P00 |

VSS |

|

||

|

6 |

5 |

4 |

3 |

2 |

1 |

44 |

43 |

42 |

41 |

40 |

|

||

EXT3/P03 |

7 |

|

|

|

|

|

|

|

|

|

|

|

39 |

/RES |

|

|

|

|

|

|

|

|

|

|

|

||||

EXT4/P04 |

8 |

|

|

|

|

|

|

|

|

|

|

|

38 |

WAIT |

VSS |

9 |

|

|

|

|

|

|

|

|

|

|

|

37 |

P24/UO2 |

EXT5/P05 |

10 |

|

|

|

|

|

|

|

|

|

|

|

36 |

P22/UO0 |

EXT6/P06 |

11 |

|

|

|

Z89323/373 |

|

|

|

35 |

CLKO |

||||

EXT7/P07 |

12 |

|

|

|

|

|

|

34 |

CLKI |

|||||

|

|

|

44-Pin PLCC |

|

|

|

||||||||

INT1/P21 |

13 |

|

|

|

|

|

|

33 |

/DS |

|||||

|

|

|

|

|

|

|

|

|

|

|

||||

EXT8/P08 |

14 |

|

|

|

|

|

|

|

|

|

|

|

32 |

P23/UO1 |

EXT9/P09 |

15 |

|

|

|

|

|

|

|

|

|

|

|

31 |

EA2 |

VSS |

16 |

|

|

|

|

|

|

|

|

|

|

|

30 |

EA1 |

EXT10/P010 |

17 |

|

|

|

|

|

|

|

|

|

|

|

29 |

EA0 |

|

18 |

19 |

20 |

21 |

22 |

23 |

24 |

25 |

26 |

27 |

28 |

|

||

|

1/P011 EXT1 |

AHIV |

ALOV |

ANGND |

AN0 |

AN1 |

AN2 |

AN3 |

ANVCC |

VDD |

|

RD//WR |

|

|

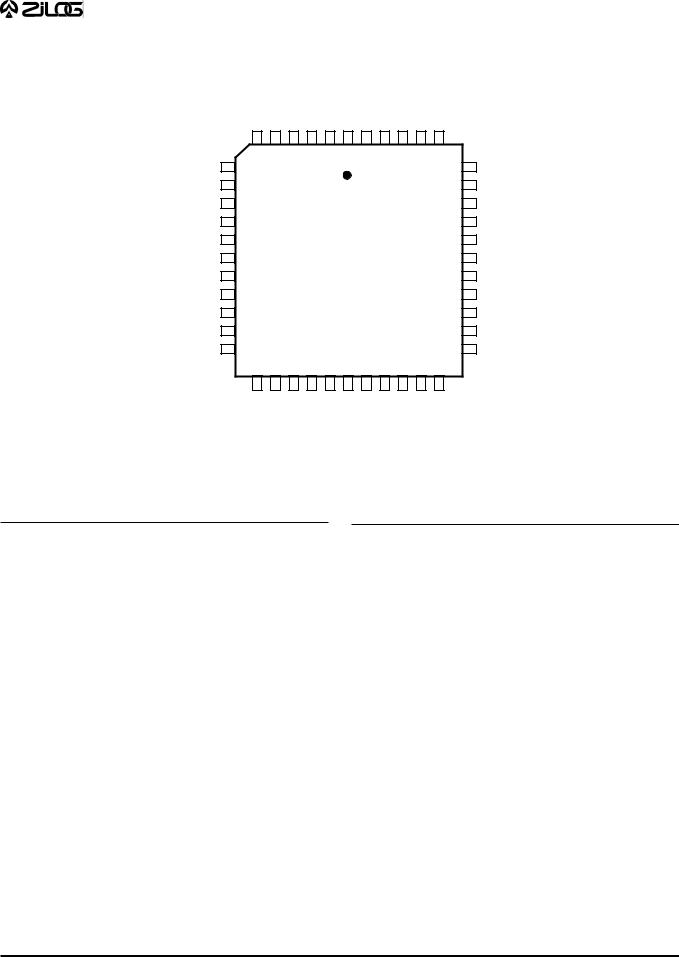

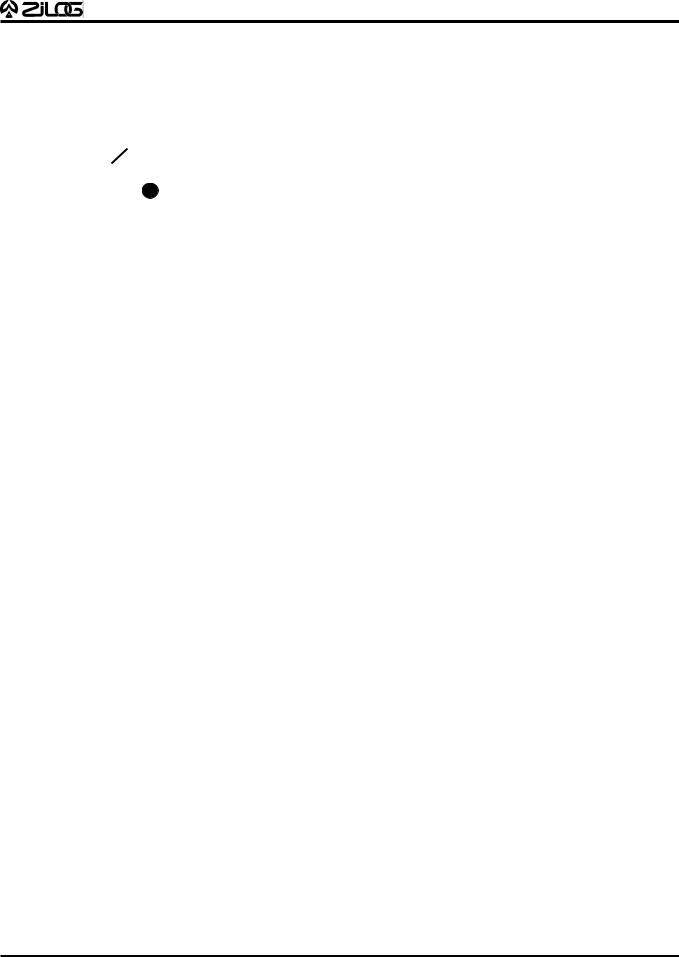

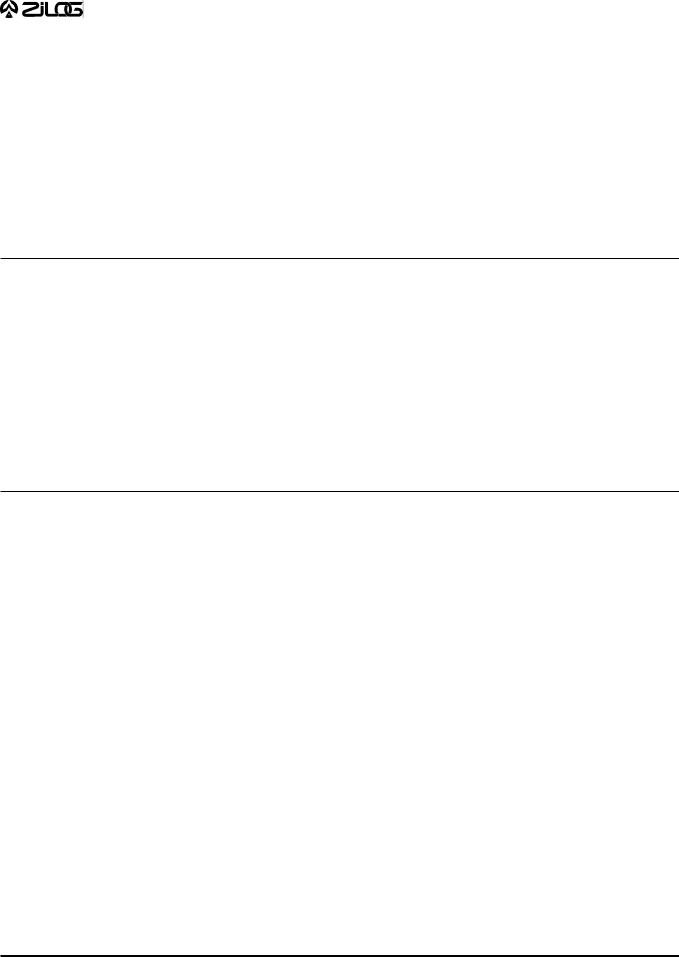

Figure 2. 44-Pin PLCC Z89323/373 Pin Configuration

Table 1. 44-Pin PLCC Z89323/373 Pin Description

No. |

Symbol |

Function |

Direction |

|

|

|

|

1 |

P20/INT0 |

Port20/Interrupt0 |

In/Output |

2 |

EXT12/P012 |

ExtData12/Port012 |

In/Output |

3 |

EXT13/P013 |

ExtData13/Port013 |

In/Output |

4 |

EXT14/P014 |

ExtData14/Port014 |

In/Output |

5 |

VSS |

Ground |

|

6 |

EXT15/P015 |

ExtData15/Port015 |

In/Output |

7 |

EXT3/P03 |

ExtData3/Port03 |

In/Output |

8 |

EXT4/P04 |

ExtData4/Port04 |

In/Output |

9 |

VSS |

Ground |

In/Output |

10 |

EXT5/P05 |

ExtData5/Port05 |

|

|

|

|

|

11 |

EXT6/P06 |

ExtData6/Port06 |

In/Output |

12 |

EXT7/P07 |

ExtData7/Port07 |

In/Output |

13 |

P21/INT1 |

Port21/Interrupt1 |

In/Output |

14 |

EXT8/P08 |

ExtData8/Port08 |

In/Output |

15 |

EXT9/P09 |

ExtData9/Port09 |

In/Output |

|

|

|

|

16 |

VSS |

Ground |

In/Output |

17 |

EXT10/P010 |

ExtData10/Port010 |

|

18 |

EXT11/P011 |

ExtData11/Port011 |

In/Output |

19 |

VAHI |

AnalogHighRef. |

Input |

20 |

VALO |

AnalogLowRef. |

Input |

21 |

ANGND |

AnalogGround |

Input |

22 |

AN0 |

A/DInput0 |

Input |

|

|

|

|

No. |

Symbol |

Function |

Direction |

|

|

|

|

23 |

AN1 |

A/DInput1 |

Input |

24 |

AN2 |

A/DInput2 |

Input |

25 |

AN3 |

A/DInput3 |

Input |

26 |

ANVCC |

AnalogPower |

Input |

27 |

V |

Power |

|

|

DD |

|

|

|

|

|

|

28 |

RD//WR |

R/WExternalBus |

Output |

29 |

EA0 |

ExtAddress0 |

Output |

30 |

EA1 |

ExtAddress1 |

Output |

31 |

EA2 |

ExtAddress2 |

Output |

32 |

P23/UO1 |

Port23/UserOutput1 |

In/Output |

|

|

|

|

33 |

/DS |

ExtDataStrobe |

Output |

34 |

CLKI |

Clock/CrystalIn |

Input |

35 |

CLKO |

Clock/CrystalOut |

Input |

36 |

P22/UO0 |

Port22/UserOutput0 |

In/Output |

37 |

P24/UO2 |

Port24/UserOutput2 |

In/Output |

|

|

|

|

38 |

WAIT |

WaitforExt |

Input |

39 |

/RES |

Reset |

Input |

40 |

V |

Ground |

|

41 |

SS |

ExtData0/Port00 |

In/Output |

EXT0/P00 |

|||

42 |

EXT1/P01 |

ExtData1/Port01 |

In/Output |

43 |

EXT2/P02 |

ExtData2/Port02 |

In/Output |

44 |

V |

Ground |

|

|

SS |

|

|

DS95DSP0101 Q4/95 |

3 |

P R E L I M I N A R Y |

Z89323/373/393 |

16-BIT DIGITAL SIGNAL PROCESSORS |

PIN DESCRIPTION (Continued)

|

|

|

|

NC |

|

EXT15/P015 |

VSS |

EXT14/P014 |

VDD |

EXT13/P013 |

EXT12/P012 |

P20/INT0 |

P12/SIN |

P11/CLKOUT |

VSS |

P10 |

|

EXT2/P02 |

|

EXT1/P01 |

EXT0/P00 |

VSS |

|

VDD |

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

9 |

|

8 |

|

7 |

|

6 |

|

5 |

|

4 |

|

3 |

|

2 |

|

1 |

|

68 |

67 |

66 |

65 |

64 |

63 |

62 |

61 |

|

|||||||||||||

|

|

|

|||||||||||||||||||||||||||||||||||||||

NC |

|

10 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

60 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

11 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

59 |

|||||

EXT3/P03 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

EXT4/P04 |

|

12 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

58 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

VSS |

|

13 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

57 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

VDD |

|

14 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

56 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

EXT5/P05 |

|

15 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

55 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

16 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

54 |

|||||

SOUT/P13 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

EXT6/P06 |

|

17 |

|

|

|

|

|

|

|

|

|

|

|

|

|

Z89323/373 |

|

|

|

|

|

|

|

|

|

|

|

|

|

53 |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

18 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

52 |

||||||||||||

SS/P14 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

68-Pin PLCC |

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

EXT7/P07 |

|

19 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

51 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

SK/P15 |

|

20 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

50 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

P27 |

|

21 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

49 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

EXT8/P08 |

|

22 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

48 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

EXT9/P09 |

|

23 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

47 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

24 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

46 |

|||||

VSS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

EXT10/P010 |

|

25 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

45 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

VSS |

|

26 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

44 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

27 |

28 |

29 |

30 |

31 |

32 |

33 |

34 |

35 |

36 |

37 |

38 |

39 |

40 |

41 |

42 |

43 |

|

||||||||||||||||||||||

|

|

|

|||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

EXT11/P011 |

|

VDD |

VAHI |

VSS |

UI0/P16 |

VALO |

UI1/P17 |

AGND |

AN0 |

AN1 |

AN2 |

AN3 |

|

VSS |

|

P21/INT1 |

ANVCC |

VDD |

|

RD//WR |

|||||||||||||||||

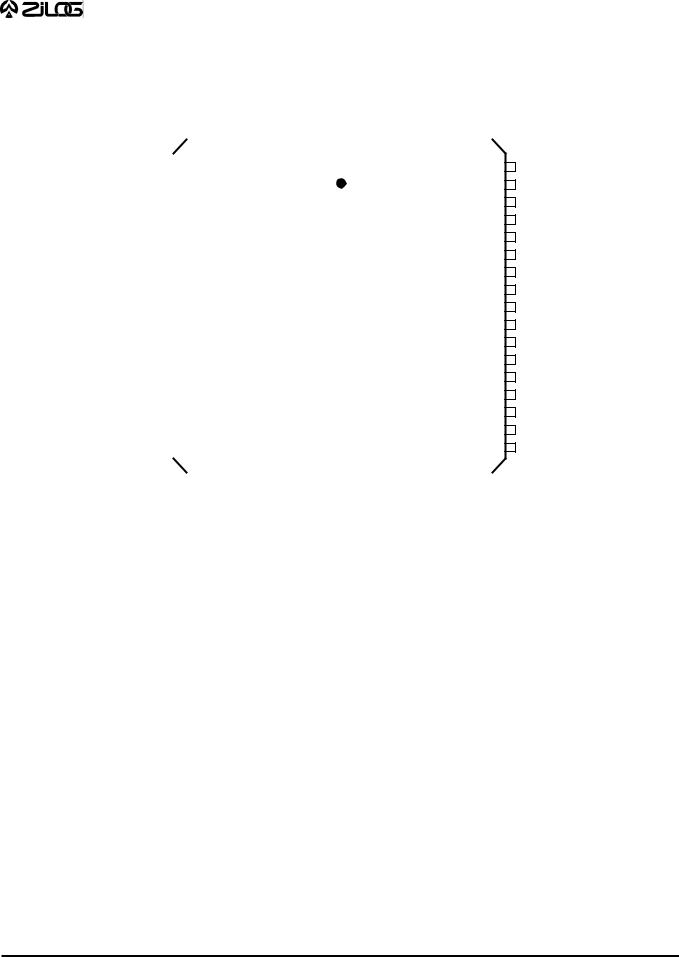

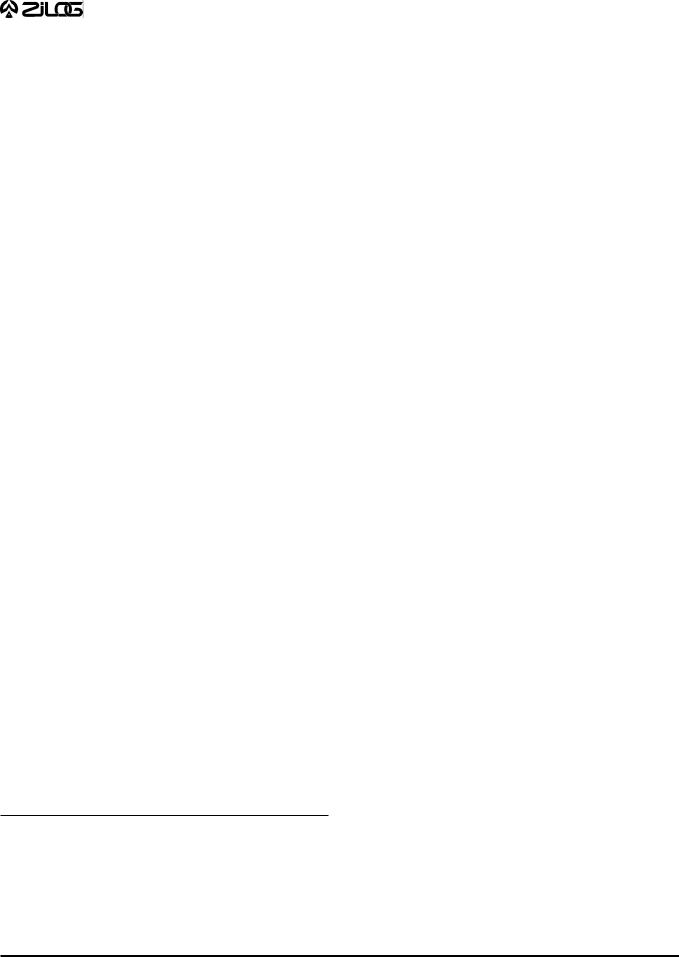

Figure 3. 68-Pin PLCC Z89323/373 Pin Configuration

VSS /RES WAIT P25/UI2 P22/UO0 P26 CLKO CLKI P24/UO2 /DS P23/UO1 VDD

NC

EA2

EA1

EA0

HALT

4 |

DS95DSP0101 Q4/95 |

P R E L I M I N A R Y |

Z89323/373/393 |

16-BIT DIGITAL SIGNAL PROCESSORS |

Table 2. 68-Pin PLCC Z89323/373 Pin Description

No. |

Symbol |

Function |

Direction |

|

|

|

|

1 |

P12/SIN |

Port12/SerialInput |

In/Output |

2 |

P20/INT0 |

Port20/Interrupt0 |

In/Output |

3 |

EXT12/P012 |

ExtData12/Port012 |

In/Output |

4 |

EXT13/P013 |

ExtData13/Port013 |

In/Output |

5 |

VDD |

Power |

|

|

|

|

|

6 |

EXT14/P014 |

ExtData14/Port014 |

In/Output |

7 |

VSS |

Ground |

In/Output |

8 |

EXT15/P015 |

ExtData15/Port015 |

|

9 |

NC |

NoConnection |

|

10 |

NC |

NoConnection |

|

|

|

|

|

11 |

EXT3/P03 |

ExtData3/Port03 |

In/Output |

12 |

EXT4/P04 |

ExtData4/Port04 |

In/Output |

13 |

VSS |

Ground |

|

14 |

VDD |

Power |

In/Output |

15 |

EXT5/P05 |

ExtData5/Port05 |

|

|

|

|

|

16 |

P13/SOUT |

Port13/SerialOutput |

In/Output |

17 |

EXT6/P06 |

ExtData6/Port06 |

In/Output |

18 |

P14/SS |

Port14/SerialSelect |

In/Output |

19 |

EXT7/P07 |

ExtData7/Port07 |

In/Output |

20 |

P15/SK |

Port15/SerialClock |

In/Output |

|

|

|

|

21 |

P27 |

Port27 |

In/Output |

22 |

EXT8/P08 |

ExtData8/Port08 |

In/Output |

23 |

EXT9/P09 |

ExtData9/Port09 |

In/Output |

24 |

VSS |

Ground |

|

25 |

EXT10/P010 |

ExtData10/Port010 |

In/Output |

26 |

VSS |

Ground |

In/Output |

27 |

EXT11/P011 |

ExtData11/Port011 |

|

28 |

VDD |

Power |

Input |

29 |

VAHI |

AnalogHighRef. |

|

|

|

|

|

30 |

VSS |

Ground |

In/Output |

31 |

P16/UI0 |

Port16/UserInput0 |

|

32 |

VALO |

AnalogLowRef. |

Input |

33 |

P17/UI1 |

Port17/UserInput1 |

In/Output |

34 |

ANGND |

AnalogGround |

Input |

|

|

|

|

No. |

Symbol |

Function |

Direction |

|

|

|

|

35 |

AN0 |

A/DInput0 |

Input |

36 |

AN1 |

A/DInput1 |

Input |

37 |

AN2 |

A/DInput2 |

Input |

38 |

AN3 |

A/DInput3 |

Input |

39 |

VSS |

Ground |

|

40 |

P21/INT1 |

Port21/Interrupt1 |

In/Output |

41 |

ANVCC |

AnalogPower |

Input |

42 |

VDD |

Power |

Input |

43 |

RD//WR |

R/WExternalBus |

Output |

44 |

HALT |

HaltExecution |

Input |

|

|

|

|

45 |

EA0 |

ExtAddress0 |

Output |

46 |

EA1 |

ExtAddress1 |

Output |

47 |

EA2 |

ExtAddress2 |

Output |

48 |

NC |

NoConnection |

|

49 |

VDD |

Power |

|

50 |

P23/UO1 |

Port23/UserOutput1 |

In/Output |

51 |

/DS |

ExtDataStrobe |

Output |

52 |

P24/UO2 |

Port24/UserOutput2 |

In/Output |

53 |

CLKI |

Clock/CrystalIn |

Input |

54 |

CLKO |

Clock/CrystalOut |

Input |

|

|

|

|

55 |

P26 |

Port26 |

In/Output |

56 |

P22/UO0 |

Port22/UserOutput0 |

In/Output |

57 |

P25/UI2 |

Port25/UserInput2 |

In/Output |

58 |

WAIT |

WaitforExt |

Input |

|

|

|

|

59 |

/RES |

Reset |

Input |

60 |

VSS |

Ground |

|

61 |

VDD |

Power |

|

62 |

VSS |

Ground |

In/Output |

63 |

EXT0/P00 |

ExtData0/Port00 |

|

|

|

|

|

64 |

EXT1/P01 |

ExtData1/Port01 |

In/Output |

65 |

EXT2/P02 |

ExtData2/Port02 |

In/Output |

66 |

P10/INT2 |

Port10/Interrupt2 |

In/Output |

67 |

VSS |

Ground |

In/Output |

68 |

P11/CLKOUT |

Port11/ClockOutput |

|

|

|

|

|

DS95DSP0101 Q4/95 |

5 |

P R E L I M I N A R Y |

Z89323/373/393 |

16-BIT DIGITAL SIGNAL PROCESSORS |

PIN DESCRIPTION (Continued)

|

|

|

|

|

EXT15/P015 |

|

VSS |

|

EXT14/P014 |

|

EXT13/P013 |

|

EXT12/P012 |

|

P20/INT0 |

|

VSS |

|

EXT2/P02 |

|

EXT1/P01 |

|

EXT0/P00 |

|

VSS |

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

44 |

43 |

42 |

41 |

40 |

39 38 |

|

37 |

36 |

35 |

34 |

|

|

|

|

|

||||||||||||||||

EXT3/P03 |

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

33 |

|

|

|

/RES |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

EXT4/P04 |

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

32 |

|

|

|

WAIT |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

VSS |

|

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

31 |

|

|

|

P24/UO2 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

EXT5/P05 |

|

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

30 |

|

|

|

P22/UO0 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

EXT6/P06 |

|

5 |

|

|

|

|

|

|

Z89323/373 |

|

|

|

|

|

|

29 |

|

|

|

CLK0 |

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

EXT7/P07 |

|

|

|

6 |

|

|

|

|

|

|

|

|

|

|

|

|

28 |

|

|

|

CLK1 |

|||||||||||

|

|

|

|

|

|

|

|

|

44-Pin QFP |

|

|

|

|

|

|

|

|

|

||||||||||||||

INT1/P21 |

|

|

|

7 |

|

|

|

|

|

|

|

|

|

|

|

|

27 |

|

|

|

/DS |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

EXT8/P08 |

|

8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

26 |

|

|

|

P23/UO1 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

EXT9/P09 |

|

9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

25 |

|

|

|

EA2 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

VSS |

|

10 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

24 |

|

|

|

EA1 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

EXT10/P010 |

|

11 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

23 |

|

|

|

EA0 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

12 |

13 |

14 |

15 |

16 |

|

17 |

18 |

|

19 |

20 |

21 |

22 |

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

EXT11/P011 |

|

VAHI |

|

VALO |

|

ANGND |

|

AN0 |

|

AN1 |

|

AN2 |

|

AN3 |

|

ANVCC |

|

VDD |

|

RD//WR |

|

|

|

|

|||

Figure 4. 44-Pin QFP Z89323/373 Pin Configuration

Table 3. 44-Pin QFP Z89323/373 Pin Description

No. |

Symbol |

Function |

Direction |

|

|

|

|

1 |

EXT3/P03 |

ExtData3/Port03 |

In/Output |

2 |

EXT4/P04 |

ExtData4/Port04 |

In/Output |

3 |

VSS |

Ground |

In/Output |

4 |

EXT5/P05 |

ExtData5/Port05 |

|

5 |

EXT6/P06 |

ExtData6/Port06 |

In/Output |

|

|

|

|

6 |

EXT7/P07 |

ExtData7/Port07 |

In/Output |

7 |

P21/INT1 |

Port21/Interrupt1 |

In/Output |

8 |

EXT8/P08 |

ExtData8/Port08 |

In/Output |

9 |

EXT9/P09 |

ExtData9/Port09 |

In/Output |

10 |

VSS |

Ground |

|

11 |

EXT10/P010 |

ExtData10/Port010 |

In/Output |

12 |

EXT11/P011 |

ExtData11/Port011 |

In/Output |

13 |

VAHI |

AnalogHighRef. |

Input |

14 |

VALO |

AnalogLowRef. |

Input |

15 |

ANGND |

AnalogGround |

Input |

16 |

AN0 |

A/DInput0 |

Input |

|

|

|

|

17 |

AN1 |

A/DInput1 |

Input |

18 |

AN2 |

A/DInput2 |

Input |

19 |

AN3 |

A/DInput3 |

Input |

20 |

ANVCC |

AnalogPower |

Input |

21 |

VDD |

Power |

Output |

22 |

RD//WR |

R/WExternalBus |

|

|

|

|

|

No. |

Symbol |

Function |

Direction |

|

|

|

|

23 |

EA0 |

ExtAddress0 |

Output |

24 |

EA1 |

ExtAddress1 |

Output |

25 |

EA2 |

ExtAddress2 |

Output |

26 |

P23/UO1 |

Port23/UserOutput1 |

In/Output |