Sharp LH5164AT-80L, LH5164AT-10L, LH5164AN-80L, LH5164AN-10L, LH5164AHT-10L Datasheet

...

LH5164A/AH |

CMOS 64K (8K × 8) Static RAM |

FEATURES

∙8,192 × 8 bit organization

∙Access times: 80/100 ns (MAX.)

∙Low-power consumption: Operating:

303 mW (MAX.) LH5164A/D/N

@80 ns

248 mW (MAX.) LH5164A/D/N/T @ 100 ns

275 mW (MAX.) LH5164AH/HD/HN/HT @ 100 ns

Standby:

LH5164A/D/N/T: 5.5 μW (MAX.) LH5164AH/HD/HN/HT:

TA ≤ 85°C: 16.5 μW (MAX.)

TA ≤ 70°C: 5.5 μW (MAX.)

∙Fully-static operation

∙Three-state outputs

∙Single +5 V power supply

∙TTL compatible I/O

∙Wide temperature range available LH5164A: -10 to +70°C LH5164AH: -40 to +85°C

∙Packages:

28-pin, 600-mil DIP

28-pin, 300-mil SK-DIP

28-pin, 450-mil SOP

28-pin, 8 × 13 mm2 TSOP (Type I)

DESCRIPTION

The LH5164A/AH are static RAMs organized as 8,192 × 8 bits. It is fabricated using silicon-gate CMOS process technology.

The LH5164AH is designed for wide temperature range from -40 to +85°C.

PIN CONNECTIONS

28-PIN DIP |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TOP VIEW |

|

28-PIN SK-DIP |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

28-PIN SOP |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

NC |

|

|

1 |

28 |

|

|

VCC |

|||||||||

|

|

|

|

|||||||||||||

|

|

|

||||||||||||||

A12 |

|

|

|

|

2 |

27 |

|

|

WE |

|

||||||

|

|

|

|

|

||||||||||||

|

|

|

|

|

||||||||||||

A7 |

|

|

|

|

3 |

26 |

|

CE2 |

||||||||

|

|

|

|

|

||||||||||||

A6 |

|

|

|

|

|

4 |

25 |

|

A8 |

|||||||

|

|

|

|

|

|

|||||||||||

A5 |

|

|

|

|

|

5 |

24 |

|

A9 |

|||||||

|

|

|

|

|

|

|||||||||||

A4 |

|

|

|

|

6 |

23 |

|

A11 |

||||||||

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|||||||||||

A3 |

|

|

|

|

|

7 |

22 |

|

|

OE |

|

|

|

|||

|

|

|

|

|

|

|||||||||||

A2 |

|

|

|

8 |

21 |

|

A10 |

|||||||||

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

A1 |

|

|

|

|

|

9 |

20 |

|

CE1 |

|||||||

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|||||||||||

A0 |

|

|

|

|

10 |

19 |

|

I/O8 |

||||||||

|

|

|

|

|

||||||||||||

I/O1 |

|

|

11 |

18 |

|

I/O7 |

||||||||||

|

|

|

|

|

|

|

||||||||||

I/O2 |

|

|

12 |

17 |

|

I/O6 |

||||||||||

|

|

|||||||||||||||

|

|

|

|

|

|

|

||||||||||

I/O3 |

|

|

13 |

16 |

|

I/O5 |

||||||||||

|

|

|||||||||||||||

|

|

|

|

|

|

|

||||||||||

GND |

|

|

14 |

15 |

|

I/O4 |

||||||||||

|

|

|

||||||||||||||

|

|

|

|

|

|

|

||||||||||

5164A-1

Figure 1. Pin Connections for DIP, SK-DIP, and SOP Packages

28-PIN TSOP (Type I) |

TOP VIEW |

|||||||||||

|

|

|

|

|

|

|

28 |

|

|

|

||

|

OE |

|

|

1 |

|

|

A10 |

|||||

|

|

|

|

|||||||||

|

|

|

|

|||||||||

|

A11 |

|

|

|

2 |

27 |

|

|

|

|

|

|

|

|

|

|

|

CE1 |

|||||||

|

|

|

|

|||||||||

|

A9 |

|

|

3 |

26 |

|

|

I/O8 |

||||

|

|

|||||||||||

|

A8 |

|

|

|

4 |

25 |

|

|

I/O7 |

|||

|

|

|

||||||||||

CE2 |

|

|

|

5 |

24 |

|

|

I/O6 |

||||

|

|

|

||||||||||

|

|

|

|

|

|

6 |

23 |

|

|

I/O5 |

||

WE |

|

|

|

|

|

|||||||

|

|

|

|

|||||||||

VCC |

|

|

7 |

22 |

|

|

I/O4 |

|||||

|

|

|

|

|

||||||||

|

|

|

|

|||||||||

|

NC |

|

|

8 |

21 |

|

|

GND |

||||

|

A12 |

|

|

9 |

20 |

|

|

I/O3 |

||||

|

|

|

|

|||||||||

|

|

|

||||||||||

|

A7 |

|

|

|

10 |

19 |

|

|

I/O2 |

|||

|

|

|

|

|||||||||

|

A6 |

|

|

|

11 |

18 |

|

|

I/O1 |

|||

|

|

|

|

|||||||||

|

A5 |

|

|

|

12 |

17 |

|

|

A0 |

|||

|

|

|

|

|||||||||

|

A4 |

|

|

13 |

16 |

|

|

A1 |

||||

|

|

|

|

|

|

|||||||

|

A3 |

|

|

14 |

15 |

|

|

A2 |

||||

|

|

|

|

|

||||||||

|

|

|

|

|

||||||||

5164A-8

Figure 2. Pin Connections for TSOP Package

1

LH5164A/AH |

|

|

|

|

|

CMOS 64K (8K × 8) Static RAM |

|

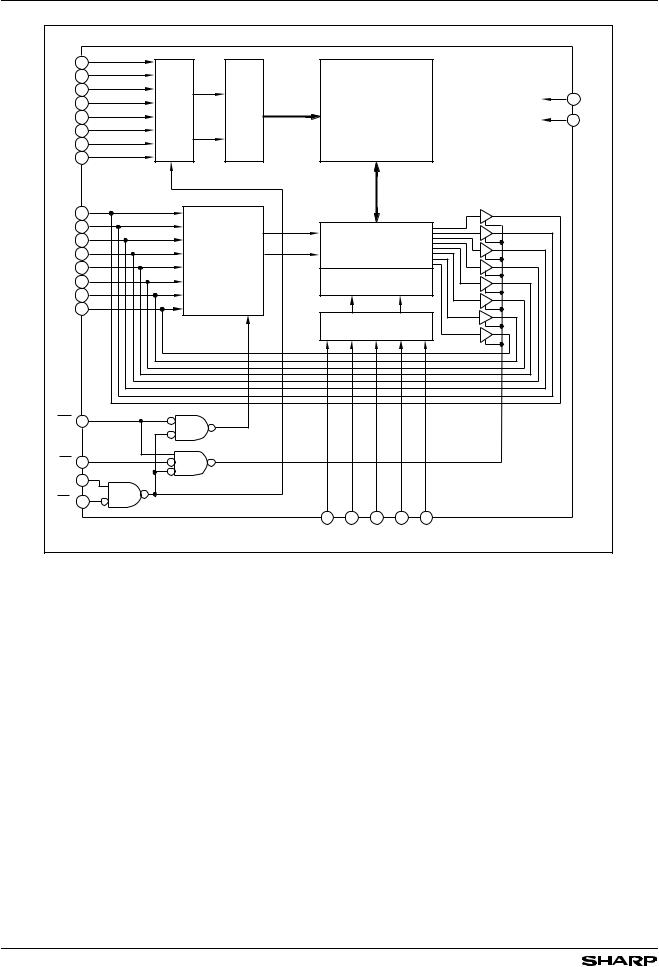

A3 |

7 |

ADDRESSROW BUFFERS |

DECODERSROW |

|

|

|

|

A9 |

24 |

|

|

|

|

||

A4 |

6 |

|

|

|

|

|

|

A5 |

5 |

|

|

MEMORY |

|

28 VCC |

|

A6 |

4 |

|

|

|

|||

A7 |

3 |

|

|

|

ARRAY |

|

14 GND |

|

|

(256 x 256) |

|||||

A8 |

25 |

|

|

|

|

|

|

A12 |

2 |

|

|

|

|

|

|

I/O1 |

11 |

|

|

|

|

|

|

I/O2 |

12 |

|

|

|

|

|

|

I/O3 |

13 |

|

|

|

I/O |

|

|

I/O4 |

15 |

|

DATA CONTROL |

CIRCUITS |

|

||

I/O5 |

16 |

|

|

|

|

|

|

|

|

|

|

|

|

||

I/O6 |

17 |

|

COLUMN DECODERS |

||||

I/O7 |

18 |

|

|

|

|

|

|

I/O8 |

19 |

|

|

|

|

|

|

|

|

|

|

COLUMN ADDRESS |

|

||

|

|

|

|

|

BUFFER |

|

|

WE 27 |

|

|

|

|

|

|

|

OE 22 |

|

|

|

|

|

|

|

CE2 |

26 |

|

|

|

|

|

|

CE1 |

20 |

|

|

|

|

|

|

|

|

|

10 |

9 |

8 |

21 |

23 |

|

|

|

A0 |

A1 |

A2 |

A10 |

A11 |

NOTE: Pin numbers apply to 28-pin DIP, SK-DIP, or SOP. |

|

|

|

5164A-2 |

|||

|

|

|

|

|

|

|

|

Figure 3. LH5164A/AH Block Diagram

PIN DESCRIPTION

SIGNAL |

PIN NAME |

SIGNAL |

PIN NAME |

A0 - A12 |

Address inputs |

I/O1 - I/O8 |

Data inputs and outputs |

CE1 - CE2 |

Chip Enable input |

VCC |

Power supply |

WE |

Write Enable input |

GND |

Ground |

OE |

Output Enable input |

NC |

No connection |

TRUTH TABLE

|

|

|

|

|

|

|

|

|

|

|

CE1 |

CE2 |

WE |

OE |

MODE |

I/O1 - I/O8 |

SUPPLY CURRENT |

NOTE |

|||

H |

X |

X |

|

X |

Deselect |

High-Z |

Standby (ISB) |

1 |

||

X |

L |

X |

|

X |

Deselect |

High-Z |

Standby (ISB) |

1 |

||

L |

H |

L |

|

X |

Write |

DIN |

Operating (ICC) |

1 |

||

L |

H |

H |

|

L |

Read |

DOUT |

Operating (ICC) |

|

||

L |

H |

H |

|

H |

Output disable |

High-Z |

Operating (ICC) |

|

||

NOTE:

1. X = H or L

2

CMOS 64K (8K × 8) Static RAM LH5164A/AH

ABSOLUTE MAXIMUM RATINGS

PARAMETER |

SYMBOL |

80 ns |

100 ns |

UNIT |

NOTE |

|

RATING |

RATING |

|||||

|

|

|

|

|||

Supply voltage |

VCC |

-0.3 to +7.0 |

-0.3 to +7.0 |

V |

1 |

|

Input voltage |

VIN |

-0.3 to VCC + 0.3 |

-0.3 to VCC + 0.3 |

V |

1, 2 |

|

Operating temperature |

Topr |

-10 to +70 |

-10 to +70 |

°C |

3 |

|

|

-40 to +85 |

°C |

4 |

|||

|

|

|

||||

Storage temperature |

Tstg |

-55 to +150 |

-55 to +150 |

°C |

|

NOTES:

1.The maximum applicable voltage on any pin with respect to GND.

2.VIN (MIN.) = -3.0 V for pulse width £50 ns.

3.LH5164A/AD/AN/AT

4.LH5164AH/AHD/AHN/AHT

RECOMMENDED OPERATING CONDITIONS 1

PARAMETER |

SYMBOL |

|

80 ns |

|

|

100 ns |

|

UNIT |

NOTE |

|

MIN. |

TYP. |

MAX. |

MIN. |

TYP. |

MAX. |

|||||

|

|

|

|

|||||||

Supply voltage |

VCC |

4.5 |

5.0 |

5.5 |

4.5 |

5.0 |

5.5 |

V |

|

|

Input voltage |

VIH |

2.2 |

|

VCC + 0.3 |

2.2 |

|

VCC + 0.3 |

V |

|

|

VIL |

-0.3 |

|

0.8 |

-0.3 |

|

0.8 |

V |

2 |

||

|

|

|

NOTES:

1.TA = -10 to +70°C (LH5164A/AD/AN/AT), TA = -40 to +85°C (LH5164AH/AHD/AHN/AHT).

2.VIN (MIN.) = -3.0 V for pulse width £50 ns.

DC CHARACTERISTICS 1 |

(VCC = 5 V ±10%) |

|

|

|

|

|

|

PARAMETER |

SYMBOL |

CONDITIONS |

|

MIN. |

MAX. |

UNIT |

NOTE |

Input leakage current |

ILI |

VIN = 0 to VCC |

|

-1.0 |

1.0 |

mA |

|

Output leakage |

|

CE1 = VIH or CE2 = VIL |

|

|

mA |

|

|

ILO |

or OE = VIH or WE = VIL |

-1.0 |

1.0 |

|

|||

current |

|

||||||

|

VI/O = 0 to VCC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CE1 = VIL, VIN = VIL or VIH |

tCYCLE = |

|

55 |

mA |

|

|

|

CE2 = VIH, Outputs open |

80 ns |

|

|

|

|

Operating current |

ICC |

CE1 = VIL, VIN = VIL or VIH |

tCYCLE = |

|

45 |

|

2 |

CE2 = VIH, Outputs open |

100 ns |

|

50 |

mA |

3 |

||

|

|

CE1 = VIL, VIN = 0.2 V or |

tCYCLE = |

|

|

|

|

|

|

|

|

|

|

||

|

|

VCC - 0.2 V |

|

10 |

|

|

|

|

|

1.0 ms |

|

|

|

||

|

|

CE2 = VIH, Outputs open |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CE1 = VIH or CE2 = VIL |

|

5 |

mA |

|

|

Standby current |

ISB1 |

CE2 £ 0.2 V or |

TA £ 70°C |

|

1.0 |

mA |

2, 3, 4 |

|

|

CE1 ³ VCC - 0.2 V |

TA £ 85°C |

|

3.0 |

mA |

3, 4 |

Output voltage |

VOL |

IOL = 2.1 mA |

|

|

0.4 |

V |

|

VOH |

IOH = -1 mA |

|

2.4 |

|

V |

|

|

|

|

|

|

||||

NOTES:

1.TA = -10 to 70°C (LH5164A/AD/AN/AT), TA = -40 to +85°C (LH5164AH/AHD/AHN/AHT)

2.LH5164A/AD/AN/AT

3.LH5164AH/AHD/AHN/AHT

4.CE2 should be ³ VCC – 0.2 V or £ 0.2 V when CE1 ³ VCC – 0.2 V

3

LH5164A/AH CMOS 64K (8K × 8) Static RAM

AC CHARACTERISTICS 1

(1) READ CYCLE (VCC = 5 V ±10%)

PARAMETER |

|

SYMBOL |

|

80 ns |

|

100 ns |

UNIT |

NOTE |

|

MIN. |

MAX. |

MIN. |

MAX. |

||||

|

|

|

|

|

||||

Read cycle time |

|

tRC |

80 |

|

100 |

|

ns |

|

Address access time |

|

tAA |

|

80 |

|

100 |

ns |

|

Chip enable |

(CE1) |

tACE1 |

|

80 |

|

100 |

ns |

|

access time |

(CE2) |

tACE2 |

|

80 |

|

100 |

ns |

|

|

|

|

|

|||||

Output enable access time |

tOE |

|

40 |

|

40 |

ns |

|

|

Output hold time |

|

tOH |

10 |

|

10 |

|

ns |

|

Chip enable to |

(CE1) |

tLZ1 |

10 |

|

10 |

|

ns |

1 |

output in Low-Z |

(CE2) |

tLZ2 |

10 |

|

10 |

|

ns |

1 |

|

|

|

||||||

Output enable to output in |

tOLZ |

5 |

|

5 |

|

ns |

1 |

|

Low-Z |

|

|

|

|||||

Chip enable to |

(CE1) |

tHZ1 |

0 |

30 |

0 |

30 |

ns |

1 |

output in High-Z |

(CE2) |

tHZ2 |

0 |

30 |

0 |

30 |

ns |

1 |

|

||||||||

Output disable to output in |

tOHZ |

0 |

20 |

0 |

20 |

ns |

1 |

|

High-Z |

|

|||||||

|

|

|

|

|

|

|

|

|

(2) WRITE CYCLE (VCC = 5 V ±10%)

PARAMETER |

SYMBOL |

80 ns |

|

|

100 ns |

UNIT |

NOTE |

|

MIN. |

MAX. |

MIN. |

MAX. |

|||||

|

|

|

|

|||||

Write cycle time |

tWC |

80 |

|

100 |

|

ns |

|

|

Chip enable to end of write |

tCW |

70 |

|

80 |

|

ns |

|

|

Address valid to end of write |

tAW |

70 |

|

80 |

|

ns |

|

|

Address setup time |

tAS |

0 |

|

0 |

|

ns |

|

|

Write pulse width |

tWP |

60 |

|

60 |

|

ns |

|

|

Write recovery time |

tWR |

0 |

|

0 |

|

ns |

|

|

Data valid to end of write |

tDW |

40 |

|

40 |

|

ns |

|

|

Data hold time |

tDH |

0 |

|

0 |

|

ns |

|

|

Output active from end of write |

tOW |

10 |

|

10 |

|

ns |

2 |

|

WE to output in High-Z |

tWZ |

0 |

30 |

0 |

30 |

ns |

2 |

|

OE to output in High-Z |

tOHZ |

0 |

20 |

0 |

20 |

ns |

2 |

NOTES:

1.TA = -10 to +70°C (LH5164A/AD/AN/AT), TA = -40 to +85°C (LH5164AH/AHD/AHN/AHT)

2.Active output to high-impedance and high-impedance to output active tests specified for a ±200 mV transition from steady state levels into the test load.

AC TEST CONDITIONS

PARAMETER |

MODE |

NOTE |

Input voltage amplitude |

0.6 to 2.4 V |

|

Input rise/fall time |

10 ns |

|

Timing reference level |

1.5 V |

|

Output load conditions |

1TTL + CL (100 pF) |

1 |

NOTE:

1. Includes scope and jig capacitance.

4

Loading...

Loading...