Sharp LH5P8128TR-80, LH5P8128TR-60, LH5P8128T-80, LH5P8128T-60, LH5P8128T-10 Datasheet

...

LH5P8128 |

CMOS 1M (128K × 8) Pseudo-Static RAM |

FEATURES

∙131,072 × 8 bit organization

∙Access times (MAX.): 60/80/100 ns

∙Cycle times (MIN.): 100/130/160 ns

∙Single +5 V power supply

∙Power consumption:

Operating: 572/385/275 mW (MAX.) Standby (CMOS level): 1.1 mW (MAX.)

∙TTL compatible I/O

∙Available for auto-refresh and self-refresh modes

∙512 refresh cycles/8 ms

∙Compatible with standard 1M SRAM pinout

∙Packages:

32-pin, 600-mil DIP

32-pin, 525-mil SOP

32-pin, 8 × 20 mm2 TSOP (Type I)

DESCRIPTION

The LH5P8128 is a 1M bit Pseudo-Static RAM organized as 131,072 × 8 bits. It is fabricated using silicon-gate CMOS process technology.

A PSRAM uses on-chip refresh circuitry with a DRAM memory cell for pseudo static operation which eliminates external clock inputs, while having the same pinout as industry standard SRAMs. Moreover, due to the functional similarities between PSRAMs and SRAMs, existing 128K × 8 SRAM sockets can be filled with the LH5P8128 with little or no changes. The advantage is the cost savings realized with the lower cost PSRAM.

The LH5P8128 PSRAM has the ability to fill the gap between DRAM and SRAM by offering low cost, low power standby and a simple interface.

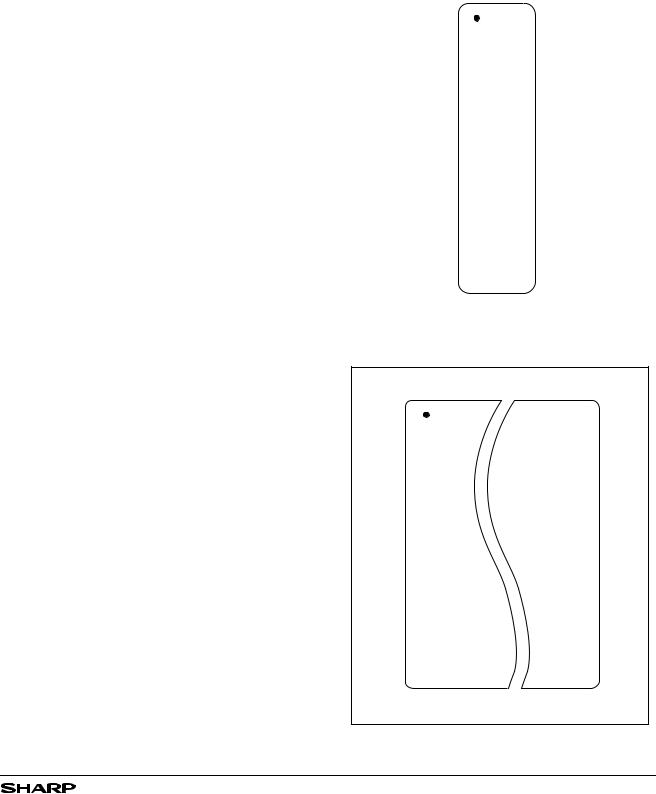

PIN CONNECTIONS

32-PIN DIP |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TOP VIEW |

|||||||||||||

32-PIN SOP |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

RFSH |

|

|

1 |

32 |

|

|

|

VCC |

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

A16 |

|

|

|

|

2 |

31 |

|

|

|

A15 |

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

A14 |

|

|

|

3 |

30 |

|

|

|

CE2 |

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

A12 |

|

|

|

|

4 |

29 |

|

|

|

R/W |

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

A7 |

|

|

|

5 |

28 |

|

|

|

A13 |

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

A6 |

|

|

|

|

6 |

27 |

|

|

|

A8 |

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

A5 |

|

|

|

|

7 |

26 |

|

|

|

A9 |

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

A4 |

|

|

|

|

|

8 |

25 |

|

|

|

A11 |

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

A3 |

|

|

|

|

|

9 |

24 |

|

|

|

OE |

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

A2 |

|

|

|

|

10 |

23 |

|

|

|

A10 |

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

22 |

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

A1 |

|

|

|

|

|

11 |

|

|

|

CE1 |

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

A0 |

|

|

|

12 |

21 |

|

|

|

I/O7 |

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

I/O0 |

|

|

|

|

13 |

20 |

|

|

|

I/O6 |

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

I/O1 |

|

|

|

|

14 |

19 |

|

|

|

I/O5 |

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

I/O2 |

|

|

15 |

18 |

|

|

|

I/O4 |

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

GND |

|

17 |

|

|

|

I/O3 |

|

|

5P8128-1 |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

16 |

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

Figure 1. Pin Connections for DIP and |

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SOP Packages |

|

|

|

|

|

|

|

||||||||

32-PIN TSOP (Type I) |

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

|

A11 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

32 |

|

|

|

|

||||

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

OE |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

A9 |

|

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

31 |

|

|

A10 |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

A8 |

|

|

|

|

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

30 |

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CE1 |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

A13 |

|

|

|

|

|

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

29 |

|

|

I/O7 |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

R/W |

|

|

|

|

5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

28 |

|

|

I/O6 |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

CE2 |

|

|

|

|

6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

27 |

|

|

I/O5 |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

A15 |

|

|

|

|

7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

26 |

|

|

I/O4 |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

VCC |

|

|

|

|

|

8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

25 |

|

|

I/O3 |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

RFSH |

|

|

|

|

9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

24 |

|

|

GND |

||||||||

|

A16 |

|

|

|

|

10 |

|

|

|

|

|

|

|

|

|

|

|

|

|

23 |

|

|

I/O2 |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

A14 |

|

|

|

|

11 |

|

|

|

|

|

|

|

|

|

|

|

|

|

22 |

|

|

I/O1 |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

A12 |

|

|

|

|

12 |

|

|

|

|

|

|

|

|

|

|

|

|

|

21 |

|

|

I/O0 |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

A7 |

|

|

13 |

|

|

|

|

|

|

|

|

|

|

|

|

|

20 |

|

|

A0 |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

A6 |

|

|

|

|

14 |

|

|

|

|

|

|

|

|

|

|

|

|

|

19 |

|

|

A1 |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

A5 |

|

|

15 |

|

|

|

|

|

|

|

|

|

|

|

|

|

18 |

|

|

A2 |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

A4 |

|

|

16 |

|

|

|

|

|

|

|

|

|

|

|

|

|

17 |

|

|

A3 |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

NOTE: Reverse bend available on request.

5P8128-1A

Figure 2. Pin Connections for TSOP Package

1

LH5P8128 |

|

|

|

|

CMOS 1M (128K × 8) Pseudo-Static RAM |

|||

|

|

|

|

|

|

|

|

16 GND |

|

|

|

|

|

|

|

|

32 VCC |

A0 12 |

|

|

|

|

VBB GENERATOR |

|

||

A1 11 |

|

|

|

|

|

|

|

|

A2 10 |

|

|

|

|

|

|

|

|

A3 |

9 |

COLUMN |

|

|

|

|

|

|

A4 |

8 |

ADDRESS |

|

|

COLUMN |

|

|

|

BUFFER |

|

|

|

|

|

|||

A5 |

7 |

|

|

DECODER |

|

|

|

|

|

|

|

|

|

|

|

||

A6 |

6 |

|

|

|

|

|

|

|

A7 |

5 |

|

|

|

SENSE |

I/O |

DATA |

13 I/O0 |

A8 27 |

|

|

|

IN |

||||

ROW |

|

|

AMPS |

SELECTOR |

14 I/O1 |

|||

A9 |

26 |

|

|

BUFFER |

||||

ADDRESS |

|

|

|

|

|

15 I/O2 |

||

A10 |

23 |

|

|

|

|

|

||

BUFFER |

|

|

|

|

|

17 I/O3 |

||

A11 25 |

|

|

|

|

|

|||

|

EXT/INT |

|

|

|

|

18 I/O4 |

||

A12 |

4 |

|

ROW |

MEMORY |

|

|

||

REFRESH |

ADDRESS |

|

|

19 I/O5 |

||||

A13 |

28 |

DECODER |

ARRAY |

|

|

|||

ADDRESS |

MUX |

|

|

20 I/O6 |

||||

A14 |

3 |

COUNTER |

|

|

|

|

DATA |

21 I/O7 |

A15 31 |

|

|

|

|

|

|||

|

|

|

|

|

OUT |

|

||

A16 |

2 |

|

|

|

|

|

BUFFER |

|

CE1 |

22 |

CLOCK |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CE2 30 |

GENERATOR |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

REFRESH |

REFRESH |

|

|

|

|

|

|

|

CONTROLLER |

TIMER |

|

|

|

RFSH 1 |

|

|

|

|

|

|

|

|

OE 24 |

|

|

|

|

|

|

|

|

R/W 29 |

|

|

|

|

|

|

|

|

NOTE: Pin numbers apply to the 32-pin DIP or SOP.

5P8128-2

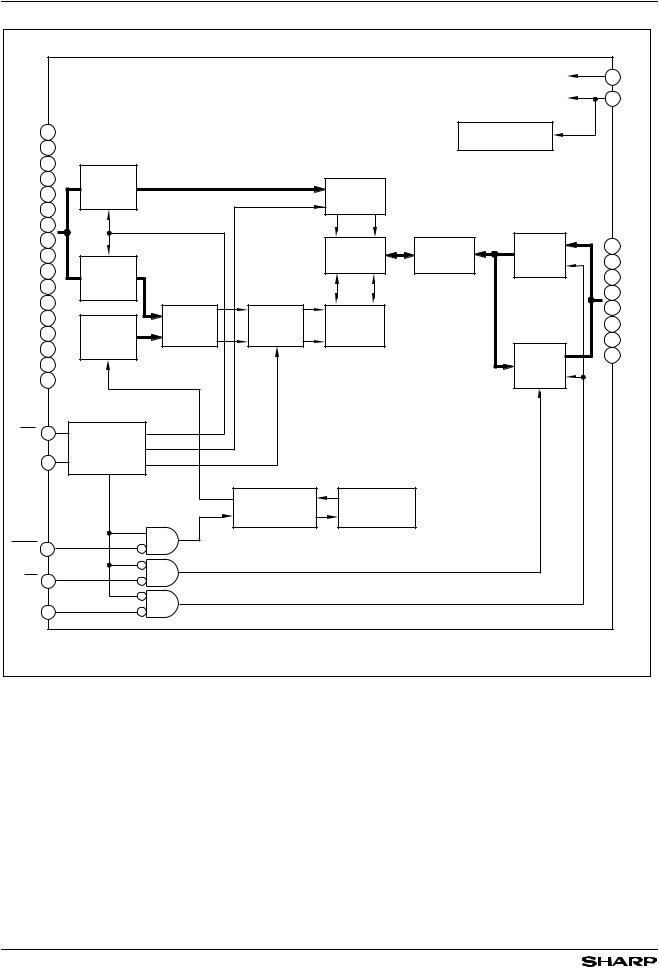

Figure 3. LH5P8128 Block Diagram

PIN DESCRIPTION

SIGNAL |

PIN NAME |

SIGNAL |

PIN NAME |

A0 - A16 |

Address input |

CE1, CE2 |

Chip Enable input |

R/W |

Read/Write input |

RFSH |

Refresh input |

OE |

Output Enable Input |

I/O0 - I/O7 |

Data input/output |

2

CMOS 1M (128K × 8) Pseudo-Static RAM |

LH5P8128 |

|

|

ABSOLUTE MAXIMUM RATINGS

PARAMETER |

SYMBOL |

RATING |

UNIT |

NOTE |

Applied voltage on any pins |

VT |

-1.0 to +7.0 |

V |

1 |

Output short circuit current |

IO |

50 |

mA |

|

Power dissipation |

PD |

600 |

mW |

|

Operating temperature |

Topr |

0 to +70 |

°C |

|

Storage temperature |

Tstg |

-55 to +150 |

°C |

|

NOTE:

1. The maximum applicable voltage on any pin with respect to GND.

RECOMMENDED OPERATING CONDITIONS (TA = 0 to +70°C)

PARAMETER |

SYMBOL |

MIN. |

TYP. |

MAX. |

UNIT |

|

Supply voltage |

VCC |

4.5 |

5.0 |

5.5 |

V |

|

GND |

0 |

0 |

0 |

V |

||

|

||||||

Input voltage |

VIH |

2.4 |

|

VCC + 0.3 |

V |

|

VIL |

-1.0 |

|

0.8 |

V |

||

|

|

CAPACITANCE (TA = 0 to +70°C, f = 1MHz, VCC = 5.0 V ±10%)

PARAMETER |

CONDITIONS |

SYMBOL |

MIN. |

MAX. |

UNIT |

|

A0 - A16 |

CIN1 |

|

8 |

pF |

Input capacitance |

R/W, OE |

CIN2 |

|

5 |

pF |

CE1, CE2 |

CIN3 |

|

5 |

pF |

|

|

|

||||

|

RFSH |

CIN4 |

|

5 |

pF |

Input/output capacitance |

I/O0 - I/O7 |

COUT1 |

|

10 |

pF |

DC CHARACTERISTICS (TA = 0 to +70°C, VCC = 5.0 V ±10%)

PARAMETER |

|

SYMBOL |

|

|

LH5P8128-60 |

|

|

Operating current |

LH5P8128-80 |

ICC1 |

|

|

LH5P8128-10 |

|

|

Standby current |

TTL Input |

ICC2 |

|

CMOS Input |

|||

|

|

||

Self-refresh average |

TTL Input |

ICC3 |

|

current |

CMOS Input |

||

|

|||

|

|

||

Input leakage current |

|

ILI |

|

I/O leakage current |

|

ILO |

|

Output HIGH voltage |

|

VOH |

|

Output LOW voltage |

|

VOL |

NOTES:

1.Specified values are with outputs open.

2.Depends on the cycle time.

3.CE1 = VIH, RFSH = VIH

4.CE1 = VCC - 0.2 V, RFSH = VCC - 0.2 V

5.CE1 = VIH, RFSH = VIL

6.CE1 = VCC - 0.2 V, RFSH = 0.2 V

CONDITIONS

tRC = tRC (MIN)

0 V ≤ VIN ≤ 6.5 V

0 V except on test pins

0 V ≤ VOUT ≤ VCC + 0.3 V Output in high-

impedance state

IOUT = -1 mA

IOUT = 4 mA

MIN. MAX.

104

70

50

1

0.2

1

0.2

-10 10

-10 10

2.4

0.4

UNIT NOTE

mA |

1, 2 |

1, 3 mA

1, 4

1, 5 mA

1, 6

μA

μA

V

V

3

LH5P8128 CMOS 1M (128K × 8) Pseudo-Static RAM

AC ELECTRICAL CHARACTERISTICS 1,2,3 (TA = 0 to +70°C, VCC = 5.0 V ±10%)

PARAMETER |

SYMBOL |

LH5P8128-60 |

LH5P8128-80 |

LH5P8128-10 |

UNIT |

NOTE |

||||

MIN. |

MAX. |

MIN. |

MAX. |

MIN. |

MAX. |

|||||

|

|

|

|

|||||||

Random read, write cycle time |

tRC |

100 |

|

130 |

|

160 |

|

ns |

|

|

Read modify write cycle time |

tRMW |

165 |

|

195 |

|

235 |

|

ns |

|

|

CE pulse width |

tCE |

60 |

10,000 |

80 |

10,000 |

100 |

10,000 |

ns |

|

|

CE precharge time |

tP |

40 |

|

40 |

|

50 |

|

ns |

|

|

Address setup time |

tAS |

0 |

|

0 |

|

0 |

|

ns |

4 |

|

Address hold time |

tAH |

15 |

|

20 |

|

25 |

|

ns |

4 |

|

Read command setup time |

tRCS |

0 |

|

0 |

|

0 |

|

ns |

|

|

Read command hold time |

tRCH |

0 |

|

0 |

|

0 |

|

ns |

|

|

CE access time |

tCEA |

|

60 |

|

80 |

|

100 |

ns |

5 |

|

OE access time |

tOEA |

|

25 |

|

30 |

|

35 |

ns |

5 |

|

CE to output in Low-Z |

tCLZ |

20 |

|

20 |

|

20 |

|

ns |

|

|

OE to output in Low-Z |

tOLZ |

0 |

|

0 |

|

0 |

|

ns |

|

|

Output enable from end of write |

tWLZ |

0 |

|

0 |

|

0 |

|

ns |

|

|

Chip disable to output in High-Z |

tCHZ |

|

20 |

|

25 |

|

30 |

ns |

|

|

Output disable to output in High-Z |

tOHZ |

|

20 |

|

25 |

|

30 |

ns |

|

|

Write enable to output in High-Z |

tWHZ |

|

20 |

|

25 |

|

30 |

ns |

|

|

OE setup time |

tOES |

0 |

|

0 |

|

0 |

|

ns |

|

|

OE hold time |

tOEH |

10 |

|

10 |

|

10 |

|

ns |

|

|

Write command pulse width |

tWP |

30 |

|

30 |

|

30 |

|

ns |

|

|

Write command setup time |

tWCS |

30 |

|

30 |

|

30 |

|

ns |

|

|

Write command hold time |

tWCH |

40 |

|

50 |

|

60 |

|

ns |

|

|

Data setup time from write |

tDSW |

25 |

|

30 |

|

35 |

|

ns |

6 |

|

Data setup time from CE |

tDSC |

25 |

|

30 |

|

35 |

|

ns |

6 |

|

Data hold time from write |

tDHW |

0 |

|

0 |

|

0 |

|

ns |

6 |

|

Data hold time from CE |

tDHC |

0 |

|

0 |

|

0 |

|

ns |

6 |

|

Transition time (rise and fall) |

tT |

3 |

35 |

3 |

35 |

3 |

35 |

ns |

|

|

Refresh time interval |

tREF |

|

8 |

|

8 |

|

8 |

ms |

|

|

Refresh command hold time |

tRHC |

15 |

|

15 |

|

15 |

|

ns |

|

|

Auto refresh cycle time |

tFC |

100 |

|

130 |

|

160 |

|

ns |

|

|

Refresh delay time from CE |

tRFD |

30 |

|

40 |

|

50 |

|

ns |

|

|

Refresh pulse width |

tFAP |

30 |

8,000 |

30 |

8,000 |

30 |

8,000 |

ns |

|

|

(Auto refresh) |

|

|||||||||

|

|

|

|

|

|

|

|

|

||

Refresh precharge time |

tFP |

30 |

|

30 |

|

30 |

|

ns |

|

|

(Auto refresh) |

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

||

Refresh pulse width (Self refresh) |

tFAS |

8,000 |

|

8,000 |

|

8,000 |

|

ns |

|

|

CE delay time from refresh |

tFRS |

140 |

|

160 |

|

190 |

|

ns |

|

|

precharge (Self refresh) |

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

||

NOTES:

1.In order to initialize the circuit, CE1 should be kept at VIH or CE2 should be kept at VIL for 100 μs after power-up, followed by at least 8 dummy cycles.

2.AC characteristics are measured at tT = 5 ns.

3.AC characteristics are measured at the following condition (see figure at right).

4.Address is latched at the negative edge of CE1 or at the positive edge of CE2.

5.Measured with a load equivalent to 2TTL + 100 pF.

6.Data is latched at the positive edge of W/R or at the positive edge of CE1 or at the negative edge of CE2.

|

|

|

2.4 V |

2.6 V |

||

INPUT |

|

|

|

|||

|

|

0.8 V |

0.6 V |

|||

|

|

|

||||

|

|

|

|

|

|

|

OUTPUT |

|

|

|

|

2.2 V |

|

|

|

|

|

|

||

|

|

|

|

0.8 V |

5P8128-3 |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

Figure 4. AC Characteristics |

|

||||

4

Loading...

Loading...