Sharp LH5496D-20, LH5496D-15, LH5496-65, LH5496-50, LH5496-35 Datasheet

...

LH5496/96H |

CMOS 512 × 9 FIFO |

FEATURES

∙ Fast Access Times:

15 */20/25/35/50/65/80 ns

∙Full CMOS Dual Port Memory Array

∙Fully Asynchronous Read and Write

∙Expandable-in Width and Depth

∙Full, Half-Full, and Empty Status Flags

∙Read Retransmit Capability

∙TTL Compatible I/O

∙Packages:

28-Pin, 300-mil PDIP

28-Pin, 600-mil PDIP

32-Pin PLCC

∙ Pin and Functionally Compatible with IDT7201

FUNCTIONAL DESCRIPTION

The LH5496/96H are dual port memories with internal addressing to implement a First-In, First-Out algorithm. Through an advanced dual port architecture, they provide fully asynchronous read/write operation. Empty, Full, and Half-Full status flags are provided to prevent data overflow and underflow. In addition, internal logic provides for unlimited expansion in both word size and depth.

Read and write operations automatically access sequential locations in memory in that data is read out in the same order that it was written, that is on a First-In, First-Out basis. Since the address sequence is internally predefined, no external address information is required for the operation of this device. A ninth data bit is provided for parity or control information often needed in communication applications.

Empty, Full, and Half-Full status flags monitor the extent to which data has been written into the FIFO, and prevent improper operations (i.e., Read if the FIFO is empty, or Write if the FIFO is full). A retransmit feature resets the Read address pointer to its initial position, thereby allowing repetitive readout of the same data. Expansion In and Expansion Out pins implement an expansion scheme that allows individual FIFOs to be cascaded to greater depth without incurring additional latency (bubblethrough) delays.

* LH5496 only.

PIN CONNECTIONS

28-PIN PDIP |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TOP VIEW |

|||||

|

|

|

|

|

|

1 |

|

|

|

|

|

28 |

|

|

|

VCC |

||||||||

|

W |

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

||||||||||||||||

D8 |

|

|

|

|

2 |

|

|

|

|

|

27 |

|

|

|

D4 |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

D3 |

|

|

|

3 |

|

|

|

|

|

26 |

|

|

|

D5 |

||||||||||

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

D2 |

|

|

4 |

|

|

|

|

|

25 |

|

|

|

D6 |

|||||||||||

|

|

|

|

|

|

|

|

|

||||||||||||||||

D1 |

|

|

5 |

|

|

|

|

|

24 |

|

|

|

D7 |

|||||||||||

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

23 |

|

|

|

|

|

|

|

|

||||

D0 |

|

|

6 |

|

|

|

|

|

|

|

|

FL/RT |

||||||||||||

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

22 |

|

|

|

|

|

|

|

|

|||

|

XI |

|

|

|

|

7 |

|

|

|

|

|

|

|

|

RS |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

21 |

|

|

|

|

|

|

|

|

|

|

FF |

|

|

|

|

|

8 |

|

|

|

|

|

|

|

|

EF |

||||||||

Q0 |

|

|

9 |

|

|

|

|

|

20 |

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

XO/HF |

|

|||||||||||||

|

|

|

|

|

|

|

|

|

||||||||||||||||

Q1 |

|

|

|

10 |

|

|

|

|

|

19 |

|

|

|

Q7 |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

Q2 |

|

|

11 |

|

|

|

|

|

18 |

|

|

|

Q6 |

|||||||||||

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

||||||||||||||||

Q3 |

|

|

12 |

|

|

|

|

|

17 |

|

|

|

Q5 |

|||||||||||

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

||||||||||||||||

Q8 |

|

|

|

|

13 |

|

|

|

|

|

16 |

|

|

|

Q4 |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

VSS |

|

|

14 |

|

|

|

|

|

15 |

|

|

|

R |

|

|

|

5496-1D |

|||||||

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Figure 1. Pin Connections for PDIP Packages |

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

32-PIN PLCC |

|

|

|

|

|

|

NC |

|

CC |

4 |

5 |

|

|

|

TOP VIEW |

|||||||||

3 |

|

|

|

|

8 |

W |

|

|

|

|

|

|||||||||||||

|

D |

|

D |

|

V |

|

D |

|

D |

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4 |

|

|

|

|

3 |

|

2 |

|

1 |

32 |

31 |

30 |

|

|

|

|

||||||||

D2 |

|

|

|

|

5 |

29 |

|

|

|

D6 |

||||||||||||

|

|

|

|

|

|

|||||||||||||||||

D1 |

|

|

|

|

6 |

28 |

|

|

|

D7 |

||||||||||||

|

|

|

|

|

|

|||||||||||||||||

D0 |

|

|

|

|

7 |

27 |

|

|

NC |

|||||||||||||

|

|

|

|

|

|

|||||||||||||||||

|

XI |

|

|

|

|

|

|

8 |

26 |

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

FL/RT |

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

FF |

|

|

|

|

9 |

25 |

|

|

RS |

|||||||||||||

Q0 |

|

|

|

|

10 |

24 |

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

EF |

|

|

|

||||||||||||

|

|

|

|

|

||||||||||||||||||

Q1 |

|

|

|

|

11 |

23 |

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

XO/HF |

||||||||||||||

NC |

|

|

|

12 |

22 |

|

|

|

|

Q7 |

||||||||||||

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|||||||||||||||||

Q2 |

|

|

|

13 |

21 |

|

|

|

|

Q6 |

||||||||||||

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|||||||||||||

14 |

|

15 |

|

16 |

|

17 |

18 |

19 |

20 |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3 |

8 |

|

SS |

|

NC |

|

R |

4 |

5 |

||||||||

|

|

|

|||||||||||||||

|

Q |

|

Q |

|

|

|

|

Q |

|

Q |

|||||||

|

|

|

V |

|

|

|

|

||||||||||

5496-2D

Figure 2. Pin Connections for PLCC Package

1

LH5496/96H |

|

|

|

|

CMOS 512 × 9 FIFO |

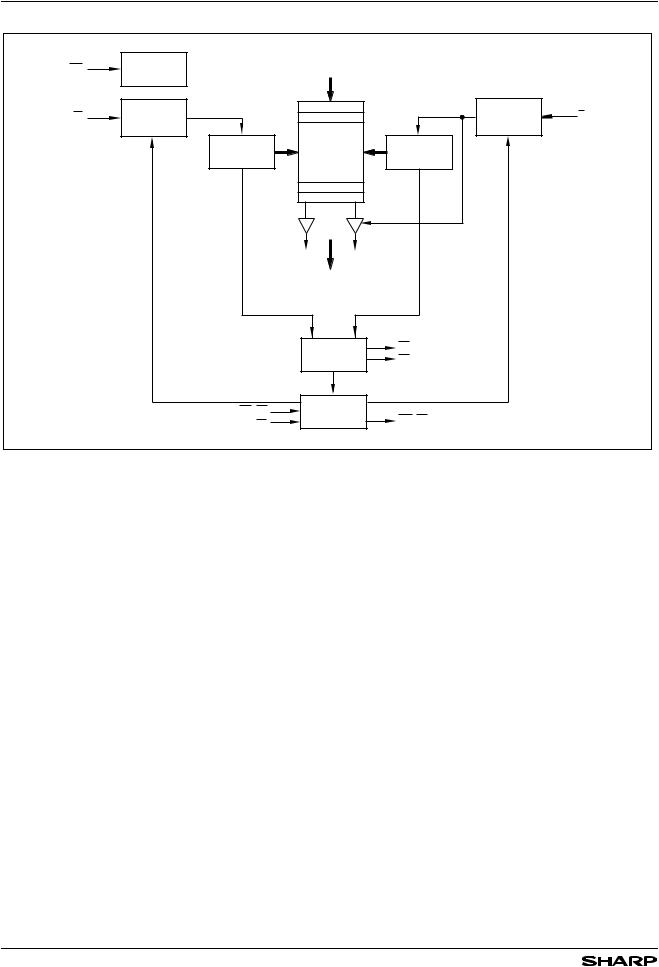

RS |

RESET |

|

DATA INPUTS |

|

|

|

D0 - D8 |

|

|

||

LOGIC |

|

|

|

||

|

INPUT |

|

|

OUTPUT |

R |

W |

PORT |

|

|

PORT |

|

|

CONTROL |

|

DUAL-PORT |

CONTROL |

|

|

|

WRITE |

RAM |

READ |

|

|

|

ARRAY |

|

||

|

|

POINTER |

POINTER |

|

|

|

|

|

|

||

|

|

|

512 x 9 |

|

|

|

|

|

. . . |

|

|

|

|

|

DATA OUTPUTS |

|

|

|

|

|

Q0 - Q8 |

|

|

|

|

|

FLAG |

EF |

|

|

|

|

LOGIC |

FF |

|

|

|

FL/RT |

EXPANSION |

|

|

|

|

LOGIC |

XO/HF |

|

|

|

|

XI |

|

||

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

5496-3 |

Figure 3. LH5496/96H Block Diagram

PIN DESCRIPTIONS

|

|

|

PIN |

PIN TYPE * |

DESCRIPTION |

|

|

PIN |

PIN TYPE * |

DESCRIPTION |

|||||

D0 – D8 |

I |

Input Data Bus |

|

|

|

|

|

|

|

O |

Expansion Out/Half-Full Flag |

||||

XO/HF |

|||||||||||||||

Q0 – Q8 |

O/Z |

Output Data Bus |

|

|

|

|

|

I |

Expansion In |

||||||

XI |

|||||||||||||||

|

|

|

|

|

I |

Write Request |

|

|

|

|

|

I |

First Load/Retransmit |

||

W |

FL/RT |

||||||||||||||

|

|

|

|

I |

Read Request |

|

|

I |

Reset |

||||||

R |

RS |

||||||||||||||

|

|

|

O |

Empty Flag |

VCC |

V |

Positive Power Supply |

||||||||

EF |

|||||||||||||||

|

|

O |

Full Flag |

VSS |

V |

Ground |

|||||||||

FF |

|||||||||||||||

* I = Input, O = Output, Z = High-Impedance, V = Power Voltage Level

2

CMOS 512 ´ 9 FIFO LH5496/96H

ABSOLUTE MAXIMUM RATINGS 1

PARAMETER |

RATING |

Supply Voltage to VSS Potential |

–0.5 V to 7 V |

Signal Pin Voltage to VSS Potential 3 |

–0.5 V to VCC + 0.5 V (not to exceed 7 V) |

DC Output Current 2 |

±50 mA |

Storage Temperature Range |

–65oC to 150oC |

Power Dissipation (Package Limit) |

1.0 W |

DC Voltage Applied To Outputs In High-Z State |

–0.5 V to Vcc + 0.5 V (not to exceed 7 V) |

NOTES:

1.Stresses greater than those listed under ‘Absolute Maximum Ratings’ may cause permanent damage to the device. This is a device stress rating for transient conditions only. Functional operation at these or any other conditions above those indicated in the ‘Operating Range’ of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

2.Outputs should not be shorted for more than 30 seconds. No more than one output should be shorted at any time.

3.Negative undershoots of 1.5 V in amplitude are permitted for up to 10 ns once per cycle.

OPERATING RANGE

SYMBOL |

PARAMETER |

MIN |

MAX |

UNIT |

TA |

Temperature, Ambient, LH5496 |

0 |

70 |

oC |

TA |

Temperature, Ambient, LH5496H |

–40 |

85 |

oC |

VCC |

Supply Voltage |

4.5 |

5.5 |

V |

VSS |

Supply Voltage |

0 |

0 |

V |

VIL |

Logic ‘0’ Input Voltage1 |

–0.5 |

0.8 |

V |

VIH |

Logic ‘1’ Input Voltage |

2.0 |

VCC + 0.5 |

V |

NOTE:

1.Negative undershoots of 1.5 V in amplitude are permitted for up to 10 ns once per cycle.

DC ELECTRICAL CHARACTERISTICS (Over Operating Range)

SYMBOL |

PARAMETER |

|

TEST CONDITIONS |

MIN |

MAX |

UNIT |

ILI |

Input Leakage Current |

VCC = 5.5 V, VIN = 0 V to VCC |

–10 |

10 |

mA |

|

ILO |

Output Leakage Current |

|

³ VIH, 0 V £ VOUT £ VCC |

–10 |

10 |

mA |

R |

||||||

VOH |

Output High Voltage |

IOH = –2.0 mA |

2.4 |

|

V |

|

VOL |

Output Low Voltage |

IOL = 8.0 mA |

|

0.4 |

V |

|

ICC |

Average Supply Current 1 |

Measured at f = 40 MHz |

|

100 |

mA |

|

ICC2 |

Average Standby Current 1 |

All Inputs = VIH |

|

15 |

mA |

|

ICC3 |

Power Down Current 1 |

All Inputs = VCC – 0.2 V |

|

5 |

mA |

|

NOTE:

1.ICC, ICC2, and ICC3 are dependent upon actual output loading and cycle rates. Specified values are with outputs open.

3

LH5496/96H |

CMOS 512 × 9 FIFO |

|

|

AC TEST CONDITIONS

PARAMETER

Input Pulse Levels

Input Rise and Fall Times (10% to 90%) Input Timing Reference Levels

Output Reference Levels

Output Load, Timing Tests

RATING

VSS to 3 V

5 ns

1.5 V

1.5 V

Figure 4

CAPACITANCE 1,2

PARAMETER |

RATING |

CIN (Input Capacitance) |

5 pF |

COUT (Output Capacitance) |

7 pF |

NOTES:

1.Sample tested only.

2.Capacitances are maximum values at 25oC measured at 1.0 MHz with VIN = 0 V.

+5 V

1.1 k Ω

DEVICE

UNDER

TEST

680 Ω |

30 pF * |

* INCLUDES JIG & SCOPE CAPACITANCES |

5496-4 |

|

Figure 4. Output Load Circuit

4

CMOS 512 × 9 FIFO LH5496/96H

AC ELECTRICAL CHARACTERISTICS 1 (Over Operating Range)

|

tA = 15 ns 2 |

tA = 20 ns |

tA = 25 ns |

tA = 35 ns |

tA = 50 ns tA = 65 ns |

tA = 80 ns |

SYMBOL |

PARAMETER |

MIN MAX |

MIN MAX |

MIN MAX |

MIN MAX MIN MAX |

UNIT |

|

MIN MAX |

MIN MAX |

tRC

tA

tRR

tRPW

tRLZ

tWLZ

tDV

tRHZ

READ CYCLE TIMING

Read Cycle Time |

25 |

– |

30 |

– |

35 |

– |

45 |

– |

65 |

– |

80 |

– |

100 |

– |

ns |

Access Time |

– |

15 |

– |

20 |

– |

25 |

– |

35 |

– |

50 |

– |

65 |

– |

80 |

ns |

Read Recover Time |

10 |

– |

10 |

– |

10 |

– |

10 |

– |

15 |

– |

15 |

– |

15 |

– |

ns |

Read Pulse Width 3 |

15 |

– |

20 |

– |

25 |

– |

35 |

– |

50 |

– |

65 |

– |

80 |

– |

ns |

Data Bus Active from Read LOW 4 |

5 |

– |

5 |

– |

5 |

– |

5 |

– |

5 |

– |

5 |

– |

10 |

– |

ns |

Data Bus Active from Write |

10 |

– |

10 |

– |

10 |

– |

10 |

– |

10 |

– |

10 |

– |

20 |

– |

ns |

HIGH 4,5 |

|||||||||||||||

Data Valid from Read Pulse HIGH |

5 |

– |

5 |

– |

5 |

– |

5 |

– |

5 |

– |

5 |

– |

5 |

– |

ns |

Data Bus High-Z from Read |

– |

15 |

– |

15 |

– |

15 |

– |

15 |

– |

20 |

– |

30 |

– |

30 |

ns |

HIGH 4 |

WRITE CYCLE TIMING

tWC |

Write Cycle Time |

25 |

– |

30 |

– |

35 |

– |

45 |

– |

65 |

– |

80 |

– |

100 |

– |

ns |

tWPW |

Write Pulse Width 3 |

15 |

– |

20 |

– |

25 |

– |

35 |

– |

50 |

– |

65 |

– |

80 |

– |

ns |

tWR |

Write Recovery Time |

10 |

– |

10 |

– |

10 |

– |

10 |

– |

15 |

– |

15 |

– |

15 |

– |

ns |

tDS |

Data Setup Time |

10 |

– |

10 |

– |

10 |

– |

15 |

– |

20 |

– |

20 |

– |

20 |

– |

ns |

tDH |

Data Hold Time |

0 |

– |

0 |

– |

0 |

– |

0 |

– |

0 |

– |

5 |

– |

5 |

– |

ns |

RESET TIMING

tRSC |

Reset Cycle Time |

25 |

– |

30 |

– |

35 |

– |

45 |

– |

65 |

– |

80 |

– |

100 |

– |

ns |

|||

tRS |

Reset Pulse Width 3 |

15 |

– |

20 |

– |

25 |

– |

35 |

– |

50 |

– |

65 |

– |

80 |

– |

ns |

|||

tRSR |

Reset Recovery Time |

10 |

– |

10 |

– |

10 |

– |

10 |

– |

15 |

– |

15 |

– |

15 |

– |

ns |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tRRSS |

Read HIGH to RS HIGH |

15 |

– |

20 |

– |

25 |

– |

35 |

– |

50 |

– |

65 |

– |

80 |

– |

ns |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tWRSS |

Write HIGH to RS HIGH |

15 |

– |

20 |

– |

25 |

– |

35 |

– |

50 |

– |

65 |

– |

80 |

– |

ns |

|||

RETRANSMIT TIMING

tRTC |

Retransmit Cycle Time |

25 |

– |

30 |

– |

35 |

– |

45 |

– |

65 |

– |

80 |

– |

100 |

– |

ns |

tRT |

Retransmit Pulse Width 3 |

15 |

– |

20 |

– |

25 |

– |

35 |

– |

50 |

– |

65 |

– |

80 |

– |

ns |

tRTR |

Retransmit Recovery Time |

10 |

– |

10 |

– |

10 |

– |

10 |

– |

15 |

– |

15 |

– |

15 |

– |

ns |

FLAG TIMING

tEFL |

Reset LOW to Empty Flag LOW |

|

tHFH,FFH |

Reset LOW to Half-Full and Full |

|

Flags HIGH |

||

|

||

tREF |

Read LOW to Empty Flag LOW |

|

tRFF |

Read HIGH to Full Flag HIGH |

|

tWEF |

Write HIGH to Empty Flag HIGH |

|

tWFF |

Write LOW to Full Flag LOW |

|

tWHF |

Write LOW to Half-Full Flag LOW |

|

tRHF |

Read HIGH to Half-Full Flag HIGH |

– |

25 |

– |

30 |

– |

35 |

– |

45 |

– |

65 |

– |

80 |

– |

100 |

ns |

– |

25 |

– |

30 |

– |

35 |

– |

45 |

– |

65 |

– |

80 |

– |

100 |

ns |

– |

20 |

– |

25 |

– |

25 |

– |

35 |

– |

45 |

– |

60 |

– |

60 |

ns |

– |

20 |

– |

25 |

– |

25 |

– |

35 |

– |

45 |

– |

60 |

– |

60 |

ns |

– |

20 |

– |

25 |

– |

25 |

– |

35 |

– |

45 |

– |

60 |

– |

60 |

ns |

– |

20 |

– |

25 |

– |

25 |

– |

35 |

– |

45 |

– |

60 |

– |

60 |

ns |

– |

25 |

– |

30 |

– |

35 |

– |

45 |

– |

65 |

– |

80 |

– |

100 |

ns |

– |

25 |

– |

30 |

– |

35 |

– |

45 |

– |

65 |

– |

80 |

– |

100 |

ns |

EXPANSION TIMING

tXOL |

Expansion Out LOW |

– |

18 |

– |

20 |

– |

25 |

– |

35 |

– |

50 |

– |

65 |

– |

80 |

ns |

tXOH |

Expansion Out HIGH |

– |

18 |

– |

20 |

– |

25 |

– |

35 |

– |

50 |

– |

65 |

– |

80 |

ns |

tXI |

Expansion In Pulse Width |

15 |

– |

20 |

– |

25 |

– |

35 |

– |

50 |

– |

65 |

– |

80 |

– |

ns |

tXIR |

Expansion In Recovery Time |

10 |

– |

10 |

– |

10 |

– |

10 |

– |

10 |

– |

10 |

– |

10 |

– |

ns |

tXIS |

Expansion in Setup Time |

7 |

– |

10 |

– |

10 |

– |

15 |

– |

15 |

– |

15 |

– |

15 |

– |

ns |

NOTES:

1.LH5496 only.

2.All timing measurements performed at ‘AC Test Condition’ levels.

5

Loading...

Loading...