NEC UPD753108GK-XXX-8A8, UPD753106GK-XXX-9ET, UPD753108GC-XXX-AB8, UPD753106GK-XXX-8A8, UPD753106GC-XXX-AB8 Datasheet

...

DATA SHEET

MOS INTEGRATED CIRCUIT

μPD753104, 753106, 753108

4-BIT SINGLE-CHIP MICROCONTROLLER

The μPD753108 is one of the 75XL Series 4-bit single-chip microcontroller chips and has a data processing capability comparable to that of an 8-bit microcontroller.

The existing 75X Series containing an LCD controller/driver supplies an 80-pin package.

The μPD753108 supplies a 64-pin package (12 x 12 mm), which is suitable for small-scale systems.

It features expanded CPU functions and can provide high-speed operation at a low supply voltage of 1.8 V compared with the existing μPD75308B.

For detailed function descriptions, refer to the following user’s manual. Be sure to read the document

before designing.

μPD753108 User’s Manual: U10890E

Features

Low voltage operation: VDD = 1.8 to 5.5 V

• Can be driven by two 1.5-V batteries On-chip memory

•Program memory (ROM): 4096 x 8 bits (μPD753104) 6144 x 8 bits (μPD753106) 8192 x 8 bits (μPD753108)

•Data memory (RAM):

512 x 4 bits

Capable of high-speed operation and variable instruction execution time for power saving

•0.95, 1.91, 3.81, 15.3 μs (@ 4.19 MHz with main system clock)

•0.67, 1.33, 2.67, 10.7 μs (@ 6.0 MHz with main system clock)

•122 μs (@ 32.768 kHz with subsystem clock)

Internal programmable LCD controller/driver

Small package:

64-pin plastic QFP (12 x 12 mm, 0.65-mm pitch) One-time PROM version: μPD75P3116

Application

Remote controllers, cameras, hemadynamometers, electronic scale, gas meters, etc.

Unless otherwise indicated, references in this data sheet to the μPD753108 mean the

μPD753104 and μPD753106.

The information in this document is subject to change without notice.

The mark  shows major revised points.

shows major revised points.

Document No. U10086EJ3V0DS00 (3rd edition)

Date Published April 1997 N |

© |

1995 |

Printed in Japan

μPD753104, 753106, 753108

Ordering Information

Part number |

Package |

ROM (x 8 bits) |

|

μPD753104GC-xxx-AB8 |

64-pin plastic QFP (14 x 14 mm, 0.8-mm pitch) |

4096 |

|

μPD753104GK-xxx-8A8 |

64-pin plastic QFP (12 x 12 mm, 0.65-mm pitch) |

4096 |

|

μPD753106GC-xxx-AB8 |

64-pin plastic QFP (14 x 14 mm, 0.8-mm pitch) |

6144 |

|

μPD753106GK-xxx-8A8 |

64-pin plastic QFP (12 x 12 mm, 0.65-mm pitch) |

6144 |

|

μPD753108GC-xxx-AB8 |

64-pin plastic QFP (14 x 14 mm, 0.8-mm pitch) |

8192 |

|

μPD753108GK-xxx-8A8 |

64-pin plastic QFP (12 x 12 mm, 0.65-mm pitch) |

8192 |

|

Remark |

xxx indicates the ROM code suffix. |

|

|

2

|

|

|

|

|

|

|

|

|

μPD753104, 753106, 753108 |

||

Functional Outline |

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Parameter |

|

|

|

|

|

Function |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

Instruction execution time |

|

• |

0.95, 1.91, 3.81, 15.3 μs (@ 4.19 MHz with main system clock) |

|

|

|||||

|

|

|

|

|

• |

0.67, 1.33, 2.67, 10.7 μs (@ 6.0 MHz with main system clock) |

|

|

|||

|

|

|

|

|

• |

122 μs (@ 32.768 kHz with subsystem clock) |

|

|

|||

|

|

|

|

|

|

|

|

|

|

||

|

On-chip memory |

|

ROM |

4096 x 8 bits (μPD753104) |

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

6144 x 8 bits (μPD753106) |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

8192 x 8 bits (μPD753108) |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

RAM |

512 x 4 bits |

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

General-purpose register |

|

• |

4-bit operation: |

8 x 4 banks |

|

|

||||

|

|

|

|

|

• |

8-bit operation: |

4 x 4 banks |

|

|

||

|

|

|

|

|

|

|

|

|

|

||

|

Input/ |

CMOS input |

|

8 |

|

On-chip pull-up resistors which can be specified by software: |

7 |

|

|||

|

output |

|

|

|

|

|

|

|

|

|

|

|

CMOS input/output |

20 |

|

On-chip pull-up resistors which can be specified by software: |

12 |

|

|||||

|

port |

|

|

||||||||

|

|

|

|

|

|

Also used for segment pins: 8 |

|

|

|||

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

||||

|

|

N-ch open-drain |

4 |

|

On-chip pull-up resistors which can be specified by mask option, 13-V withstand |

|

|||||

|

|

input/output pins |

|

|

voltage |

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Total |

|

32 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

LCD controller/driver |

|

• |

Segment selection: |

16/20/24 segments (can be changed to CMOS input/ |

|

|||||

|

|

|

|

|

|

|

|

|

output port in 4 time-unit; max. 8) |

|

|

|

|

|

|

|

• |

Display mode selection: Static, 1/2 duty (1/2 bias), 1/3 duty (1/2 bias), |

|

||||

|

|

|

|

|

|

|

|

|

1/3 duty (1/3 bias), 1/4 duty (1/3 bias) |

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

• |

On-chip split resistor for LCD drive can be specified by mask option |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

Timer |

|

|

|

5 channels |

|

|

|

|

||

|

|

|

|

|

• |

8-bit timer/event counter: 3 channels (16-bit timer/event counter, carrier generator, |

|

||||

|

|

|

|

|

|

timer with gate) |

|

|

|

|

|

|

|

|

|

|

• |

Basic interval timer/watchdog timer: 1 channel |

|

|

|||

|

|

|

|

|

• |

Watch timer: 1 channel |

|

|

|

||

|

|

|

|

|

|

||||||

|

Serial interface |

|

• |

3-wire serial I/O mode ... MSB or LSB can be selected for transferring first bit |

|

||||||

|

|

|

|

|

• |

2-wire serial I/O mode |

|

|

|

||

|

|

|

|

|

• |

SBI mode |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

Bit sequential buffer (BSB) |

|

16 bits |

|

|

|

|

||||

|

|

|

|

|

|

|

|||||

|

Clock output (PCL) |

|

• |

Φ, 524, 262, 65.5 kHz (@ 4.19 MHz with main system clock) |

|

|

|||||

|

|

|

|

|

• |

Φ, 750, 375, 93.8 kHz (@ 6.0 MHz with main system clock) |

|

|

|||

|

|

|

|

|

|

|

|

||||

|

Buzzer output (BUZ) |

|

• |

2, 4, 32 kHz |

(@ 4.19 MHz with main system clock or |

|

|

||||

|

|

|

|

|

|

|

|

@ 32.768 kHz with subsystem clock) |

|

|

|

|

|

|

|

|

• |

2.93, 5.86, 46.9 kHz (@ 6.0 MHz with main system clock) |

|

|

|||

|

|

|

|

|

|

|

|||||

|

Vectored interrupt |

|

External: 3, Internal: 5 |

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|||

|

Test input |

|

|

|

External: 1, Internal: 1 |

|

|

|

|||

|

|

|

|

|

|

|

|||||

|

System clock oscillator |

|

• |

Ceramic or crystal oscillator for main system clock oscillation |

|

|

|||||

|

|

|

|

|

• |

Crystal oscillator for subsystem clock oscillation |

|

|

|||

|

|

|

|

|

|

|

|

||||

|

Standby function |

|

STOP/HALT mode |

|

|

|

|

||||

|

|

|

|

|

|

|

|

||||

|

Supply voltage |

|

VDD = 1.8 to 5.5 V |

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|||

|

Package |

|

|

|

• |

64-pin plastic QFP (14 x 14 mm, 0.8-mm pitch) |

|

|

|||

|

|

|

|

|

• |

64-pin plastic QFP (12 x 12 mm, 0.65-mm pitch) |

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

3

|

|

μPD753104, 753106, 753108 |

|

|

|

CONTENTS |

|

1. |

PIN CONFIGURATION (Top View) ...................................................................................................... |

6 |

|

2. |

BLOCK DIAGRAM ................................................................................................................................ |

8 |

|

3. |

PIN FUNCTIONS ................................................................................................................................... |

9 |

|

|

3.1 |

Port Pins ...................................................................................................................................... |

9 |

|

3.2 |

Non-port Pins ............................................................................................................................ |

11 |

|

3.3 |

Pin Input/Output Circuits ......................................................................................................... |

13 |

|

3.4 |

Recommended Connections for Unused Pins ....................................................................... |

15 |

4. |

SWITCHING FUNCTION BETWEEN Mk I MODE AND Mk II MODE ................................................ |

16 |

|

|

4.1 |

Difference between Mk I Mode and Mk II Mode ...................................................................... |

16 |

|

4.2 |

Setting Method of Stack Bank Select Register (SBS) ........................................................... |

17 |

5. |

MEMORY CONFIGURATION ............................................................................................................. |

18 |

|

6. |

PERIPHERAL HARDWARE FUNCTION ........................................................................................... |

23 |

|

|

6.1 |

Digital I/O Port ........................................................................................................................... |

23 |

|

6.2 |

Clock Generator ........................................................................................................................ |

23 |

|

6.3 |

Subsystem Clock Oscillator Control Functions .................................................................... |

25 |

|

6.4 |

Clock Output Circuit ................................................................................................................. |

26 |

|

6.5 |

Basic Interval Timer/Watchdog Timer ..................................................................................... |

27 |

|

6.6 |

Watch Timer .............................................................................................................................. |

28 |

|

6.7 |

Timer/Event Counter ................................................................................................................. |

29 |

|

6.8 |

Serial Interface .......................................................................................................................... |

33 |

|

6.9 |

LCD Controller/Driver ............................................................................................................... |

35 |

|

6.10 |

Bit Sequential Buffer ................................................................................................................ |

37 |

7. |

INTERRUPT FUNCTION AND TEST FUNCTION .............................................................................. |

38 |

|

8. |

STANDBY FUNCTION ........................................................................................................................ |

40 |

|

9. |

RESET FUNCTION ............................................................................................................................. |

41 |

|

10. |

MASK OPTION ................................................................................................................................... |

44 |

|

11. |

INSTRUCTION SET ............................................................................................................................ |

45 |

|

12. |

ELECTRICAL SPECIFICATIONS ....................................................................................................... |

59 |

|

13. CHARACTERISTIC CURVES (FOR REFERENCE ONLY) ............................................................... |

75 |

||

14. PACKAGE DRAWINGS ..................................................................................................................... |

78 |

||

15. RECOMMENDED SOLDERING CONDITIONS ................................................................................. |

80 |

||

4

μPD753104, 753106, 753108 |

|

APPENDIX A. μPD75308B, 753108 AND 75P3116 FUNCTIONAL LIST .............................................. |

81 |

APPENDIX B. DEVELOPMENT TOOLS ................................................................................................. |

83 |

APPENDIX C. RELATED DOCUMENTS ................................................................................................ |

87 |

5

μPD753104, 753106, 753108

1.PIN CONFIGURATION (Top View)

•64-pin plastic QFP (14 x 14 mm, 0.8-mm pitch)

μPD753104GC-xxx-AB8, μPD753106GC-xxx-AB8,

μPD753108GC-xxx-AB8

•64-pin plastic QFP (12 x 12 mm, 0.65-mm pitch)

μPD753104GK-xxx-8A8, μPD753106GK-xxx-8A8,

μPD753108GK-xxx-8A8

|

COM3 |

COM2 |

COM1 |

COM0 |

S0 |

S1 |

S2 |

S3 |

S4 |

S5 |

S6 |

S7 |

S8 |

S9 |

S10 |

S11 |

|

|

64 |

63 |

62 |

61 |

60 |

59 |

58 |

57 |

56 |

55 |

54 |

53 |

52 |

51 |

50 |

49 |

|

BIAS |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

48 |

S12 |

VLC0 |

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

47 |

S13 |

VLC1 |

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

46 |

S14 |

VLC2 |

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

45 |

S15 |

P30/LCDCL |

5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

44 |

S16/P93 |

P31/SYNC |

6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

43 |

S17/P92 |

P32 |

7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

42 |

S18/P91 |

P33 |

8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

41 |

S19/P90 |

VSS |

9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

40 |

S20/P83 |

P50 |

10 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

39 |

S21/P82 |

P51 |

11 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

38 |

S22/P81 |

P52 |

12 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

37 |

S23/P80 |

P53 |

13 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

36 |

P23/BUZ |

P60/KR0 |

14 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

35 |

P22/PCL/PTO2 |

P61/KR1 |

15 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

34 |

P21/PTO1 |

P62/KR2 |

16 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

33 |

P20/PTO0 |

|

17 |

18 |

19 |

20 |

21 |

22 |

23 |

24 |

25 |

26 |

27 |

28 |

29 |

30 |

31 |

32 |

|

|

P63/KR3 |

RESET |

XT1 |

XT2 |

IC Note |

X1 |

X2 |

VDD |

P00/INT4 |

P01/SCK |

P02/SO/SB0 |

P03/SI/SB1 |

P10/INT0 |

P11/INT1 |

P12/INT2/TI1/TI2 |

P13/TI0 |

|

Note Connect the IC (Internally Connected) pin directly to VDD.

6

μPD753104, 753106, 753108

Pin Identification |

|

|||

|

P00 to P03 |

: Port 0 |

||

|

P10 to P13 |

: Port 1 |

||

|

P20 to P23 |

: Port 2 |

||

|

P30 to P33 |

: Port 3 |

||

|

P50 to P53 |

: Port 5 |

||

|

P60 to P63 |

: Port 6 |

||

|

P80 to P83 |

: Port 8 |

||

|

P90 to P93 |

: Port 9 |

||

|

KR0 to KR3 |

: Key Return 0 to 3 |

||

|

|

: Serial Clock |

||

|

SCK |

|

||

|

SI |

: Serial Input |

||

|

SO |

: Serial Output |

||

|

SB0, SB1 |

: Serial Data Bus 0, 1 |

||

|

|

|

: Reset |

|

|

RESET |

|

||

|

S0 to S23 |

: Segment Output 0 to 23 |

||

|

COM0 to COM3 |

: Common Output 0 to 3 |

||

VLC0 to VLC2 |

: LCD Power Supply 0 to 2 |

BIAS |

: LCD Power Supply Bias Control |

LCDCL |

: LCD Clock |

SYNC |

: LCD Synchronization |

TI0 to TI2 |

: Timer Input 0 to 2 |

PTO0 to PTO2 |

: Programmable Timer Output 0 to 2 |

BUZ |

: Buzzer Clock |

PCL |

: Programmable Clock |

INT0, INT1, INT4 |

: External Vectored Interrupt 0, 1, 4 |

INT2 |

: External Test Input 2 |

X1, X2 |

: Main System Clock Oscillation 1, 2 |

XT1, XT2 |

: Subsystem Clock Oscillation 1, 2 |

VDD |

: Positive Power Supply |

VSS |

: Ground |

IC |

: Internally Connected |

7

8

|

BUZ/P23 |

WATCH |

|

|

|

TIMER |

|

||

|

|

|

||

|

|

INTW |

fLCD |

|

|

|

BASIC |

|

|

|

|

INTERVAL |

|

|

|

|

TIMER/ |

|

|

|

|

WATCHDOG |

||

|

|

TIMER |

|

|

|

|

INTBT |

|

|

|

TI0/P13 |

8-BIT |

|

|

|

PTO0/P20 |

TIMER/EVENT |

||

|

COUNTER #0 |

|||

|

|

INTT0 |

TOUT0 |

|

|

|

INTT1 |

|

|

TI1/TI2/P12/INT2 |

8-BIT |

|

|

|

TIMER/EVENT CASCADED |

||||

|

||||

PTO1/P21 |

COUNTER #1 16-BIT |

|

||

|

8-BIT |

TIMER/ |

|

|

|

EVENT |

|

||

PTO2/PCL/P22 |

TIMER/EVENT COUNTER |

|||

COUNTER #2 |

|

|||

TOUT0 |

|

|||

|

|

|

||

|

|

INTT2 |

|

|

SI/SB1/P03 |

CLOCKED |

|

||

SO/SB0/P02 |

|

|||

SERIAL |

|

|||

|

SCK/P01 |

INTERFACE |

||

|

|

|

||

|

|

INTCSI TOUT0 |

||

|

INT0/P10 |

INT1 |

||

|

|

|

||

|

INT1/P11 |

|

|

|

|

INT4/P00 |

INTERRUPT |

||

INT2/P12/TI1/TI2 |

||||

KR0/P60 to |

CONTROL |

|

||

4 |

|

|||

|

KR3/P63 |

|

||

|

|

|

||

|

|

BIT SEQ. |

|

|

|

|

BUFFER (16) |

||

|

|

|

|

|

CY |

|

|

|

|

SP(8) |

|||

PROGRAM |

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

||||||

COUNTER |

|

ALU |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

SBS |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

BANK |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

GENERAL REG. |

||||||||

PROGRAM |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MEMORY Note |

|

DECODE |

|

|

|

|

|

|

|

|

|

|

|

(ROM) |

|

|

|

DATA MEMORY |

|||||||||

|

AND |

|

|

||||||||||

|

|

|

|

||||||||||

|

|

CONTROL |

|

|

(RAM) |

|

|

||||||

|

|

|

|

|

512 x 4 BITS |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

fx/2 |

N |

CPU |

|

|

|

|

CLOCK Φ |

|

||

CLOCK |

CLOCK |

|

SYSTEM CLOCK |

|

|

OUTPUT |

DIVIDER |

GENERATOR |

STAND BY |

fLCD |

|

CONTROL |

|

|

MAIN SUB |

CONTROL |

|

|

|

|

|

||

|

|

|

|

|

|

PCL/PTO2/P22 |

|

X1 X2 XT1XT2 |

IC |

VDD VSS RESET |

|

|

|

|

|

||

PORT0 |

4 |

P00 to P03 |

PORT1 |

|

P10 to P13 |

|

||

4 |

||

PORT2 |

|

P20 to P23 |

|

||

4 |

||

PORT3 |

|

P30 to P33 |

|

||

4 |

||

PORT5 |

|

P50 to P53 |

|

||

4 |

||

PORT6 |

|

P60 to P63 |

|

||

4 |

||

PORT8 |

|

P80 to P83 |

|

||

4 |

||

PORT9 |

|

P90 to P93 |

|

||

4 |

||

|

|

|

LCD

CONTROLLER/ 16 S0 to S15 DRIVER

S16/P93 to 4 S19/P90

S20/P83 to 4 S23/P80

4 COM0 to COM3

BIAS

BIAS

VLC0

VLC0

VLC1

VLC1

VLC2

VLC2

SYNC/P31

SYNC/P31

LCDCL/P30

LCDCL/P30

DIAGRAM BLOCK .2

Note The ROM capacity depends on the product.

753108 753106, PD753104,μ

μPD753104, 753106, 753108

3. |

PIN FUNCTIONS |

|

|

|

|

|

|

|

||

3.1 |

Port Pins (1/2) |

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

Pin Name |

Input/Output |

Alternate |

Function |

8-bit |

After Reset |

I/O Circuit |

||||

Function |

I/O |

TYPE Note 1 |

||||||||

|

|

|

|

|

||||||

P00 |

Input |

INT4 |

4-bit input port (PORT0). |

No |

Input |

(B) |

||||

|

|

|

|

|

|

For P01 to P03, connection of on-chip pull- |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

P01 |

Input/Output |

SCK |

|

|

(F)-A |

|||||

up resistors can be specified by software in |

|

|

||||||||

|

|

|

|

|

|

|

|

|

||

P02 |

Input/Output |

SO/SB0 |

3-bit units. |

|

|

(F)-B |

||||

|

|

|

|

|

|

|

|

|

||

P03 |

Input/Output |

SI/SB1 |

|

|

|

(M)-C |

||||

|

|

|

|

|

|

|

|

|

||

P10 |

Input |

INT0 |

4-bit input port (PORT1). |

No |

Input |

(B)-C |

||||

|

|

|

|

|

|

Connection of on-chip pull-up resistors can |

|

|

|

|

P11 |

|

INT1 |

|

|

|

|||||

|

be specified by software in 4-bit units. |

|

|

|

||||||

|

|

|

|

|

|

|

|

|

||

P12 |

|

TI1/TI2/INT2 |

P10/INT0 can select noise elimination |

|

|

|

||||

|

|

|

|

|

|

circuit. |

|

|

|

|

P13 |

|

|

TI0 |

|

|

|

||||

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

||

P20 |

Input/Output |

PTO0 |

4-bit input/output port (PORT2). |

No |

Input |

E-B |

||||

|

|

|

|

|

|

Connection of on-chip pull-up resistors can |

|

|

|

|

P21 |

|

PTO1 |

|

|

|

|||||

|

be specified by software in 4-bit units. |

|

|

|

||||||

|

|

|

|

|

|

|

|

|

||

P22 |

|

PCL/PTO2 |

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

||

P23 |

|

BUZ |

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

||

P30 |

Input/Output |

LCDCL |

Programmable 4-bit input/output port |

No |

Input |

E-B |

||||

|

|

|

|

|

|

(PORT3). |

|

|

|

|

P31 |

|

SYNC |

|

|

|

|||||

|

This port can be specified for input/output |

|

|

|

||||||

|

|

|

|

|

|

|

|

|

||

P32 |

|

|

– |

bit-wise. |

|

|

|

|||

|

|

|

|

|

|

Connection of on-chip pull-up resistors can |

|

|

|

|

P33 |

|

|

– |

|

|

|

||||

|

|

be specified by software in 4-bit units. |

|

|

|

|||||

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

||

P50-P53 Note 2 |

Input/Output |

|

– |

N-ch open-drain 4-bit input/output port |

No |

High level |

M-D |

|||

|

|

|

|

|

|

(PORT5). |

|

(when pull- |

|

|

|

|

|

|

|

|

|

up resistors |

|

||

|

|

|

|

|

|

A pull-up resistor can be contained bit-wise |

|

|

||

|

|

|

|

|

|

|

are provided) |

|

||

|

|

|

|

|

|

(mask option). |

|

or high- |

|

|

|

|

|

|

|

|

Withstand voltage is 13 V in open-drain mode. |

|

impedance |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

Notes 1. Characters in parentheses indicate the Schmitt trigger input.

2.If on-chip pull-up resistors are not specified by mask option (when used as N-ch open-drain input port), low-level input leakage current increases when input or bit manipulation instruction is executed.

9

μPD753104, 753106, 753108

3.1 Port Pins (2/2)

Pin Name |

Input/Output |

Alternate |

Function |

8-bit |

After Reset |

I/O Circuit |

|

Function |

I/O |

TYPE Note 1 |

|||||

|

|

|

|

||||

P60 |

Input/Output |

KR0 |

Programmable 4-bit input/output port |

No |

Input |

(F)-A |

|

|

|

|

(PORT6). |

|

|

|

|

P61 |

|

KR1 |

|

|

|

||

|

This port can be specified for input/output |

|

|

|

|||

|

|

|

|

|

|

||

|

|

|

bit-wise. |

|

|

|

|

P62 |

|

KR2 |

|

|

|

||

|

Connection of on-chip pull-up resistors can |

|

|

|

|||

|

|

|

|

|

|

||

P63 |

|

KR3 |

be specified by software in 4-bit units. |

|

|

|

|

|

|

|

|

|

|

|

|

P80 |

Input/Output |

S23 |

4-bit input/output port (PORT8). |

Yes |

Input |

H |

|

P81 |

|

S22 |

Connection of on-chip pull-up resistors can |

|

|

|

|

|

be specified by software in 4-bit units Note 2. |

|

|

|

|||

|

|

|

|

|

|

||

P82 |

|

S21 |

|

|

|

||

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

P83 |

|

S20 |

|

|

|

|

|

|

|

|

|

|

|

|

|

P90 |

Input/Output |

S19 |

4-bit input/output port (PORT9). |

|

Input |

H |

|

Connection of on-chip pull-up resistors can |

|

||||||

|

|

|

|

|

|

||

P91 |

|

S18 |

|

|

|

||

|

be specified by software in 4-bit units Note 2. |

|

|

|

|||

P92 |

|

S17 |

|

|

|

|

|

|

|

|

|

|

|

|

|

P93 |

|

S16 |

|

|

|

|

|

|

|

|

|

|

|

|

Notes 1. Characters in parentheses indicate the Schmitt trigger input.

2. When these pins are used as segment signal output pins, do not connect the on-chip pull-up resistor

by software.

10

μPD753104, 753106, 753108

3.2 Non-port Pins (1/2)

|

Pin Name |

Input/Output |

Alternate |

Function |

After Reset |

I/O Circuit |

|||

|

Function |

TYPE Note 1 |

|||||||

|

|

|

|

|

|

|

|

||

TI0 |

Input |

P13 |

Inputs external event pulses to the timer/event |

Input |

(B)-C |

||||

|

|

|

|

|

counter. |

|

|

|

|

TI1 |

|

P12/INT2/TI2 |

|

|

|

||||

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

TI2 |

|

P12/INT2/TI1 |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

PTO0 |

Output |

P20 |

Timer/event counter output |

|

Input |

E-B |

|||

|

|

|

|

|

|

|

|

|

|

PTO1 |

|

P21 |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

PTO2 |

|

P22/PCL |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

PCL |

|

P22/PTO2 |

Clock output |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

BUZ |

|

P23 |

Optional frequency output (for buzzer output or |

|

|

||||

|

|

|

|

|

system clock trimming) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SCK |

Input/Output |

P01 |

Serial clock input/output |

|

Input |

(F)-A |

|||

|

|

|

|

|

|

|

|

|

|

SO/SB0 |

|

P02 |

Serial data output |

|

|

(F)-B |

|||

|

|

|

|

|

Serial data bus input/output |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SI/SB1 |

|

P03 |

Serial data input |

|

|

(M)-C |

|||

|

|

|

|

|

Serial data bus input/output |

|

|

|

|

|

|

|

|

|

|

|

|||

INT4 |

Input |

P00 |

Edge detection vectored interrupt input (both |

Input |

(B) |

||||

|

|

|

|

|

rising edge and falling edge detection) |

|

|

||

|

|

|

|

|

|

|

|

||

INT0 |

Input |

P10 |

Edge detection vectored |

|

Noise elimination circuit/ |

Input |

(B)-C |

||

|

|

|

|

|

interrupt input (detection |

|

asynchronous selection |

|

|

|

|

|

|

|

edge can be selected). |

|

|

|

|

INT1 |

|

P11 |

|

Asynchronous |

|

|

|||

|

INT0/P10 can select noise |

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

elimination circuit. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

INT2 |

|

P12/TI1/TI2 |

Rising edge detection |

|

Asynchronous |

|

|

||

|

testable input |

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

KR0-KR3 |

Input |

P60-P63 |

Falling edge detection testable input |

Input |

(F)-A |

||||

|

|

|

|

|

|

|

|

||

S0-S15 |

Output |

– |

Segment signal output |

|

Note 2 |

G-A |

|||

|

|

|

|

|

|

|

|||

S16-S19 |

Output |

P93-P90 |

Segment signal output |

|

Input |

H |

|||

|

|

|

|

|

|

|

|||

S20-S23 |

Output |

P83-P80 |

Segment signal output |

|

Input |

H |

|||

|

|

|

|

|

|

|

|

||

COM0-COM3 |

Output |

– |

Common signal output |

|

Note 2 |

G-B |

|||

|

|

|

|

|

|

|

|

||

VLC0-VLC2 |

– |

– |

LCD drive power |

|

– |

– |

|||

|

|

|

|

|

On-chip split resistor is enabled (mask option). |

|

|

||

|

|

|

|

|

|

|

|||

BIAS |

Output |

– |

Output for external split resistor disconnect |

Note 3 |

– |

||||

|

|

|

|

|

|

|

|||

LCDCL Note 4 |

Output |

P30 |

Clock output for externally expanded driver |

Input |

E-B |

||||

SYNC Note 4 |

Output |

P31 |

Clock output for externally expanded driver |

Input |

E-B |

||||

|

|

|

|

|

synchronization |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Notes 1. Characters in parentheses indicate the Schmitt trigger input.

2.Each display output selects the following VLCX as input source. S0-S15: VLC1, COM0-COM2: VLC2, COM3: VLC0

3.When a split resistor is contained ........ Low level

When no split resistor is contained ...... High-impedance

4.These pins are provided for future system expansion.

At present, these pins are used only as pins P30 and P31.

11

μPD753104, 753106, 753108

3.2 Non-port Pins (2/2)

|

Pin Name |

Input/Output |

Alternate |

Function |

After Reset |

I/O Circuit |

|

|

Function |

TYPE Note |

|||||

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

X1 |

Input |

– |

Crystal/ceramic connection pin for the main |

– |

– |

|

|

|

|

|

|

system clock oscillation. When the external |

|

|

|

X2 |

– |

|

|

|

||

|

|

clock is used, input the external clock to pin |

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

X1, and the inverted phase of the external clock |

|

|

|

|

|

|

|

to pin X2. |

|

|

|

|

|

|

|

|

|

|

|

XT1 |

Input |

– |

Crystal connection pin for the subsystem clock |

– |

– |

|

|

oscillation. When the external clock is used, input |

||||||

|

|

|

|

|

|

|

|

|

XT2 |

– |

|

|

|

||

|

|

the external clock to pin XT1, and the inverted |

|

|

|||

|

|

|

|

|

phase of the external clock to pin XT2. Pin XT1 can |

|

|

|

|

|

|

|

be used as a 1-bit input (test) pin. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

RESET |

Input |

– |

System reset input (low-level active) |

– |

(B) |

|

|

|

|

|

|

|

|

|

|

IC |

– |

– |

Internally connected. Connect directly to VDD. |

– |

– |

|

|

|

|

|

|

|

|

|

|

VDD |

– |

– |

Positive power supply |

– |

– |

|

|

|

|

|

|

|

|

|

|

VSS |

– |

– |

Ground potential |

– |

– |

|

|

|

|

|

|

|

|

|

Note Characters in parentheses indicate the Schmitt trigger input.

12

μPD753104, 753106, 753108

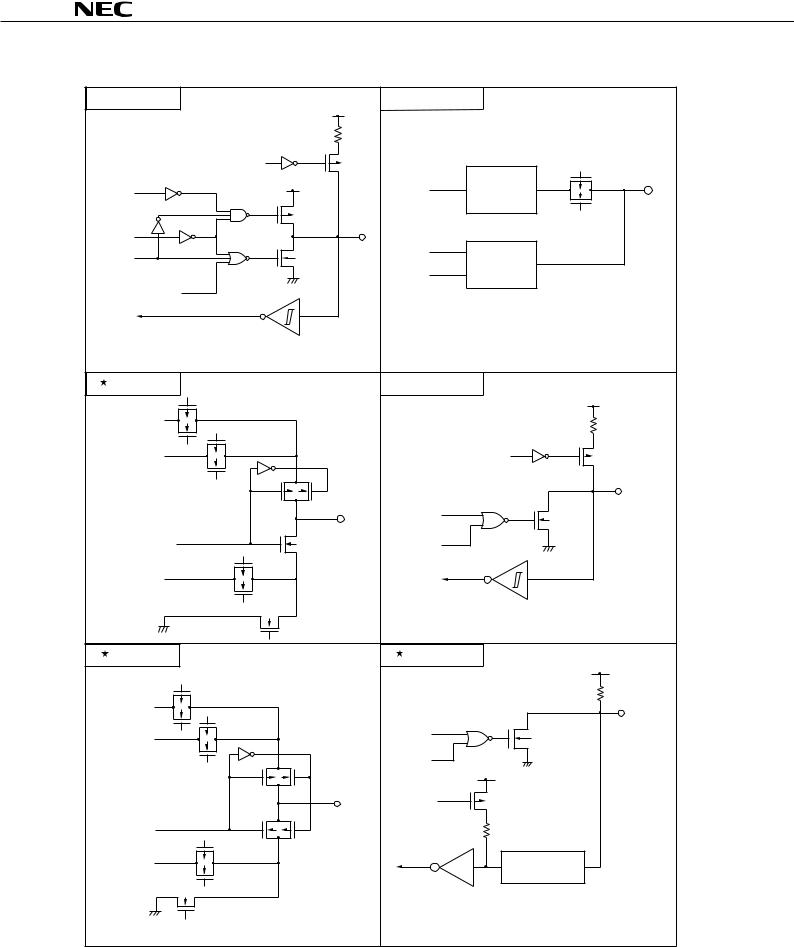

3.3 Pin Input/Output Circuits

The μPD753108 pin input/output circuits are shown schematically.

(1/2)

TYPE A |

TYPE D |

|

|

|

|

VDD |

|

VDD |

|

|

|

|

data |

P-ch |

|

|

|

||

P-ch |

|

OUT |

|

IN |

|

|

|

|

output |

N-ch |

|

N-ch |

disable |

||

|

|

|

Push-pull output that can be placed in output |

||

CMOS standard input buffer |

|

high-impedance (both P-ch and N-ch off). |

|

|

TYPE B |

|

TYPE E-B |

|

|

|

|

VDD |

||

|

|

|

P.U.R. |

|

|

|

P.U.R. |

P-ch |

|

|

|

enable |

||

|

|

|

||

IN |

|

|

|

|

|

|

data |

IN/OUT |

|

|

|

Type D |

||

|

|

|

||

|

|

output |

|

|

|

|

disable |

|

|

|

|

Type A |

|

|

Schmitt trigger input with hysteresis characteristics |

|

|

||

|

|

P.U.R. : Pull-Up Resistor |

|

|

TYPE B-C |

|

TYPE F-A |

|

|

|

|

|

VDD |

|

VDD |

|

|

P.U.R. |

|

|

|

|

||

P.U.R. |

|

P.U.R. |

P-ch |

|

|

|

enable |

||

|

|

|

||

P-ch |

P.U.R. |

data |

|

|

enable |

IN/OUT |

|||

|

|

|||

|

|

Type D |

|

|

|

|

output |

|

|

|

|

disable |

|

|

IN |

|

|

|

|

|

|

Type B |

|

|

P.U.R. : Pull-Up Resistor |

P.U.R. : Pull-Up Resistor |

|||

13

μPD753104, 753106, 753108

|

|

|

|

|

(2/2) |

|

TYPE F-B |

|

VDD |

TYPE H |

|

|

|

|

|

|

|

|

||

|

|

P.U.R. |

|

|

|

|

|

P.U.R |

P-ch |

|

|

|

|

|

enable |

|

|

|

||

|

|

|

|

IN/OUT |

||

output |

VDD |

SEG |

TYPE G-A |

|||

|

||||||

disable |

|

|

data |

|

||

|

|

|

|

|||

(P) |

|

P-ch |

|

|

|

|

|

|

|

|

|

||

data |

|

IN/OUT |

|

|

|

|

|

|

|

|

|

||

output |

|

N-ch |

data |

TYPE E-B |

|

|

disable |

|

output |

|

|||

|

|

|

||||

|

|

|

|

|

||

output |

|

|

disable |

|

|

|

disable |

|

|

|

|

|

|

(N) |

|

|

|

|

|

|

P.U.R. : Pull-Up Resistor |

|

|

|

|

||

TYPE G-A |

|

|

TYPE M-C |

|

|

|

|

|

|

|

|

VDD |

|

VLC0 |

P-ch |

|

|

|

P.U.R. |

|

N-ch |

|

|

|

|||

|

|

|

|

|||

P-ch |

|

|

|

P.U.R. |

P-ch |

|

VLC1 |

|

|

|

enable |

||

N-ch |

|

|

|

|

||

|

P-ch |

N-ch |

|

|

IN/OUT |

|

|

|

|

|

|

||

|

|

OUT |

data |

N-ch |

|

|

|

|

|

|

|||

SEG |

|

|

output |

|

|

|

data |

N-ch |

|

disable |

|

|

|

|

|

|

|

|

||

VLC2 |

P-ch |

|

|

|

|

|

N-ch |

|

|

|

|

||

|

|

|

|

|

||

|

N-ch |

|

|

|

|

|

|

|

|

|

P.U.R. : Pull-Up Resistor |

|

|

TYPE G-B |

|

|

TYPE M-D |

|

VDD |

|

|

|

|

|

|

||

|

|

|

|

|

|

P.U.R. |

VLC0 |

P-ch |

|

|

|

|

(Mask Option) |

|

|

|

|

|

||

N-ch |

|

|

|

|

IN/OUT |

|

|

|

|

|

|

||

VLC1 |

P-ch |

|

data |

|

N-ch |

|

N-ch |

|

|

|

|

||

|

|

output |

|

(+13 V |

|

|

|

P-ch |

N-ch |

|

withstand |

|

|

|

disable |

VDD |

|

|||

|

|

|

voltage) |

|

||

|

|

|

|

|

||

|

|

OUT |

input |

P-ch |

|

|

|

|

instruction |

|

|||

|

|

|

|

|

||

COM |

|

|

|

|

Note |

|

|

|

|

|

P.U.R. |

|

|

data |

|

|

|

|

|

|

N-ch P-ch |

|

|

|

|

||

|

|

|

|

|

||

VLC2 |

P-ch |

|

|

|

Voltage limitation |

|

N-ch |

|

|

|

|

||

|

|

|

|

circuit |

(+13 V withstand |

|

|

|

|

|

|

||

|

N-ch |

|

|

|

|

voltage) |

|

|

|

|

|

|

|

Note The pull-up resistor operates only when an input instruction is executed (current flows from VDD to the pin when the pin is low).

14

μPD753104, 753106, 753108

3.4 Recommended Connections for Unused Pins

Table 3-1. List of Recommended Connections for Unused Pins

|

|

Pin |

|

Recommended Connection |

|

|

|

|

|

P00/INT4 |

Connect to VSS or VDD |

|||

|

|

|

|

|

|

|

|

|

|

P01/SCK |

Connect to VSS or VDD via a resistor individually |

|||

|

|

|

|

|

P02/SO/SB0 |

|

|

||

|

|

|

|

|

P03/SI/SB1 |

Connect to VSS |

|||

|

|

|

|

|

P10/INT0, P11/INT1 |

Connect to VSS or VDD |

|||

|

|

|

|

|

P12/TI1/TI2/INT2 |

|

|

||

|

|

|

|

|

P13/TI0 |

|

|

||

|

|

|

|

|

P20/PTO0 |

Input state: |

Connect to VSS or VDD via a resistor |

||

|

|

|

|

|

P21/PTO1 |

|

individually |

||

|

|

|

|

|

P22/PCL/PTO2 |

Output state: Leave open |

|||

|

|

|

|

|

P23/BUZ |

|

|

||

|

|

|

|

|

P30/LCDCL |

|

|

||

|

|

|

|

|

P31/SYNC |

|

|

||

|

|

|

|

|

P32 |

|

|

||

|

|

|

|

|

P33 |

|

|

||

|

|

|

|

|

P50-P53 |

Input state: |

Connect to VSS |

||

|

|

|

Output state: Connect to VSS (do not connect a |

|

|

|

|

|

pull-up resistor of mask option) |

|

|

|

|

|

P60/KR0-P63/KR3 |

Input state: |

Connect to VSS or VDD via a resistor |

||

|

|

|

|

individually |

|

|

|

Output state: Leave open |

|

|

|

|

|

|

S0-S15 |

Leave open |

|

||

|

|

|

||

COM0-COM3 |

|

|

||

|

|

|

||

S16/P93-S19/P90 |

Input state: |

Connect to VSS or VDD via a resistor |

||

|

|

|

|

individually |

|

|

|||

S20/P83-S23/P80 |

Output state: Leave open |

|||

|

|

|||

VLC0-VLC2 |

Connect to VSS |

|||

|

|

|||

BIAS |

Only if all of VLC0 to VLC2 are unused, connect to VSS. |

|||

|

|

|

In other cases, leave open. |

|

|

|

|||

XT1 Note |

Connect to VSS or VDD |

|||

XT2 Note |

Leave open |

|

||

IC |

Connect directly to VDD |

|||

|

|

|

|

|

Note When the subsystem clock is not used, specify SOS.0 = 1 (so as not

to use the on-chip feedback resistor).

15

μPD753104, 753106, 753108

4. SWITCHING FUNCTION BETWEEN Mk I MODE AND Mk II MODE

4.1 Difference between Mk I Mode and Mk II Mode

The CPU of the μPD753108 has the following two modes: Mk I and Mk II, either of which can be selected. The mode can be switched by bit 3 of the stack bank select register (SBS).

• Mk I mode: Upward compatible with the μPD75308B. Can be used in the 75XL CPU with a ROM capacity of up to 16 Kbytes.

• Mk II mode: Incompatible with the μPD75308B. Can be used in all the 75XL CPU’s including those products whose ROM capacity is more than 16 Kbytes.

Table 4-1. Differences between Mk I Mode and Mk II Mode

|

Mk I mode |

Mk II mode |

|

|

|

Number of stack bytes |

2 bytes |

3 bytes |

for subroutine instructions |

|

|

|

|

|

BRA !addr1 instruction |

Not available |

Available |

CALLA !addr1 instruction |

|

|

|

|

|

CALL !addr instruction |

3 machine cycles |

4 machine cycles |

|

|

|

CALLF !faddr instruction |

2 machine cycles |

3 machine cycles |

|

|

|

Caution The Mk II mode supports a program area exceeding 16 Kbytes for the 75X and 75XL Series. Therefore, this mode is effective for enhancing software compatibility with products exceeding 16 Kbytes.

When the Mk II mode is selected, the number of stack bytes used during execution of subroutine call instructions increases by one byte per stack compared to the Mk I mode. When the CALL !addr and CALLF !faddr instructions are used, the machine cycle becomes longer by one machine cycle. Therefore, use the Mk I mode if the RAM efficiency and processing performance are more important than software compatibility.

16

μPD753104, 753106, 753108

4.2 Setting Method of Stack Bank Select Register (SBS)

Switching between the Mk I mode and Mk II mode can be done by the stack bank select register (SBS). Figure 4-1 shows the format.

The SBS is set by a 4-bit memory manipulation instruction.

When using the Mk I mode, the SBS must be initialized to 100xB Note at the beginning of a program. When using the Mk II mode, it must be initialized to 000xB Note.

Note Set the desired value in the x position.

Figure 4-1. Stack Bank Select Register Format

Address |

3 |

2 |

1 |

0 |

Symbol |

||

F84H |

SBS3 |

SBS2 |

SBS1 |

SBS0 |

SBS |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Stack area specification

|

0 |

0 |

Memory bank 0 |

|

|

|

|

|

0 |

1 |

Memory bank 1 |

|

|

|

|

Other than above setting prohibited

0 0 must be set in the bit 2 position.

Mode switching specification

0 Mk II mode

1 Mk I mode

Caution Since SBS. 3 is set to “1” after a RESET signal is generated, the CPU operates in the Mk I mode. When executing an instruction in the Mk II mode, set SBS. 3 to “0” to select the Mk II mode.

17

μPD753104, 753106, 753108

5. MEMORY CONFIGURATION

Program Memory (ROM) .... 4096 x 8 bits (μPD753104)

Program Memory (ROM) .... 4096 x 8 bits (μPD753104)

.... 6144 x 8 bits (μPD753106)

.... 8192 x 8 bits (μPD753108)

•Addresses 0000H and 0001H

Vector table wherein the program start address and the values set for the RBE and MBE at the time a RESET signal is generated are written. Reset start is possible from any address.

•Addresses 0002H to 000DH

Vector table wherein the program start address and the values set for the RBE and MBE by each vectored interrupt are written. Interrupt processing can start from any address.

•Addresses 0020H to 007FH

Table area referenced by the GETI instruction Note.

Note The GETI instruction realizes a 1-byte instruction on behalf of any 2-byte instruction, 3-byte instruction, or two 1-byte instructions. It is used to decrease the number of program steps.

Data Memory (RAM)

Data Memory (RAM)

•Data area ... 512 words x 4 bits (000H to 1FFH)

•Peripheral hardware area ... 128 words x 4 bits (F80H to FFFH)

18

μPD753104, 753106, 753108

Figure 5-1. Program Memory Map (1/3)

|

|

|

|

|

|

|

(a) μPD753104 |

|

Address |

7 |

6 |

5 |

4 |

|

|

0 |

|

|

|

|

|

|||||

0 0 0 |

H |

MBE |

RBE |

0 |

0 |

Internal reset start address |

(high-order 4 bits) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Internal reset start address |

(low-order 8 bits) |

|

|

|

|

|

|

|

|

|

|

0 0 2 |

H |

MBE |

RBE |

0 |

0 |

INTBT/INT4 |

start address |

(high-order 4 bits) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

INTBT/INT4 |

start address |

(low-order 8 bits) |

|

|

|

|

|

|

|

|

|

0 0 4 |

H |

MBE |

RBE |

0 |

0 |

INT0 |

start address |

(high-order 4 bits) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

INT0 |

start address |

(low-order 8 bits) |

|

|

|

|

|

|

|

|

|

0 0 6 |

H |

MBE |

RBE |

0 |

0 |

INT1 |

start address |

(high-order 4 bits) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

INT1 |

start address |

(low-order 8 bits) |

|

|

|

|

|

|

|

|

|

0 0 8 |

H |

MBE |

RBE |

0 |

0 |

INTCSI |

start address |

(high-order 4 bits) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

INTCSI |

start address |

(low-order 8 bits) |

|

|

|

|

|

|

|

|

|

0 0 A H |

MBE |

RBE |

0 |

0 |

INTT0 |

start address |

(high-order 4 bits) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

INTT0 |

start address |

(low-order 8 bits) |

|

|

|

|

|

|

|

|

|

0 0 C H |

MBE |

RBE |

0 |

0 |

INTT1/INTT2 |

start address |

(high-order 4 bits) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

INTT1/INTT2 |

start address |

(low-order 8 bits) |

0 2 0 H

GETI instruction reference table

0 7 F H

0 8 0 H

7 F F H

8 0 0 H

F F F H

CALLF !faddr instruction

entry

address Branch address of BR BCXA, BR

BCDE, BR !addr, BRA !addr1 Note or CALLA !addr1 Note instruction

CALL !addr instruction subroutine entry address

BR $addr instruction relative branch address

–15 to –1, +2 to +16

BRCB !caddr instruction branch address

Branch destination address and subroutine entry address when GETI instruction is executed

Note Can be used in Mk II mode only.

Remark In addition to the above, a branch can be taken to the address indicated by changing only the low-order eight bits of PC by executing the BR PCDE or BR PCXA instruction.

19

μPD753104, 753106, 753108

Figure 5-1. Program Memory Map (2/3)

|

|

|

|

|

|

(b) |

μPD753106 |

Address |

7 |

6 |

5 |

|

|

0 |

|

|

|

|

|

||||

0 0 0 0 |

H |

MBE |

RBE |

0 |

Internal reset start address |

(high-order 5 bits) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Internal reset start address |

(low-order 8 bits) |

|

|

|

|

|

|

|

|

|

0 0 0 2 |

H |

MBE |

RBE |

0 |

INTBT/INT4 |

start address |

(high-order 5 bits) |

|

|

|

|

|

|

|

|

|

|

|

|

|

INTBT/INT4 |

start address |

(low-order 8 bits) |

|

|

|

|

|

|

|

|

0 0 0 4 |

H |

MBE |

RBE |

0 |

INT0 |

start address |

(high-order 5 bits) |

|

|

|

|

|

|

|

|

|

|

|

|

|

INT0 |

start address |

(low-order 8 bits) |

|

|

|

|

|

|

|

|

0 0 0 6 |

H |

MBE |

RBE |

0 |

INT1 |

start address |

(high-order 5 bits) |

|

|

|

|

|

|

|

|

|

|

|

|

|

INT1 |

start address |

(low-order 8 bits) |

|

|

|

|

|

|

|

|

0 0 0 8 |

H |

MBE |

RBE |

0 |

INTCSI |

start address |

(high-order 5 bits) |

|

|

|

|

|

|

|

|

|

|

|

|

|

INTCSI |

start address |

(low-order 8 bits) |

|

|

|

|

|

|

|

|

0 0 0 A H |

MBE |

RBE |

0 |

INTT0 |

start address |

(high-order 5 bits) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

INTT0 |

start address |

(low-order 8 bits) |

|

|

|

|

|

|

|

|

0 0 0 C H |

MBE |

RBE |

0 |

INTT1/INTT2 |

start address |

(high-order 5 bits) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

INTT1/INTT2 |

start address |

(low-order 8 bits) |

0 0 2 0 H

GETI instruction reference table

0 0 7 F H

0 0 8 0 H

0 7 F F H

0 8 0 0 H

0 F F F H

1 0 0 0 H

|

|

|

|

|

|

|

Branch address |

||

|

|

of BR BCXA, BR |

||

CALLF |

||||

BCDE, BR !addr, |

||||

!faddr |

||||

BRA !addr1 Note or |

||||

instruction |

||||

CALLA !addr1 Note |

||||

entry |

||||

instruction |

||||

address |

||||

|

|

|||

|

|

CALL !addr |

||

|

|

instruction |

||

|

|

subroutine entry |

||

|

|

address |

||

|

|

BR $addr |

||

|

|

instruction relative |

||

|

|

branch address |

||

|

|

–15 to –1, |

||

|

|

+2 to +16 |

||

|

|

|

|

|

BRCB !caddr instruction branch address

Branch destination address and subroutine entry address when GETI instruction is executed

BRCB !caddr instruction branch address

1 7 F F H

Note Can be used in Mk II mode only.

Remark |

In addition to the above, a branch can be taken to the address indicated by changing only the low-order |

20 |

eight bits of PC by executing the BR PCDE or BR PCXA instruction. |

μPD753104, 753106, 753108

Figure 5-1. Program Memory Map (3/3)

|

|

|

|

|

|

(c) |

μPD753108 |

Address |

7 |

6 |

5 |

|

|

0 |

|

|

|

|

|

||||

0 0 0 0 |

H |

MBE |

RBE |

0 |

Internal reset start address |

(high-order 5 bits) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Internal reset start address |

(low-order 8 bits) |

|

|

|

|

|

|

|

|

|

0 0 0 2 |

H |

MBE |

RBE |

0 |

INTBT/INT4 |

start address |

(high-order 5 bits) |

|

|

|

|

|

|

|

|

|

|

|

|

|

INTBT/INT4 |

start address |

(low-order 8 bits) |

|

|

|

|

|

|

|

|

0 0 0 4 |

H |

MBE |

RBE |

0 |

INT0 |

start address |

(high-order 5 bits) |

|

|

|

|

|

|

|

|

|

|

|

|

|

INT0 |

start address |

(low-order 8 bits) |

|

|

|

|

|

|

|

|

0 0 0 6 |

H |

MBE |

RBE |

0 |

INT1 |

start address |

(high-order 5 bits) |

|

|

|

|

|

|

|

|

|

|

|

|

|

INT1 |

start address |

(low-order 8 bits) |

|

|

|

|

|

|

|

|

0 0 0 8 |

H |

MBE |

RBE |

0 |

INTCSI |

start address |

(high-order 5 bits) |

|

|

|

|

|

|

|

|

|

|

|

|

|

INTCSI |

start address |

(low-order 8 bits) |

|

|

|

|

|

|

|

|

0 0 0 A H |

MBE |

RBE |

0 |

INTT0 |

start address |

(high-order 5 bits) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

INTT0 |

start address |

(low-order 8 bits) |

|

|

|

|

|

|

|

|

0 0 0 C H |

MBE |

RBE |

0 |

INTT1/INTT2 |

start address |

(high-order 5 bits) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

INTT1/INTT2 |

start address |

(low-order 8 bits) |

0 0 2 0 H

GETI instruction reference table

0 0 7 F H

0 0 8 0 H

0 7 F F H

0 8 0 0 H

0 F F F H

1 0 0 0 H

|

|

|

|

|

|

|

Branch address |

||

|

|

of BR BCXA, BR |

||

CALLF |

||||

BCDE, BR !addr, |

||||

!faddr |

BRA !addr1 Note or |

|||

instruction |

CALLA !addr1 Note |

|||

entry |

instruction |

|||

address |

||||

|

|

|||

|

|

CALL !addr |

||

|

|

instruction |

||

|

|

subroutine entry |

||

|

|

address |

||

|

|

BR $addr |

||

|

|

instruction relative |

||

|

|

branch address |

||

|

|

–15 to –1, |

||

|

|

+2 to +16 |

||

|

|

|

|

|

BRCB !caddr instruction branch address

Branch destination address and subroutine entry address when GETI instruction is executed

BRCB !caddr instruction branch address

1 F F F H

Note Can be used in Mk II mode only.

Remark In addition to the above, a branch can be taken to the address indicated by changing only the low-order eight bits of PC by executing the BR PCDE or BR PCXA instruction.

21

μPD753104, 753106, 753108

Figure 5-2. Data Memory Map

0 0 0 H

General-purpose register area

0 1 F H

|

Stack area Note |

|

Data area |

0 F F H |

|

static RAM |

1 0 0 H |

|

(512 x 4) |

||

|

1 D F H

1 E 0 H Display data

1 E 0 H Display data

memory

1 F 7 H

1 F 8 H

1 F F H

Data memory |

Memory bank |

(32 x 4)

0

256 x 4

(224 x 4)

256 x 4

(224 x 4)

1

(24 x 4)

(8 x 4)

Not incorporated

F 8 0 H

Peripheral hardware area |

128 x 4 |

15 |

F F F H

Note Either memory bank 0 or 1 can be selected for the stack area.

22

μPD753104, 753106, 753108

6. PERIPHERAL HARDWARE FUNCTION

6.1 Digital I/O Port

There are three kinds of I/O port.

• CMOS input ports (PORT 0, 1) |

: 8 |

•CMOS input/output ports (PORT 2, 3, 6, 8, 9) : 20

•N-ch open-drain input/output ports (PORT 5) : 4

Total |

|

|

|

32 |

|

|

|

|

|

|

Table 6-1. Types and Features of Digital Ports |

|

|

|

|||

|

|

|

|

|

|

|

|

|

Port name |

Function |

|

Operation and features |

Remarks |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

PORT0 |

4-bit input |

|

When the serial interface function is used, the dual |

Also used for the INT4, SCK, |

||||

|

|

|

function pins function as output ports depending on the |

SO/SB0, SI/SB1 pins. |

||||

|

|

|

operation mode. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PORT1 |

|

|

4-bit input only port. |

|

|

Also used for the INT0-INT2/ |

||

|

|

|

|

|

|

TI1/TI2, TI0 pins. |

||

|

|

|

|

|

|

|

|

|

PORT2 |

4-bit input/ |

|

Can be set to input mode or output mode in 4-bit units. |

Also used for the PTO0- |

||||

|

output |

|

|

|

|

PTO2/PCL, BUZ pins. |

||

|

|

|

|

|

|

|

|

|

PORT3 |

|

|

Can be set to input mode or output mode bit-wise. |

Also used for the LCDCL, |

||||

|

|

|

|

|

|

SYNC pins. |

||

|

|

|

|

|

|

|

|

|

PORT5 |

4-bit input/ |

|

Can be set to input mode or output mode in 4-bit units. |

— |