Siemens TLE4269GM, TLE4269GL, TLE4269G, TLE4269A Datasheet

TLE 4269

5-V Low-Drop Fixed Voltage Regulator |

TLE 4269 |

Features

●Output voltage tolerance ≤ ± 2 %

●Very low current consumption

●Early warning

●Reset output low doown to VQ = 1 V

●Overtemperature protection

●Reverse polarity proof

●Settable reset threshold

●Very low drop voltage

●Wide temperature range

●Integrated pull up resistor at logic outputs

|

Type |

Ordering Code |

Package |

|

|

|

|

|

|

|

TLE 4269 A |

Q67000-A9190 |

P-DIP-8-4 |

|

|

|

|

|

|

|

|

TLE 4269 G |

Q67006-A9173 |

P-DSO-8-1 (SMD) |

|

|

|

|

|

▼ |

TLE 4269 GM |

Q67006-A9288 |

P-DSO-14-4 (SMD) |

|

|

|

|

|

|

|

|

TLE 4269 GL |

Q67006-A9192 |

P-DSO-20-6 (SMD) |

|

|

|

|

|

|

▼ New type |

|

|

|

Functional Description

This device is a voltage regulator with a fixed 5-V output, e.g. in a P-DSO-8-1 package. The maximum operating voltage is 45 V. The output is able to drive a 150 mA load. It is short circuit protected and the thermal shutdown switches the output off if the junction temperature is in excess of 150 °C. A reset signal is generated for an output voltage of VQ < 4.6 V. The reset threshold voltage can be decreased by external connection of a voltage divider. The reset delay time can be set by an external capacitor. Reset and sense output have integrated pull up resistors. If the integrated resistors are not desired TLE 4279 can be used. It is also possible to supervise the input voltage by using an integrated comparator to give a low voltage warning.

P-DIP-8-4

P-DSO-8-1

P-DSO-20-6

P-DSO-14-4

Semiconductor Group |

1 |

1998-11-01 |

TLE 4269

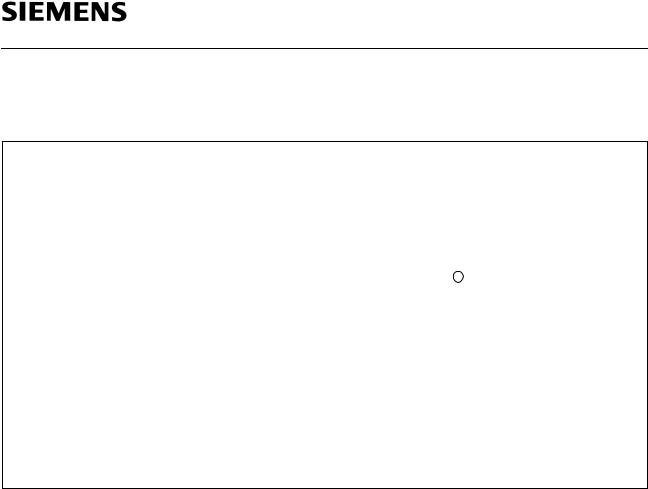

Pin Configuration

(top view)

|

|

|

P-DIP-8-4 |

|

|

|

|

P-DSO-8-1 |

|

||||||

|

|

|

|

|

|

|

|

Ι |

|

|

|

|

|

|

|

Ι |

|

|

|

|

|

|

|

|

|

1 |

8 |

|

|

Q |

|

|

1 |

8 |

|

Q |

|

|

|

|

|||||||

|

|

S Ι |

|

|

2 |

7 |

|

|

SO |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

RE |

|

|

3 |

6 |

|

|

R |

|

S Ι |

|

2 |

7 |

|

SO |

|

|

|

|

||||||

|

|

|

|

||||||||||||

|

|

3 |

6 |

|

R |

D |

|

|

4 |

5 |

|

|

GND |

||

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

||||||

RE |

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

AEP01668 |

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

D |

|

4 |

5 |

|

GND |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AEP01813 |

|

|

|

|

|

|

|

|

|

|

Pin Definitions and Functions (TLE 4269 A and TLE 4269 G)

Pin No. |

Symbol |

Function |

|

|

|

1 |

I |

Input; block directly to GND on the IC with a ceramic capacitor. |

|

|

|

2 |

SI |

Sense Input; if not needed connect to Q. |

|

|

|

3 |

RE |

Reset Threshold; if not needed connect to ground. |

|

|

|

4 |

D |

Reset Delay; to select delay time, connect to GND via external |

|

|

capacitor. |

|

|

|

5 |

GND |

Ground |

|

|

|

6 |

R |

Reset Output; the open-collector output is internally linked to Q |

|

|

via a 20 kΩ pull-up resistor. |

|

|

|

7 |

SO |

Sense Output; the open-collector output is internally linked to the |

|

|

output via a 20 kΩ pull-up resistor. |

|

|

|

8 |

Q |

5-V Output; connect to GND with a 10 µF capacitor, ESR < 10 Ω. |

|

|

|

Semiconductor Group |

2 |

1998-11-01 |

TLE 4269

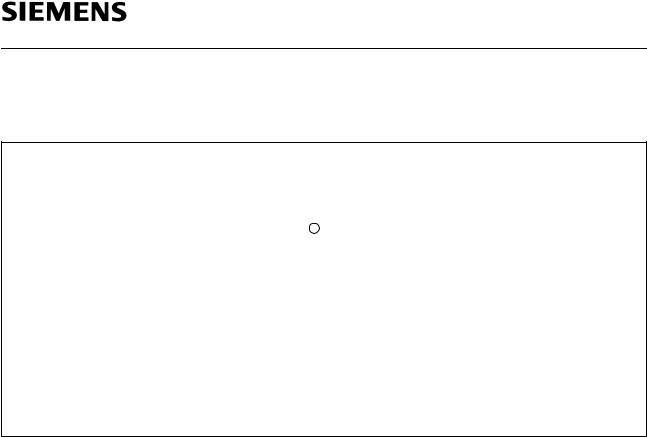

Pin Configuration

(top view)

P-DSO-14-4

RE |

|

1 |

14 |

|

|

SI |

|

|

|

|

|

||||

|

|

|

|||||

D |

|

2 |

13 |

|

|

Ι |

|

|

|

|

|

||||

GND |

|

|

3 |

12 |

|

|

GND |

|

|

|

|

||||

GND |

|

4 |

11 |

|

|

GND |

|

|

|

|

|

||||

GND |

|

5 |

10 |

|

|

GND |

|

|

|

|

|

||||

GND |

|

|

6 |

9 |

|

|

Q |

|

|

|

|

||||

R |

|

7 |

8 |

|

|

SO |

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

AEP02248 |

|

||

Pin Definitions and Functions (TLE 4269 GM)

Pin No. |

Symbol |

Function |

|

|

|

|

|

|

|

1 |

RE |

Reset Threshold; if not needed connect to GND. |

|

|

|

|

|

|

|

2 |

D |

Reset Delay; connect to GND via external delay capacitor for |

|

|

|

|

setting delay time. |

|

|

|

|

|

|

|

3, 4, 5, 6 |

GND |

Ground |

|

|

|

|

|

|

|

7 |

R |

Reset Output; open-collector output, internally connected to Q |

|

|

|

|

via a pull-up resistor of 20 kΩ. |

|

|

|

|

|

|

|

8 |

SO |

Sense Output; open-collector output, internally connected to Q |

|

|

|

|

via a 20 kΩ pull-up resistor. |

|

|

|

|

|

|

|

9 |

Q |

5-V Output; connect to GND with a 10 µF capacitor, ESR < 10 Ω. |

|

|

|

|

|

|

|

10, 11, 12 |

GND |

Ground |

|

|

|

|

|

|

|

13 |

I |

Input; block to GND directly at the IC by a ceramic capacitor. |

|

|

|

|

|

|

|

14 |

SI |

Sense Input; if not needed connect to Q. |

|

|

|

|

|

|

|

Semiconductor Group |

3 |

1998-11-01 |

TLE 4269

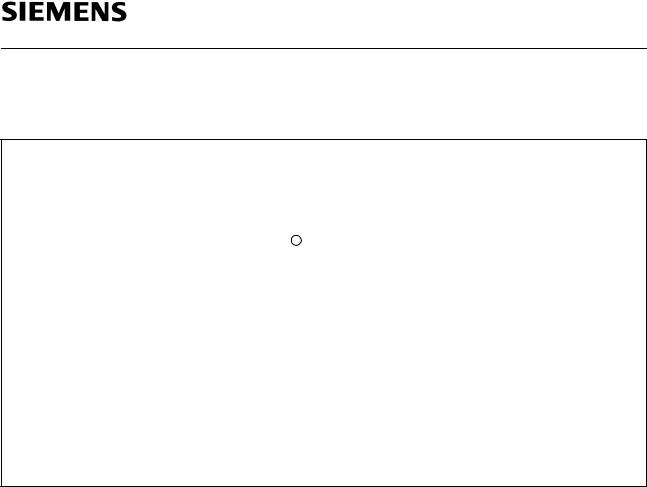

Pin Configuration

(top view)

P-DSO-20-6

RE |

|

1 |

20 |

|

|

SΙ |

|

|

|

|

|

||||

D |

|

2 |

19 |

|

|

Ι |

|

|

|

|

|

||||

N.C. |

|

3 |

18 |

|

|

N.C. |

|

|

|

|

|

||||

GND |

|

|

4 |

17 |

|

|

GND |

|

|

|

|

||||

GND |

|

|

5 |

16 |

|

|

GND |

|

|

|

|

||||

GND |

|

|

6 |

15 |

|

|

GND |

|

|

|

|

||||

GND |

|

|

7 |

14 |

|

|

GND |

|

|

|

|

||||

N.C. |

|

8 |

13 |

|

|

N.C. |

|

|

|

|

|

||||

N.C. |

|

|

9 |

12 |

|

|

Q |

|

|

|

|

||||

R |

|

10 |

11 |

|

|

SO |

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

AEP01802 |

|

||

Pin Definitions and Functions (TLE 4269 GL)

Pin No. |

Symbol |

Function |

|

|

|

1 |

RE |

Reset Threshold; if not needed connect to GND. |

|

|

|

2 |

D |

Reset Delay; to select delay time connect to GND via external |

|

|

capacitor. |

|

|

|

4-7, 14-17 |

GND |

Ground |

|

|

|

10 |

R |

Reset Output; the open-collector output is internally linked to |

|

|

Q via 20 kΩ pull-up resistor. |

|

|

|

11 |

SO |

Sense Output; the open-collector output is internally linked to |

|

|

Q via 20 kΩ pull-up resistor. |

|

|

|

12 |

Q |

Output; connect to GND with a 10 µF capacitor, ESR < 10 Ω. |

|

|

|

19 |

I |

Input; block directly to GND at the IC by a ceramic capacitor. |

|

|

|

20 |

SI |

Sense Input; if not needed connect to Q. |

|

|

|

Semiconductor Group |

4 |

1998-11-01 |

TLE 4269

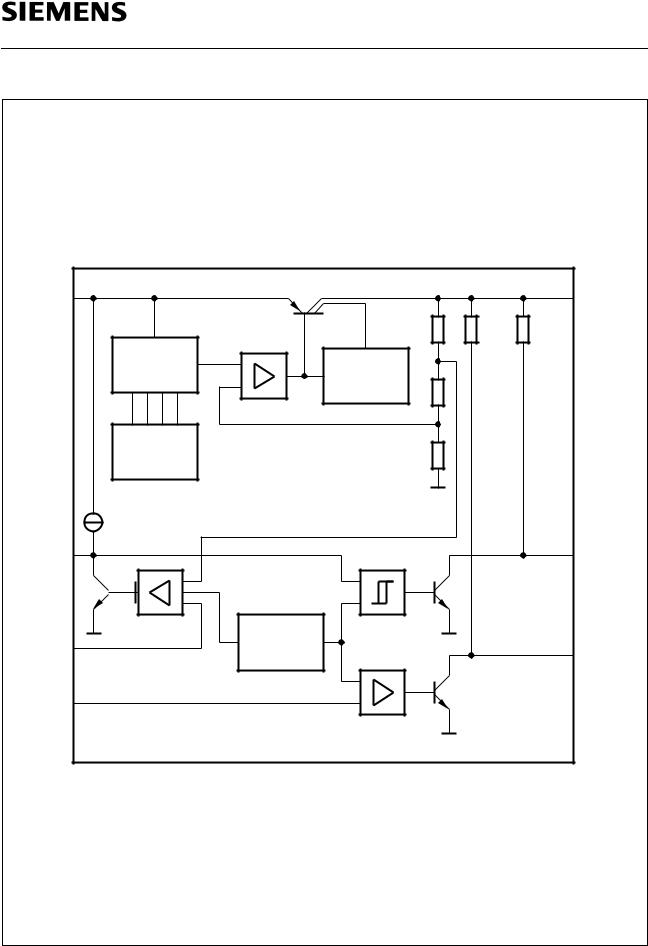

Circuit Description

The control amplifier compares a reference voltage, made highly accurate by resistance balancing, with a voltage proportional to the output voltage and drives the base of the series PNP transistor via a buffer. Saturation control as a function of the load current prevents any over-saturation of the power element.

In the reset generator block a comparator compares a reference voltage independent of the input voltage with the scaled-down output voltage. If the output voltage reaches 4.6 V the reset delay capacitor is discharged and the reset output is set to low. This low is guaranteed down to an output voltage of 1 V. As the output voltage increases again, from 4.6 V onward the reset delay capacitor is charged with constant current. When the capacitor voltage reaches the upper switching threshold VdT, the reset returns to high. By choosing the value of this capacitor, the reset delay time can be selected over a wide range. With the reset threshold input RE it is possible to lower the reset threshold Vrt. If pin RE is connected to pin Q via a voltage divider, for example, the reset condition is reached when this voltage is decreased below the switching threshold Vre of 1.35 V.

Another comparator compares the signal of the pin SI, normally fed by a voltage divider from the input voltage, with the reference and gives an early warning on the pin SO. It is also possible to superwise an other voltage e.g. of a second regulator, or to build a watchdog circuit with few external components.

Application Description

The input capacitor CI is necessary for compensating line influences. Using a resistor of approx. 1 Ω in series with CI, the oscillating circuit consisting of input inductivity and input capacitance can be damped. The output capacitor CQ is necessary for the stability of the regulating circuit. Stability is guaranteed at values ≥ 10 µF and an ESR ≤ 10 Ω within the operating temperature range. For small tolerances of the reset delay the spread of the capacitance of the delay capacitor and its temperature coefficient should be noted.

Semiconductor Group |

5 |

1998-11-01 |

TLE 4269

Ι |

|

|

Q |

|

Error |

20 kΩ |

20 kΩ |

|

Amplifier |

|

|

|

Reference |

Current and |

|

|

|

Saturation |

|

|

|

Control |

|

|

Trimming |

|

|

D |

|

|

R |

RE |

Reference |

|

SO |

|

|

||

|

|

|

|

SI |

|

|

|

|

|

|

AEB01669 |

Block Diagram

Semiconductor Group |

6 |

1998-11-01 |

Loading...

Loading...