Philips ISP1107W, ISP1107DH, ISP1107, ISP1106W, ISP1105 Datasheet

...

ISP1105/1106/1107

Advanced Universal Serial Bus transceivers

Rev. 06 — 30 November 2001 |

Product data |

1. General description

The ISP1105/1106/1107 range of Universal Serial Bus (USB) transceivers are fully compliant with the Universal Serial Bus Specification Rev. 1.1. They are ideal for portable electronics devices such as mobile phones, digital still cameras, Personal Digital Assistants (PDA) and Information Appliances (IA).

They allow USB Application Specific ICs (ASICs) and Programmable Logic Devices (PLDs) with power supply voltages from 1.65 V to 3.6 V to interface with the physical layer of the Universal Serial Bus. They have an integrated 5 V to 3.3 V voltage regulator for direct powering via the USB supply VBUS.

The ISP1105/1106/1107 range can be used as a USB device transceiver or a USB host transceiver. They can transmit and receive serial data at both full-speed

(12 Mbit/s) and low-speed (1.5 Mbit/s) data rates.

ISP1105 allows single/differential input modes selectable by a MODE input and it is available in HBCC16 package. ISP1106 allows only differential input mode and is available in both TSSOP16 and HBCC16 packages. ISP1107 allows only single-ended input mode and is available in both TSSOP16 and HBCC16 packages.

2. Features

■Complies with Universal Serial Bus Specification Rev. 1.1

■Integrated bypassable 5 V to 3.3 V voltage regulator for powering via USB VBUS

■VBUS disconnection indication through VP and VM

■Used as a USB device transceiver or a USB host transceiver

■Supports full-speed (12 Mbit/s) and low-speed (1.5 Mbit/s) serial data rates

■Stable RCV output during SE0 condition

■Two single-ended receivers with hysteresis

■Low-power operation

■Supports an I/O voltage range from 1.65 V to 3.6 V

■4 kV on-chip ESD protection

■Full industrial operating temperature range −40 to +85 °C

■Available in small TSSOP16 (except ISP1105) and HBCC16 packages.

Philips Semiconductors |

ISP1105/1106/1107 |

|

Advanced USB transceivers |

3. Applications

Portable electronic devices, such as:

Mobile phone

Digital still camera

Personal Digital Assistant (PDA)

Information Appliance (IA).

4.Ordering information

Table 1: Ordering information

Type number |

Package |

|

|

|

Name |

Description |

Version |

ISP1105W[1] |

HBCC16 |

plastic, heatsink bottom chip carrier; 16 terminals; body 3 × 3 × 0.65 mm |

SOT639-2 |

ISP1106W |

|

|

|

ISP1107W |

|

|

|

|

|

|

|

ISP1106DH |

TSSOP16 |

plastic thin shrink small outline package; 16 leads; body width 4.4 mm |

SOT403-1 |

ISP1107DH |

|

|

|

|

|

|

|

[1]The ground terminal of ISP1105W is connected to the exposed diepad (heatsink).

4.1 Ordering options

Table 2: |

Selection guide |

|

Product |

Package(s) |

Description |

ISP1105 |

HBCC16 |

Supports both single-ended and differential input modes[1] |

ISP1106 |

TSSOP16 or HBCC16 |

Supports only the differential input mode[2] |

ISP1107 |

TSSOP16 or HBCC16 |

Supports only the single-ended input mode[3] |

[1]Refer to Table 5 and Table 6.

[2]Refer to Table 6.

[3]Refer to Table 5.

9397 750 08872 |

© Koninklijke Philips Electronics N.V. 2001. All rights reserved. |

Product data |

Rev. 06 — 30 November 2001 |

2 of 24 |

Philips Semiconductors |

ISP1105/1106/1107 |

|

Advanced USB transceivers |

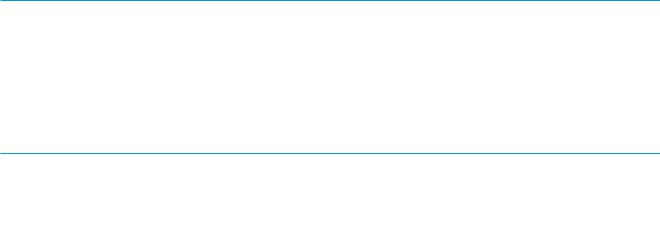

5. Functional diagram

VCC(I/O) |

3.3 V |

VOLTAGE |

VCC(5.0) |

|

|

|

|

||||

REGULATOR |

|

||||

|

|

|

Vreg(3.3) |

|

|

SOFTCON |

|

|

Vpu(3.3) |

|

|

|

|

|

|

|

|

OE |

|

|

|

33 Ω(1) |

1.5 kΩ(2) |

|

|

D+ |

(1%) |

||

SPEED |

|

|

|||

|

|

|

|

||

|

|

|

|

|

|

VMO/FSE0(3) |

|

|

D− |

|

|

VPO/VO(3) |

|

|

|

33 Ω(1) (1%) |

|

MODE(4) |

LEVEL |

|

|

|

|

SUSPND |

|

|

|

|

|

SHIFTER |

|

|

|

|

|

|

|

|

|

|

|

RCV |

ISP1105 |

|

|

|

|

|

ISP1106 |

|

|

|

|

|

ISP1107 |

|

|

|

|

VP |

|

|

|

|

|

VM |

|

|

|

|

|

|

|

|

MBL301 |

|

|

|

|

GND |

|

|

|

(1)Use a 39 Ω resistor (1%) for a USB v2.0 compliant output impedance range.

(2)Connect to D− for low-speed operation.

(3)Pin function depends on device type see Section 7.2.

(4)Only for ISP1105.

Fig 1. Functional diagram (combined ISP1105, ISP1106 and ISP1107).

9397 750 08872 |

© Koninklijke Philips Electronics N.V. 2001. All rights reserved. |

Product data |

Rev. 06 — 30 November 2001 |

3 of 24 |

Philips Semiconductors |

ISP1105/1106/1107 |

|

Advanced USB transceivers |

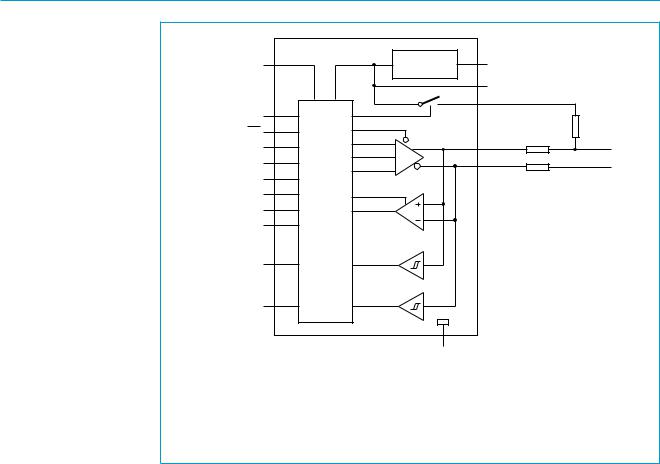

6.Pinning information

6.1Pinning

|

|

|

|

|

|

MODE |

CC(I/O) |

SPEED |

|

|

|

|

|

|

|

|

V |

|

|

||

SUSPND |

5 |

6 |

7 |

8 |

9 |

D- |

||||

|

|

|

|

|

|

|

|

D+ |

||

VM |

4 |

|

|

|

|

10 |

||||

|

|

|

|

|

|

ISP1105W |

11 |

VPO/VO |

||

|

VP |

3 |

|

|

|

|

||||

RCV |

2 |

|

GND |

|

|

12 |

VMO/FSE0 |

|||

|

(exposed diepad) |

|||||||||

|

|

|

1 |

|

|

|

|

13 |

Vreg(3.3) |

|

|

|

|

|

16 |

15 |

14 |

||||

|

OE |

|

|

|||||||

Bottom view |

|

|

SOFTCON |

pu(3.3) |

CC(5.0) |

|

MBL303 |

|||

|

|

V |

V |

|

||||||

Fig 2. Pinning diagram HBCC16 (ISP1105).

|

|

|

|

|

|

GND |

CC(I/O) |

SPEED |

|

|

|

|

|

|

|

|

V |

|

|

||

SUSPND |

5 |

6 |

7 |

8 |

9 |

D− |

||||

|

|

|

|

|

|

|

|

D+ |

||

VM |

4 |

|

|

|

|

10 |

||||

|

VP |

3 |

|

ISP1106W |

11 |

VPO/VO* |

||||

|

|

ISP1107W* |

||||||||

|

|

|

|

|

|

|

VMO/FSE0* |

|||

RCV |

2 |

|

|

|

|

12 |

||||

|

|

|

1 |

|

|

|

|

13 |

Vreg(3.3) |

|

|

|

|

|

16 |

15 |

14 |

||||

|

OE |

|

|

|||||||

Bottom view |

|

|

SOFTCON |

pu(3.3) |

CC(5.0) |

|

MBL304 |

|||

|

|

V |

V |

|

||||||

The asterisk (*) denotes that the signal names VO and FSE0 apply to the ISP1107W.

Fig 3. Pinning diagram HBCC16 (ISP1106 and ISP1107).

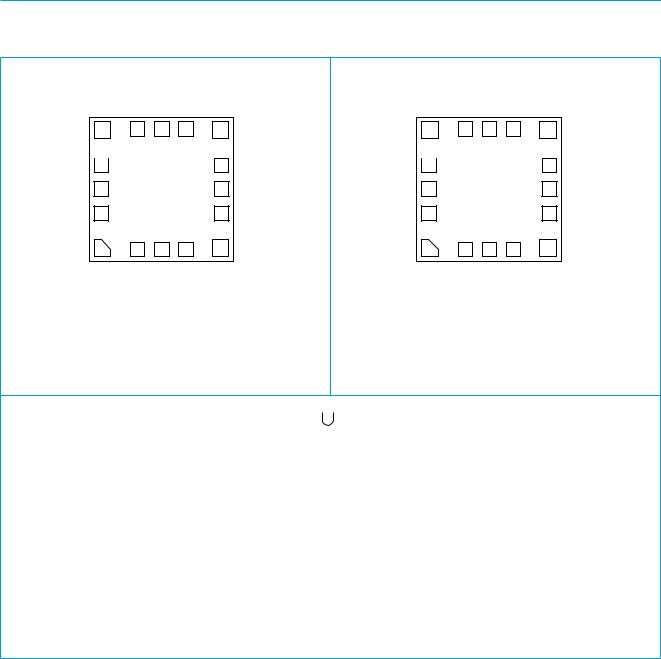

Vpu(3.3) |

|

|

|

VCC(5.0) |

||

1 |

|

16 |

||||

SOFTCON |

|

|

|

Vreg(3.3) |

||

2 |

|

15 |

||||

|

|

|

|

|

|

VMO/FSE0* |

OE |

3 |

|

14 |

|||

|

|

|

|

|

|

VPO/VO* |

RCV |

4 |

ISP1106DH |

13 |

|||

|

|

|

|

|

|

|

|

|

|

|

ISP1107DH* |

|

D+ |

|

VP |

5 |

12 |

|||

|

|

|

|

|

|

D− |

VM |

6 |

|

11 |

|||

|

|

|

|

|

|

|

SUSPND |

7 |

|

10 |

SPEED |

||

|

|

|

|

|

|

|

GND |

8 |

|

9 |

VCC(I/O) |

||

|

|

|

|

|

|

|

|

|

|

|

MBL302 |

|

|

The asterisk (*) denotes that the signal names VO and FSE0 apply to the ISP1107DH.

Fig 4. Pinning diagram TSSOP16 (ISP1106 and ISP1107).

9397 750 08872 |

© Koninklijke Philips Electronics N.V. 2001. All rights reserved. |

Product data |

Rev. 06 — 30 November 2001 |

4 of 24 |

Philips Semiconductors |

|

|

|

ISP1105/1106/1107 |

|

||||||

|

|

|

|

|

|

|

|

|

|

Advanced USB transceivers |

|

|

|

|

|

|

6.2 Pin description |

|

|

|

|||

Table 3: |

Pin description |

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

Symbol[1] |

|

Pin |

|

|

|

|

Type |

Description |

||

|

|

|

|

ISP1105 |

|

ISP1106/7 |

ISP1106/7 |

|

|

|

|

|

|

|

|

HBCC16 |

|

HBCC16 |

TSSOP16 |

|

|

|

|

|

|

|

1 |

1 |

3 |

|

I |

input for output enable (CMOS level with respect to VCC(I/O), |

|||

|

OE |

||||||||||

|

|

|

|

|

|

|

|

|

|

active LOW); enables the transceiver to transmit data on |

|

|

|

|

|

|

|

|

|

|

|

the USB bus |

|

|

|

|

|

|

|

|

|

||||

|

RCV |

2 |

2 |

4 |

|

O |

differential data receiver output (CMOS level with respect to |

||||

|

|

|

|

|

|

|

|

|

|

VCC(I/O)); driven LOW when input SUSPND is HIGH; the |

|

|

|

|

|

|

|

|

|

|

|

output state of RCV is preserved and stable during an SE0 |

|

|

|

|

|

|

|

|

|

|

|

condition |

|

|

|

|

|

|

|

|

|

||||

|

VP |

3 |

3 |

5 |

|

O |

single-ended D+ receiver output (CMOS level with respect |

||||

|

|

|

|

|

|

|

|

|

|

to VCC(I/O)); for external detection of single-ended zero |

|

|

|

|

|

|

|

|

|

|

|

(SE0), error conditions, speed of connected device; driven |

|

|

|

|

|

|

|

|

|

|

|

HIGH when no supply voltage is connected to VCC(5.0) and |

|

|

|

|

|

|

|

|

|

|

|

Vreg(3.3) |

|

|

VM |

4 |

4 |

6 |

|

O |

single-ended D− receiver output (CMOS level with respect |

||||

|

|

|

|

|

|

|

|

|

|

to VCC(I/O)); for external detection of single-ended zero |

|

|

|

|

|

|

|

|

|

|

|

(SE0), error conditions, speed of connected device; driven |

|

|

|

|

|

|

|

|

|

|

|

HIGH when no supply voltage is connected to VCC(5.0) and |

|

|

|

|

|

|

|

|

|

|

|

Vreg(3.3) |

|

|

SUSPND |

5 |

5 |

7 |

|

I |

suspend input (CMOS level with respect to VCC(I/O)); a |

||||

|

|

|

|

|

|

|

|

|

|

HIGH level enables low-power state while the USB bus is |

|

|

|

|

|

|

|

|

|

|

|

inactive and drives output RCV to a LOW level |

|

|

|

|

|

|

|

|

|

|

|||

|

MODE |

6 |

|

|

|

|

I |

mode input (CMOS level with respect to VCC(I/O)); a HIGH |

|||

|

|

|

|

|

|

|

|

|

|

level enables the differential input mode (VPO, VMO) |

|

|

|

|

|

|

|

|

|

|

|

whereas a LOW level enables a single-ended input mode |

|

|

|

|

|

|

|

|

|

|

|

(VO, FSE0). see Table 5 and Table 6 |

|

|

|

|

|

|

|

|

|

||||

|

GND |

-[2] |

6 |

8 |

|

- |

ground supply |

||||

|

VCC(I/O) |

7 |

7 |

9 |

|

- |

supply voltage for digital I/O pins (1.65 to 3.6 V). When |

||||

|

|

|

|

|

|

|

|

|

|

VCC(I/O) is not connected, the (D+, D−) pins are in |

|

|

|

|

|

|

|

|

|

|

|

three-state. This supply pin is totally independent of |

|

|

|

|

|

|

|

|

|

|

|

VCC(5.0) and Vreg(3.3) and must never exceed the Vreg(3.3) |

|

|

|

|

|

|

|

|

|

|

|

voltage. |

|

|

|

|

|

|

|

|

|

||||

|

SPEED |

8 |

8 |

10 |

|

I |

speed selection input (CMOS level with respect to VCC(I/O)); |

||||

|

|

|

|

|

|

|

|

|

|

adjusts the slew rate of differential data outputs D+ and D− |

|

|

|

|

|

|

|

|

|

|

|

according to the transmission speed: |

|

|

|

|

|

|

|

|

|

|

|

LOW: low-speed (1.5 Mbit/s) |

|

|

|

|

|

|

|

|

|

|

|

HIGH: full-speed (12 Mbit/s) |

|

|

|

|

|

|

|

|

|

||||

|

D− |

9 |

9 |

11 |

|

AI/O |

negative USB data bus connection (analog, differential); for |

||||

|

|

|

|

|

|

|

|

|

|

low-speed mode connect to pin Vpu(3.3) via a 1.5 kΩ resistor |

|

|

D+ |

10 |

10 |

12 |

|

AI/O |

positive USB data bus connection (analog, differential); for |

||||

|

|

|

|

|

|

|

|

|

|

full-speed mode connect to pin Vpu(3.3) via a 1.5 kΩ resistor |

|

|

VPO/VO |

11 |

11 |

13 |

|

I |

driver data input (CMOS level with respect to VCC(I/O), |

||||

|

|

|

|

|

|

|

|

|

|

Schmitt trigger); see Table 5 and Table 6 |

|

|

|

|

|

|

|

|

|

||||

|

VMO/FSE0 |

12 |

12 |

14 |

|

I |

driver data input (CMOS level with respect to VCC(I/O), |

||||

|

|

|

|

|

|

|

|

|

|

Schmitt trigger); see Table 5 and Table 6 |

|

9397 750 08872 |

|

|

|

|

|

|

|

© Koninklijke Philips Electronics N.V. 2001. All rights reserved. |

|

||

Product data |

Rev. 06 — 30 November 2001 |

5 of 24 |

Philips Semiconductors |

|

|

ISP1105/1106/1107 |

|

|||

|

|

|

|

|

|

Advanced USB transceivers |

|

Table 3: |

Pin description…continued |

|

|

|

|

||

|

|

|

|

|

|

|

|

Symbol[1] |

|

Pin |

|

|

Type |

Description |

|

|

|

ISP1105 |

ISP1106/7 |

ISP1106/7 |

|

|

|

|

|

HBCC16 |

HBCC16 |

TSSOP16 |

|

|

|

Vreg(3.3) |

13 |

13 |

15 |

- |

Internal regulator option: regulated supply voltage output |

||

|

|

|

|

|

|

(3.0 to 3.6 V) during 5 V operation; a decoupling capacitor |

|

|

|

|

|

|

|

of at least 0.1 μF is required |

|

|

|

|

|

|

|

Regulator bypass option: used as a supply voltage input |

|

|

|

|

|

|

|

for 3.3 V operation. (3.3 V ±10%) |

|

|

|

|

|

|

|

||

VCC(5.0) |

14 |

14 |

16 |

- |

Internal regulator option: supply voltage input |

||

|

|

|

|

|

|

(4.0 to 5.5 V); can be connected directly to USB supply |

|

|

|

|

|

|

|

VBUS |

|

|

|

|

|

|

|

Regulator bypass option: connect to Vreg(3.3) |

|

Vpu(3.3) |

15 |

15 |

1 |

- |

pull-up supply voltage (3.3 V ±10%); connect an external |

||

|

|

|

|

|

|

1.5 kΩ resistor on D+ (full-speed) or D− (low-speed); pin |

|

|

|

|

|

|

|

function is controlled by input SOFTCON: |

|

|

|

|

|

|

|

SOFTCON = LOW — Vpu(3.3) floating (high impedance); |

|

|

|

|

|

|

|

ensures zero pull-up current |

|

|

|

|

|

|

|

SOFTCON = HIGH — Vpu(3.3) = 3.3 V; internally connected |

|

|

|

|

|

|

|

to Vreg(3.3) |

|

SOFTCON |

16 |

16 |

2 |

I |

software controlled USB connection input; a HIGH level |

||

|

|

|

|

|

|

applies 3.3 V to pin Vpu(3.3), which is connected to an |

|

|

|

|

|

|

|

external 1.5 kΩ pull-up resistor; this allows USB |

|

connect/disconnect signalling to be controlled by software

[1]Symbol names with an overscore (e.g. NAME) indicate active LOW signals.

[2]Down bonded to the exposed diepad.

7.Functional description

7.1Function selection

Table 4: |

Function table |

|

|

|

|||

SUSPND |

|

OE |

|

(D+, D−) |

RCV |

VP/VM |

Function |

L |

|

L |

|

driving & |

active |

active |

normal driving |

|

|

|

|

receiving |

|

|

(differential receiver active) |

L |

|

H |

|

receiving[1] |

active |

active |

receiving |

H |

|

L |

|

driving |

inactive[2] |

active |

driving during ‘suspend’[3] |

|

|

|

|

|

|

|

(differential receiver inactive) |

H |

|

H |

|

high-Z[1] |

inactive[2] |

active |

low-power state |

[1]Signal levels on (D+, D−) are determined by other USB devices and external pull-up/down resistors.

[2]In ‘suspend’ mode (SUSPND = HIGH) the differential receiver is inactive and output RCV is always LOW. Out-of-suspend (‘K’) signalling is detected via the single-ended receivers VP and VM.

[3]During suspend, the slew-rate control circuit of low-speed operation is disabled. The (D+, D−) lines are still driven to their intended states, without slew-rate control. This is permitted because driving during suspend is used to signal remote wake-up by driving a ‘K’ signal (one transition from idle to ‘K’ state) for a period of 1 to 15 ms.

9397 750 08872 |

© Koninklijke Philips Electronics N.V. 2001. All rights reserved. |

Product data |

Rev. 06 — 30 November 2001 |

6 of 24 |

Philips Semiconductors |

|

|

|

|

ISP1105/1106/1107 |

||||||

|

|

|

|

|

|

|

Advanced USB transceivers |

||||

7.2 Operating functions |

|

|

|

|

|

|

|||||

|

Table 5: |

Driving function using single-ended input data interface |

|

|

= L) [for |

||||||

(OE |

|||||||||||

|

|

ISP1107 and ISP1105 (MODE = L)] |

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

FSE0 |

VO |

|

|

Data |

|

|||||

|

L |

L |

|

|

differential logic 0 |

|

|||||

|

L |

H |

|

|

differential logic 1 |

|

|||||

|

H |

L |

|

|

SE0 |

|

|||||

|

H |

H |

|

|

SE0 |

|

|||||

|

|

|

|

|

|

||||||

|

Table 6: |

Driving function using differential input data interface |

|

|

= L) [for ISP1106 |

||||||

|

(OE |

||||||||||

|

|

and ISP1105 (MODE = H)] |

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|||

|

VMO |

VPO |

|

|

Data |

|

|||||

|

L |

L |

|

|

SE0 |

|

|||||

|

L |

H |

|

|

differential logic 1 |

|

|||||

|

H |

L |

|

|

differential logic 0 |

|

|||||

|

H |

H |

|

|

illegal state |

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

Table 7: |

Receiving function |

|

= H) |

|

|

|

|

|

|

|

|

(OE |

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|||||

|

|

(D+, D−) |

|

RCV |

VP[1] |

VM[1] |

|||||

|

differential logic 0 |

|

L |

L |

H |

||||||

|

differential logic 1 |

|

H |

H |

L |

||||||

|

|

SE0 |

|

RCV*[2] |

L |

L |

|||||

[1]VP = VM = H indicates the sharing mode (VCC(5.0)/Vreg(3.3) is disconnected).

[2]RCV* denotes the signal level on output RCV just before SE0 state occurs. This level is stable during the SE0 period.

7.3Power supply configurations

The ISP1105/1106/1107 can be used with different power supply configurations, which can be changed dynamically. An overview is given in Table 9.

Normal mode — Both VCC(I/O) and VCC(5.0) or (VCC(5.0) and Vreg(3.3)) are connected. For 5 V operation, VCC(5.0) is connected to a 5 V source (4.0 to 5.5 V). The internal voltage regulator then produces 3.3 V for the USB connections. For 3.3 V operation,

both VCC(5.0) and Vreg(3.3) are connected to a 3.3 V source (3.0 to 3.6 V). VCC(I/O) is independently connected to a voltage source (1.65 V to 3.6 V), depending on the

supply voltage of the external circuit.

Disable mode — VCC(I/O) is not connected, VCC(5.0) or (VCC(5.0) and Vreg(3.3)) are connected. In this mode, the internal circuits of the ISP1105/1106/1107 ensure that

the (D+, D−) pins are in three-state and the power consumption drops to the low-power (suspended) state level. Some hysteresis is built into the detection of

VCC(I/O) lost.

Sharing mode — VCC(I/O) is connected, (VCC(5.0) and Vreg(3.3)) are not connected. In this mode, the (D+, D−) pins are made three-state and the ISP1105/1106/1107 allows

external signals of up to 3.6 V to share the (D+, D−) lines. The internal circuits of the ISP1105/1106/1107 ensure that virtually no current (maximum 10 μA) is drawn via the (D+, D−) lines. The power consumption through pin VCC(I/O) drops to the

9397 750 08872 |

© Koninklijke Philips Electronics N.V. 2001. All rights reserved. |

Product data |

Rev. 06 — 30 November 2001 |

7 of 24 |

Philips Semiconductors |

ISP1105/1106/1107 |

|

Advanced USB transceivers |

low-power (suspended) state level. Both the VP and VM pins are driven HIGH to indicate this mode. Pin RCV is made LOW. Some hysteresis is built into the detection of Vreg(3.3) lost.

Table 8: Pin states in Disable or Sharing mode

Pins |

Disable mode state |

Sharing mode state |

||

VCC(5.0)/Vreg(3.3) |

5 V input / 3.3 V output |

not present |

||

|

|

|

3.3 V input / 3.3 V input |

|

VCC(I/O) |

not present |

1.65 V to 3.6 V input |

||

Vpu(3.3) |

high impedance (off) |

high impedance (off) |

||

(D+, D−) |

high impedance |

high impedance |

||

(VP, VM) |

invalid[1] |

H |

||

RCV |

invalid[1] |

L |

||

Inputs (VO/VPO, FSE0/VMO, |

high impedance |

high impedance |

||

SPEED, MODE[2], SUSPND, |

|

|

|

|

OE, |

|

|

||

SOFTCON) |

|

|

||

|

|

|

|

|

[1]High impedance or driven LOW.

[2]ISP1105 only.

Table 9: Power supply configuration overview

VCC(5.0) or |

VCC(I/O) |

Configuration |

Special characteristics |

Vreg(3.3) |

|

|

|

connected |

connected |

Normal mode |

- |

|

|

|

|

connected |

not connected |

Disable mode |

(D+, D−) and Vpu(3.3) high |

|

|

|

impedance; VP, VM, RCV: |

|

|

|

invalid[1] |

not connected |

connected |

Sharing mode |

(D+, D−) and Vpu(3.3) high |

|

|

|

impedance; |

|

|

|

VP, VM driven HIGH; |

|

|

|

RCV driven LOW |

|

|

|

|

[1]High impedance or driven LOW.

7.4Power supply input options

The ISP1105/1106/1107 range has two power supply input options:

Internal regulator — VCC(5.0) is connected to 4.0 to 5.5 V. The internal regulator is used to supply the internal circuitry with 3.3 V (nominal). The Vreg(3.3) pin becomes a 3.3 V output reference.

Regulator bypass — VCC(5.0) and Vreg(3.3) are connected to the same supply. The internal regulator is bypassed and the internal circuitry is supplied directly from the

Vreg(3.3) power supply. The voltage range is 3.0 to 3.6 V to comply with the USB specification.

The supply voltage range for each input option is specified in Table 10.

9397 750 08872 |

© Koninklijke Philips Electronics N.V. 2001. All rights reserved. |

Product data |

Rev. 06 — 30 November 2001 |

8 of 24 |

Loading...

Loading...