MOTOROLA SN74LS195ADR2, SN74LS195AN Datasheet

Semiconductor Components Industries, LLC, 1999

December, 1999 – Rev. 6

1 Publication Order Number:

SN74LS195A/D

SN74LS195A

Universal 4-Bit

Shift Register

The SN74LS195A is a high speed 4-Bit Shift Register offering

typical shift frequencies of 39 MHz. It is useful for a wide variety of

register and counting applications. It utilizes the Schottky diode

clamped process to achieve high speeds and is fully compatible with

all ON Semiconductor TTL products.

• Typical Shift Right Frequency of 39 MHz

• Asynchronous Master Reset

• J, K Inputs to First Stage

• Fully Synchronous Serial or Parallel Data Transfers

• Input Clamp Diodes Limit High Speed Termination Effects

GUARANTEED OPERATING RANGES

Symbol Parameter Min Typ Max Unit

V

CC

Supply Voltage 4.75 5.0 5.25 V

T

A

Operating Ambient

T emperature Range

0 25 70 °C

I

OH

Output Current – High –0.4 mA

I

OL

Output Current – Low 8.0 mA

LOW

POWER

SCHOTTKY

Device Package Shipping

ORDERING INFORMATION

SN74LS195AN 16 Pin DIP 2000 Units/Box

SN74LS195AD 16 Pin

SOIC

D SUFFIX

CASE 751B

http://onsemi.com

2500/Tape & Reel

PLASTIC

N SUFFIX

CASE 648

16

1

16

1

SN74LS195A

http://onsemi.com

2

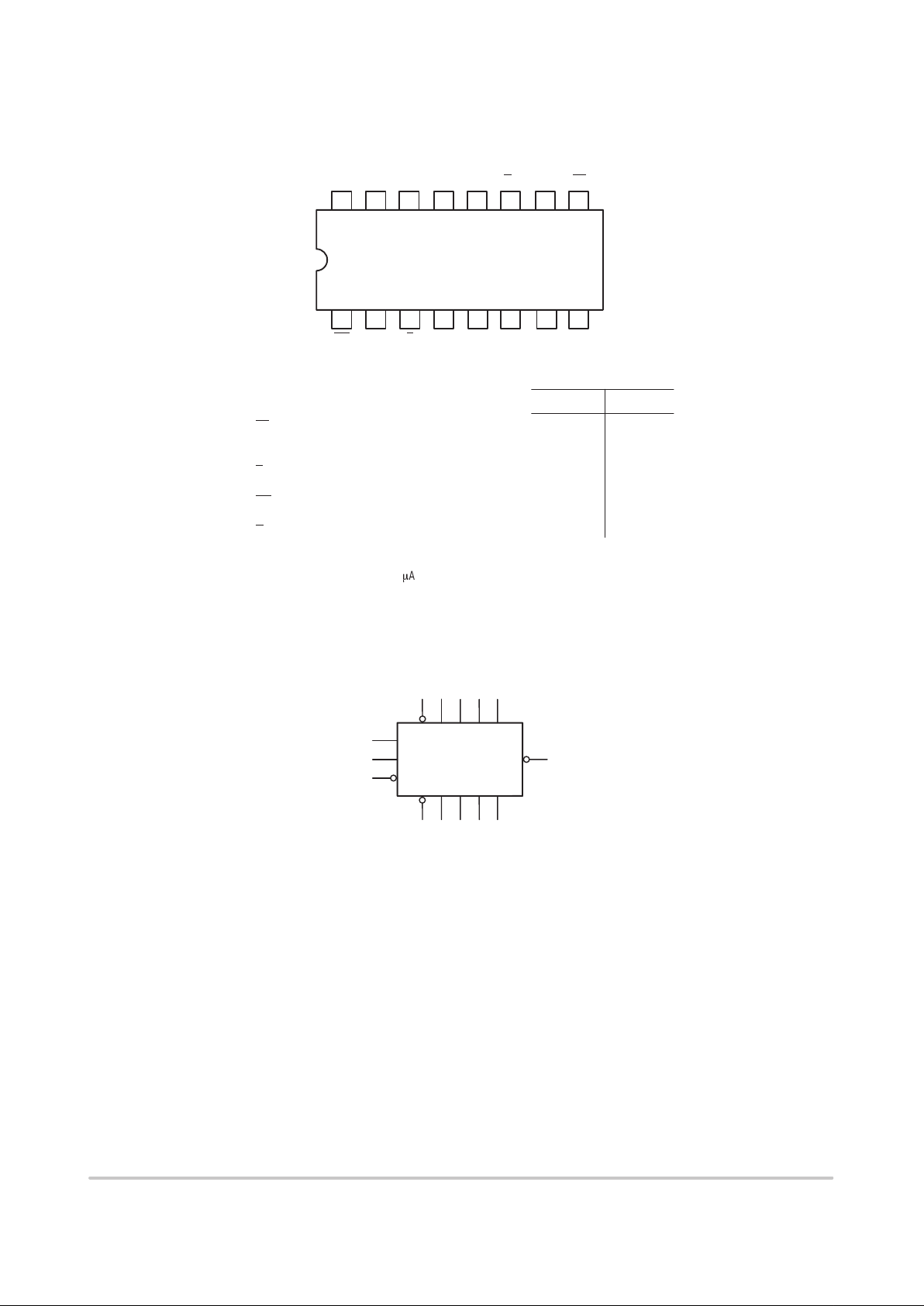

CONNECTION DIAGRAM DIP (TOP VIEW)

Parallel Enable (Active LOW) Input

Parallel Data Inputs

First Stage J (Active HIGH) Input

First Stage K (Active LOW) Input

Clock (Active HIGH Going Edge) Input

Master Reset (Active LOW) Input

Parallel Outputs

Complementary Last Stage Output

PE

P0 – P

3

J

K

CP

MR

Q0 – Q

3

Q

3

0.5 U.L.

0.5 U.L.

0.5 U.L.

0.5 U.L.

0.5 U.L.

0.5 U.L.

10 U.L.

10 U.L.

0.25 U.L.

0.25 U.L.

0.25 U.L.

0.25 U.L.

0.25 U.L.

0.25 U.L.

5 U.L.

5 U.L.

NOTES:

a) 1 TTL Unit Load (U.L.) = 40 mA HIGH/1.6 mA LOW.

HIGH LOW

(Note a)LOADING

PIN NAMES

LOGIC SYMBOL

2

10

3

4567

11

121314151

9

J

PE

CP

K

MR

P0P1P2P

3

Q0Q1Q2Q

3

Q

3

VCC = PIN 16

GND = PIN 8

NOTE:

The Flatpak version has the same

pinouts (Connection Diagram) as

the Dual In-Line Package.

14 13 12 11 10 9

123456

7

16 15

8

V

CC

MR

Q0Q1Q2Q

3

CPQ

3

PE

JKP0P1P2P3GND

SN74LS195A

http://onsemi.com

3

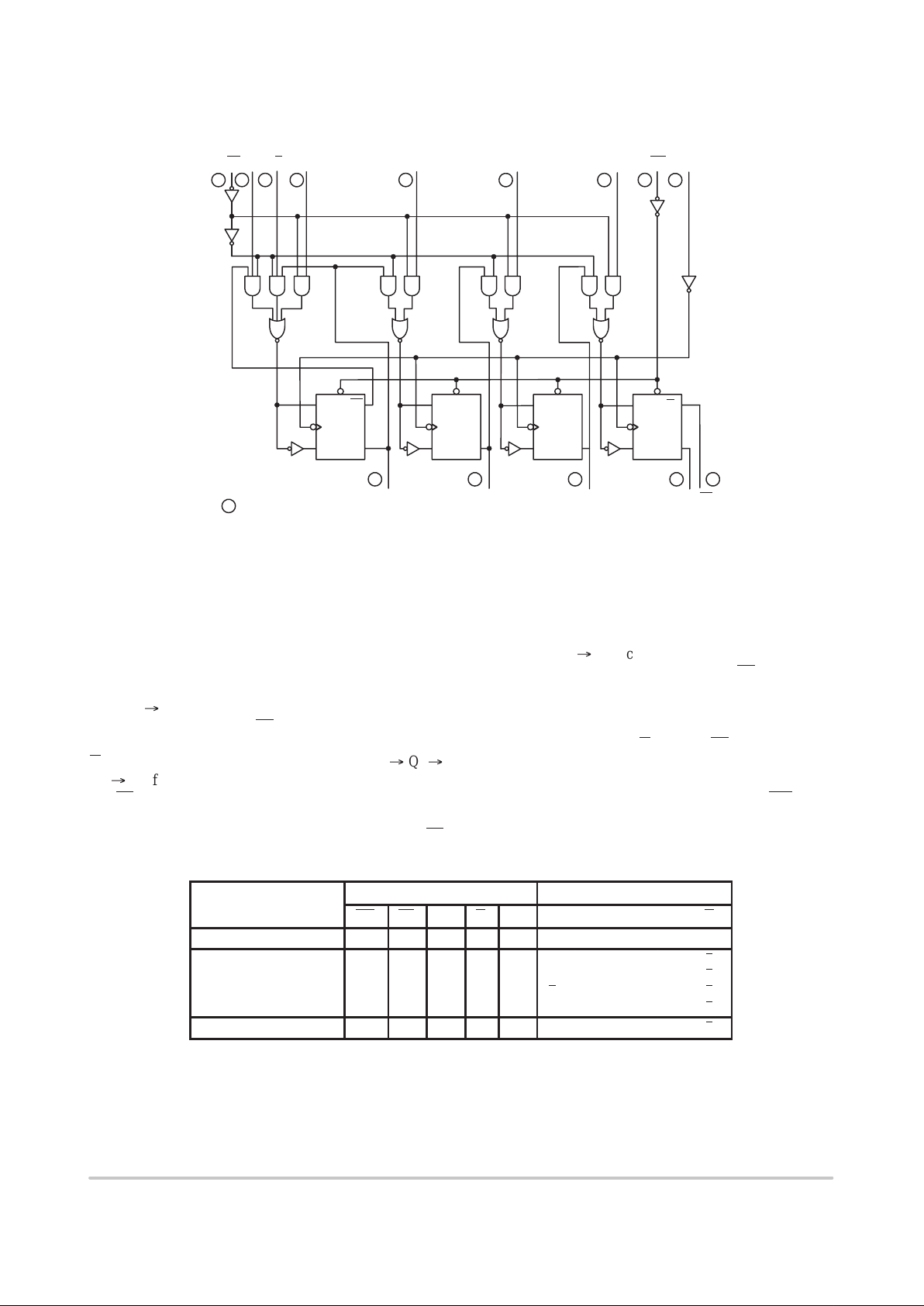

LOGIC DIAGRAM

JP

0

P

1

P

2

P

3

CPPE K MR

Q

0

Q

0

Q

1

Q

3

R

CP

S

C

D

Q

0

Q

2

Q

3

14

12673 4 59

1112

10

1315

VCC = PIN 16

GND = PIN 8

= PIN NUMBERS

R

CP

S

C

D

Q

0

R

CP

S

C

D

Q

2

Q

3

R

CP

S

C

D

Q

3

FUNCTIONAL DESCRIPTION

The Logic Diagram and Truth Table indicate the

functional characteristics of the LS195A 4-Bit Shift

Register. The device is useful in a wide variety of shifting,

counting and storage applications. It performs serial,

parallel, serial to parallel, or parallel to serial data transfers

at very high speeds.

The LS195A has two primary modes of operation, shift

right (Q

0

³ Q1) and parallel load which are controlled by the

state of the Parallel Enable (PE

) input. When the PE input is

HIGH, serial data enters the first flip-flop Q0 via the J and

K inputs and is shifted one bit in the direction Q

0

³

Q

1

³

Q2 ³Q3 following each LOW to HIGH clock transition.

The JK inputs provide the flexibility of the JK type input for

special applications, and the simple D type input for general

applications by tying the two pins together. When the PE

input is LOW , the LS195A appears as four common clocked

D flip-flops. The data on the parallel inputs P0, P1, P2, P3 is

transferred to the respective Q0, Q1, Q2, Q3 outputs

following the LOW to HIGH clock transition. Shift left

operations (Q

3

³Q2) can be achieved by tying the Q

n

Outputs to the P

n–1

inputs and holding the PE input LOW.

All serial and parallel data transfers are synchronous,

occurring after each LOW to HIGH clock transition. Since

the LS195A utilizes edge-triggering, there is no restriction

on the activity of the J, K

, Pn and PE inputs for logic

operation — except for the set-up and release time

requirements.

A LOW on the asynchronous Master Reset (MR) input

sets all Q outputs LOW, independent of any other input

condition.

MODE SELECT — TRUTH TABLE

INPUTS OUTPUTS

OPERATING MODES

MR PE J K PnQ0Q

1

Q2Q3Q

3

Asynchronous Reset L X X X X L L L L H

Shift, Set First Stage H h h h X H q

0

q

1

q2q

2

Shift, Reset First H h I I X L q

0

q

1

q2q

2

Shift, Toggle First Stage H h h I X q

0

q

0

q

1

q2q

2

Shift, Retain First Stage H h I h X q

0

q

0

q

1

q2q

2

Parallel Load H I X X p

n

p

0

p

1

p

2

p3p

3

L = LOW voltage levels

H = HIGH voltage levels

X = Don’t Care

I = LOW voltage level one set-up time prior to the LOW to HIGH clock transition.

h = HIGH voltage level one set-up time prior to the LOW to HIGH clock transition.

p

n

(qn) = Lower case letters indicate the state of the referenced input (or output) one set-up time prior to the LOW to

HIGH clock transition.

Loading...

Loading...