MOTOROLA MC74VHC4066DT, MC74VHC4066D, MC74VHC4066DR2, MC74VHC4066DTR2 Datasheet

SEMICONDUCTOR TECHNICAL DATA

Order this document

by MC74VHC4066/D

1

REV 3

Motorola, Inc. 1999

07/99

! "

! #! #

High–Performance Silicon–Gate CMOS

The MC74VHC4066 utilizes silicon–gate CMOS technology to

achieve fast propagation delays, low ON resistances, and low OFF–

channel leakage current. This bilateral switch/multiplexer/demultiplexer

controls analog and digital voltages that may vary across the full

power–supply range (from VCC to GND).

The VHC4066 is identical in pinout to the metal–gate CMOS MC14066

and the high–speed CMOS HC4066A. Each device has four independent

switches. The device has been designed so that the ON resistances

(RON) are much more linear over input voltage than RON of metal–gate

CMOS analog switches.

The ON/OFF control inputs are compatible with standard CMOS

outputs; with pullup resistors, they are compatible with LSTTL outputs.

For analog switches with voltage–level translators, see the VHC4316.

• Fast Switching and Propagation Speeds

• High ON/OFF Output Voltage Ratio

• Low Crosstalk Between Switches

• Diode Protection on All Inputs/Outputs

• Wide Power–Supply Voltage Range (VCC – GND) = 2.0 to 12.0 Volts

• Analog Input Voltage Range (VCC – GND) = 2.0 to 12.0 Volts

• Improved Linearity and Lower ON Resistance over Input Voltage than

the MC14016 or MC14066

• Low Noise

• Chip Complexity: 44 FETs or 11 Equivalent Gates

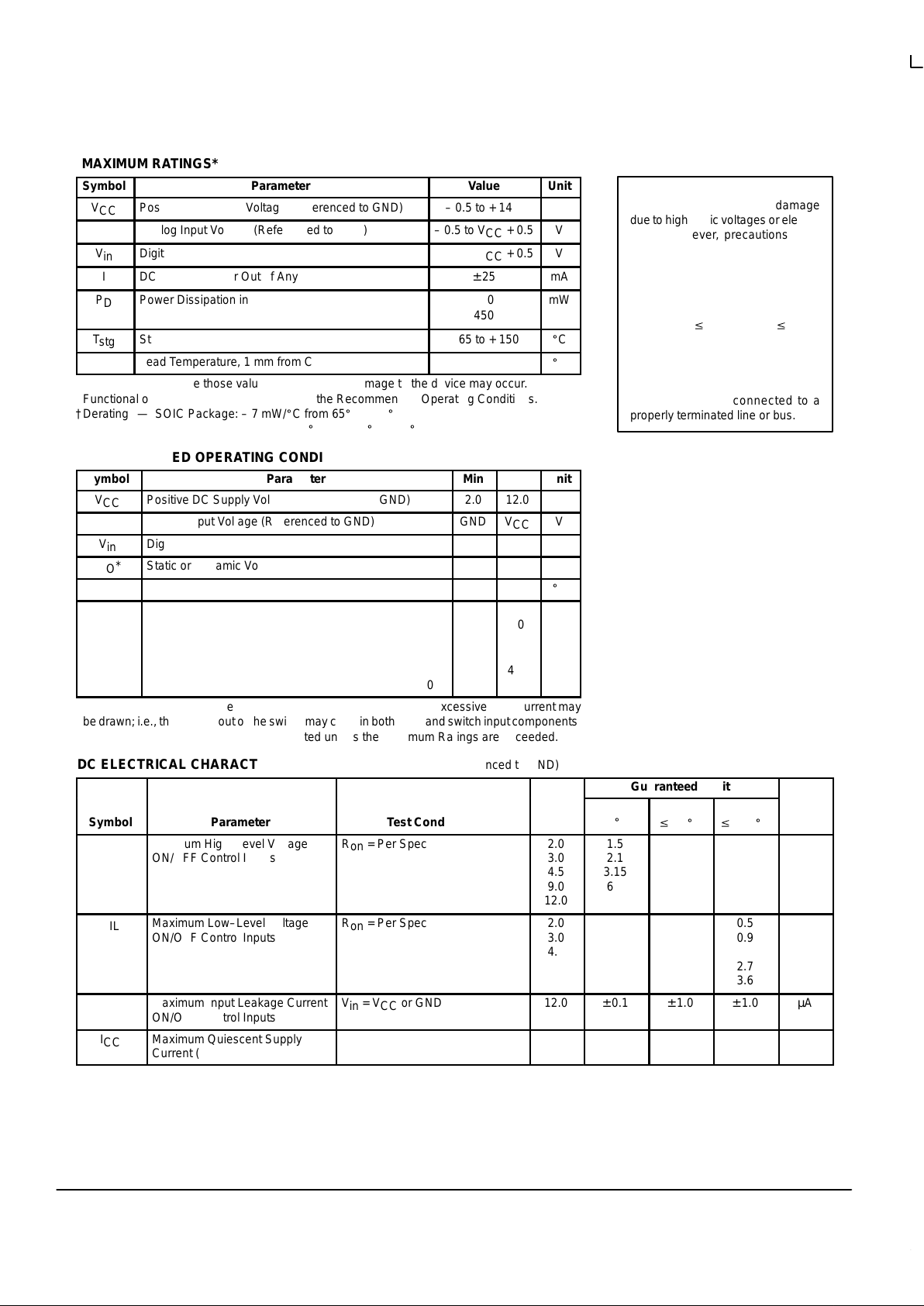

LOGIC DIAGRAM

X

A

Y

A

12

A ON/OFF CONTROL

13

X

B

Y

B

43

B ON/OFF CONTROL

5

X

C

Y

C

89

C ON/OFF CONTROL

6

X

D

Y

D

11 10

D ON/OFF CONTROL

12

ANALOG

OUTPUTS/INPUTS

ANALOG INPUTS/OUTPUTS = XA, XB, XC, X

D

PIN 14 = V

CC

PIN 7 = GND

This document contains information on a new product. Specifications and information herein are subject to

change without notice.

FUNCTION TABLE

PIN ASSIGNMENT

11

12

13

14

8

9

105

4

3

2

1

7

6

Y

D

X

D

D ON/OFF

CONTROL

A ON/OFF

CONTROL

V

CC

X

C

Y

C

X

B

Y

B

Y

A

X

A

GND

C ON/OFF

CONTROL

B ON/OFF

CONTROL

On/Off Control State of

Input Analog Switch

LOff

HOn

ORDERING INFORMATION

MC74VHCXXXXD

MC74VHCXXXXDT

SOIC

TSSOP

D SUFFIX

14–LEAD SOIC PACKAGE

CASE 751A–03

DT SUFFIX

14–LEAD TSSOP PACKAGE

CASE 948G–01

MC74VHC4066

MOTOROLA VHC Data – Advanced CMOS Logic

DL203 — Rev 2

2

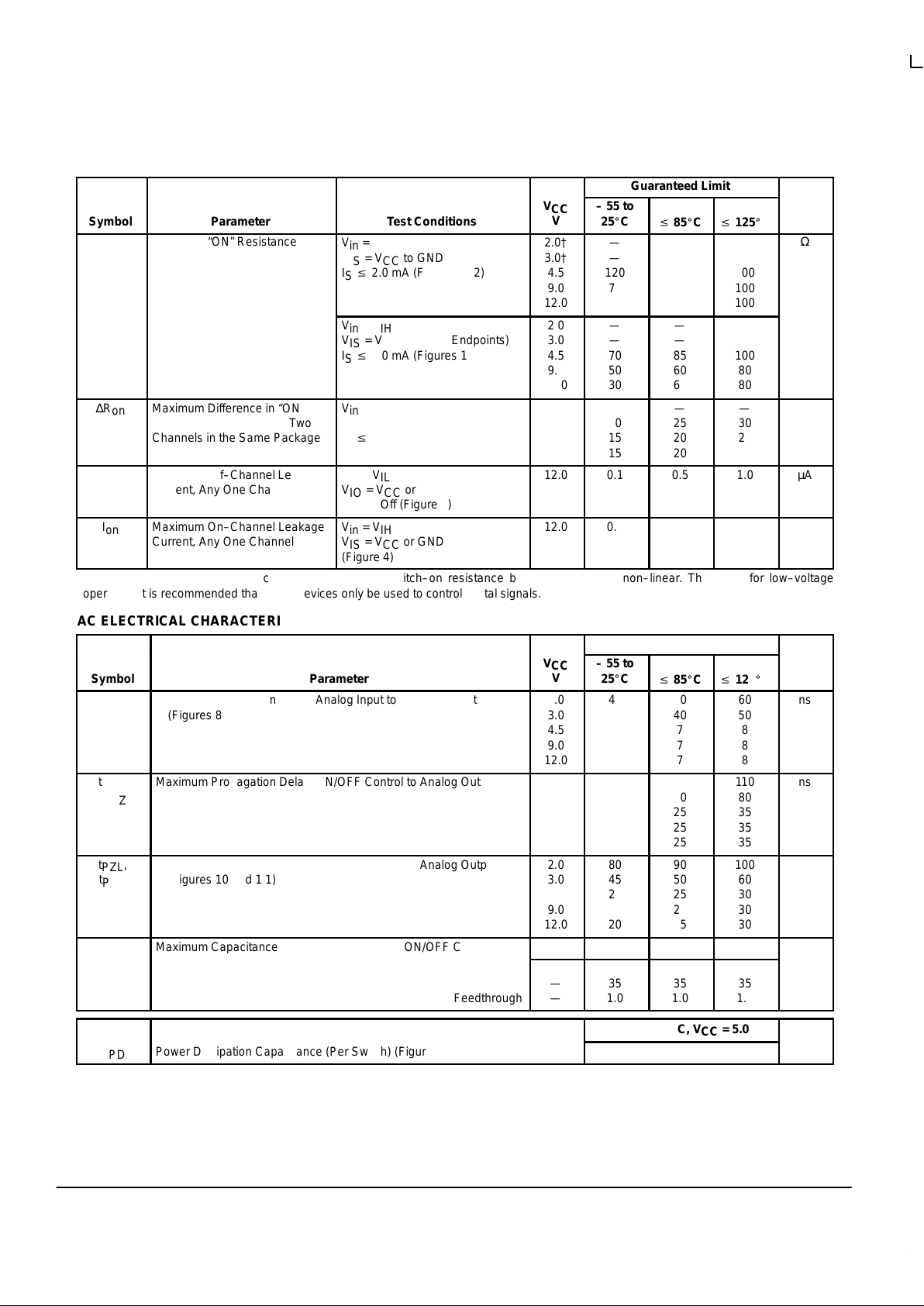

MAXIMUM RATINGS*

Symbol

Parameter

Value

Unit

V

CC

Positive DC Supply Voltage (Referenced to GND)

– 0.5 to + 14.0

V

V

IS

Analog Input Voltage (Referenced to GND)

– 0.5 to VCC + 0.5

V

V

in

Digital Input Voltage (Referenced to GND)

– 0.5 to VCC + 0.5

V

I

DC Current Into or Out of Any Pin

± 25

mA

Î

Î

P

D

ОООООООООООО

Î

Power Dissipation in Still Air, SOIC Package†

TSSOP Package†

ÎÎÎÎ

Î

500

450

Î

Î

mW

T

stg

Storage Temperature

– 65 to + 150

_

C

T

L

Lead Temperature, 1 mm from Case for 10 Seconds

260

_

C

*Maximum Ratings are those values beyond which damage to the device may occur.

Functional operation should be restricted to the Recommended Operating Conditions.

†Derating — SOIC Package: – 7 mW/_C from 65_ to 125_C

TSSOP Package: – 6.1 mW/_C from 65_ to 125_C

RECOMMENDED OPERATING CONDITIONS

Symbol

Parameter

Min

Max

Unit

V

CC

Positive DC Supply Voltage (Referenced to GND)

2.0

12.0

V

V

IS

Analog Input Voltage (Referenced to GND)

GND

V

CC

V

V

in

Digital Input Voltage (Referenced to GND)

GND

V

CC

V

ÎÎ

Î

VIO*

ОООООООООООО

Î

Static or Dynamic Voltage Across Switch

Î

Î

—

Î

Î

1.2

Î

Î

V

ÎÎ

T

A

ОООООООООООО

Operating Temperature, All Package Types

Î

– 55Î+ 125

Î

_

C

ÎÎ

Î

ÎÎ

Î

ÎÎ

Î

ÎÎ

Î

tr, t

f

ОООООООООООО

Î

ОООООООООООО

Î

ОООООООООООО

Î

ОООООООООООО

Î

Input Rise and Fall Time, ON/OFF Control

Inputs (Figure 10) VCC = 2.0 V

VCC = 3.0 V

VCC = 4.5 V

VCC = 9.0 V

VCC = 12.0 V

Î

Î

Î

Î

Î

Î

Î

Î

0

0

0

0

0

Î

Î

Î

Î

Î

Î

Î

Î

1000

600

500

400

250

Î

Î

Î

Î

Î

Î

Î

Î

ns

*For voltage drops across the switch greater than 1.2 V (switch on), excessive VCC current may

be drawn; i.e., the current out of the switch may contain both VCC and switch input components.

The reliability of the device will be unaffected unless the Maximum Ratings are exceeded.

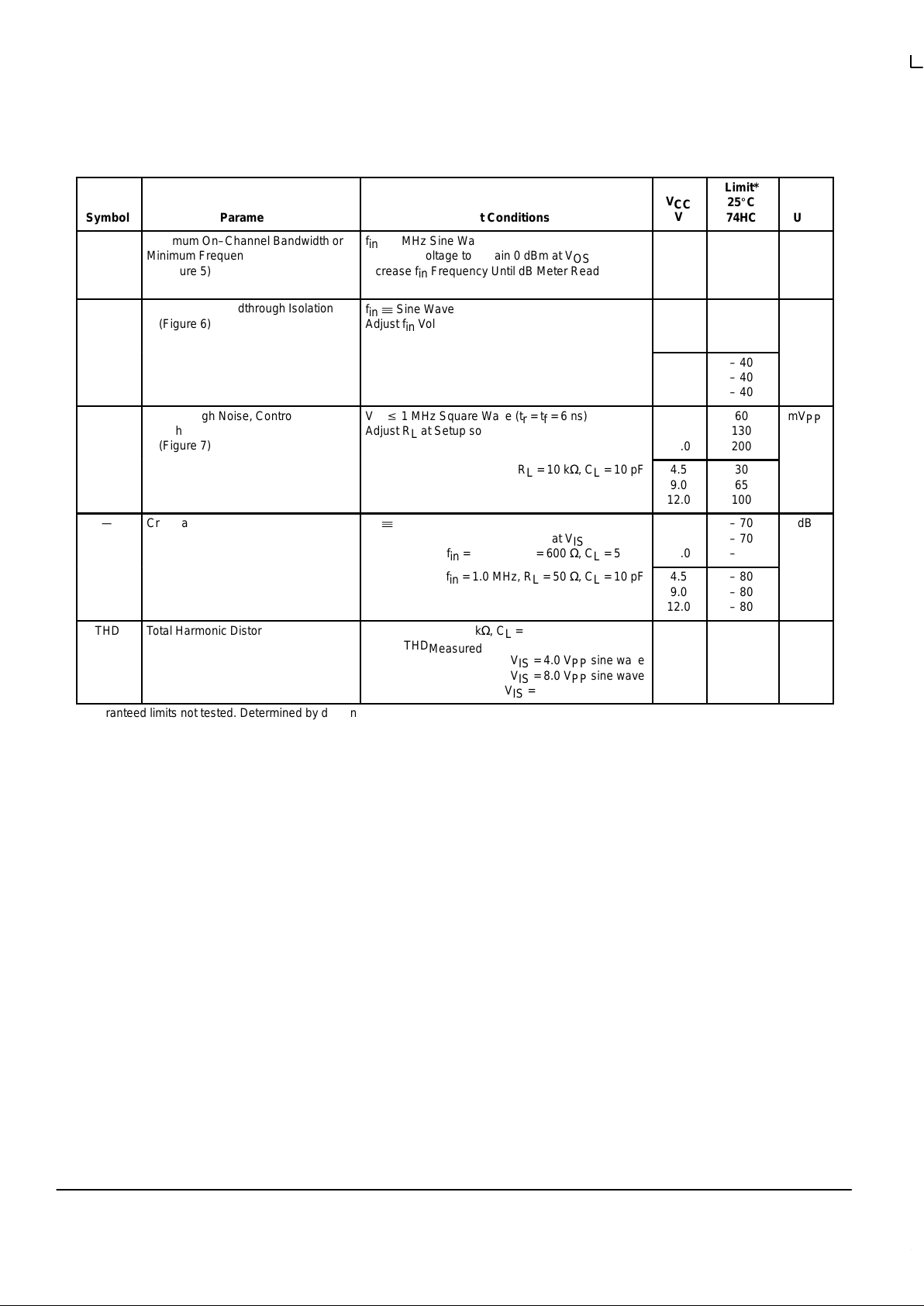

DC ELECTRICAL CHARACTERISTIC Digital Section (Voltages Referenced to GND)

Guaranteed Limit

ÎÎ

Î

Symbol

ООООООО

Î

Parameter

ООООООО

Î

Test Conditions

ÎÎ

Î

V

CC

V

ÎÎ

– 55 to

25_C

ÎÎ

Î

v

85_C

ÎÎ

Î

v

125_C

Î

Î

Unit

ÎÎ

Î

ÎÎ

Î

ÎÎ

Î

V

IH

ООООООО

Î

ООООООО

Î

ООООООО

Î

Minimum High–Level Voltage

ON/OFF Control Inputs

ООООООО

Î

ООООООО

Î

ООООООО

Î

Ron = Per Spec

ÎÎ

Î

ÎÎ

Î

ÎÎ

Î

2.0

3.0

4.5

9.0

12.0

ÎÎ

ÎÎ

ÎÎ

1.5

2.1

3.15

6.3

8.4

ÎÎ

Î

ÎÎ

Î

ÎÎ

Î

1.5

2.1

3.15

6.3

8.4

ÎÎ

Î

ÎÎ

Î

ÎÎ

Î

1.5

2.1

3.15

6.3

8.4

Î

Î

Î

Î

Î

Î

V

ÎÎ

Î

ÎÎ

Î

V

IL

ООООООО

Î

ООООООО

Î

Maximum Low–Level Voltage

ON/OFF Control Inputs

ООООООО

Î

ООООООО

Î

Ron = Per Spec

ÎÎ

Î

ÎÎ

Î

2.0

3.0

4.5

9.0

12.0

ÎÎ

ÎÎ

0.5

0.9

1.35

2.7

3.6

ÎÎ

Î

ÎÎ

Î

0.5

0.9

1.35

2.7

3.6

ÎÎ

Î

ÎÎ

Î

0.5

0.9

1.35

2.7

3.6

Î

Î

Î

Î

V

ÎÎ

Î

I

in

ООООООО

Î

Maximum Input Leakage Current

ON/OFF Control Inputs

ООООООО

Î

Vin = VCC or GND

ÎÎ

Î

12.0

ÎÎ

± 0.1

ÎÎ

Î

± 1.0

ÎÎ

Î

± 1.0

Î

Î

µA

ÎÎ

Î

I

CC

ООООООО

Î

Maximum Quiescent Supply

Current (per Package)

ООООООО

Î

Vin = VCC or GND

VIO = 0 V

ÎÎ

Î

6.0

12.0

ÎÎ

2

4

ÎÎ

Î

20

40

ÎÎ

Î

40

160

Î

Î

µA

This device contains protection

circuitry to guard against damage

due to high static voltages or electric

fields. However, precautions must

be taken to avoid applications of any

voltage higher than maximum rated

voltages to this high–impedance circuit. For proper operation, Vin and

V

out

should be constrained to the

range GND v (Vin or V

out

) v VCC.

Unused inputs must always be

tied to an appropriate logic voltage

level (e.g., either GND or VCC).

Unused outputs must be left open.

I/O pins must be connected to a

properly terminated line or bus.

MC74VHC4066

VHC Data – Advanced CMOS Logic

DL203 — Rev 2

3 MOTOROLA

DC ELECTRICAL CHARACTERISTICS Analog Section (Voltages Referenced to GND)

Guaranteed Limit

ÎÎ

Î

Symbol

ООООООО

Î

Parameter

ООООООО

Î

Test Conditions

ÎÎ

Î

V

CC

V

ÎÎ

– 55 to

25_C

ÎÎ

Î

v

85_C

ÎÎ

Î

v

125_C

Î

Î

Unit

ÎÎ

Î

ÎÎ

Î

R

on

ООООООО

Î

ООООООО

Î

Maximum “ON” Resistance

ООООООО

Î

ООООООО

Î

Vin = V

IH

VIS = VCC to GND

IS v 2.0 mA (Figures 1, 2)

ÎÎ

Î

ÎÎ

Î

2.0†

3.0†

4.5

9.0

12.0

ÎÎ

ÎÎ

—

—

120

70

70

ÎÎ

Î

ÎÎ

Î

—

—

160

85

85

ÎÎ

Î

ÎÎ

Î

—

—

200

100

100

Î

Î

Î

Î

Ω

ÎÎ

Î

ÎÎ

Î

ÎÎ

Î

ООООООО

Î

ООООООО

Î

ООООООО

Î

ООООООО

Î

ООООООО

Î

ООООООО

Î

Vin = V

IH

VIS = VCC or GND (Endpoints)

IS v 2.0 mA (Figures 1, 2)

ÎÎ

Î

ÎÎ

Î

ÎÎ

Î

2.0

3.0

4.5

9.0

12.0

ÎÎ

ÎÎ

ÎÎ

—

—

70

50

30

ÎÎ

Î

ÎÎ

Î

ÎÎ

Î

—

—

85

60

60

ÎÎ

Î

ÎÎ

Î

ÎÎ

Î

—

—

100

80

80

Î

Î

Î

Î

Î

Î

ÎÎ

Î

ÎÎ

Î

∆R

on

ООООООО

Î

ООООООО

Î

Maximum Difference in “ON”

Resistance Between Any Two

Channels in the Same Package

ООООООО

Î

ООООООО

Î

Vin = V

IH

VIS = 1/2 (VCC – GND)

IS v 2.0 mA

ÎÎ

Î

ÎÎ

Î

2.0

4.5

9.0

12.0

ÎÎ

ÎÎ

—

20

15

15

ÎÎ

Î

ÎÎ

Î

—

25

20

20

ÎÎ

Î

ÎÎ

Î

—

30

25

25

Î

Î

Î

Î

Ω

ÎÎ

Î

I

off

ООООООО

Î

Maximum Off–Channel Leakage

Current, Any One Channel

ООООООО

Î

Vin = V

IL

VIO = VCC or GND

Switch Off (Figure 3)

ÎÎ

Î

12.0

ÎÎ

0.1

ÎÎ

Î

0.5

ÎÎ

Î

1.0

Î

Î

µA

ÎÎ

Î

I

on

ООООООО

Î

Maximum On–Channel Leakage

Current, Any One Channel

ООООООО

Î

Vin = V

IH

VIS = VCC or GND

(Figure 4)

ÎÎ

Î

12.0

ÎÎ

0.1

ÎÎ

Î

0.5

ÎÎ

Î

1.0

Î

Î

µA

†At supply voltage (VCC) approaching 3 V the analog switch–on resistance becomes extremely non–linear. Therefore, for low–voltage

operation, it is recommended that these devices only be used to control digital signals.

AC ELECTRICAL CHARACTERISTICS (C

L

= 50 pF, ON/OFF Control Inputs: tr = tf = 6 ns)

Guaranteed Limit

Symbol

Parameter

V

CC

V

– 55 to

25_C

v

85_Cv 125_C

Unit

ÎÎ

Î

ÎÎ

Î

ÎÎ

Î

t

PLH

,

t

PHL

ООООООООООООООО

Î

ООООООООООООООО

Î

ООООООООООООООО

Î

Maximum Propagation Delay , Analog Input to Analog Output

(Figures 8 and 9)

ÎÎ

Î

ÎÎ

Î

ÎÎ

Î

2.0

3.0

4.5

9.0

12.0

ÎÎ

ÎÎ

ÎÎ

40

30

5

5

5

ÎÎ

Î

ÎÎ

Î

ÎÎ

Î

50

40

7

7

7

ÎÎ

Î

ÎÎ

Î

ÎÎ

Î

60

50

8

8

8

Î

Î

Î

Î

Î

Î

ns

ÎÎ

Î

ÎÎ

Î

ÎÎ

t

PLZ

,

t

PHZ

ООООООООООООООО

Î

ООООООООООООООО

Î

ООООООООООООООО

Maximum Propagation Delay, ON/OFF Control to Analog Output

(Figures 10 and 11)

ÎÎ

Î

ÎÎ

Î

ÎÎ

2.0

3.0

4.5

9.0

12.0

ÎÎ

ÎÎ

ÎÎ

80

60

20

20

20

ÎÎ

Î

ÎÎ

Î

ÎÎ

90

70

25

25

25

ÎÎ

Î

ÎÎ

Î

ÎÎ

110

80

35

35

35

Î

Î

Î

Î

Î

ns

ÎÎ

Î

ÎÎ

Î

ÎÎ

Î

t

PZL

,

t

PZH

ООООООООООООООО

Î

ООООООООООООООО

Î

ООООООООООООООО

Î

Maximum Propagation Delay, ON/OFF Control to Analog Output

(Figures 10 and 1 1)

ÎÎ

Î

ÎÎ

Î

ÎÎ

Î

2.0

3.0

4.5

9.0

12.0

ÎÎ

ÎÎ

ÎÎ

80

45

20

20

20

ÎÎ

Î

ÎÎ

Î

ÎÎ

Î

90

50

25

25

25

ÎÎ

Î

ÎÎ

Î

ÎÎ

Î

100

60

30

30

30

Î

Î

Î

Î

Î

Î

ns

C

Maximum Capacitance ON/OFF Control Input

—

10

10

10

pF

ÎÎÎООООООООООООООО

Î

Control Input = GND

Analog I/O

Feedthrough

ÎÎ

Î

—

—

ÎÎ

35

1.0

ÎÎ

Î

35

1.0

ÎÎ

Î

35

1.0

Î

Î

Typical @ 25°C, VCC = 5.0 V

C

PD

Power Dissipation Capacitance (Per Switch) (Figure 13)*

15

pF

*Used to determine the no–load dynamic power consumption: PD = CPD V

CC

2

f + ICC VCC.

MC74VHC4066

MOTOROLA VHC Data – Advanced CMOS Logic

DL203 — Rev 2

4

ADDITIONAL APPLICATION CHARACTERISTICS (Voltages Referenced to GND Unless Noted)

ÎÎ

Î

ÎÎ

Symbol

ОООООООО

Î

ОООООООО

Parameter

ОООООООООООО

Î

ОООООООООООО

Test Conditions

Î

Î

Î

V

CC

V

ÎÎ

Î

ÎÎ

Limit*

25_C

74HC

Î

Î

Î

Unit

ÎÎ

Î

ÎÎ

Î

BW

ОООООООО

Î

ОООООООО

Î

Maximum On–Channel Bandwidth or

Minimum Frequency Response

(Figure 5)

ОООООООООООО

Î

ОООООООООООО

Î

fin = 1 MHz Sine Wave

Adjust fin Voltage to Obtain 0 dBm at V

OS

Increase fin Frequency Until dB Meter Reads – 3 dB

RL = 50 Ω, CL = 10 pF

Î

Î

Î

Î

4.5

9.0

12.0

ÎÎ

Î

ÎÎ

Î

150

160

160

Î

Î

Î

Î

MHz

ÎÎ

Î

ÎÎ

Î

—

ОООООООО

Î

ОООООООО

Î

Off–Channel Feedthrough Isolation

(Figure 6)

ОООООООООООО

Î

ОООООООООООО

Î

fin Sine Wave

Adjust fin Voltage to Obtain 0 dBm at V

IS

fin = 10 kHz, RL = 600 Ω, CL = 50 pF

Î

Î

Î

Î

4.5

9.0

12.0

ÎÎ

Î

ÎÎ

Î

– 50

– 50

– 50

Î

Î

Î

Î

dB

ÎÎÎООООООООÎОООООООООООО

Î

fin = 1.0 MHz, RL = 50 Ω, CL = 10 pF

Î

Î

4.5

9.0

12.0

ÎÎ

Î

– 40

– 40

– 40

Î

Î

ÎÎ

Î

—

ОООООООО

Î

Feedthrough Noise, Control to

Switch

(Figure 7)

ОООООООООООО

Î

Vin v 1 MHz Square Wave (tr = tf = 6 ns)

Adjust RL at Setup so that IS = 0 A

RL = 600 Ω, CL = 50 pF

Î

Î

4.5

9.0

12.0

ÎÎ

Î

60

130

200

Î

Î

mV

PP

ÎÎ

Î

ÎÎ

Î

ОООООООО

Î

ОООООООО

Î

ОООООООООООО

Î

ОООООООООООО

Î

RL = 10 kΩ, CL = 10 pF

Î

Î

Î

Î

4.5

9.0

12.0

ÎÎ

Î

ÎÎ

Î

30

65

100

Î

Î

Î

Î

ÎÎ

Î

—

ОООООООО

Î

Crosstalk Between Any Two Switches

(Figure 12)

ОООООООООООО

Î

fin Sine Wave

Adjust fin Voltage to Obtain 0 dBm at V

IS

fin = 10 kHz, RL = 600 Ω, CL = 50 pF

Î

Î

4.5

9.0

12.0

ÎÎ

Î

– 70

– 70

– 70

Î

Î

dB

ÎÎÎООООООООÎОООООООООООО

Î

fin = 1.0 MHz, RL = 50 Ω, CL = 10 pF

Î

Î

4.5

9.0

12.0

ÎÎ

Î

– 80

– 80

– 80

Î

Î

ÎÎ

Î

ÎÎ

Î

ÎÎ

Î

THD

ОООООООО

Î

ОООООООО

Î

ОООООООО

Î

Total Harmonic Distortion

(Figure 14)

ОООООООООООО

Î

ОООООООООООО

Î

ОООООООООООО

Î

fin = 1 kHz, RL = 10 kΩ, CL = 50 pF

THD = THD

Measured

– THD

Source

VIS = 4.0 VPP sine wave

VIS = 8.0 VPP sine wave

VIS = 11.0 VPP sine wave

Î

Î

Î

Î

Î

Î

4.5

9.0

12.0

ÎÎ

Î

ÎÎ

Î

ÎÎ

Î

0.10

0.06

0.04

Î

Î

Î

Î

Î

Î

%

*Guaranteed limits not tested. Determined by design and verified by qualification.

Loading...

Loading...