Linear Technology LTC1272-8CCN, LTC1272-8ACS, LTC1272-3CCS, LTC1272-3CCN, LTC1272-3ACS Datasheet

...

FEATURES

■AD7572 Pinout

■12-Bit Resolution

■3μs and 8μs Conversion Times

■On-Chip Sample-and-Hold

■Up to 250kHz Sample Rates

■5V Single Supply Operation

■No Negative Supply Required

■On-Chip 25ppm/°C Reference

■75mW (Typ) Power Consumption

■24-Pin Narrow DIP and SOL Packages

■ESD Protected on All Pins

APPLICATIOUS

■High Speed Data Acquisition

■Digital Signal Processing (DSP)

■Multiplexed Data Acquisition Systems

■Single Supply Systems

LTC1272

12-Bit, 3μs, 250kHz Sampling A/D Converter

DESCRIPTIOU

The LTC1272 is a 3μs, 12-bit, successive approximation sampling A/D converter. It has the same pinout as the industry standard AD7572 and offers faster conversion time, on-chip sample-and-hold, and single supply operation. It uses LTBiCMOSTM switched-capacitor technology to combine a high speed 12-bit ADC with a fast, accurate sample-and-hold and a precision reference.

The LTC1272 operates with a single 5V supply but can also accept the 5V/–15V supplies required by the AD7572 (Pin

23, the negative supply pin of the AD7572, is not connected on the LTC1272). The LTC1272 has the same 0V to 5V input range as the AD7572 but, to achieve single supply operation, it provides a 2.42V reference output instead of the

– 5.25V of the AD7572. It plugs in for the AD7572 if the reference capacitor polarity is reversed and a 1μs sample- and-hold acquisition time is allowed between conversions.

The output data can be read as a 12-bit word or as two 8-bit bytes. This allows easy interface to both 8-bit and higher processors. The LTC1272 can be used with a crystal or an external clock and comes in speed grades of 3μs and 8μs.

LTBiCMOS is a trademark of Linear Technology Corporation

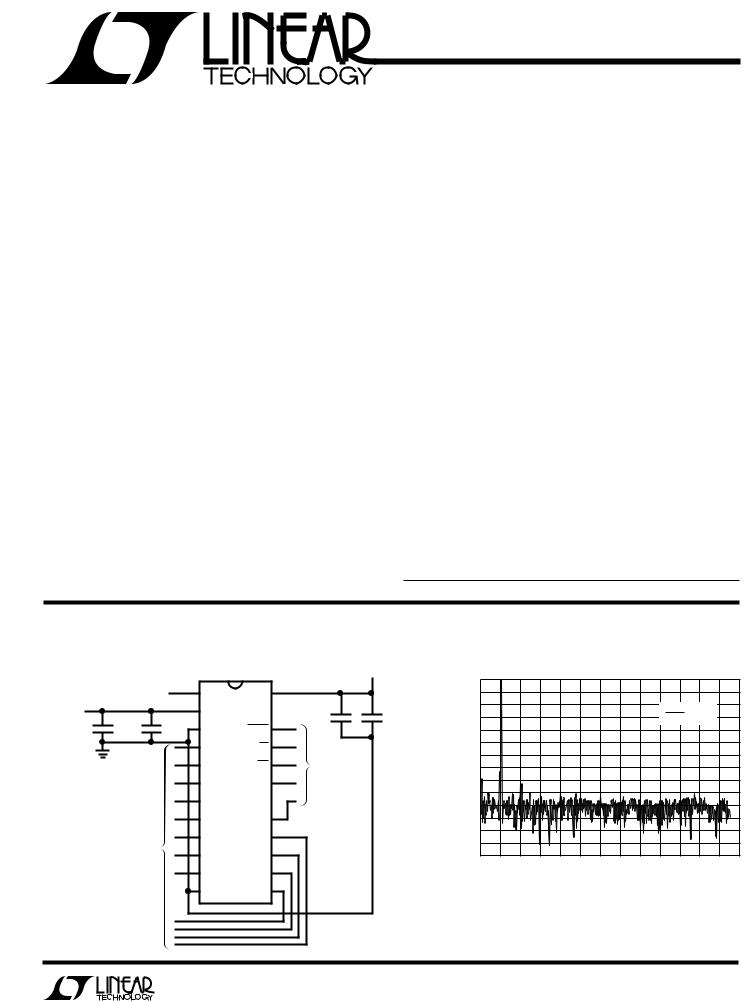

TYPICAL APPLICATIOU

|

Single 5V Supply, 3μs, 12-Bit Sampling ADC |

5V |

|

|

1024 Point FFT, fS = 250kHz, fIN = 10kHz |

||||||||||||

|

|

|

LTC1272 |

|

|

|

|

0 |

|

|

|

|

|

|

|||

|

ANALOG INPUT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

A IN |

|

VDD |

|

|

|

|

|

|

|

|

|

|

|

|

||

2.42V |

(0V TO 5V) |

|

|

|

+ |

|

|

–20 |

|

|

|

|

|

|

|||

VREF |

|

NC |

|

|

|

|

|

|

|

|

S |

= 72.1 |

|||||

VREF |

+ |

|

|

|

|

|

|

|

|

|

|

||||||

|

|

10 |

μ |

F |

μ |

F |

|

|

|

|

|

(N+D) |

|||||

OUTPUT |

10μF |

|

|

|

|

0.1 |

|

|

|

|

|

|

|

||||

0.1μF |

AGND |

|

BUSY |

|

|

|

|

(dB) |

–40 |

|

|

|

|

|

|

||

|

|

|

D11 (MSB) |

CS |

μP |

|

–60 |

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

AMPLITUDE |

|

|

|

|

|

|

||||

|

|

|

D10 |

|

RD |

|

CONTROL |

|

|

|

|

|

|

|

|

||

|

|

|

D9 |

|

HBEN |

|

LINES |

|

|

–80 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

D8 |

CLK OUT |

|

|

|

|

|

–100 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D7 |

|

CLK IN |

|

|

|

|

|

|

|

|

|

|

|

|

|

8 OR 12-BIT |

|

D6 |

|

D0/8 |

|

|

|

|

|

–120 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

PARALLEL |

|

D5 |

|

D1/9 |

|

|

|

|

|

–140 |

|

|

|

|

|

|

|

BUS |

|

|

|

|

|

|

|

20 |

40 |

60 |

80 |

100 |

120 |

|||

|

|

|

|

|

|

|

|

|

|

0 |

|||||||

|

|

|

D4 |

|

D2/10 |

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

FREQUENCY (kHz) |

|

|

|||

|

|

|

DGND |

|

D3/11 |

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LTC1272 • TA02 |

||

|

|

|

|

|

|

|

|

LTC1272 • TA01 |

|

|

|

|

|

|

|

|

|

1

LTC1272

ABSOLUTE WAXIWUW RATIUGS

(Notes 1 and 2)

Supply Voltage (VDD) ................................................. |

6V |

Analog Input Voltage (Note 3) ................... |

– 0.3V to 15V |

Digital Input Voltage .................................. |

– 0.3V to 12V |

Digital Output Voltage .................... |

– 0.3V to VDD + 0.3V |

Power Dissipation .............................................. |

500mW |

Operating Temperature Range |

0°C to 70°C |

LTC1272-XAC, CC ................................. |

|

Storage Temperature Range ................. |

– 65°C to 150°C |

Lead Temperature (Soldering, 10 sec).................. |

300°C |

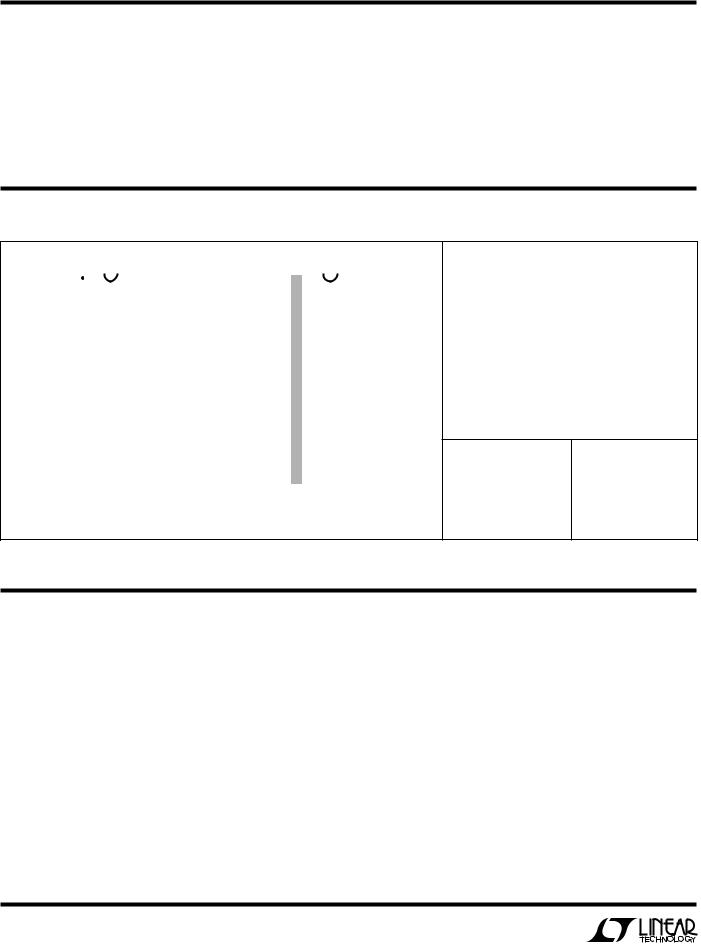

PACKAGE/ORDER IUFORWATIOU

|

|

TOP VIEW |

|

|

|

|

|

|

|

TOP VIEW |

|

|

|

|

||||

A IN |

|

|

|

|

VDD |

|

|

|

|

|

|

|

|

|

|

|||

1 |

|

24 |

|

A IN |

1 |

|

|

24 |

|

VDD |

||||||||

|

|

|

|

|

NC |

|

|

|

|

|

|

|

|

|

|

|||

VREF |

2 |

|

23 |

|

VREF |

2 |

|

|

23 |

|

NC |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AGND |

3 |

|

22 |

|

BUSY |

|

AGND |

3 |

|

|

22 |

|

BUSY |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(MSB) D11 |

4 |

|

21 |

|

CS |

|

|

(MSB) D11 |

4 |

|

|

21 |

|

CS |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D10 |

5 |

|

20 |

|

RD |

|

D10 |

5 |

|

|

20 |

|

RD |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D9 |

6 |

|

19 |

|

HBEN |

D9 |

6 |

|

|

19 |

|

HBEN |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D8 |

7 |

|

18 |

|

CLK OUT |

D8 |

7 |

|

|

18 |

|

CLK OUT |

||||||

D7 |

|

|

|

|

CLK IN |

|

|

|

|

|

|

|

|

|

|

|||

8 |

|

17 |

|

D7 |

8 |

|

|

17 |

|

CLK IN |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D6 |

9 |

|

16 |

|

D0/8 |

D6 |

9 |

|

|

16 |

|

D0/8 |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D5 |

10 |

|

15 |

|

D1/9 |

D5 |

10 |

|

|

15 |

|

D1/9 |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D4 |

11 |

|

14 |

|

D2/10 |

D4 |

11 |

|

|

14 |

|

D2/10 |

||||||

DGND |

|

|

|

|

D3/11 |

|

|

|

|

|

|

|

|

|

|

|||

12 |

|

13 |

|

DGND |

12 |

|

|

13 |

|

D3/11 |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

N PACKAGE |

|

|

|

|

|

|

|

S PACKAGE |

|

|

|

|

||||

|

24-LEAD PLASTIC DIP |

|

|

|

|

|

|

24-LEAD PLASTIC SOL |

|

|

|

|

||||||

TJMAX = 110°C, θJA = 100°C/W |

|

|

|

|

|

TJMAX = 110°C, θJA = 130°C/W |

|

|

|

|

||||||||

ORDER PART NUMBER

CONVERSION |

CONVERSION |

TIME = 3μs |

TIME = 8μs |

|

|

LTC1272-3ACN |

LTC1272-8ACN |

LTC1272-3CCN |

LTC1272-8CCN |

|

|

S PACKAGE ONLY

LTC1272-3ACS LTC1272-8ACS LTC1272-3CCS LTC1272-8CCS

Consult factory for Industrial and Military grade parts.

COUVERTER CHARACTERISTICS |

With Internal Reference (Note 4) |

|

|

|

|

|||||

|

|

|

|

|

LTC1272-XA |

|

|

LTC1272-XC |

|

|

PARAMETER |

CONDITIONS |

|

|

MIN |

TYP |

MAX |

MIN |

TYP |

MAX |

UNITS |

Resolution (No Missing Codes) |

|

|

● |

12 |

|

|

12 |

|

|

Bits |

|

|

|

|

|

|

|

|

|

|

|

Integral Linearity Error |

(Note 5) |

|

● |

|

|

±1/2 |

|

|

±1 |

LSB |

|

|

|

|

|

|

|

|

|

|

|

Differential Linearity Error |

|

|

● |

|

|

±1 |

|

|

±1 |

LSB |

|

|

|

|

|

|

|

|

|

|

|

Offset Error |

|

|

|

|

|

±3 |

|

|

±4 |

LSB |

|

|

|

● |

|

|

±4 |

|

|

±6 |

LSB |

|

|

|

|

|

|

|

|

|

|

|

Gain Error |

|

|

|

|

|

±10 |

|

|

±15 |

LSB |

|

|

|

|

|

|

|

|

|

|

|

Full-Scale Tempco |

IOUT (Reference) = 0 |

|

● |

|

±5 |

±25 |

|

±10 |

±45 |

ppm/°C |

2

LTC1272

IUTERUAL REFEREUCE CHARACTERISTICS (Note 4) |

|

|

|

|

|

||||

|

|

|

|

LTC1272-XA |

|

|

LTC1272-XC |

|

|

PARAMETER |

CONDITIONS |

|

MIN |

TYP |

MAX |

MIN |

TYP |

MAX |

UNITS |

|

|

|

|

|

|

|

|

|

|

VREF Output Voltage (Note 6) |

IOUT = 0 |

|

2.400 |

2.420 |

2.440 |

2.400 |

2.420 |

2.440 |

V |

VREF Output Tempco |

IOUT = 0 |

● |

|

5 |

25 |

|

10 |

45 |

ppm/°C |

VREF Line Regulation |

4.75V £ VDD £ 5.25V, IOUT = 0 |

|

|

0.01 |

|

|

0.01 |

|

LSB/V |

VREF Load Regulation (Sourcing Current) |

0 £ êIOUT ê £ 1mA |

|

|

2 |

|

|

2 |

|

LSB/mA |

DIGITAL AUD DC ELECTRICAL CHARACTERISTICS |

(Note 4) |

|

|

|

|

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LTC1272-XA/C |

|

|

|

|

SYMBOL |

PARAMETER |

CONDITIONS |

|

|

|

|

MIN |

TYP |

MAX |

UNITS |

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VIH |

High Level Input Voltage |

CS, |

|

|

RD, |

HBEN, CLK IN |

VDD = 5.25V |

|

● |

|

2.4 |

|

|

V |

||||||||||||

|

VIL |

Low Level Input Voltage |

|

|

|

|

|

|

|

|

VDD = 4.75V |

|

|

|

|

|

|

0.8 |

V |

||||||||

|

CS, |

RD, HBEN, CLK IN |

|

● |

|

|

|

||||||||||||||||||||

|

IIN |

Input Current |

|

|

|

HBEN |

VIN = 0V to VDD |

|

|

|

|

|

|

±10 |

mA |

||||||||||||

|

CS, |

RD, |

|

● |

|

|

|

||||||||||||||||||||

|

|

Input Current CLK IN |

VIN = 0V to VDD |

|

● |

|

|

|

±20 |

mA |

|||||||||||||||||

|

VOH |

High Level Output Voltage All Logic Outputs |

VDD = 4.75V IOUT = – 10mA |

|

|

|

|

|

4.7 |

|

V |

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IOUT = – 200mA |

|

● |

|

|

4.0 |

|

V |

|

|

VOL |

Low Level Output Voltage All Logic Outputs |

VDD = 4.75V, IOUT = 1.6mA |

|

● |

|

|

|

0.4 |

V |

|||||||||||||||||

|

IOZ |

High-Z Output Leakage D11-D0/8 |

VOUT = 0V to VDD |

|

● |

|

|

|

±10 |

mA |

|||||||||||||||||

|

COZ |

High-Z Output Capacitance (Note 7) |

|

|

|

|

|

|

● |

|

|

|

15 |

pF |

|||||||||||||

|

ISOURCE |

Output Source Current |

VOUT = 0V |

|

|

|

|

|

– 10 |

|

mA |

||||||||||||||||

|

ISINK |

Output Sink Current |

VOUT = VDD |

|

|

|

|

|

10 |

|

mA |

||||||||||||||||

|

IDD |

Positive Supply Current |

|

|

= |

|

= VDD, AIN = 5V |

|

|

|

|

|

15 |

30 |

mA |

||||||||||||

|

CS |

RD |

|

● |

|

|

|||||||||||||||||||||

|

PD |

Power Dissipation |

|

|

|

|

|

|

|

|

|

|

75 |

|

mW |

||||||||||||

DYUAWIC ACCURACY (Note 4) fSAMPLE = 250kHz (LTC1272-3), 111kHz (LTC1272-8) |

|

|

|

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LTC1272-XA/C |

|

|

|

SYMBOL |

PARAMETER |

CONDITIONS |

|

|

|

|

MIN |

TYP |

MAX |

UNITS |

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

S/(N + D) |

Signal-to-Noise Plus Distortion Ratio |

10kHz Input Signal |

|

|

|

|

|

72 |

|

dB |

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

THD |

Total Harmonic Distortion (Up to 5th Harmonic) |

10kHz Input Signal |

|

|

|

|

|

– 82 |

|

dB |

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

Peak Harmonic or Spurious Noise |

10kHz Input Signal |

|

|

|

|

|

– 82 |

|

dB |

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AUALOG I

U

PUT

(Note 4)

|

|

|

|

|

LTC1272-XA/B/C |

|

|

SYMBOL |

PARAMETER |

CONDITIONS |

|

MIN |

TYP |

MAX |

UNITS |

|

|

|

|

|

|

|

|

VIN |

Input Voltage Range |

4.75V £ VDD £ 5.25V |

● |

0 |

|

5 |

V |

IIN |

Input Current |

|

● |

|

|

3.5 |

mA |

CIN |

Input Capacitance |

|

|

|

50 |

|

pF |

tACQ |

Sample-and-Hold Acquisition Time |

|

● |

|

0.45 |

1 |

ms |

3

LTC1272

TIWIUG CHARACTERISTICS |

(Note 8) |

|

|

|

|

|

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LTC1272-XA/C |

|

|

SYMBOL |

PARAMETER |

|

CONDITIONS |

|

MIN |

TYP |

MAX |

UNITS |

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t1 |

|

|

|

CS |

|

|

to |

RD |

|

|

Setup Time |

|

|

● |

0 |

|

|

ns |

||||||||||||

t2 |

|

|

|

|

to |

|

|

|

|

|

Delay |

|

CL = 50pF |

|

|

80 |

190 |

ns |

||||||||||||

RD |

BUSY |

|

|

|

||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

COM Grade |

● |

|

|

230 |

ns |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t3 |

Data Access Time After |

|

↓ |

|

CL = 20pF |

|

|

50 |

90 |

ns |

||||||||||||||||||||

RD |

|

|

|

|||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

COM Grade |

● |

|

|

110 |

ns |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CL = 100pF |

|

|

70 |

125 |

ns |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

COM Grade |

● |

|

|

150 |

ns |

t4 |

|

|

|

Pulse Width |

|

|

|

t3 |

|

|

ns |

|||||||||||||||||||

RD |

|

|

|

|

|

|||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

COM Grade |

● |

t3 |

|

|

ns |

t5 |

|

|

to |

|

|

|

Hold Time |

|

|

|

0 |

|

|

ns |

||||||||||||||||

CS |

RD |

|

|

● |

|

|

||||||||||||||||||||||||

t6 |

Data Setup Time After |

|

|

|

|

|

|

40 |

70 |

ns |

||||||||||||||||||||

BUSY |

|

|

|

|

||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

COM Grade |

● |

|

|

90 |

ns |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t7 |

Bus Relinquish Time |

|

|

|

20 |

30 |

75 |

ns |

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

COM Grade |

● |

20 |

|

85 |

ns |

t8 |

HBEN to |

|

Setup Time |

|

|

|

0 |

|

|

ns |

||||||||||||||||||||

RD |

|

|

● |

|

|

|||||||||||||||||||||||||

t9 |

HBEN to |

|

Hold Time |

|

|

|

0 |

|

|

ns |

||||||||||||||||||||

RD |

|

|

● |

|

|

|||||||||||||||||||||||||

t10 |

Delay Between |

|

Operations |

|

|

|

200 |

|

|

ns |

||||||||||||||||||||

RD |

|

|

● |

|

|

|||||||||||||||||||||||||

t11 |

Delay Between Conversions |

|

|

|

1 |

|

|

μs |

||||||||||||||||||||||

t12 |

Aperture Delay of Sample and Hold |

|

Jitter <50ps |

|

|

25 |

|

ns |

||||||||||||||||||||||

t13 |

CLK to |

|

Delay |

|

|

|

|

80 |

170 |

ns |

||||||||||||||||||||

BUSY |

|

|

|

|

||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

COM Grade |

● |

|

|

220 |

ns |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tCONV |

Conversion Time |

|

|

● |

12 |

|

13 |

CLK |

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CYCLES |

The ● indicates specifications which apply over the full operating temperature range; all other limits and typicals TA = 25°C.

Note 1: Absolute maximum ratings are those values beyond which the life of a device may be impaired.

Note 2: All voltage values are with respect to ground with DGND and AGND wired together, unless otherwise noted.

Note 3: When the analog input voltage is taken below ground it will be clamped by an internal diode. This product can handle, with no external diode, input currents of greater than 60mA below ground without latch-up.

Note 4: VDD = 5V, fCLK = 4MHz for LTC1272-3, and 1.6MHz for LTC1272-8, tr = tf = 5ns unless otherwise specified. For best analog

performance, the LTC1272 clock should be synchronized to the RD and CS control inputs with at least 40ns separating convert start from the nearest clock edge.

Note 5: Linearity error is specified between the actual end points of the A/D transfer curve.

Note 6: The LTC1272 has the same 0V to 5V input range as the AD7572 but, to achieve single supply operation, it provides a 2.42V reference output instead of the –5.25V of the AD7572. This requires that the polarity of the reference bypass capacitor be reversed when plugging an LTC1272 into an AD7572 socket.

Note 7: Guaranteed by design, not subject to test.

Note 8: VDD = 5V. Timing specifications are sample tested at 25°C to ensure compliance. All input control signals are specified with tr = tf = 5ns (10% to 90% of 5V) and timed from a voltage level of 1.6V. See Figures 13 through 17.

4

LTC1272

PIU FUUCTIOUS

AIN (Pin 1): Analog Input, 0V to 5V Unipolar Input.

VREF (Pin 2): 2.42V Reference Output. When plugging into an AD7572 socket, reverse the reference bypass capacitor polarity and short the 10Ω series resistor.

AGND (Pin 3): Analog Ground.

D11 to D4 (Pins 4-11): Three-State Data Outputs.

DGND (Pin 12): Digital Ground.

D3/11 to D0/8 (Pins 13-16): Three-State Data Outputs.

CLK IN (Pin 17): Clock Input. An external TTL/CMOS compatible clock may be applied to this pin or a crystal can be connected between CLK IN and CLK OUT.

CLK OUT (Pin 18): Clock Output. An inverted CLK IN signal appears at this pin.

Data Bus Output, CS and RD = LOW

HBEN (Pin 19): High Byte Enable Input. This pin is used to multiplex the internal 12-bit conversion result into the lower bit outputs (D7 to D0/8). See table below. HBEN also disables conversion starts when HIGH.

RD (Pin 20): Read Input. This active low signal starts a conversion when CS and HBEN are low. RD also enables the output drivers when CS is low.

CS (Pin 21): The Chip Select Input must be low for the ADC to recognize RD and HBEN inputs.

BUSY (Pin 22): The BUSY Output is low when a conversion is in progress.

NC (Pin 23): Not Connected Internally. The LTC1272 does not require negative supply. This pin can accommodate the –15V required by the AD7572 without problems.

VDD (Pin 24): Positive Supply, 5V.

|

Pin 4 |

Pin 5 |

Pin 6 |

Pin 7 |

Pin 8 |

Pin 9 |

Pin 10 |

Pin 11 |

Pin 13 |

Pin 14 |

Pin 15 |

Pin 16 |

|

|

|

|

|

|

|

|

|

|

|

|

|

MNEMONIC* |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3/11 |

D2/10 |

D1/9 |

D0/8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

HBEN = LOW |

DB11 |

DB10 |

DB9 |

DB8 |

DB7 |

DB6 |

DB5 |

DB4 |

DB3 |

DB2 |

DB1 |

DB0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

HBEN = HIGH |

DB11 |

DB10 |

DB9 |

DB8 |

LOW |

LOW |

LOW |

LOW |

DB11 |

DB10 |

DB9 |

DB8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

*D11...D0/8 are the ADC data output pins.

DB11...DB0 are the 12-bit conversion results, DB11 is the MSB.

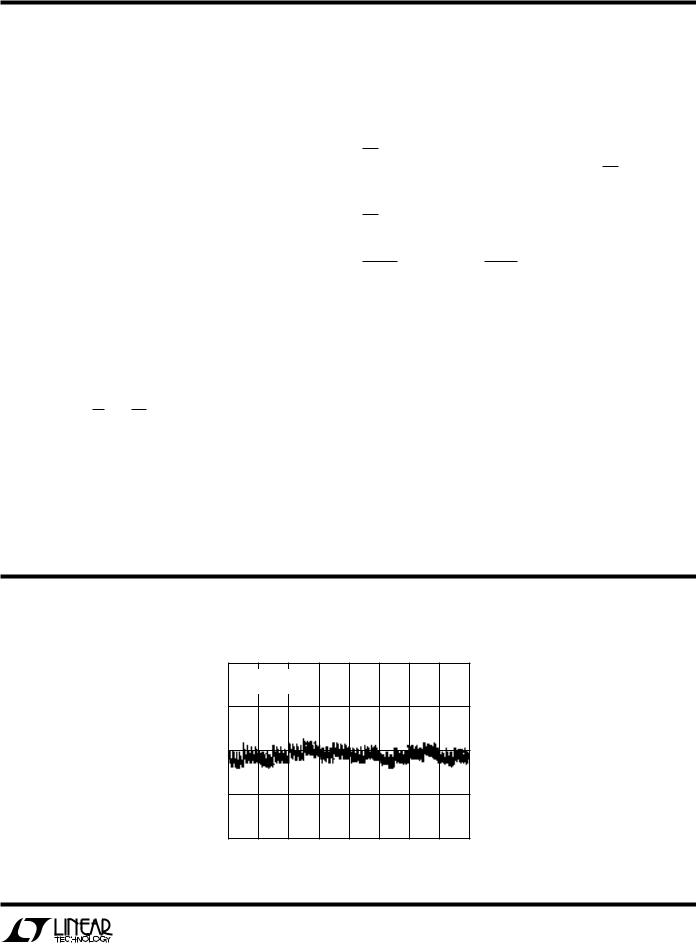

TYPICAL PERFORWAUCE CHARACTERISTICS

Integral Nonlinearity

INL ERROR (LSBs)

1.0

VDD = 5V fCLK = 4MHz

0.5

0

–0.5

–1.0

0 |

512 |

1024 |

1536 |

2048 |

2560 |

3072 |

3584 |

4096 |

CODE

LTC1272 • TPC01

5

LTC1272

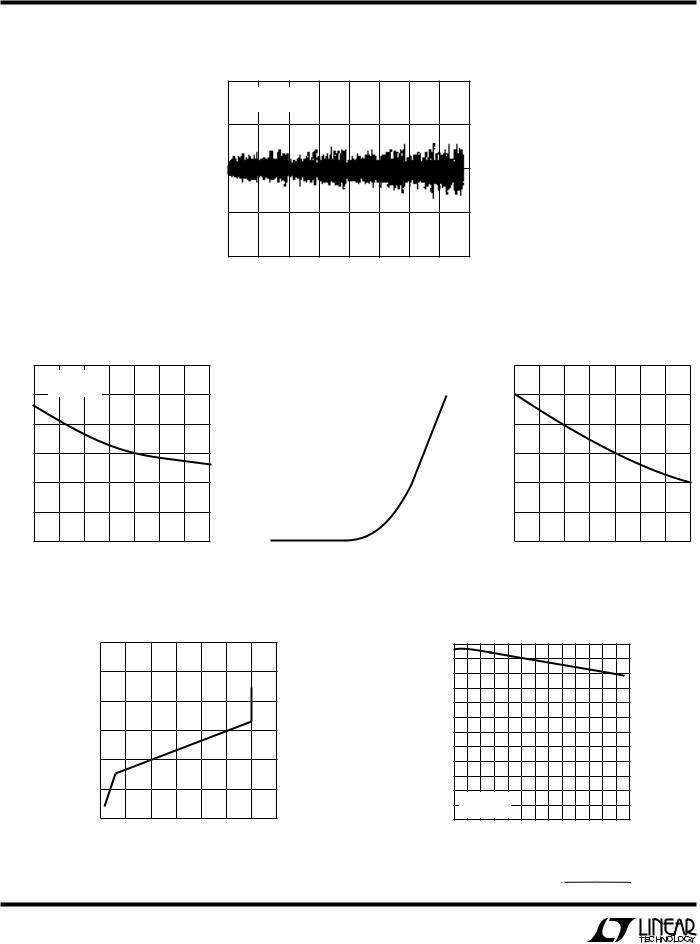

TYPICAL PERFORWAUCE CHARACTERISTICS

INL ERROR (LSBs)

Differential Nonlinearity

1.0

VDD = 5V

fCLK = 4MHz

0.5

0

–0.5

–1.0

0 |

512 |

1024 |

1536 |

2048 |

2560 |

3072 |

3584 |

4096 |

CODE

LTC1272 • TPC02

VDD SUPPLY CURRENT, IDD (mA)

VDD Supply Current vs

Temperature

30

VDD = 5V 25 fCLK = 4MHz

20

15

10

5

0 |

–25 |

0 |

25 |

50 |

75 |

100 |

125 |

–55 |

TEMPERATURE (°C)

LT1272 • TPC03

Minimum Clock Frequency vs

Temperature

|

600 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VDD = 5V |

|

|

|

|

|

|

|

|

|

|

|||

(kHz) |

500 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

400 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

FREQUENCY |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

300 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CLOCK |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

200 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

100 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

–25 |

0 |

25 |

50 |

75 |

100 |

125 |

||||||||

|

–55 |

|||||||||||||||

TEMPERATURE (°C)

LT1272 • TPC04

CLOCK FREQUENCY (MHz)

Maximum Clock Frequency vs Temperature

8

7

6

5

4

3

2 |

–25 |

0 |

25 |

50 |

75 |

100 |

125 |

–55 |

TEMPERATURE (°C)

LT1272 • TPC05

|

VREF vs ILOAD (mA) |

|

|

|

|

|||

|

2.435 |

|

|

|

|

|

|

|

|

2.430 |

|

|

|

|

|

|

|

|

2.425 |

|

|

|

|

|

|

|

(V) |

2.420 |

|

|

|

|

|

|

ENOBs* |

V |

|

|

|

|

|

|

||

REF |

|

|

|

|

|

|

|

|

|

2.415 |

|

|

|

|

|

|

|

|

2.410 |

|

|

|

|

|

|

|

|

2.405 |

–4 |

–3 |

–2 |

–1 |

0 |

1 |

2 |

|

–5 |

|||||||

|

|

|

|

IL (mA) |

|

LT1272 • TPC06 |

||

|

|

|

|

|

|

|

||

LTC1272 ENOBs* vs Frequency

12

11

10

9

8

7

6

5

4

3

2

fS = 250kHz 1 VDD = 5V

0

0 |

20 |

40 |

60 |

80 |

100 |

120 |

fIN (kHz)

LT1272 • TPC07

*EFFECTIVE NUMBER OF BITS, ENOBs = S/(N + D) – 1.76dB 6.02

6

Loading...

Loading...