Linear Technology LTC1291BIJ8, LTC1291BCN8, LTC1291DMJ8, LTC1291DIN8, LTC1291DIJ8 Datasheet

...

FEATURES

■Built-In Sample-and-Hold

■Single Supply 5V Operation

■Power Shutdown

■Direct 3- or 4-Wire Interface to Most MPU Serial Ports and All MPU Parallel Ports

■Two-Channel Analog Multiplexer

■Analog Inputs Common Mode to Supply Rails

■8-Pin DIP Package

KEY SPECIFICATIOUS

■Resolution: 12 Bits

■Fast Conversion Time: 12μs Max Over Temp.

■Low Supply Current:

6.0mA (Typ) Active Mode

10μA (Max) Shutdown Mode

LTC1291

Single Chip 12-Bit

Data Acquisition System

DESCRIPTIOU

The LTC1291 is a data acquisition system that contains a serial I/O successive approximation A/D converter. It uses LTCMOSTM switched capacitor technology to perform a 12-bit unipolar A/D conversion. The input multiplexer can be configured for either single-ended or differential inputs. An on-chip sample-and-hold is included on the “+” input. When the LTC1291 is idle, it can be powered down in applications where low power consumption is desired. An external reference is not required because the LTC1291 takes its reference from the power supply (VCC). All these features are packaged in an 8-pin DIP.

The serial I/O is designed to communicate without external hardware to most MPU serial ports and all MPU parallel I/O ports allowing data to be transmitted over three or four wires. Given the accuracy, ease of use and small package size, this device is well suited for digitizing analog signals in remote applications where minimum number of interconnects, small physical size, and low power consumption are important.

LTCMOSTM is a trademark of Linear Technology Corporation

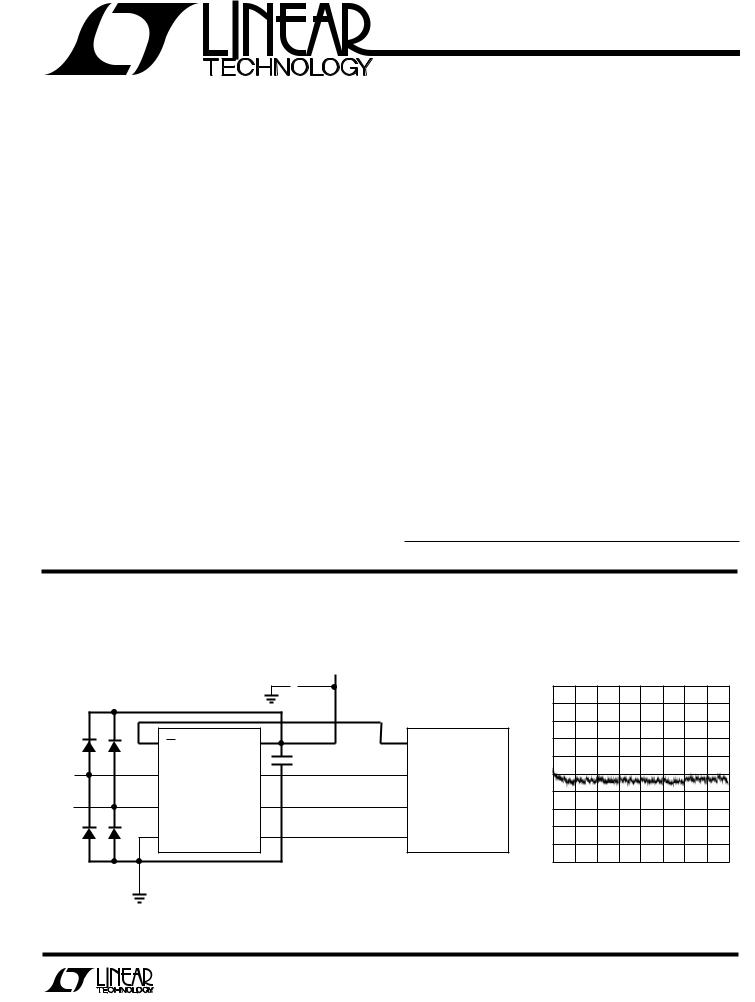

TYPICAL APPLICATIOU

2-Channel 12-Bit Data Acquisition System |

Channel-to-Channel |

22µF |

INL Matching |

TANTALUM +5V |

|

+

+

CS |

VCC(VREF) |

DO |

(LSB) |

|

|

|

0.1µF |

||

CH0 |

CLK |

SCK |

||

DELTA |

||||

2-CHANNEL |

LTC1291 |

MC68HC11 |

||

MUX* |

||||

|

|

|

||

CH1 |

DOUT |

MISO |

|

|

GND |

DIN |

MOSI |

|

|

|

|

1291 TA01 |

|

0.5

0.4

0.3

0.2

0.1

0

–0.1

–0.2

–0.3

–0.4

–0.5

0 512 1024 1536 2048 2560 3072 3584 4096

*FOR OVERVOLTAGE PROTECTION LIMIT THE INPUT CURRENT TO 15mA |

CODE |

PER PIN OR CLAMP THE INPUTS TO VCC AND GND WITH 1N4148 DIODES. |

1291 TA02 |

CONVERSION RESULTS ARE NOT VALID WHEN THE SELECTED CHANNEL OR |

|

THE OTHER CHANNEL IS OVERVOLTAGED (VIN < GND OR VIN > VCC). SEE |

|

SECTION ON OVERVOLTAGE PROTECTION IN THE APPLICATIONS INFORMATION. |

|

1

LTC1291

ABSOLUTE WAXIWUW |

RATIUGS |

|

(Notes 1 and 2) |

|

|

Supply Voltage (VCC) to GND .................................. |

|

12V |

Voltage |

|

|

Analog Inputs ............................ |

–0.3V to VCC + 0.3V |

|

Digital Inputs........................................ |

|

–0.3V to 12V |

Digital Outputs .......................... |

–0.3V to VCC + 0.3V |

|

Power Dissipation............................................. |

|

500mW |

Operating Temperature Range |

|

|

LTC1291BC, LTC1291CC, |

|

0 ° C to 70°C |

LTC1291DC ............................................ |

|

|

LTC1291BI, LTC1291CI, |

|

–40 ° C to 85°C |

LTC1291DI ........................................ |

|

|

LTC1291BM, LTC1291CM, |

|

–55 ° C to 125°C |

LTC1291DM ................................... |

|

|

Storage Temperature Range ................ |

|

–65 ° C to 150°C |

Lead Temperature (Soldering, 10 sec.) |

................ 300°C |

|

PACKAGE/ORDER IUFORWATIOU

|

|

|

|

|

|

|

|

ORDER PART |

|

|

|

|

|

|

|

|

NUMBER |

|

|

|

|

TOP VIEW |

|

|

LTC1291BMJ8 |

|

|

|

|

|

|

|

|

|

LTC1291CMJ8 |

|

|

|

|

|

|

|

|

|

CS |

1 |

|

8 |

VCC |

(VREF) |

LTC1291DMJ8 |

||

|

|

|

|

|

|

|

|

|

CH0 |

2 |

|

7 |

CLK |

|

|||

|

|

LTC1291BIJ8 |

||||||

|

|

|

|

|

|

|

|

|

CH1 |

3 |

|

6 |

DOUT |

||||

|

LTC1291CIJ8 |

|||||||

|

|

|

|

|

|

|

|

|

GND |

4 |

|

5 |

DIN |

|

LTC1291DIJ8 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

J8 PACKAGE |

|

|

LTC1291BIN8 |

|

|

|

|

8-LEAD CERAMIC DIP |

|

|

LTC1291CIN8 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

N8 PACKAGE |

|

|

LTC1291DIN8 |

|

|

|

|

8-LEAD PLASTIC DIP |

|

|

|||

|

|

|

|

|

LTC1291BCN8 |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LTC1291CCN8 |

|

|

|

|

|

|

|

|

LTC1291DCN8 |

|

|

|

|

|

|

|

|

|

COUVERTER AUD WULTIPLEXER CHARACTERISTICS(Note 3)

|

|

|

|

LTC1291B |

LTC1291C |

LTC1291D |

|

|

PARAMETER |

CONDITIONS |

|

MIN TYP MAX |

MIN TYP MAX |

MIN TYP MAX |

UNITS |

|

|

|

|

|

|

|

|

|

Offset Error |

(Note 4) |

● |

±3.0 |

±3.0 |

±3.0 |

LSB |

|

|

|

|

|

|

|

|

|

Linearity Error (INL) |

(Note 4 & 5) |

● |

±0.5 |

±0.5 |

±0.75 |

LSB |

|

|

|

|

|

|

|

|

|

Gain Error |

(Note 4) |

● |

±1.0 |

±2.0 |

±4.0 |

LSB |

|

|

|

|

|

|

|

|

Minimum Resolution for which No |

|

● |

12 |

12 |

12 |

Bits |

|

|

Missing Codes are Guaranteed |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Analog Input Range |

(Note 7) |

|

|

– 0.05V to VCC + 0.05V |

|

V |

|

On Channel Leakage Current |

On Channel = 5V |

● |

±1 |

±1 |

±1 |

μA |

|

(Note 8) |

Off Channel = 0V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

On Channel = 0V |

● |

±1 |

±1 |

±1 |

μA |

|

|

Off Channel = 5V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Off Channel Lekage Current |

On Channel = 5V |

● |

±1 |

±1 |

±1 |

μA |

|

(Note 8) |

Off Channel = 0V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

On Channel = 0V |

● |

±1 |

±1 |

±1 |

μA |

|

|

Off Channel = 5V |

|

|

|

|

|

|

|

|

|

|

|

|

|

AC CHARACTERISTICS (Note 3)

|

|

|

|

LTC1291B/LTC1291C/LTC1291D |

|

||

SYMBOL |

PARAMETER |

CONDITIONS |

|

MIN |

TYP |

MAX |

UNITS |

|

|

|

|

|

|

|

|

fCLK |

Clock Frequency |

VCC = 5V (Note 6) |

|

(Note 9) |

|

1.0 |

MHz |

|

|

|

|

|

|

|

|

tSMPL |

Analog Input Sample Time |

See Operating Sequence |

|

|

2.5 |

|

CLK Cycles |

|

|

|

|

|

|

|

|

tCONV |

Conversion Time |

See Operating Sequence |

|

|

12 |

|

CLK Cycles |

|

|

|

|

|

|

|

|

tCYC |

Total Cycle Time |

See Operating Sequence (Note 6) |

|

18 CLK |

|

|

Cycles |

|

|

|

|

+ 500ns |

|

|

|

|

|

|

|

|

|

|

|

tdDO |

Delay Time, CLK↓ to DOUT Data Valid |

See Test Circuits |

● |

|

160 |

300 |

ns |

|

|

|

|

|

|

|

|

2

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LTC1291 |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AC CHARACTERISTICS (Note 3) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LTC1291B/LTC1291C/LTC1291D |

|

|

|

||||

SYMBOL |

PARAMETER |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CONDITIONS |

|

|

|

|

MIN |

TYP |

MAX |

|

|

UNITS |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tdis |

Delay Time, |

CS |

|

- to DOUT Hi-Z |

|

See Test Circuits |

|

● |

|

|

|

80 |

150 |

|

|

ns |

|

|||||||||||||||||

ten |

Delay Time, CLK¯ to DOUT Enabled |

|

See Test Circuits |

|

● |

|

|

|

80 |

200 |

|

|

ns |

|

||||||||||||||||||||

thDI |

Hold Time, DIN after CLK- |

|

|

|

|

|

|

|

|

|

|

|

VCC = 5V (Note 6) |

|

|

|

|

50 |

|

|

|

|

ns |

|

||||||||||

thDO |

Time Output Data Remains Valid after CLK¯ |

|

|

|

|

|

|

|

|

130 |

|

|

|

ns |

|

|||||||||||||||||||

tWHCLK |

CLK High Time |

|

|

|

|

|

|

|

|

|

|

|

VCC = 5V (Note 6) |

|

|

|

|

300 |

|

|

|

|

ns |

|

||||||||||

tWLCLK |

CLK Low Time |

|

|

|

|

|

|

|

|

|

|

|

VCC = 5V (Note 6) |

|

|

|

|

400 |

|

|

|

|

ns |

|

||||||||||

tf |

DOUT Fall Time |

|

|

|

|

|

|

|

|

|

|

|

See Test Circuits |

|

● |

|

|

|

65 |

130 |

|

|

ns |

|

||||||||||

tr |

DOUT Rise Time |

|

|

|

|

|

|

|

|

|

|

|

See Test Circuits |

|

● |

|

|

|

25 |

50 |

|

|

ns |

|

||||||||||

tsuDI |

Setup Time, DIN Stable before CLK- |

|

VCC = 5V (Note 6) |

|

|

|

|

50 |

|

|

|

|

ns |

|

||||||||||||||||||||

tsuCS |

|

Setup Time, |

|

¯ before CLK- |

|

VCC = 5V (Note 6) |

|

|

|

|

50 |

|

|

|

|

ns |

|

|||||||||||||||||

CS |

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||

tWHCS |

|

|

|

High Time During Conversion |

|

VCC = 5V (Note 6) |

|

|

|

|

500 |

|

|

|

|

ns |

|

|||||||||||||||||

|

CS |

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||

|

|

|

|

Low Time During Data Transfer |

|

VCC = 5V (Note 6) |

|

|

|

|

18 |

|

|

|

CLK Cycles |

|

||||||||||||||||||

tWLCS |

|

CS |

|

|

|

|

|

|

|

|

||||||||||||||||||||||||

CIN |

Input Capacitance |

|

|

|

|

|

|

|

|

|

|

|

Analog Inputs On Channel |

|

|

|

|

|

|

100 |

|

|

|

pF |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Analog Inputs Off Channel |

|

|

|

|

|

|

5 |

|

|

|

pF |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Digital Inputs |

|

|

|

|

|

|

5 |

|

|

|

pF |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

DIGITAL A |

D DC ELECTRICAL CHARACTERISTICS |

(Note 3) |

|

|

|

|

|

|

||||||||||||||||||||||||||

|

|

|

|

|

U |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LTC1291B/LTC1291C/LTC1291D |

|

|

||||

SYMBOL |

PARAMETER |

|

|

|

CONDITIONS |

|

|

|

|

|

|

|

|

MIN |

TYP |

MAX |

|

UNITS |

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

VIH |

High Level Input Voltage |

VCC = 5.25V |

|

|

|

|

|

|

● |

|

2.0 |

|

|

|

V |

|

||||||||||||||||||

VIL |

Low Level Input Voltage |

VCC = 4.75V |

|

|

|

|

|

|

● |

|

|

|

0.8 |

|

V |

|

||||||||||||||||||

IIH |

High Level Input Current |

VIN = VCC |

|

|

|

|

|

|

● |

|

|

|

2.5 |

|

mA |

|

||||||||||||||||||

IIL |

Low Level Input Current |

VIN = 0V |

|

|

|

|

|

|

● |

|

|

|

–2.5 |

|

mA |

|

||||||||||||||||||

VOH |

High Level Output Voltage |

VCC = 4.75V, IOUT = –10mA |

|

|

|

|

|

|

4.7 |

|

|

V |

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

VCC = 4.75V, IOUT = – 360mA |

|

|

|

● |

|

2.4 |

4.0 |

|

|

V |

|

||||||||||||

VOL |

Low Level Output Voltage |

VCC = 4.75V, IOUT = 1.6mA |

|

|

|

● |

|

|

|

0.4 |

|

V |

|

|||||||||||||||||||||

IOZ |

High Z Output Leakage |

VOUT = VCC, |

|

|

High |

|

|

|

|

|

|

|

3 |

|

mA |

|||||||||||||||||||

CS |

|

|

|

● |

|

|

|

|||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

VOUT = 0V, |

|

High |

|

|

|

|

|

|

|

|

|

|

– 3 |

|

mA |

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

CS |

|

|

|

|

|

|

● |

|

|

|

|||||||||||||

ISOURCE |

Output Source Current |

VOUT = 0V |

|

|

|

|

|

|

|

|

|

– 20 |

|

|

mA |

|

||||||||||||||||||

ISINK |

Output Sink Current |

VOUT = VCC |

|

|

|

|

|

|

|

|

|

20 |

|

|

mA |

|

||||||||||||||||||

ICC |

Positive Supply Current |

|

|

|

|

High |

|

|

|

|

|

|

|

|

|

6 |

12 |

|

mA |

|

||||||||||||||

CS |

|

|

|

|

|

|

● |

|

|

|||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

CS |

High |

|

LTC1291BC, LTC1291CC, LTC1291DC |

|

|

● |

|

|

5 |

10 |

|

mA |

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

Power shutdown |

|

LTC1291BI, LTC1291CI, LTC1291DI, |

|

|

|

● |

|

|

5 |

15 |

|

mA |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

CLK Off |

|

LTC1291BM, LTC1291CM, LTC1291DM |

|

|

|

|

|

|

|

|

|

||||||||||||

The ● denotes specifications which apply over the operating temperature range; all other limits and typicals TA = 25°C.

Note 1: Absolute Maximum Ratings are those values beyond which the life of a device may be impaired.

Note 2: All voltage values are with respect to ground (unless otherwise noted).

Note 3: VCC = 5V, CLK = 1.0MHz unless otherwise specified.

Note 4: One LSB is equal to VCC divided by 4096. For example, when VCC = 5V, 1LSB = 5V/4096 = 1.22mV.

Note 5: Linearity error is specified between the actual end points of the A/D transfer curve. The deviation is measured from the center of the quantization band.

Note 6: Recommended operating conditions.

Note 7: Two on-chip diodes are tied to each analog input which will conduct for analog voltages one diode drop below GND or one diode drop above VCC. Be careful during testing at low VCC levels (4.5V), as high level analog inputs (5V) can cause this input diode to conduct, especially at elevated temperature, and cause errors for inputs near full scale. This spec allows 50mV forward bias of either diode. This means that as long as the analog input does not exceed the supply voltage by more than 50mV, the output code will be correct.

Note 8: Channel leakage current is measured after the channel selection.

Note 9: Increased leakage currents at elevated temperatures cause the S/H to droop, therefore it is recommended that fCLK ³ 125kHz at 125°C, fCLK ³ 30kHz at 85°C and fCLK ³ 3kHz at 25°C.

3

LTC1291

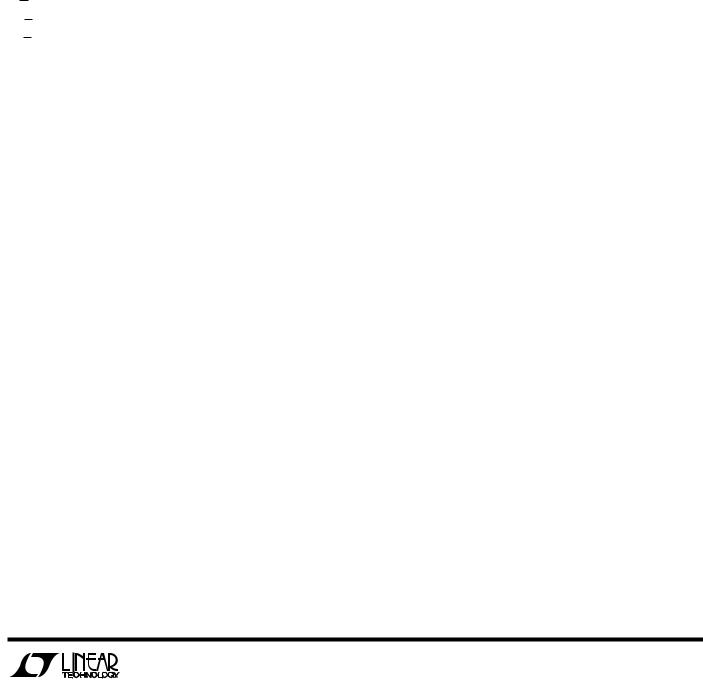

TYPICAL PERFORWAUCE CHARACTERISTICS

|

Supply Current vs Supply Voltage |

|

|

Supply Current vs Temperature |

||||||||||||||||||||||||||

|

10 |

|

|

|

|

|

|

|

10 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

CLK = 1MHz |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CLK = 1MHz |

|

||||||

(mA) |

8 |

|

TA = 25°C |

|

|

|

|

(mA) |

9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VCC = 5V |

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

CURRENT |

6 |

|

|

|

|

|

|

CURRENT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SUPPLY |

4 |

|

|

|

|

|

|

SUPPLY |

6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

4 |

5 |

6 |

–50 –30 –10 |

10 |

30 |

50 |

70 |

90 |

110 |

130 |

|

SUPPLY VOLTAGE (V) |

|

AMBIENT TEMPERATURE (°C) |

|

|

|||||

|

|

1291 G01 |

|

|

|

|

|

|

1291 G02 |

|

|

Change in Linearity vs Supply |

|

|

Change in Gain Error vs Supply |

|||||||

)) |

Voltage |

|

|

|

|

)) |

Voltage |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

REF |

0.5 |

|

|

|

|

REF |

0.5 |

|

|

|

|

(V |

|

|

|

|

|

(V |

0.4 |

|

|

|

|

CC |

|

|

|

|

|

CC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

LINEARITYINCHANGE(LSB = 1/4096 × V |

0.4 |

|

|

|

|

ERRORGAININCHANGE(LSB = 1/4096 ×V |

0.3 |

|

|

|

|

4.0 |

4.5 |

5.0 |

5.5 |

6.0 |

4.0 |

4.5 |

5.0 |

5.5 |

6.0 |

||

|

|

|

|

|

|

|

0.2 |

|

|

|

|

|

0.3 |

|

|

|

|

|

0.1 |

|

|

|

|

|

|

|

|

|

|

|

0 |

|

|

|

|

|

0.2 |

|

|

|

|

|

–0.1 |

|

|

|

|

|

|

|

|

|

|

|

–0.2 |

|

|

|

|

|

0.1 |

|

|

|

|

|

–0.3 |

|

|

|

|

|

|

|

|

|

|

|

–0.4 |

|

|

|

|

|

0 |

|

|

|

|

|

–0.5 |

|

|

|

|

|

|

SUPPLY VOLTAGE (V) |

|

|

|

SUPPLY VOLTAGE (V) |

|

||||

|

|

|

|

|

1291 G04 |

|

|

|

|

|

1291 G05 |

|

Change in Linearity vs |

|

|

|

|

|

|||

|

Temperature |

|

Change in Gain vs Temperature |

||||||

(LSB)CHANGELINEARITY |

0.5 |

|

|

|

|

0.5 |

|

|

|

|

|

|

|

|

|

|

|||

|

|

VCC = 5V |

|

(LSB)CHANGEGAINOF |

|

|

VCC = 5V |

|

|

|

|

|

CLK = 1MHz |

|

|

0.4 |

|

CLK = 1MHz |

|

|

0.4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

||

|

0.3 |

|

|

|

|

0.3 |

|

|

|

|

|

|

|

|

|

|

|

||

MAGNITUDEOF |

0.2 |

|

|

|

MAGNITUDE |

0.2 |

|

|

|

|

|

|

|

|

|

||||

0.1 |

|

|

|

0.1 |

|

|

|

||

|

|

|

|

|

|

|

|

||

|

0 |

|

|

|

|

0 |

|

|

|

|

|

|

|

|

|

|

|

||

–50 –25 0 |

25 50 |

75 100 125 |

–50 –25 0 |

25 50 |

75 100 125 |

AMBIENT TEMPERATURE (°C) |

AMBIENT TEMPERATURE (°C) |

||||

|

|

1291 G07 |

|

|

1291 G08 |

* AS THE CLK FREQUENCY IS DECREASED FROM 1MHz, MINIMUM CLK FREQUENCY ( ERROR ≤ 0.1LSB) REPRESENTS THE FREQUENCY AT WHICH A 0.1LSB SHIFT IN ANY CODE TRANSITION FROM ITS 1MHz VALUE IS FIRST DETECTED.

Change in Offset vs Supply

Voltage

)) |

0.5 |

|

|

|

|

REF |

0.4 |

|

|

|

|

(V |

|

|

|

|

|

CC |

0.3 |

|

|

|

|

V |

|

|

|

|

|

× |

0.2 |

|

|

|

|

1/4096 |

|

|

|

|

|

0.1 |

|

|

|

|

|

= |

0 |

|

|

|

|

(LSB |

|

|

|

|

|

–0.1 |

|

|

|

|

|

IN OFFSET |

|

|

|

|

|

–0.2 |

|

|

|

|

|

–0.3 |

|

|

|

|

|

CHANGE |

–0.4 |

|

|

|

|

–0.5 |

4.5 |

5.0 |

5.5 |

6.0 |

|

|

4.0 |

SUPPLY VOLTAGE (V)

1291 G03

Change in Offset vs Temperature

|

0.5 |

|

|

|

|

|

|

|

(LSB) |

|

VCC = 5V |

|

|

|

|

|

|

|

CLK = 1MHz |

|

|

|

|

|

||

0.4 |

|

|

|

|

|

|

|

|

CHANGE |

|

|

|

|

|

|

|

|

0.3 |

|

|

|

|

|

|

|

|

OFFSET |

|

|

|

|

|

|

|

|

0.2 |

|

|

|

|

|

|

|

|

OF |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MAGNITUDE |

0.1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

0 |

25 |

50 |

75 |

|

125 |

|

–50 |

–25 |

100 |

|||||

AMBIENT TEMPERATURE (°C)

1291 G06

Minimum Clock Rate for 0.1 LSB Error

VCC = 5V

(MHz) |

0.25 |

|

FREQUENCY*CLK |

0.20 |

|

|

||

|

0.15 |

|

MINIMUM |

0.10 |

|

0.05 |

||

|

–50 |

–25 |

0 |

25 |

50 |

75 |

100 |

125 |

AMBIENT TEMPERATURE (°C)

1291 G09

4

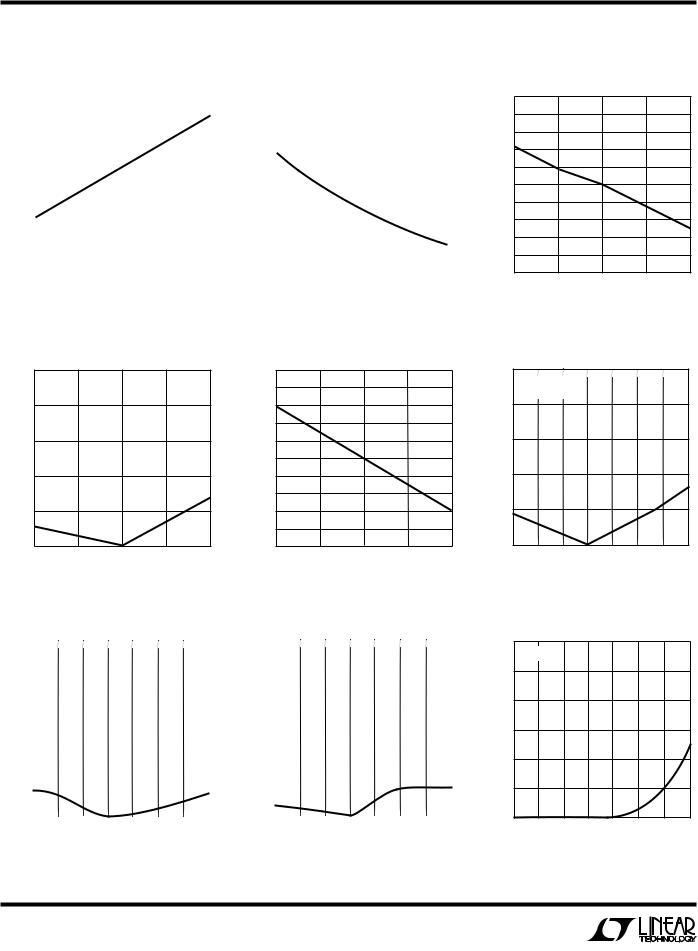

LTC1291

TYPICAL PERFORWAUCE CHARACTERISTICS

|

Maximum Clock Rate vs Source |

DOUT Delay Time vs Temperature |

Resistance |

|

250 |

VCC = 5V |

|

|

|

|

|

|

1.0 |

|

VCC = 5V |

||

|

|

|

|

|

|

|

|

|

|

||||

↓(ns) |

|

|

|

|

|

|

|

|

(MHz) |

|

|

CLK = 1MHz |

|

200 |

|

|

|

|

|

|

|

0.8 |

|

|

|

||

FROMTIMEDELAYCLK |

|

|

|

|

|

|

|

FREQUENCY*CLK |

|

|

|

||

150 |

MSB-FIRST DATA |

|

|

|

|

0.6 |

|

+VIN |

+ +IN |

||||

|

|

|

|

|

|

|

RSOURCE– |

– –IN |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

100 |

|

|

|

LSB-FIRST DATA |

|

MAXIMUM |

0.4 |

|

|

|

||

D |

|

|

|

|

|

|

|

|

|

|

|

|

|

OUT |

50 |

|

|

|

|

|

|

|

|

0.2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

0 |

|

|

25 |

|

|

|

|

|

0 |

|

|

|

|

–50 |

–25 |

0 |

50 |

75 |

100 |

125 |

|

100 |

1k |

10k |

100k |

|

|

|

|

AMBIENT TEMPERATURE (°C) |

|

|

|

RSOURCE– (Ω) |

|

|||||

|

|

|

|

|

|

|

1291 G10 |

|

|

|

|

1291 G11 |

|

|

Maximum Filter Resistor vs |

|

||

|

Cycle Time |

|

|

|

|

10k |

|

|

|

|

|

RFILTER |

+ |

|

Ω) |

1k |

+VIN |

|

|

CFILTER ³1µF |

|

|

||

( |

|

|

– |

|

** |

|

|

|

|

FILTER |

100 |

|

|

|

R |

|

|

|

|

MAXIMUM |

10 |

|

|

|

|

1 |

|

|

|

|

10 |

100 |

1k |

10k |

|

|

CYCLE TIME (µs) |

|

|

|

|

|

|

1291 G12 |

S/H AQUISITION TIME TO 0.02% (µs)

Sample-and-Hold Acquisition |

Input Channel Leakage Current |

Time vs Source Resistance |

vs Temperature |

100 |

|

|

|

1000 |

|

|

|

|

|

|

|

|

VCC = 5V |

|

(nA) |

900 |

|

|

|

|

GUARANTEED |

|

|||

TA |

= 25°C |

|

|

|

|

|

|

|||||

|

CURRENT |

|

|

|

|

|

|

|

|

|

||

0V TO 5V INPUT STEP |

800 |

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

700 |

|

|

|

|

|

|

|

|

|

|

RSOURCE+ |

LEAKAGE |

600 |

|

|

|

|

|

|

|

|

10 |

VIN |

500 |

|

|

|

|

|

|

|

|

||

+ |

|

|

|

|

|

|

|

|

|

|||

|

|

– |

CHANNEL |

400 |

|

|

|

|

|

|

|

|

|

|

|

300 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

INPUT |

200 |

|

|

|

|

ON CHANNEL |

|

||

|

|

|

100 |

|

|

|

|

|

||||

|

|

|

|

|

|

OFF CHANNEL |

|

|

||||

|

|

|

|

|

|

|

|

|

||||

1 |

|

|

|

0 |

|

|

|

|

70 |

90 |

|

|

100 |

|

1k |

10k |

–50 –30 |

–10 |

10 |

30 |

50 |

110 |

130 |

||

|

|

RSOURCE+ (Ω) |

|

|

AMBIENT TEMPERATURE (°C) |

|

|

|||||

|

|

|

1291 G13 |

|

|

|

|

|

|

|

1291 G14 |

|

*MAXIMUM CLK FREQUENCY REPRESENTS THE CLK FREQUENCY AT WHICH A 0.1LSB SHIFT IN THE ERROR AT ANY CODE TRANSITION FROM ITS 1MHz VALUE IS FIRST DETECTED.

**MAXIMUM RFILTER REPRESENTS THE FILTER RESISTOR VALUE AT WHICH A 0.1LSB CHANGE IN FULL SCALE

ERROR FROM ITS VALUE AT RFILTER = 0Ω IS FIRST DETECTED.

PIU FUUCTIOUS

# |

PIN |

FUNCTION |

DESCRIPTION |

|||

|

|

|

|

|

|

|

1 |

|

|

|

Chip Select Input |

A logic low on this input enables the LTC1291. |

|

CS |

||||||

2, 3 |

CH0, CH1 |

Analog Inputs |

These inputs must be free of noise with respect to GND. |

|||

4 |

GND |

Analog Ground |

GND should be tied directly to an analog ground plane. |

|||

5 |

DIN |

Digital Data Input |

The multiplexer address is shifted into this input. |

|||

6 |

DOUT |

Digital Data Output |

The A/D conversion result is shifted out of this output. |

|||

7 |

CLK |

Shift Clock |

This clock synchronizes the serial data transfer. |

|||

8 |

VCC(VREF) |

Positive Supply and |

This pin provides power and defines the span of the A/D converter. This supply must be kept free of noise and |

|||

|

|

|

|

Reference Voltage |

ripple by bypassing directly to the analog ground plane. |

|

|

|

|

|

|

|

|

5

LTC1291

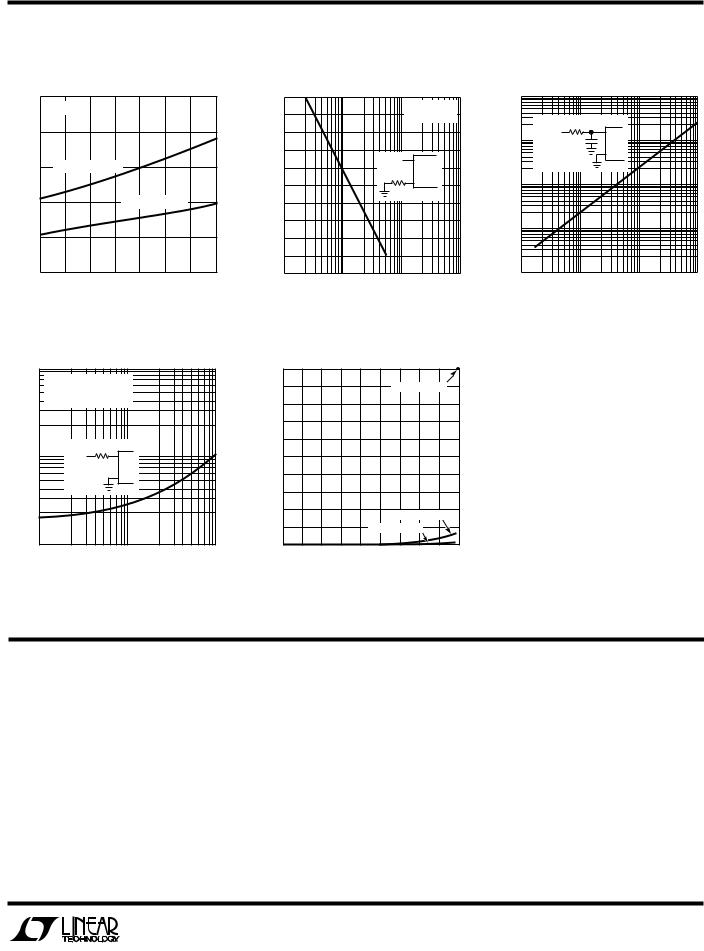

BLOCK DIAGRAW

|

|

|

|

|

|

|

|

7 |

V |

(V |

REF |

) |

8 |

|

|

|

CLK |

CC |

|

|

|

|

|

|

|

|

|

|

|

|

5 |

INPUT |

|

OUTPUT |

6 |

|

|

DIN |

SHIFT |

|

SHIFT |

DOUT |

||

|

|

|

|

|||||

|

|

|

|

|

REGISTER |

|

REGISTER |

|

|

|

CH0 |

2 |

ANALOG |

SAMPLE |

|

|

|

|

|

|

|

|

||||

|

|

|

|

3 |

AND |

|

|

|

|

|

CH1 |

INPUT MUX |

|

|

|||

|

|

|

HOLD |

COMP |

|

|||

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

12-BIT |

|

|

|

|

|

|

|

|

SAR |

|

|

|

|

|

|

|

|

12-BIT |

|

|

|

|

|

|

|

|

CAPACITIVE |

|

|

|

|

|

|

|

|

DAC |

|

|

|

|

|

|

4 |

|

CONTROL |

1 |

|

|

|

|

|

|

AND |

CS |

|

|

|

|

|

|

GND |

|

TIMING |

|

|

|

|

|

|

|

|

|

|

1291 BD

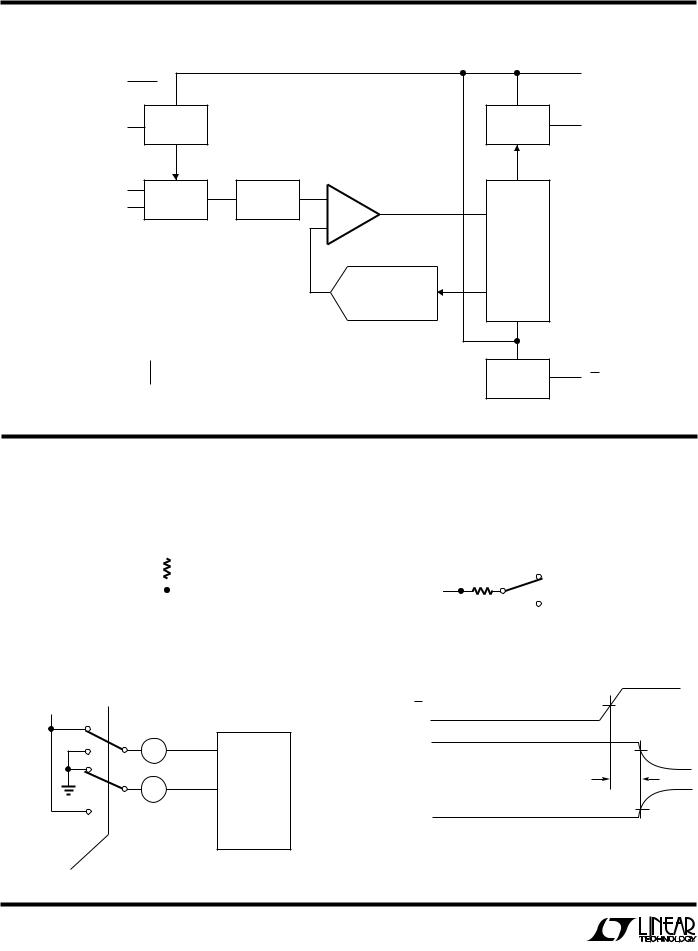

TEST CIRCUITS

Load Circuit for tdDO, tr and tf |

|

|

|

|

|

Load Circuit for tdis and ten |

|||||||||||||||||||||||||

|

|

1.4V |

TEST POINT |

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

3k |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

5V tdis WAVEFORM 2, ten |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

DOUT |

|

|

|

|

|

|

|

|

|

|

TEST POINT |

DOUT |

|

|

|

|

|

|

|

|

|

3k |

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tdis WAVEFORM 1 |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

100pF |

|

|

|

|

|

|

|

|

|

|

100pF |

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

1291 TC02 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1291 TC05 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

On and Off Channel Leakage Current |

|

|

|

Voltage Waveforms for tdis |

|||||||||||||||||||||||||||

5V |

|

CS |

ION |

|

|

A |

ON CHANNEL |

DOUT |

|

|

WAVEFORM 1 |

IOFF |

|

(SEE NOTE 1) |

|

|

|

A |

OFF CHANNEL |

DOUT |

|

|

|

|

|

WAVEFORM 2 |

|

|

(SEE NOTE 2) |

POLARITY |

1291 TC01 |

1291 TC06 |

|

|

2.0V

90%

tdis

10%

NOTE 1: WAVEFORM 1 IS FOR AN OUTPUT WITH INTERNAL CONDITIONS SUCH THAT THE OUTPUT IS HIGH UNLESS DISABLED BY THE OUTPUT CONTROL. NOTE 2: WAVEFORM 2 IS FOR AN OUTPUT WITH INTERNAL CONDITIONS SUCH THAT THE OUTPUT IS LOW UNLESS DISABLED BY THE OUTPUT CONTROL.

6

Loading...

Loading...