Page 1

Please read the Important Notice and Warnings at the end of this document

IM111-X3Q1B

CIPOS™ Nano

IM111-X3Q1B

Description

IM111-X3Q1B is an H-bridge integrated power module (IPM) designed for advanced appliance motor drive

applications. This advanced low profile IPM offers a combination of Infineon’s low R

DS(ON)

OptiMOS ™ technology

and the industry benchmark high voltage, rugged driver in a small 12x10mm QFN package.

Features

Integrated gate drivers and bootstrap

functionality

Overcurrent protection & fault reporting

Low 0.063Ω R

DS(on)

, 250V OptiMOS™

Under-voltage lockout for both channels

Shoot through protection

Matched propagation delay for all channels

Optimized dv/dt for loss and EMI trade offs

Advanced input filter

3.3V input logic compatible

Motor power range 80-200W

1500V

RMS

min isolation

Potential Applications

Linear refrigerator compressors

High efficiency single-phase motor drives

DC-AC inverters

Product Validation

Qualified for industrial applications according to the relevant tests of JEDEC47/20/22.

Table 1 Part Ordering Table

Base Part Number

Package Type

Standard Pack

Orderable Part Number

Form

Quantity

IM111-X3Q1B

QFN 12x10mm

Tray

800

IM111-X3Q1B

Tape and Reel

2000

IM111-X3Q1BTR

Final Datasheet

www.infineon.com

Revision 1.0

2019-12-12

Page 2

CIPOS™ Nano

2

Table of contents

Description ……………………………………………………………………………………………………………..1

Features………………………………………………………………………………………………………………...1

Potential Applications ..................................................................................................................... 1

Product Validation .......................................................................................................................... 1

Table of contents ............................................................................................................................ 2

1

2

2.1

2.2

3

3.1

3.2

3.3

4

5

6

6.1

6.2

7

7.1

7.2

8

9

10

10.1

10.2

11

11.1

11.2

11.3

12

IM111-X3Q1B

Internal Electrical Schematic .......................................................................................... 3

Pin Configuration ........................................................................................................... 4

Pin Assignment ........................................................................................................................................ 4

Pin Descriptions ....................................................................................................................................... 5

Absolute Maximum Rating .............................................................................................. 6

Module ..................................................................................................................................................... 6

Inverter .................................................................................................................................................... 6

Control ..................................................................................................................................................... 6

Thermal Characteristics ................................................................................................. 7

Recommended Operating Conditions ............................................................................... 8

Static Parameters .......................................................................................................... 9

Inverter .................................................................................................................................................... 9

Control ..................................................................................................................................................... 9

Dynamic Parameters ..................................................................................................... 10

Inverter .................................................................................................................................................. 10

Control ................................................................................................................................................... 10

Thermistor Characteristics ............................................................................................ 11

Qualification Information .............................................................................................. 12

Diagrams & Tables ........................................................................................................ 13

Input-Output Logic Table ...................................................................................................................... 13

Switching Time Definitions ................................................................................................................... 13

Application Guide ......................................................................................................... 14

Typical Application Schematic ............................................................................................................. 14

Performance Charts .............................................................................................................................. 14

–Vs Immunity ......................................................................................................................................... 15

Package Outline ........................................................................................................... 16

Revision History ............................................................................................................................ 18

Final Datasheet

Revision 1.0

2019-12-12

Page 3

CIPOS™ Nano

3

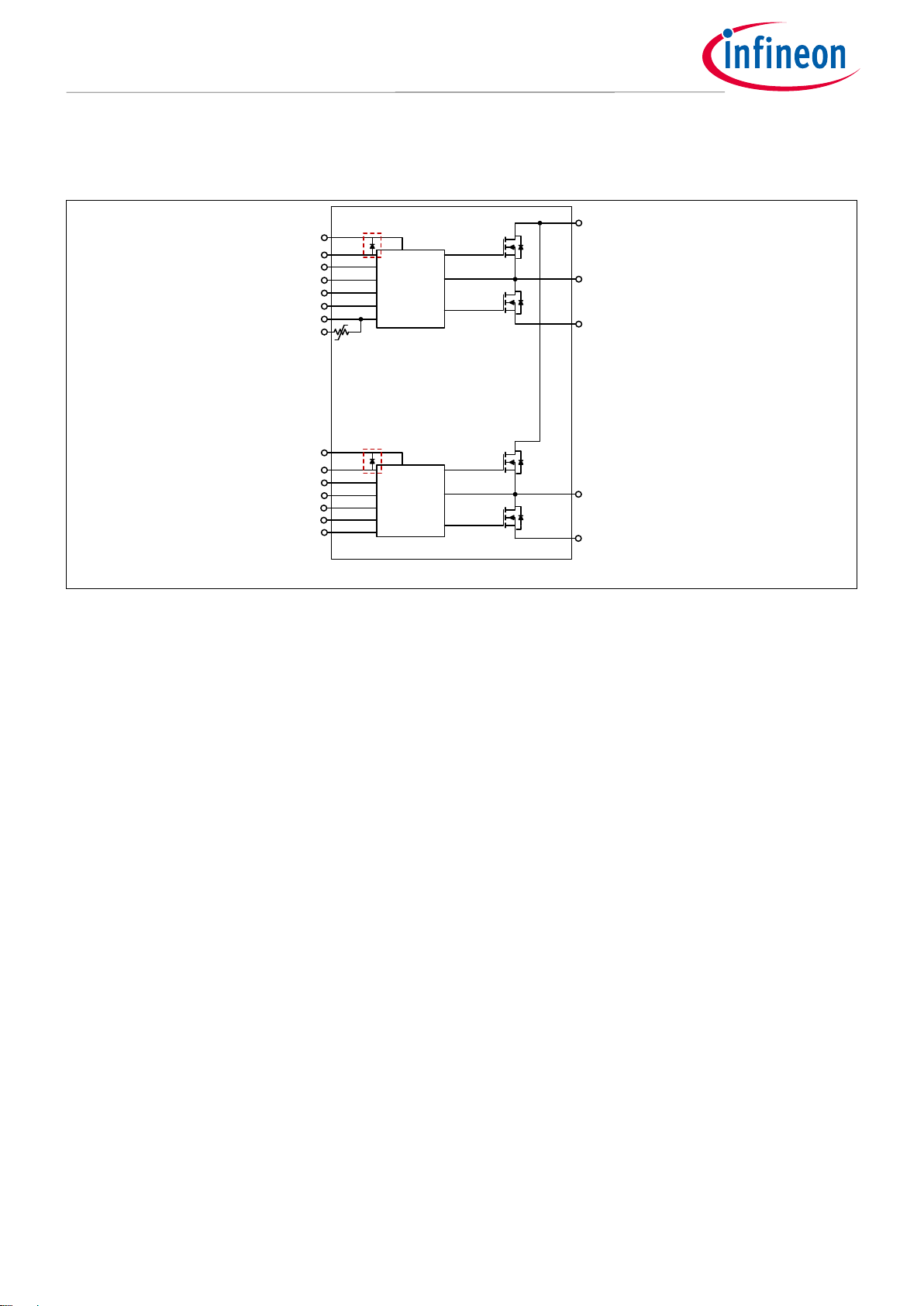

1 Internal Electrical Schematic

Half-Bridge

HVIC

Half-Bridge

HVIC

13 ITRIP1

9 VB1

10 VDD1

11 HIN1

12 LIN1

14 RFE1

15, 39 COM1

16 NTC

36 VB2

37 VDD2

1 HIN2

2 LIN2

5, 38 COM2

6~8, 32~35 V+

19~25 VS1

17~18 VR1

29~30 VR2

26~28, 31 VS2

Integrated in HVIC

3 ITRIP2

4 RFE2

Figure 1 Internal electrical schematic.

IM111-X3Q1B

Final Datasheet

Revision 1.0

2019-12-12

Page 4

CIPOS™ Nano

4

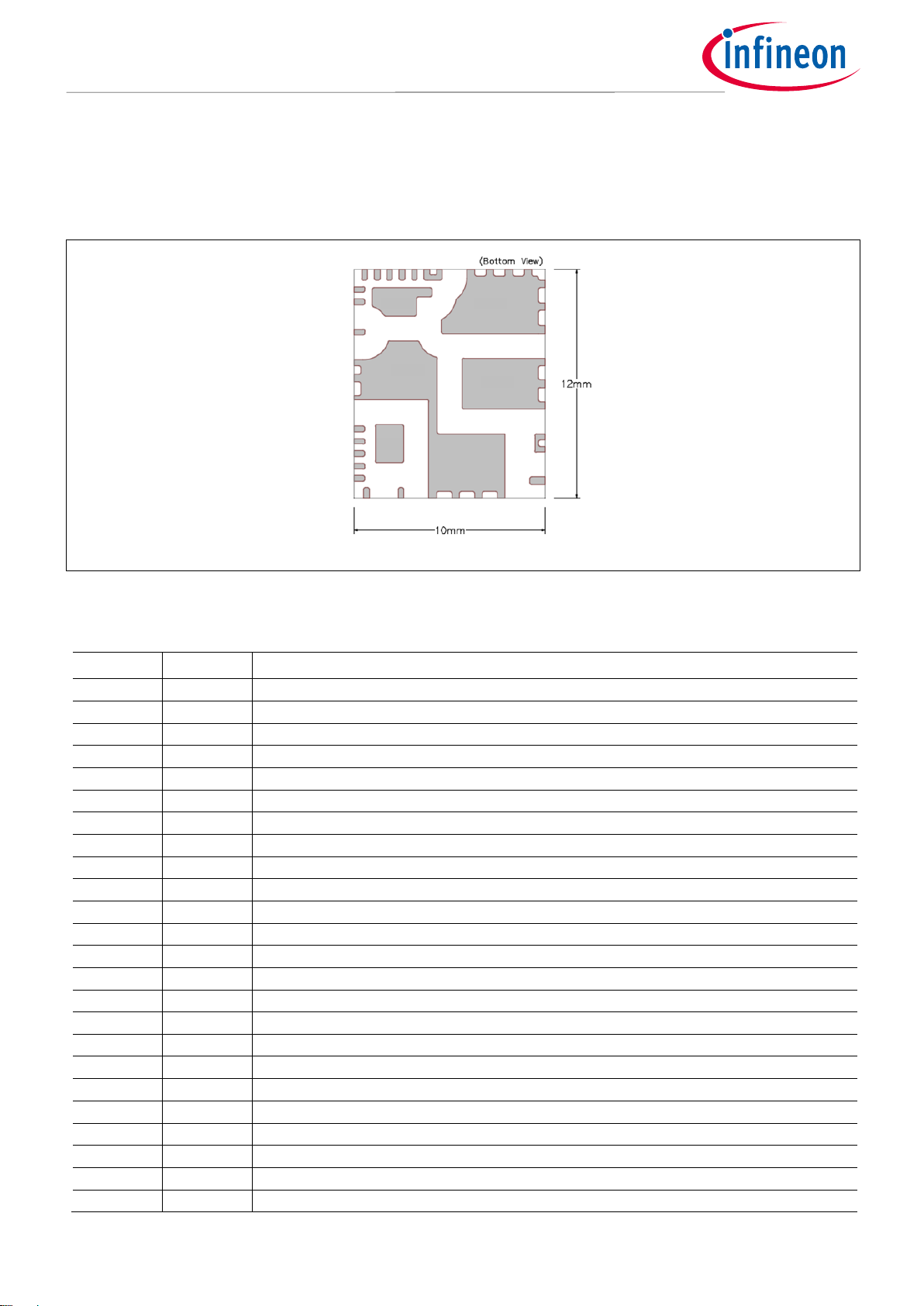

2 Pin Configuration

2.1 Pin Assignment

1

2

3

4

5

6

7

8

9

10

11

12 13 14 15 16 17 18

39

38

19

20 21 22

23

24

25

26

27

28

29

30

31

32333435

3637

Figure 2 Module pinout

Table 2 Pin Assignment

Pin

Name

Description

1

HIN2

Logic Input for High Side Gate Driver (Active High)

2

LIN2

Logic Input for Low Side Gate Driver (Active High)

3

I

TRIP2

Over Current Protection

4

RFE2

Fault Clear, Fault Reporting & Enable

5

COM2

Logic Ground

6-8

V+

DC Bus Voltage Positive

9

VB1

High Side Floating Supply (Bootstrap Cap Connection +)

10

V

DD1

Low Side Control Supply

11

HIN1

Logic Input for High Side Gate Driver (Active High)

12

LIN1

Logic Input for Low Side Gate Driver (Active High)

13

I

TRIP1

Over Current Protection

14

RFE1

Fault Clear, Fault Reporting & Enable

15

COM1

Logic Ground

16

NTC

Negative Temperature Coeffient Thermistor

17-18

VR1

Low Side Source

19-25

VS1

Phase Output

26-28

VS2

Phase Output

29-30

VR2

Low Side Source

31

VS2

Phase Output (Bootstrap Cap Connection -)

32-35

V+

DC Bus Voltage Positive

36

VB2

High Side Floating Supply (Bootstrap Cap Connection +)

37

V

DD2

Low Side Control Supply

38

COM2

Logic Ground

39

COM1

Logic Ground

IM111-X3Q1B

Final Datasheet

Revision 1.0

2019-12-12

Page 5

CIPOS™ Nano

5

2.2 Pin Descriptions

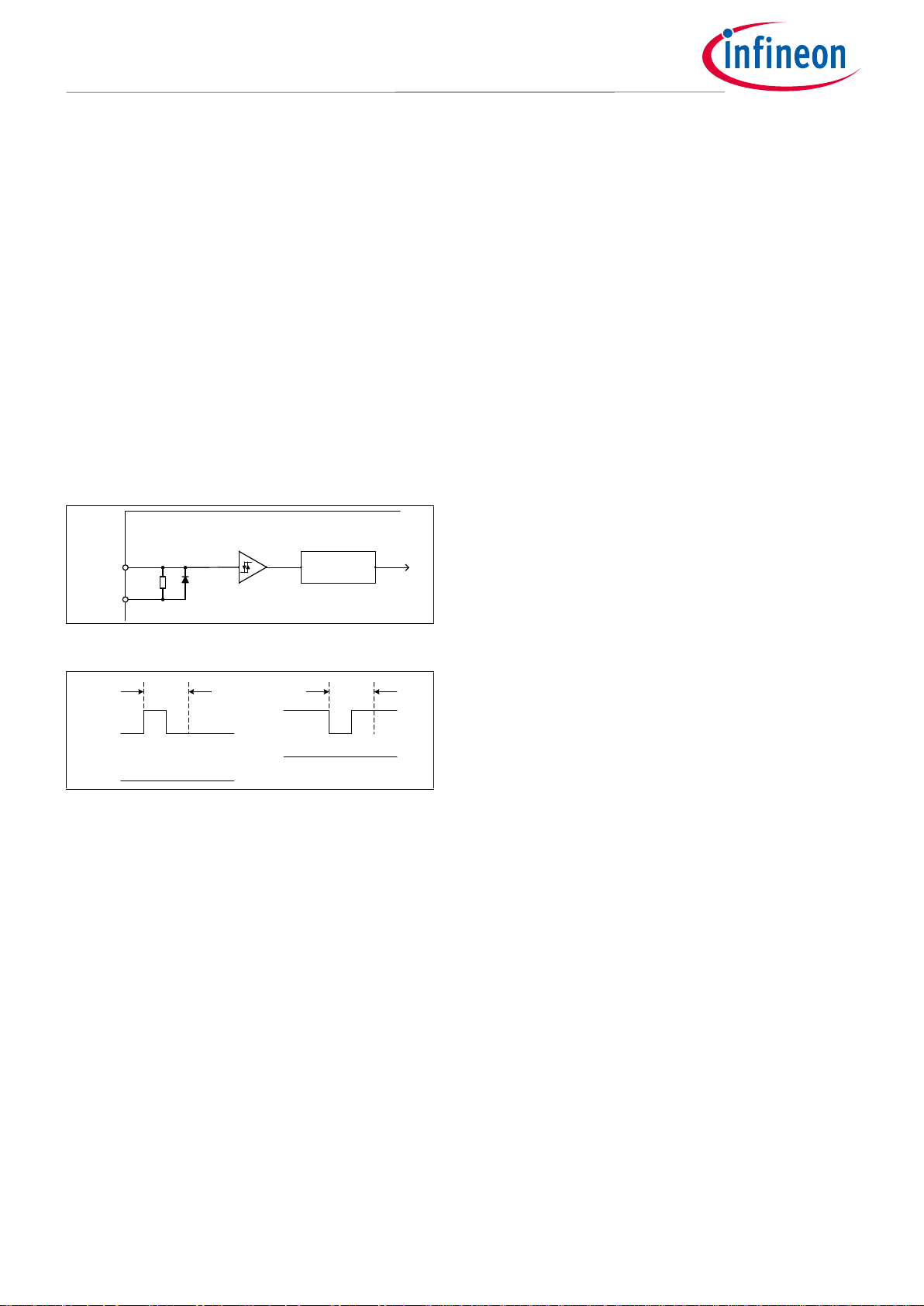

LIN and HIN (Low side and high side control pins)

These pins are positive logic and they are

responsible for the control of the integrated

OptiMOS. The Schmitt-trigger input thresholds of

them are such to guarantee LSTTL and CMOS

compatibility down to 3.3V controller outputs. Pulldown resistor of about 800k is internally provided

to pre-bias inputs during supply start-up and an ESD

diode is provided for pin protection purposes. Input

Schmitt-trigger and noise filter provide beneficial

noise rejection to short input pulses.

The noise filter suppresses control pulses which are

below the filter time t

FILIN

. The filter acts according to

Figure 4.

CIPOS

TM

INPUT NOISE

FILTER

M8.0

Schmitt-Trigger

SWITCH LEVEL

VIH; V

IL

COM

HINx

LINx

Figure 3 Input pin structure

HIN

LIN

HO

LO

low

high

t

FILIN

t

FILIN

a) b)

HIN

LIN

HO

LO

Figure 4 Input filter timing diagram

The integrated gate drive provides additionally a

shoot through prevention capability which avoids

the simultaneous on-state of the high-side and lowside switch of the same inverter phase. A minimum

deadtime insertion of typically 300ns is also

provided by driver IC, in order to reduce crossconduction of the external power switches.

VDD, COM (Low side control supply and reference)

VDD is the control supply and it provides power both

to input logic and to output power stage. Input logic

is referenced to COM ground.

The under-voltage circuit enables the device to

operate at power on when a supply voltage of at

least a typical voltage of V

DDUV+

= 8.9V is present.

The IC shuts down all the gate drivers power

outputs, when the VDD supply voltage is below V

DDUV-

= 7.7V. This prevents the external power switches

from critically low gate voltage levels during onstate and therefore from excessive power

dissipation.

VB and VS (High side supplies)

VB to VS is the high side supply voltage. The high side

circuit can float with respect to COM following the

external high side power device source voltage.

Due to the low power consumption, the floating

driver stage is supplied by integrated bootstrap

circuit.

The under-voltage detection operates with a rising

supply threshold of typical V

BSUV+

= 8.9V and a falling

threshold of V

BSUV-

= 7.7V.

VS provide a high robustness against negative

voltage in respect of COM. This ensures very stable

designs even under rough conditions.

VR (Low side source)

The low side source is available for current

measurements of each phase leg. It is

recommended to keep the connection to pin COM as

short as possible in order to avoid unnecessary

inductive voltage drops.

VS (High side source and low side drain)

This pin is motor input pin.

V+ (Positive bus input voltage)

The high side OptiMOS devices are connected to the

bus voltage. It is noted that the bus voltage does not

exceed 200V.

I

TRIP

(Over current protection)

Analog input for over-current shutdown. When

active, I

TRIP

shuts down outputs and activates RFE

low.

RFE (Fault clear, fault reporting and enable)

Integrated fault reporting function, fault clear timer

and external enable pin. This pin has negative logic

and an open-drain output.

IM111-X3Q1B

Final Datasheet

Revision 1.0

2019-12-12

Page 6

CIPOS™ Nano

6

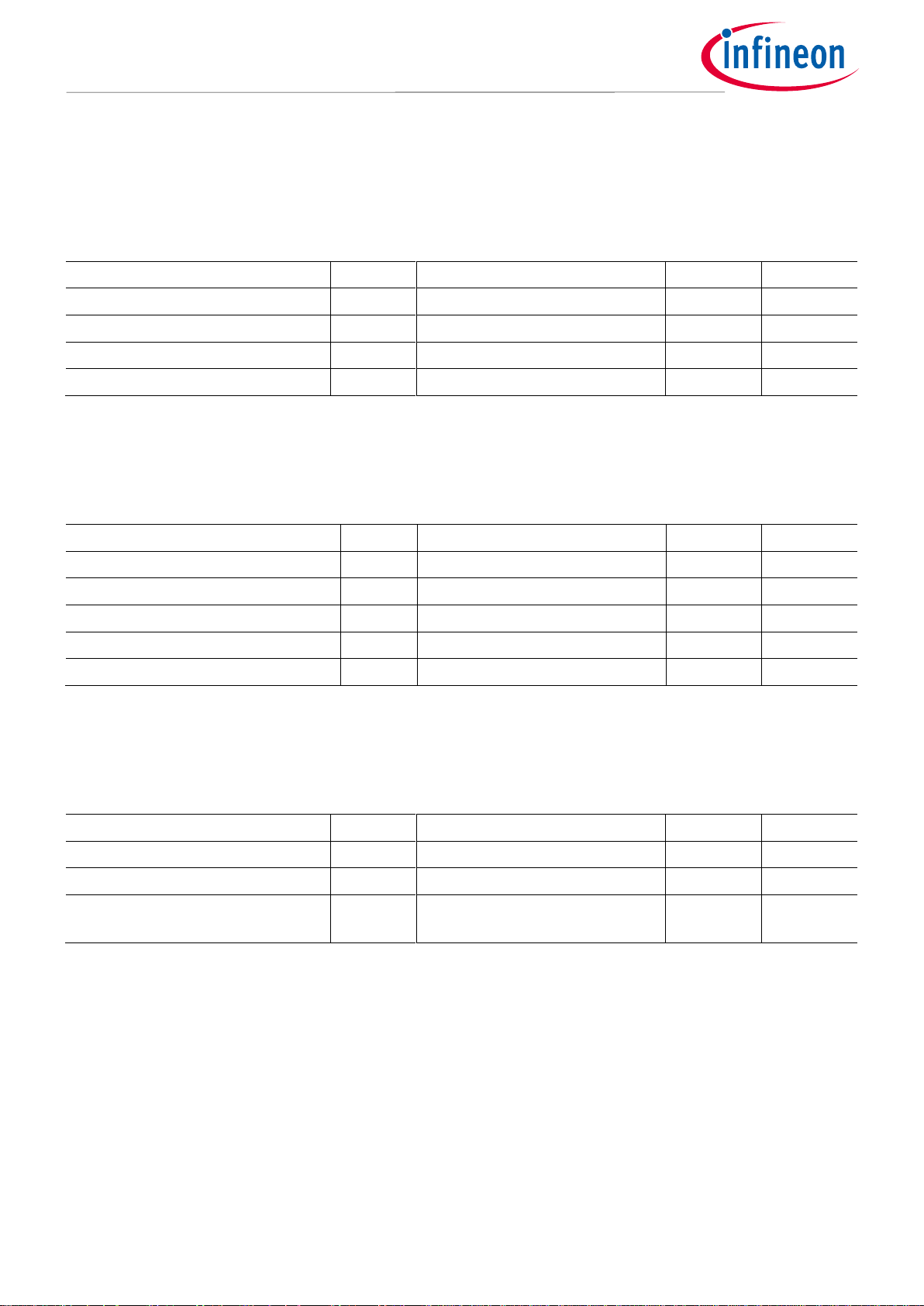

3 Absolute Maximum Ratings

3.1 Module

Table 3

Parameter

Symbol

Condition

Units

Storage temperature

T

STG

-40 ~ 150

°C

Operating case temperature

TC -40 ~ 125

°C

Operating junction temperature

TJ -40 ~ 150

°C

Isolation voltage1

V

ISO

1min, RMS, f = 60Hz

1500

V

1. Characterized, not tested at production

3.2 Inverter

Table 4

Parameter

Symbol

Condition

Units

Max. blocking voltage

V

DSS/VRRM

250

V

Output current based on R

TH(J-C)B

1

IO TC = 25°C, DC

12 A Peak output current

IOP

TC = 25°C, pulsed current

38 A Output current based on R

TH(J-A)

IOA

TA = 25°C, DC

4

A

Peak power dissipation per MOSFET

P TC = 25°C

150

W

1. Limited by wire bonding current capability inside the package

3.3 Control

Table 5

Parameter

Symbol

Condition

Units

Low side control supply voltage

V

DD

-0.3 ~ 20

V

Input voltage LIN, HIN

V

IN

-0.3 ~ V

DD

V

High side floating supply voltage

(VB reference to VS)

V

BS

-0.3 ~ 20

V

IM111-X3Q1B

Final Datasheet

Revision 1.0

2019-12-12

Page 7

CIPOS™ Nano

7

4 Thermal Characteristics

Table 6

Parameter

Symbol

Conditions

Min.

Typ.

Max.

Units

Single MOSFET thermal

resistance, junction-case

(bottom)

R

TH(J-C)B

Measures either high

side or low side

device

-

0.7 - °C/W

Thermal resistance,

junction-ambient

(1)

R

TH(J-A)

- 12 - °C/W

(1) The junction to ambient thermal resistance is simulated based on standard JESD51-5/7 using a FR4

2s2p board with device mounted and power evenly distributed to four power MOSFETs.

IM111-X3Q1B

Final Datasheet

Revision 1.0

2019-12-12

Page 8

CIPOS™ Nano

8

5 Recommended Operating Conditions

Table 7

Parameter

Symbol

Min.

Typ.

Max.

Units

Positive DC bus input voltage

V+ - - 200

V

Low side control supply voltage

VDD

13.5

-

16.5

V

High side floating supply voltage

V

BS

12.5

-

17.5

V

Input voltage

V

IN

0 - 5

V

PWM carrier frequency

F

PWM -

6 - kHz

External dead time between HIN & LIN

DT 1 - - µs

Voltage between COM and VR

V

COMR

-5 - 5

V

Minimum input pulse width

PW

IN(ON)

,

PW

IN(OFF)

0.5 - -

µs

IM111-X3Q1B

Final Datasheet

Revision 1.0

2019-12-12

Page 9

CIPOS™ Nano

9

6 Static Parameters

6.1 Inverter

(VDD-COM) = (VB - VS) = 15 V. TC = 25°C unless otherwise specified.

Table 8

Parameter

Symbol

Conditions

Min.

Typ.

Max.

Units

Drain to Source ON Resistance

R

DS(on)

ID = 1A

-

0.063

0.073

Ω

ID= 1A, TJ = 150℃

-

0.12

-

Ω

Drain source leakage current

I

DSS

VIN = 0V, V+ = 250V

-

15 - µA

VIN = 0V, V+ = 250V, TJ

= 150°C

-

40 - µA

Diode forward voltage

V

F

IF = 1A

-

0.71

-

V

IF = 1A, TJ = 150℃

-

0.48

-

V

6.2 Control

(VDD-COM) = (VB - VS) = 15 V. TC = 25°C unless otherwise specified. The VIN and IIN are referenced to COM and are

applicable to all six channels. The V

DDUV

is referenced to COM. The V

BSUV

is referenced to VS.

Table 9

Parameter

Symbol

Min.

Typ.

Max.

Units

Logic “1” input voltage (LIN, HIN)

V

IN,TH+

2.2 - -

V

Logic “0” input voltage (LIN, HIN)

V

IN,TH-

- - 0.8 V RFE positive going threshold

V

RFE+

- - 2.5

V

RFE negative going threshold

V

RFE-

0.8 - -

V

VDD/V

BS

supply undervoltage, positive going

threshold

V

DD,UV+

,

V

BS,UV+

8

8.9

9.8

V

VDD/VBS supply undervoltage, negative going

threshold

V

DD,UV-

,

V

BS,UV-

6.9

7.7

8.5

V

VDD/VBS supply undervoltage lock-out

hysteresis

V

DDUVH

,

V

BSUVH

-

1.2 - V

Quiescent VBS supply current

I

QBS

-

45

70

µA

Quiescent VDD supply current

I

QCC

1.0

1.7

3.0

mA

Input bias current VIN=4V for LIN,HIN

I

IN+

- 5 20

µA

Input bias current VIN=0V for LIN, HIN

I

IN-

- - 2 µA

Input bias current VIN = 4V for RFE

I

IN,RFE+

- 0 1

µA

Input bias current VIN = 4V for I

TRIP

I

TRIP+

- 5 20

µA

I

TRIP

positive going threshold

V

IT,TH+

0.475

0.500

0.525

V

I

TRIP

negative going threshold

V

IT,TH-

-

0.43

-

V

I

TRIP

input hysteresis

V

IT,HYS

-

0.07

-

V

Bootstrap resistance

R

BS

-

200

-

Ω

RFE low on resistance

R

RFE

-

50

100

Ω

IM111-X3Q1B

Final Datasheet

Revision 1.0

2019-12-12

Page 10

CIPOS™ Nano

10

7 Dynamic Parameters

7.1 Inverter

(VDD-COM) = (VB - VS) = 15 V. TC = 25°C unless otherwise specified.

Table 10

Parameter

Symbol

Conditions

Min.

Typ.

Max.

Units

Input to output turn-on

propagation delay

T

ON

ID = 1A, V+ = 150V

-

0.6

-

µs

Turn-on rise time

T

R

-

11

-

ns

Turn-on switching time

T

C(on)

-

42

-

ns

Input to output turn-off

propagation delay

T

OFF

ID = 1A, V+ = 150V

-

0.7

-

µs

Turn-off fall time

T

F

-

106

-

ns

Turn-off switching time

T

C(off)

-

96

-

ns

RFE low to six switch turn-off

propagation delay

T

EN

V

IN

= 0 or VIN = 5V, VEN =

5V

-

0.44

-

µs

I

TRIP

to six switch turn-off

propagation delay

T

ITRIP

- 920 - ns

Turn-on switching energy

E

ON

ID = 1A, V+ = 150V,

VDD = 15V, L = 9mH

-

-

µJ

Turn-off switching energy

E

OFF

- 5 -

Diode reverse recovery energy

E

REC

-

-

Diode reverse recovery time

T

RR

-

35

-

ns

Turn-on switching energy

E

ON

ID = 1A, V+ = 150V,

VDD = 15V, L = 9mH, TJ

= 150°C

-

-

µJ

Turn-off switching energy

E

OFF

- 5 -

Diode reverse recovery energy

E

REC

-

-

Diode reverse recovery time

T

RR

-

55

-

ns

7.2 Control

(VDD-COM) = (VB - VS) = 15V. TC = 25°C unless otherwise specified.

Table 11

Parameter

Symbol

Conditions

Min.

Typ.

Max.

Units

Input filter time (HIN, LIN, I

TRIP

)

T

FIL,IN

V

IN

= 0 or VIN = 5V

-

300 - ns

Input filter time (RFE)

T

FIL,EN

V

RFE

= 0 or V

RFE

= 5V

-

500 - ns

ITRIP to Fault propagation

delay

T

FLT

V

IN

= 0 or VIN = 5V, V

ITRIP

= 5V

-

660 - ns

Internal injected dead time

T

DT,GD VIN

= 0 or VIN = 5V

-

300 - ns

Matching propagation delay

time (on and off) for same

phase high-side and low-side

M

T

External dead time >

1µs

- - 50

ns

IM111-X3Q1B

12

10

24

13

Final Datasheet

Revision 1.0

2019-12-12

Page 11

CIPOS™ Nano

11

8 Thermistor Characteristics

Table 12

Parameter

Symbol

Conditions

Min.

Typ.

Max.

Units

Resistance

R

25

TC = 25°C, ±5% tolerance

44.65

47

49.35

kΩ

Resistance

R

125

TC = 125°C

1.27

1.39

1.51

kΩ

B-constant

(25/100)

B ±1% tolerance

-

4006

- K Temperature

Range

-20 - 150

°C

Figure 5 Thermistor resistance – temperature curve, for R

EXT

=9.76kΩ, and thermistor resistance

variation with temperature.

0.0

0.5

1.0

1.5

2.0

2.5

3.0

3.5

4.0

0 10 20 30 40 50 60 70 80 90 100 110 120 130 140 150

Thermistor Pin Readout Voltage VTH (V)

Thermistor Temperature TTH (°C)

max

typ

min

T

TH

[℃]

Rmin

[kΩ]

Rtyp

[kΩ]

Rmax

[kΩ]

50

15.448

16.432

17.436

60

10.483

11.194

11.924

70

7.245

7.765

8.302

80

5.092

5.477

5.876

90

3.648

3.937

4.237

100

2.653

2.872

3.101

110

1.957

2.125

2.301

120

1.462

1.592

1.729

125

1.269

1.384

1.505

+3.3V

R

EXT

R

V

TH

IM111-X3Q1B

Final Datasheet

Revision 1.0

2019-12-12

Page 12

CIPOS™ Nano

12

9 Qualification Information

Table 13

Moisture sensitivity level

MSL3

RoHS Compliant

Yes

ESD

CDM

±2kV, Class C3, per ANSI/ESDA/JEDEC JS-002 standard

HBM

±2kV, Class 2, per ANSI/ESDA/JEDEC JESD22-A114F standard

IM111-X3Q1B

Final Datasheet

Revision 1.0

2019-12-12

Page 13

CIPOS™ Nano

13

10 Diagrams & Tables

10.1 Input-Output Logic Table

Gate

Driver

IC

V+

U/V/W

Lo

Ho

HIN

LIN

Figure 6 Module block diagram

Table 14

RFE

I

TRIP

HIN

LIN

U,V,W

1 0 1 0 V+

1 0 0 1 0

1 0 0 0 ‡

1 0 1 1 ‡

1 1 x x ‡

0 x x x ‡

‡ Voltage depends on direction of phase current

10.2 Switching Time Definitions

HIN

LIN

i

D

v

DS

0.9V

2.1V

90%

10%

10%

10%

90%

t

off

t

f

t

on

t

r

t

c(off)

t

c(on)

10%

t

rr

10%

Figure 7 Switching times definition

IM111-X3Q1B

Final Datasheet

Revision 1.0

2019-12-12

Page 14

CIPOS™ Nano

14

11 Application Guide

11.1 Typical Application Schematic

IM111-X3Q1B

VDD1

LIN1

HIN1

VB1

Power

Supply

PWMWL

PWMUH

PWMUL

AIN1

IFB+

IFB-

IFBO

VSS

VDD

VDDCAP

XTAL0

XTAL1

COM1

VBUS

uP

PWMWH

VS1

VDD2

LIN2

HIN2

VB2

COM2

VS2

ITRIP1 ITRIP2

Fault/

Shutdown

RFE2

RFE1

NTC

+

-

Vtemp

U

V

HO

LO

HO

LO

Figure 8 Application schematic

11.2 Performance Charts

Figure 9 Max current SOA

0

1

2

3

4

5

6

7

0 10 20 30 40 50 60 70 80 90 100 110 120 130 140 150

Max Motor Current [Arms]

PCB Ambient Temperature [℃]

F

PWM

=6kHz

F

PWM

=16kHz

IM111-X3Q1B

V+ = 170V, VDD=VBS=15V,

TJ≤150°C, MI=0.8, PF=0.8,

Bipolar SPWM, RTH(J-A)=12°C/W

Final Datasheet

Revision 1.0

2019-12-12

Page 15

CIPOS™ Nano

15

11.3 –Vs Immunity

Figure 10 –Vs immunity

IM111-X3Q1B

Final Datasheet

Revision 1.0

2019-12-12

Page 16

CIPOS™ Nano

16

12 Package Outline

Dimensions in mm

IM111-X3Q1B

Final Datasheet

Revision 1.0

2019-12-12

Page 17

CIPOS™ Nano

17

Note: Exposed tie bars on side of the module.

T1 is internally connected to pin 37

T2 is internally connected to pin 15

T3 is internally connected to pin 12

T4 is internally connected to pin 31

T5 is internally connected to pin 5

IM111-X3Q1B

Final Datasheet

Revision 1.0

2019-12-12

Page 18

CIPOS™ Nano

18

Revision History

Major changes since the last revision

Page or Reference

Description of change

IM111-X3Q1B

Final Datasheet

Revision 1.0

2019-12-12

Page 19

Trademarks

All referenced product or service names and trademarks are the property of their respective owners.

81726 München, Germany

© 2019 Infineon Technologies AG.

All Rights Reserved.

Do you have a question about this

document?

Email: erratum@infineon.com

Document reference

IMPORTANT NOTICE

The information given in this document shall in no

event be regarded as a guarantee of conditions or

characteristics (“Beschaffenheitsgarantie”) .

With respect to any examples, hints or any typical

values stated herein and/or any information

regarding the application of the product, Infineon

Technologies hereby disclaims any and all

warranties and liabilities of any kind, including

without limitation warranties of non-infringement of

intellectual property rights of any third party.

In addition, any information given in this document

is subject to customer’s compliance with its

obligations stated in this document and any

applicable legal requirements, norms and standards

concerning customer’s products and any use of the

product of Infineon Technologies in customer’s

applications.

The data contained in this document is exclusively

intended for technically trained staff. It is the

responsibility of customer’s technical departments

to evaluate the suitability of the product for the

intended application and the completeness of the

product information given in this document with

respect to such application.

For further information on the product, technology,

delivery terms and conditions and prices please

contact your nearest Infineon Technologies office

(www.infineon.com).

Please note that this product is not qualified

according to the AEC Q100 or AEC Q101 documents

of the Automotive Electronics Council.

WARNINGS

Due to technical requirements products may contain

dangerous substances. For information on the types

in question please contact your nearest Infineon

Technologies office.

Except as otherwise explicitly approved by Infineon

Technologies in a written document signed by

authorized representatives of Infineon

Technologies, Infineon Technologies’ products may

not be used in any applications where a failure of the

product or any consequences of the use thereof can

reasonably be expected to result in personal injury.

Edition 2019-12-12

Published by

Infineon Technologies AG

Loading...

Loading...