CTLST CAT28F020TRI-90T, CAT28F020TRI-70T, CAT28F020TRI-12T, CAT28F020TRA-90T, CAT28F020TRA-70T Datasheet

...

|

|

|

|

|

|

CAT28F020 |

|

Licensed Intel |

2 Megabit CMOS Flash Memory |

|

second source |

|

|

FEATURES

■Fast Read Access Time: 70/90/120 ns

■Low Power CMOS Dissipation:

–Active: 30 mA max (CMOS/TTL levels)

–Standby: 1 mA max (TTL levels)

–Standby: 100μA max (CMOS levels)

■High Speed Programming:

–10μs per byte

–4 Seconds Typical Chip Program

■0.5 Seconds Typical Chip-Erase

■12.0V ± 5% Programming and Erase Voltage

■Commercial, Industrial and Automotive Temperature Ranges

■Stop Timer for Program/Erase

■On-Chip Address and Data Latches

■JEDEC Standard Pinouts:

–32-pin DIP

–32-pin PLCC

–32-pin TSOP (8 x 20)

■100,000 Program/Erase Cycles

■10 Year Data Retention

■Electronic Signature

DESCRIPTION

The CAT28F020 is a high speed 256K x 8-bit electrically erasable and reprogrammable Flash memory ideally suited for applications requiring in-system or after-sale code updates. Electrical erasure of the full memory contents is achieved typically within 0.5 second.

It is pin and Read timing compatible with standard EPROM and E2PROM devices. Programming and Erase are performed through an operation and verify algorithm. The instructions are input via the I/O bus,

using a two write cycle scheme. Address and Data are latched to free the I/O bus and address bus during the write operation.

The CAT28F020 is manufactured using Catalyst’s advanced CMOS floating gate technology. It is designed to endure 100,000 program/erase cycles and has a data retention of 10 years. The device is available in JEDEC approved 32-pin plastic DIP, 32-pin PLCC or 32-pin TSOP packages.

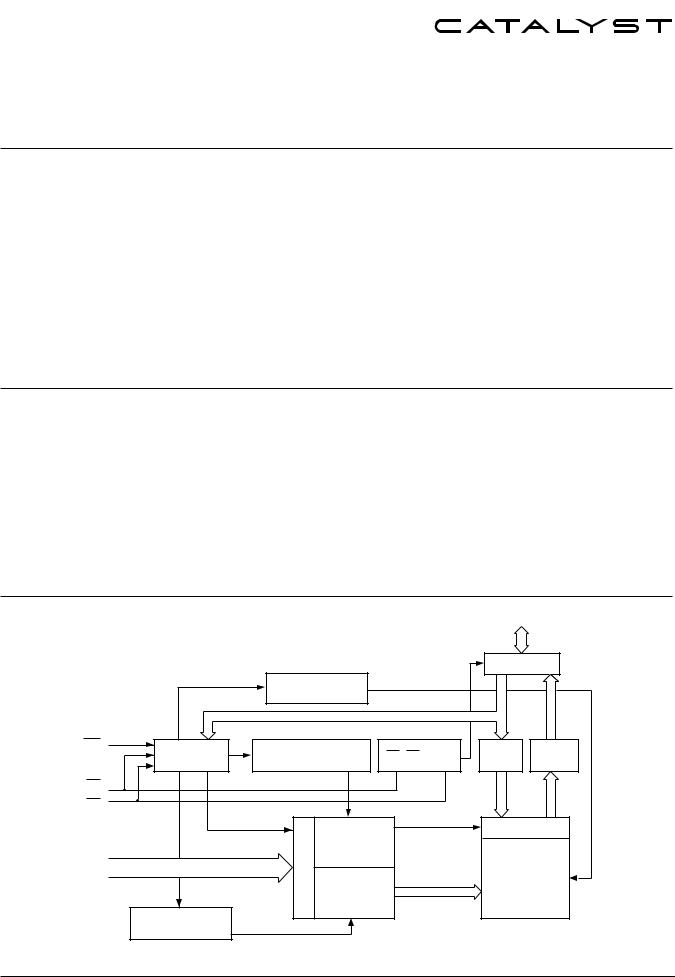

BLOCK DIAGRAM |

|

|

|

I/O0–I/O7 |

||

|

|

|

|

|

I/O BUFFERS |

|

|

|

ERASE VOLTAGE |

|

|

|

|

|

|

SWITCH |

|

|

|

|

WE |

COMMAND |

PROGRAM VOLTAGE |

CE, OE LOGIC |

DATA |

SENSE |

|

|

REGISTER |

SWITCH |

LATCH |

AMP |

||

|

|

|||||

CE |

|

|

|

|

|

|

OE |

|

LATCH |

|

|

|

|

|

|

|

|

Y-GATING |

||

|

|

|

|

|

||

|

|

ADDRESS |

Y-DECODER |

|

|

|

A0–A17 |

|

|

|

2,097,152 BIT |

||

|

|

|

X-DECODER |

MEMORY |

||

|

|

|

ARRAY |

|||

|

VOLTAGE VERIFY |

|

|

|

|

|

|

SWITCH |

|

|

|

|

|

5115 FHD F02

© 1998 by Catalyst Semiconductor, Inc. |

Doc. No. 25037-00 2/98 F-1 |

Characteristics subject to change without notice |

1 |

CAT28F020

PIN CONFIGURATION

DIP Package (P)

VPP |

1 |

32 |

VCC |

|

A16 |

2 |

31 |

WE |

|

A15 |

3 |

30 |

A17 |

|

A12 |

4 |

29 |

A14 |

A7 |

A7 |

5 |

28 |

A13 |

A6 |

A6 |

6 |

27 |

A8 |

A5 |

A5 |

7 |

26 |

A9 |

A4 |

A4 |

8 |

25 |

A11 |

A3 |

A3 |

9 |

24 |

OE |

A2 |

A2 |

10 |

23 |

A10 |

A1 |

A1 |

11 |

22 |

CE |

A0 |

A0 |

12 |

21 |

I/O7 |

I/O |

I/O0 |

13 |

20 |

I/O6 |

0 |

|

||||

I/O1 |

14 |

19 |

I/O5 |

|

I/O2 |

15 |

18 |

I/O4 |

|

VSS |

16 |

17 |

I/O3 |

|

PIN FUNCTIONS

PLCC Package (N) |

|

|

Pin Name |

Type |

Function |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A |

A |

A |

V |

V |

WE |

A |

|

|

|

A0–A17 |

Input |

Address Inputs for |

||

12 |

15 |

16 |

PP |

CC |

|

17 |

|

|

|

|||||

4 |

3 |

2 |

1 |

32 31 30 |

|

|

|

|

|

|

|

memory addressing |

||

|

|

|

|

|

|

|

|

|||||||

|

|

|

I/O0–I/O7 |

I/O |

Data Input/Output |

|||||||||

5 |

|

|

|

|

|

29 |

A14 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

6 |

|

|

|

|

|

28 |

|

CE |

Input |

Chip Enable |

||||

|

|

|

|

|

A13 |

|

||||||||

7 |

|

|

|

|

|

27 |

|

|

|

|

|

|

||

|

|

|

|

|

A8 |

|

|

|

|

|

|

|||

|

|

|

|

|

|

OE |

Input |

Output Enable |

||||||

8 |

|

|

|

|

|

26 |

|

|||||||

|

|

|

|

|

A9 |

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

Input |

Write Enable |

||||

9 |

|

|

|

|

|

25 |

A11 |

|

WE |

|

||||

10 |

|

|

|

|

|

24 |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

OE |

|

VCC |

|

Voltage Supply |

|||||

11 |

|

|

|

|

|

23 |

A10 |

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

VSS |

|

Ground |

||||||

12 |

|

|

|

|

|

22 |

|

|

|

|

||||

|

|

|

|

|

CE |

|

||||||||

13 |

|

|

|

|

|

21 |

I/O7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

VPP |

|

Program/Erase |

||||||

14 15 16 17 18 19 20 |

|

|

||||||||||||

|

|

|

|

|

|

|

Voltage Supply |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

2 |

SS |

3 |

4 |

5 |

6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

I/O |

I/O |

V |

I/O |

I/O |

I/O |

I/O |

|

|

|

|

|

|

|

|

5115 FHD F01

TSOP Package (Standard Pinout) (T)

A11 |

|

|

1 |

32 |

|

|

OE |

||||

|

|

|

|

||||||||

|

A9 |

|

2 |

31 |

|

|

A10 |

||||

|

|

|

|||||||||

|

A8 |

|

|

3 |

30 |

|

|

|

CE |

|

|

|

|

|

|

||||||||

A13 |

|

4 |

29 |

|

|

I/O7 |

|||||

|

|

|

|||||||||

A14 |

|

5 |

28 |

|

|

I/O6 |

|||||

|

|

|

|||||||||

A17 |

|

6 |

27 |

|

|

I/O5 |

|||||

|

|

|

|||||||||

|

WE |

|

|

|

7 |

26 |

|

|

I/O4 |

||

|

|

|

|||||||||

VCC |

|

8 |

25 |

|

|

I/O3 |

|||||

|

|

|

|||||||||

VPP |

|

9 |

24 |

|

|

VSS |

|||||

|

|

|

|||||||||

A16 |

|

10 |

23 |

|

|

I/O2 |

|||||

|

|

|

|||||||||

A15 |

|

11 |

22 |

|

|

I/O1 |

|||||

|

|

|

|||||||||

A12 |

|

12 |

21 |

|

|

I/O0 |

|||||

|

|

|

|||||||||

|

A7 |

|

13 |

20 |

|

|

A0 |

||||

|

|

|

|||||||||

|

A6 |

|

14 |

19 |

|

|

A1 |

||||

|

|

|

|||||||||

|

A5 |

|

15 |

18 |

|

|

A2 |

||||

|

|

|

|||||||||

|

A4 |

|

16 |

17 |

|

|

A3 |

||||

|

|

|

|||||||||

TSOP Package (Reverse Pinout) (TR)

OE |

|

|

1 |

32 |

|

|

A11 |

||||

|

|

|

|||||||||

A10 |

|

2 |

31 |

|

|

A9 |

|||||

|

|

|

|||||||||

|

CE |

|

|

|

3 |

30 |

|

|

A8 |

||

|

|

|

|||||||||

I/O7 |

|

4 |

29 |

|

|

A13 |

|||||

|

|

|

|||||||||

I/O6 |

|

5 |

28 |

|

|

A14 |

|||||

|

|

|

|||||||||

I/O5 |

|

6 |

27 |

|

|

A17 |

|||||

|

|

|

|||||||||

I/O4 |

|

|

7 |

26 |

|

|

|

WE |

|

||

|

|

|

|||||||||

I/O3 |

|

8 |

25 |

|

|

VCC |

|||||

|

|

|

|||||||||

VSS |

|

|

9 |

24 |

|

|

VPP |

||||

|

|

|

|

||||||||

I/O2 |

|

10 |

23 |

|

|

A16 |

|||||

|

|

|

|||||||||

I/O1 |

|

11 |

22 |

|

|

A15 |

|||||

|

|

|

|||||||||

I/O0 |

|

12 |

21 |

|

|

A12 |

|||||

|

|

|

|||||||||

|

A0 |

|

13 |

20 |

|

|

A7 |

||||

|

|

|

|||||||||

|

A1 |

|

14 |

19 |

|

|

A6 |

||||

|

|

|

|||||||||

|

A2 |

|

15 |

18 |

|

|

A5 |

||||

|

|

|

|||||||||

|

A3 |

|

16 |

17 |

|

|

A4 |

||||

|

|

|

|||||||||

5115 FHD F14

Doc. No. 25037-00 2/98 F-1 |

2 |

|

CAT28F020

ABSOLUTE MAXIMUM RATINGS* |

*COMMENT |

Temperature Under Bias ................... |

–55°C to +95°C |

|

Storage Temperature ....................... |

–65°C to +150°C |

|

Voltage on Any Pin with |

|

|

Respect to Ground(1) ........... |

–2.0V to +VCC + 2.0V |

|

Voltage on Pin A9 with |

|

|

Respect to Ground(1) ................... |

–2.0V to +13.5V |

|

VPP with Respect to Ground |

|

|

during Program/Erase(1) .............. |

–2.0V to +14.0V |

|

VCC with Respect to Ground(1) ............ |

|

–2.0V to +7.0V |

Package Power Dissipation |

|

|

Capability (TA = 25°C) .................................. |

|

1.0 W |

Lead Soldering Temperature (10 secs) |

............ 300°C |

|

Output Short Circuit Current(2) ........................ |

|

100 mA |

RELIABILITY CHARACTERISTICS

Stresses above those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions outside of those listed in the operational sections of this specification is not implied. Exposure to any absolute maximum rating for extended periods may affect device performance and reliability.

Symbol |

Parameter |

Min. |

Max. |

Units |

Test Method |

|

|

|

|

|

|

NEND(3) |

Endurance |

100K |

|

Cycles/Byte |

MIL-STD-883, Test Method 1033 |

TDR(3) |

Data Retention |

10 |

|

Years |

MIL-STD-883, Test Method 1008 |

VZAP(3) |

ESD Susceptibility |

2000 |

|

Volts |

MIL-STD-883, Test Method 3015 |

ILTH(3)(4) |

Latch-Up |

100 |

|

mA |

JEDEC Standard 17 |

CAPACITANCE TA = 25°C, f = 1.0 MHz

|

|

|

Limits |

|

|

|

|

|

|

|

|

|

|

Symbol |

Test |

Min |

|

Max. |

Units |

Conditions |

|

|

|

|

|

|

|

CIN(3) |

Input Pin Capacitance |

|

|

6 |

pF |

VIN = 0V |

COUT(3) |

Output Pin Capacitance |

|

|

10 |

pF |

VOUT = 0V |

CVPP(3) |

VPP Supply Capacitance |

|

|

25 |

pF |

VPP = 0V |

Note:

(1)The minimum DC input voltage is –0.5V. During transitions, inputs may undershoot to –2.0V for periods of less than 20 ns. Maximum DC voltage on output pins is VCC +0.5V, which may overshoot to VCC + 2.0V for periods of less than 20ns.

(2)Output shorted for no more than one second. No more than one output shorted at a time.

(3)This parameter is tested initially and after a design or process change that affects the parameter.

(4)Latch-up protection is provided for stresses up to 100 mA on address and data pins from –1V to VCC +1V.

Doc. No. 25037-00 2/98 F-1

3

CAT28F020

D.C. OPERATING CHARACTERISTICS

VCC = +5V ±10%, unless otherwise specified.

|

|

|

Limits |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Symbol |

Parameter |

Min. |

Max. |

Unit |

|

|

|

Test Conditions |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ILI |

Input Leakage Current |

|

±1 |

μA |

VIN = VCC or VSS |

||||||||

|

|

|

|

|

VCC = 5.5V, |

OE |

= VIH |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ILO |

Output Leakage Current |

|

±1 |

μA |

VOUT = VCC or VSS, |

||||||||

|

|

|

|

|

VCC = 5.5V, |

OE |

|

= VIH |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ISB1 |

VCC Standby Current CMOS |

|

100 |

μA |

|

|

|

= VCC ±0.5V, |

|||||

|

CE |

||||||||||||

|

|

|

|

|

VCC = 5.5V |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ISB2 |

VCC Standby Current TTL |

|

1 |

mA |

|

|

= VIH, VCC = 5.5V |

||||||

|

CE |

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ICC1 |

VCC Active Read Current |

|

30 |

mA |

VCC = 5.5V, |

|

|

|

= VIL, |

||||

|

CE |

||||||||||||

|

|

|

|

|

IOUT = 0mA, f = 6 MHz |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ICC2(1) |

VCC Programming Current |

|

15 |

mA |

VCC = 5.5V, |

||||||||

|

|

|

|

|

Programming in Progress |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ICC3(1) |

VCC Erase Current |

|

15 |

mA |

VCC = 5.5V, |

||||||||

|

|

|

|

|

Erasure in Progress |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ICC4(1) |

VCC Prog./Erase Verify Current |

|

15 |

mA |

VCC = 5.5V, Program or |

||||||||

|

|

|

|

|

Erase Verify in Progress |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IPPS |

VPP Standby Current |

|

±10 |

μA |

VPP = VPPL |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IPP1 |

VPP Read Current |

|

200 |

μA |

VPP = VPPH |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IPP2(1) |

VPP Programming Current |

|

30 |

mA |

VPP = VPPH, |

||||||||

|

|

|

|

|

Programming in Progress |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IPP3(1) |

VPP Erase Current |

|

30 |

mA |

VPP = VPPH, |

||||||||

|

|

|

|

|

Erasure in Progress |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IPP4(1) |

VPP Prog./Erase Verify Current |

|

5 |

mA |

VPP = VPPH, Program or |

||||||||

|

|

|

|

|

Erase Verify in Progress |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VIL |

Input Low Level TTL |

–0.5 |

0.8 |

V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VILC |

Input Low Level CMOS |

–0.5 |

0.8 |

V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VOL |

Output Low Level |

|

0.45 |

V |

IOL = 5.8mA, VCC = 4.5V |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VIH |

Input High Level TTL |

2 |

VCC+0.5 |

V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VIHC |

Input High Level CMOS |

VCC*0.7 |

VCC+0.5 |

V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VOH1 |

Output High Level TTL |

2.4 |

|

V |

IOH = –2.5mA, VCC = 4.5V |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VOH2 |

Output High Level CMOS |

VCC–0.4 |

|

V |

IOH = –400μA, VCC = 4.5V |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VID |

A9 Signature Voltage |

11.4 |

13 |

V |

A9 = VID |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IID(1) |

A9 Signature Current |

|

200 |

μA |

A9 = VID |

||||||||

VLO |

VCC Erase/Prog. Lockout Voltage |

2.5 |

|

V |

|

|

|

|

|

|

|

|

|

Note:

(1) This parameter is tested initially and after a design or process change that affects the parameter.

Doc. No. 25037-00 2/98 F-1 |

4 |

|

|

|

|

|

|

CAT28F020 |

SUPPLY CHARACTERISTICS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Limits |

|

|

|

|

|

|

|

|

Symbol |

Parameter |

Min |

|

Max. |

Unit |

|

|

|

|

|

|

VCC |

VCC Supply Voltage |

4.5 |

|

5.5 |

V |

VPPL |

VPP During Read Operations |

0 |

|

6.5 |

V |

VPPH |

VPP During Read/Erase/Program |

11.4 |

|

12.6 |

V |

A.C. CHARACTERISTICS, Read Operation

VCC = +5V ±10%, unless otherwise specified.

|

JEDEC |

Standard |

|

|

28F020-70(8) |

28F020-90(7) |

28F020-12(7) |

|

|

|||||||||||||||||

|

Symbol |

Symbol |

Parameter |

Min. |

Max. |

Min. |

Max. |

Min. |

Max. |

Unit |

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tAVAV |

|

tRC |

Read Cycle Time |

70 |

|

90 |

|

|

|

|

|

120 |

|

|

ns |

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tELQV |

|

tCE |

CE Access Time |

|

|

70 |

|

|

90 |

|

|

|

|

|

120 |

ns |

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tAVQV |

|

tACC |

Address Access Time |

|

|

70 |

|

|

90 |

|

|

|

|

|

120 |

ns |

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tGLQV |

|

tOE |

OE Access Time |

|

|

28 |

|

|

35 |

|

|

|

|

|

50 |

ns |

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tAXQX |

|

tOH |

Output Hold from Address OE/CE Change |

0 |

|

0 |

|

|

|

|

|

0 |

|

|

ns |

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tGLQX |

|

tOLZ(1)(6) |

OE to Output in Low-Z |

0 |

|

0 |

|

|

|

|

|

0 |

|

|

|

ns |

|

||||||||

|

tELQX |

|

tLZ(1)(6) |

CE to Output in Low-Z |

0 |

|

0 |

|

|

|

|

|

0 |

|

|

ns |

|

|||||||||

|

tGHQZ |

|

tDF(1)(2) |

OE High to Output High-Z |

|

|

20 |

|

|

30 |

|

|

|

|

|

30 |

ns |

|

||||||||

|

tEHQZ |

|

tDF(1)(2) |

CE High to Output High-Z |

|

|

30 |

|

|

40 |

|

|

|

|

|

40 |

ns |

|

||||||||

|

|

(1) |

|

|

|

|

|

|

|

6 |

|

6 |

|

|

|

|

|

|

|

|

|

|

μ |

|

||

|

tWHGL |

- |

|

|

|

|

Write Recovery Time Before Read |

|

|

|

|

|

|

|

|

6 |

|

|

s |

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

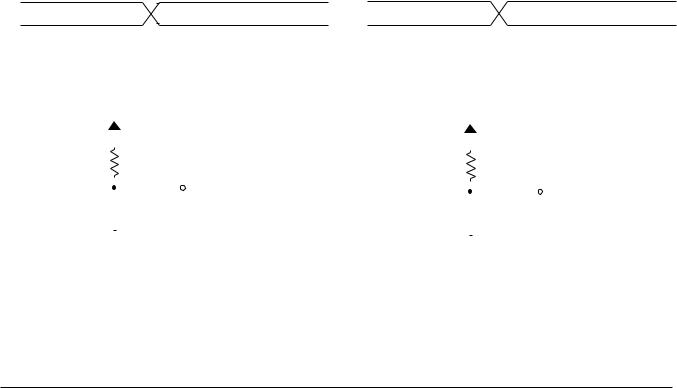

Figure 1. A.C. Testing Input/Output Waveform(3)(4)(5) Figure 2. Highspeed A.C. Testing Input/Output |

|||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

Waveform(3)(4)(5) |

|

|

|||||||||||

|

2.4 V |

|

|

|

|

|

|

2.0 V |

3.0 V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

INPUT PULSE LEVELS |

|

REFERENCE POINTS |

|

|

INPUT PULSE LEVELS |

|

|

1.5 V |

REFERENCE POINTS |

|||||||||||||||

|

|

|

|

|

|

|

||||||||||||||||||||

0.45 V |

|

|

|

|

|

|

0.8 V |

0.0 V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

Testing Load Circuit (example) |

|

Testing Load Circuit (example) |

|

|

|||||||||||||||||||||

|

|

|

1.3V |

|

|

|

|

|

|

|

1.3V |

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

1N914 |

|

|

|

|

|

|

|

|

|

|

1N914 |

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

3.3K |

|

|

|

|

|

|

|

|

|

|

3.3K |

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

DEVICE |

|

|

|

|

|

|

OUT |

|

DEVICE |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

UNDER |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

OUT |

||||||

|

|

|

|

|

|

|

|

UNDER |

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

TEST |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

CL = 100 pF |

|

|

TEST |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CL = 30 pF |

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

CL INCLUDES JIG CAPACITANCE |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CL INCLUDES JIG CAPACITANCE |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

Note:

(1)This parameter is tested initially and after a design or process change that affects the parameter.

(2)Output floating (High-Z) is defined as the state where the external data line is no longer driven by the output buffer.

(3)Input Rise and Fall Times (10% to 90%) < 10 ns.

(4)Input Pulse Levels = 0.45V and 2.4V. For High Speed Input Pulse Levels 0.0V and 3.0V.

(5)Input and Output Timing Reference = 0.8V and 2.0V. For High Speed Input and Output Timing Reference = 1.5V.

(6)Low-Z is defined as the state where the external data may be driven by the output buffer but may not be valid.

(7)For load and reference points, see Fig. 1

(8)For load and reference points, see Fig. 2

Doc. No. 25037-00 2/98 F-1

5

Loading...

Loading...