CTLST CAT24WC256KA-3TE13, CAT24WC256KA-1.8TE13, CAT24WC256K-TE13, CAT24WC256K-3TE13, CAT24WC256K-1.8TE13 Datasheet

...

Preliminary

CAT24WC256

256K-Bit I2C Serial CMOS E2PROM

FEATURES

■1MHz I2C Bus Compatible*

■1.8 to 6 Volt Operation

■Low Power CMOS Technology

■64-Byte Page Write Buffer

■Self-Timed Write Cycle with Auto-Clear

■Commercial, Industrial and Automotive Temperature Ranges

■ Write Protect Feature

– Entire Array Protected When WP at V

IH

■100,000 Program/Erase Cycles

■100 Year Data Retention

■8-Pin DIP or 8-Pin SOIC

DESCRIPTION

The CAT24WC256 is a 256K-bit Serial CMOS E2PROM internally organized as 32,768 words of 8 bits each. Catalyst’s advanced CMOS technology substantially reduces device power requirements. The

CAT24WC256 features a 64-byte page write buffer. The device operates via the I2C bus serial interface and is available in 8-pin DIP or 8-pin SOIC packages.

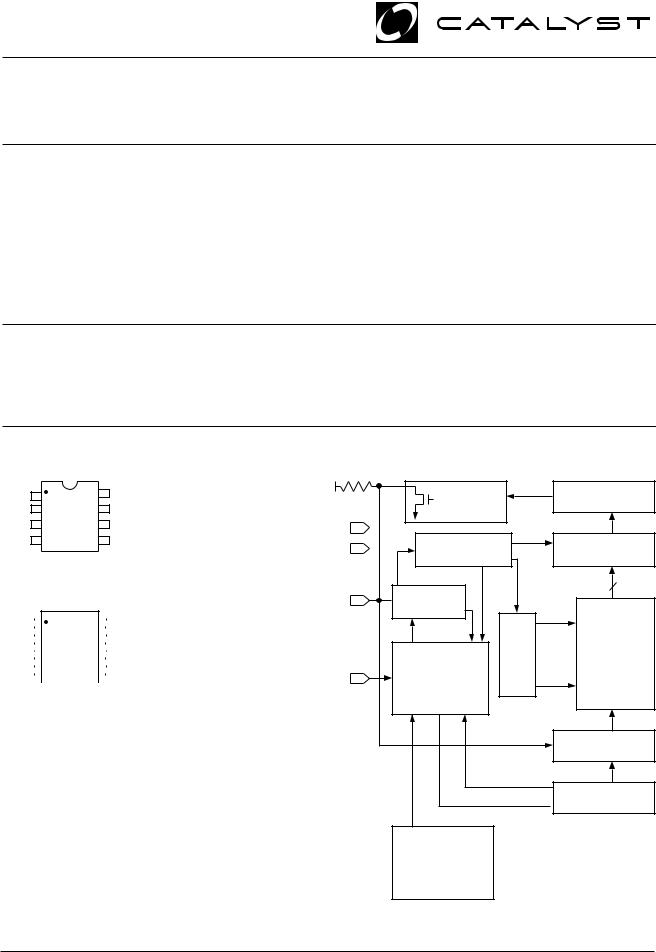

PIN CONFIGURATION |

BLOCK DIAGRAM |

DIP Package (P) |

EXTERNAL LOAD |

A0 |

1 |

8 |

VCC |

A1 |

2 |

7 |

WP |

NC |

3 |

6 |

SCL |

VSS |

4 |

5 |

SDA |

SOIC Package (K)

A0 |

|

|

|

1 |

8 |

|

|

|

VCC |

|

|

|

|

|

|||||

|

|

|

2 |

7 |

|

|

|

||

A1 |

|

|

|

|

|

|

WP |

||

|

|

|

3 |

6 |

|

|

|

||

NC |

|

|

|

|

|

|

SCL |

||

|

|

|

4 |

5 |

|

|

|

|

|

VSS |

|

|

|

|

|

|

SDA |

||

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

24WC256 F01 |

PIN FUNCTIONS |

|||

|

|

|

|

Pin Name |

|

Function |

|

|

|

||

A0, A1 |

Address Inputs |

||

|

|

||

SDA |

Serial Data/Address |

||

|

|

||

SCL |

Serial Clock |

||

|

|

||

WP |

Write Protect |

||

|

|

||

VCC |

+1.8V to +6.0V Power Supply |

||

|

|

||

VSS |

Ground |

||

|

|

||

NC |

No Connect |

||

|

|

|

|

|

DOUT |

|

SENSE AMPS |

|

SHIFT REGISTERS |

||

|

ACK |

||

|

|

|

|

VCC |

|

|

|

VSS |

WORD ADDRESS |

|

COLUMN |

BUFFERS |

|

DECODERS |

|

|

|

||

|

|

|

512 |

SDA |

START/STOP |

|

|

LOGIC |

|

|

|

|

|

|

|

|

XDEC |

512 |

E2PROM |

|

512X512 |

||

|

|

|

|

WP |

CONTROL |

|

|

LOGIC |

|

|

|

|

|

|

|

|

|

DATA IN STORAGE |

|

HIGH VOLTAGE/

TIMING CONTROL

TIMING CONTROL

SCL  STATE COUNTERS

STATE COUNTERS

A0  SLAVE

SLAVE

A1  ADDRESS

ADDRESS

COMPARATORS

24WC256 F02

* Catalyst Semiconductor is licensed by Philips Corporation to carry the I2C Bus Protocol.

© 1998 by Catalyst Semiconductor, Inc. |

Doc. No. 25061-00 6/99 S-1 |

Characteristics subject to change without notice |

1 |

CAT24WC256 |

Preliminary |

ABSOLUTE MAXIMUM RATINGS* |

*COMMENT |

Temperature Under Bias ................. |

–55°C to +125°C |

|

Storage Temperature ....................... |

–65°C to +150°C |

|

Voltage on Any Pin with |

|

|

Respect to Ground(1) ........... |

–2.0V to +VCC + 2.0V |

|

VCC with Respect to Ground ............... |

|

–2.0V to +7.0V |

Package Power Dissipation |

|

|

Capability (Ta = 25°C) ................................... |

|

1.0W |

Lead Soldering Temperature (10 secs) |

............ 300°C |

|

Output Short Circuit Current(2) ........................ |

|

100mA |

Stresses above those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions outside of those listed in the operational sections of this specification is not implied. Exposure to any absolute maximum rating for extended periods may affect device performance and reliability.

RELIABILITY CHARACTERISTICS

Symbol |

Parameter |

Min. |

Max. |

Units |

Reference Test Method |

|

|

|

|

|

|

NEND(3) |

Endurance |

100,000 |

|

Cycles/Byte |

MIL-STD-883, Test Method 1033 |

TDR(3) |

Data Retention |

100 |

|

Years |

MIL-STD-883, Test Method 1008 |

VZAP(3) |

ESD Susceptibility |

2000 |

|

Volts |

MIL-STD-883, Test Method 3015 |

ILTH(3)(4) |

Latch-up |

100 |

|

mA |

JEDEC Standard 17 |

D.C. OPERATING CHARACTERISTICS

VCC = +1.8V to +6.0V, unless otherwise specified.

|

|

|

Limits |

|

|

|

|

|

|

|

|

|

|

|

|

Symbol |

Parameter |

Min. |

|

Typ. |

Max. |

Units |

Test Conditions |

|

|

|

|

|

|

|

|

ICC1 |

Power Supply Current - Read |

|

|

|

1 |

mA |

fSCL = 100 KHz |

|

|

|

|

|

|

|

VCC=5V |

ICC2 |

Power Supply Current - Write |

|

|

|

3 |

mA |

fSCL = 100KHz |

|

|

|

|

|

|

|

VCC=5V |

ISB(5) |

Standby Current |

|

|

|

0 |

μA |

VIN = GND or VCC |

|

|

|

|

|

|

|

VCC=5V |

ILI |

Input Leakage Current |

|

|

|

1 |

μA |

VIN = GND to VCC |

ILO |

Output Leakage Current |

|

|

|

1 |

μA |

VOUT = GND to VCC |

VIL |

Input Low Voltage |

–1 |

|

|

VCC x 0.3 |

V |

|

VIH |

Input High Voltage |

VCC x 0.7 |

|

|

VCC + 0.5 |

V |

|

VOL1 |

Output Low Voltage (VCC = +3.0V) |

|

|

|

0.4 |

V |

IOL = 3.0 mA |

VOL2 |

Output Low Voltage (VCC = +1.8V) |

|

|

|

0.5 |

V |

IOL = 1.5 mA |

CAPACITANCE TA = 25°C, f = 1.0 MHz, VCC = 5V

Symbol |

Test |

Max. |

Units |

Conditions |

|

|

|

|

|

CI/O(3) |

Input/Output Capacitance (SDA) |

8 |

pF |

VI/O = 0V |

CIN(3) |

Input Capacitance (SCL, WP, A0, A1) |

6 |

pF |

VIN = 0V |

Note:

(1)The minimum DC input voltage is –0.5V. During transitions, inputs may undershoot to –2.0V for periods of less than 20 ns. Maximum DC voltage on output pins is VCC +0.5V, which may overshoot to VCC + 2.0V for periods of less than 20ns.

(2)Output shorted for no more than one second. No more than one output shorted at a time.

(3)This parameter is tested initially and after a design or process change that affects the parameter.

(4)Latch-up protection is provided for stresses up to 100 mA on address and data pins from –1V to VCC +1V.

(5)Standby current (ISB ) = 0 μA (<900 nA).

Doc. No. 25061-00 6/99 S-1

2

Preliminary |

CAT24WC256 |

A.C. CHARACTERISTICS

VCC = +1.8V to +6V, unless otherwise specified

Output Load is 1 TTL Gate and 100pF

Read & Write Cycle Limits

Symbol |

Parameter |

VCC=1.8V - 6.0V |

VCC=2.5V - 6.0V |

VCC=3.0V - 5.5V |

|

|||

|

|

Min. |

Max. |

Min. |

Max. |

Min. |

Max. |

Units |

|

|

|

|

|

|

|

|

|

FSCL |

Clock Frequency |

|

100 |

|

400 |

|

1000 |

kHz |

|

|

|

|

|

|

|

|

|

tAA |

SCL Low to SDA Data Out |

0.1 |

3.5 |

0.05 |

0.9 |

0.05 |

0.55 |

μs |

|

and ACK Out |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tBUF(2) |

Time the Bus Must be Free Before |

4.7 |

|

1.2 |

|

0.5 |

|

μs |

|

a New Transmission Can Start |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tHD:STA |

Start Condition Hold Time |

4.0 |

|

0.6 |

|

0.25 |

|

μs |

|

|

|

|

|

|

|

|

|

tLOW |

Clock Low Period |

4.7 |

|

1.2 |

|

0.6 |

|

μs |

|

|

|

|

|

|

|

|

|

tHIGH |

Clock High Period |

4.0 |

|

0.6 |

|

0.4 |

|

μs |

|

|

|

|

|

|

|

|

|

tSU:STA |

Start Condition Setup Time |

4.0 |

|

0.6 |

|

0.25 |

|

μs |

|

(for a Repeated Start Condition) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tHD:DAT |

Data In Hold Time |

0 |

|

0 |

|

0 |

|

ns |

|

|

|

|

|

|

|

|

|

tSU:DAT |

Data In Setup Time |

100 |

|

100 |

|

100 |

|

ns |

|

|

|

|

|

|

|

|

|

tR(2) |

SDA and SCL Rise Time |

|

1.0 |

|

0.3 |

|

0.3 |

μs |

tF(2) |

SDA and SCL Fall Time |

|

300 |

|

300 |

|

100 |

ns |

tSU:STO |

Stop Condition Setup Time |

4.7 |

|

0.6 |

|

0.25 |

|

μs |

|

|

|

|

|

|

|

|

|

tDH |

Data Out Hold Time |

100 |

|

50 |

|

50 |

|

ns |

|

|

|

|

|

|

|

|

|

tWR |

Write Cycle Time |

|

10 |

|

10 |

|

5 |

ms |

|

|

|

|

|

|

|

|

|

Power-Up Timing (2)(3)

Symbol |

Parameter |

Max. |

Units |

|

|

|

|

tPUR |

Power-Up to Read Operation |

1 |

ms |

|

|

|

|

tPUW |

Power-Up to Write Operation |

1 |

ms |

|

|

|

|

Note:

(1)AC measurement conditions:

RL (connects to VCC): 0.3VCC to 0.7 VCC Input rise and fall times: < 50ns

Input and output timing reference voltages: 0.5 VCC

(2)This parameter is tested initially and after a design or process change that affects the parameter.

(3)tPUR and tPUW are the delays required from the time VCC is stable until the specified operation can be initiated.

The write cycle time is the time from a valid stop condition of a write sequence to the end of the internal program/erase cycle. During the write cycle, the bus

interface circuits are disabled, SDA is allowed to remain high, and the device does not respond to its slave address.

3 |

Doc. No. 25061-00 6/99 S-1 |

Loading...

Loading...