MOTOROLA SN74LS293DR2, SN74LS293N, SN74LS290N, SN74LS293D, SN74LS290D Datasheet

...

5-1

FAST AND LS TTL DAT A

DECADE COUNTER;

4-BIT BINARY COUNTER

The SN54/74LS290 and SN54/74LS293 are high-speed 4-bit ripple type

counters partitioned into two sections. Each counter has a divide-by-two section and either a divide-by-five (LS290) or divide-by-eight (LS293) section

which are triggered by a HIGH-to-LOW transition on the clock inputs. Each

section can be used separately or tied together (Q to CP

)to form BCD,

Bi-quinary , or Modulo-16 counters. Both of the counters have a 2-input gated

Master Reset (Clear), and the LS290 also has a 2-input gated Master Set

(Preset 9).

• Corner Power Pin Versions of the LS90 and LS93

• Low Power Consumption . . . Typically 45 mW

• High Count Rates . . . Typically 42 MHz

• Choice of Counting Modes . . . BCD, Bi-Quinary, Binary

• Input Clamp Diodes Limit High Speed Termination Effects

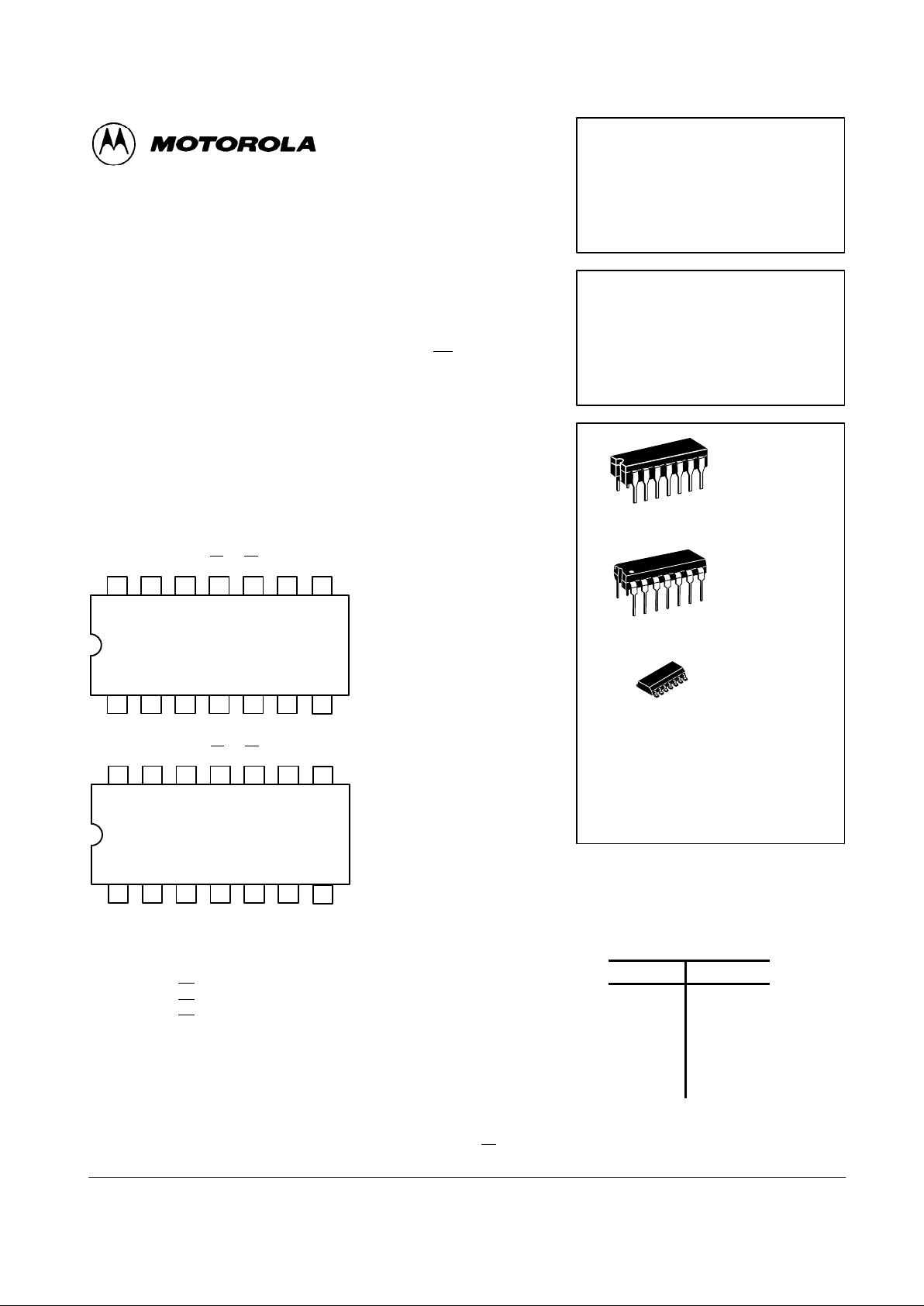

14 13 12 11 10 9

123456

8

7

VCCMR MR CP

1CP0Q0Q3

MS NC MS Q2Q1NC GND

CONNECTION DIAGRAM DIP (TOP VIEW)

LS290

LS293

NOTE:

The Flatpak version

has the same pinouts

(Connection Diagram) as

the Dual In-Line Package.

14 13 12 11 10 9

123456

8

7

VCCMR MR CP

1CP0Q0Q3

NC NC NC Q2Q1NC GND

PIN NAMES LOADING (Note a)

HIGH

LOW

CP

0

Clock (Active LOW going edge) Input to ÷2 Section. 0.05 U.L. 1.5 U.L.

CP1 Clock (Active LOW going edge) Input to ÷5 Section (LS290). 0.05 U.L. 2.0 U.L.

CP1 Clock (Active LOW going edge) Input to ÷8 Section (LS293). 0.05 U.L. 1.0 U.L.

MR1, MR2 Master Reset (Clear) Inputs 0.5 U.L. 0.25 U.L.

MS1, MS2 Master Set (Preset-9, LS290) Inputs 0.5 U.L. 0.25 U.L.

Q0 Output from ÷2 Section (Notes b & c) 10 U.L. 5 (2.5) U.L.

Q1, Q2, Q3 Outputs from ÷5 & ÷8 Sections (Note b) 10 U.L. 5 (2.5) U.L.

NOTES:

a) 1 TTL Unit Load (U.L.) = 40 µA HIGH/1.6 mA LOW.

b) The Output LOW drive factor is 2.5 U.L. for Military (54) and 5 U.L. for Commercial (74) Temperature Ranges.

c) The Q0 Outputs are guaranteed to drive the full fan-out plus the CP

1

Input of the device.

SN54/74LS290

SN54/74LS293

DECADE COUNTER;

4-BIT BINARY COUNTER

LOW POWER SCHOTTKY

ORDERING INFORMATION

SN54LSXXXJ Ceramic

SN74LSXXXN Plastic

SN74LSXXXD SOIC

J SUFFIX

CERAMIC

CASE 632-08

N SUFFIX

PLASTIC

CASE 646-06

14

1

14

1

14

1

D SUFFIX

SOIC

CASE 751A-02

5-2

FAST AND LS TTL DATA

SN54/74LS290 D SN54/74LS293

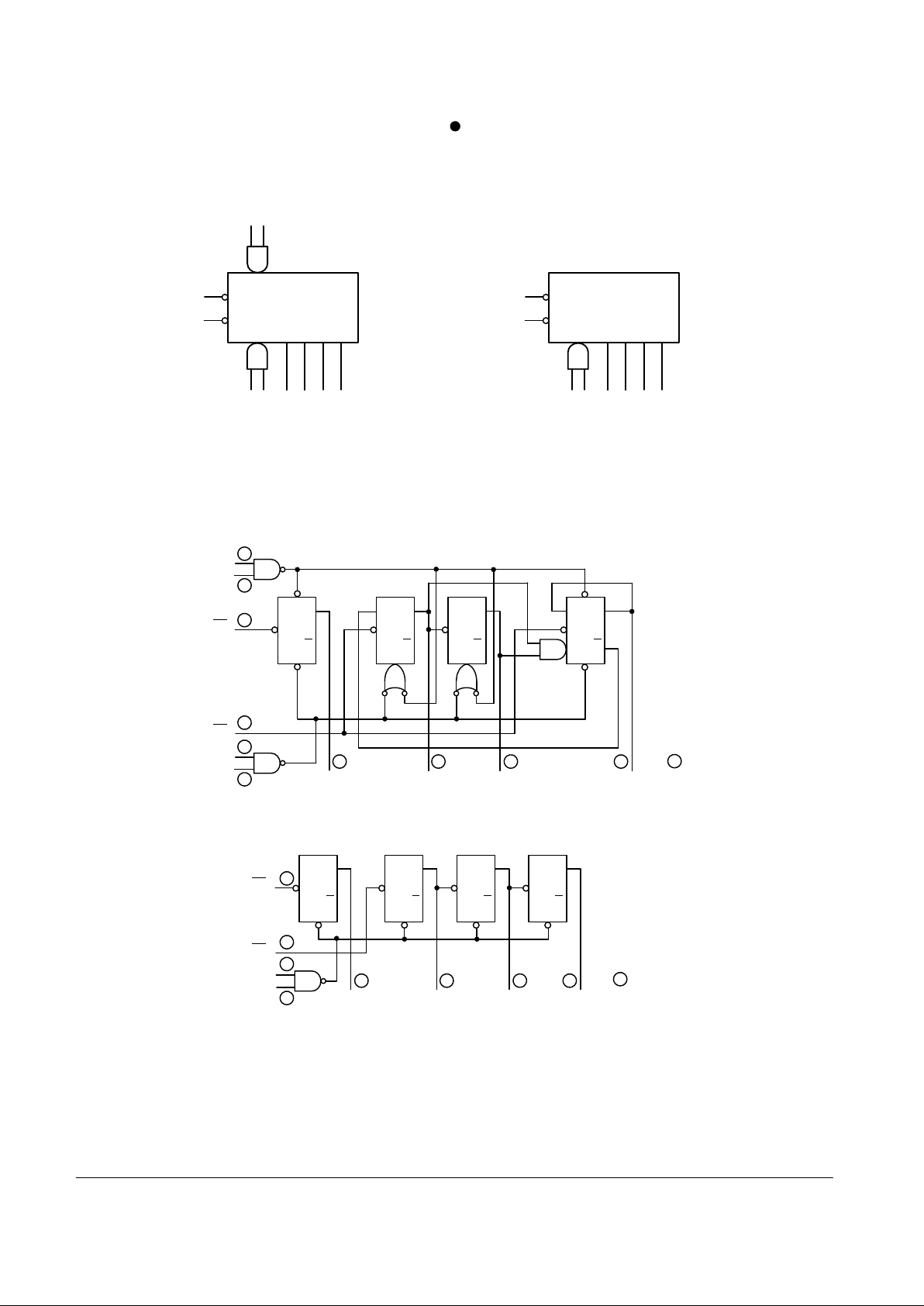

LOGIC SYMBOL

LS290 LS293

VCC = PIN 14

GND = PIN 7

NC = PINS 2, 6

13

12

12

10

11

MS

CP

0

CP

1

MR Q0Q1Q2Q

3

12 13 9 5 4 8

VCC = PIN 14

GND = PIN 7

NC = PINS 1, 2, 3, 6

12

10

11

CP

0

CP

1

MR Q0Q1Q2Q

3

12 13 9 5 4 8

LS290

LS293

LOGIC DIAGRAMS

S

D

J

CP

C

D

Q

QJ

CP

C

D

Q

QJ

CP

C

D

Q

QR

CP

C

D

Q

Q

S

D

KS

J

CP

C

D

Q

Q

K

J

CP

C

D

Q

Q

K

J

CP

C

D

Q

Q

K

J

CP

C

D

Q

Q

K

MS

1

MS

2

CP

0

CP

1

MR

1

MR

2

CP

0

CP

1

MR

1

MR

2

Q

0

Q

1

Q

2

Q

3

Q

0

Q

1

Q

2

Q

3

VCC = PIN 14

GND = PIN 7

= PIN NUMBERS

VCC = PIN 14

GND = PIN 7

= PIN NUMBERS

1

3

8459

11

12

10

13

10

13

11

12

8459

K

Loading...

Loading...