Fairchild Semiconductor NM25C160EN, NM25C160LEM8, NM25C160LEN, NM25C160LEM8X, NM25C160LM8 Datasheet

...

March 1999

NM25C160

16K-Bit Serial CMOS EEPROM

(Serial Peripheral Interface (SPI) Synchronous Bus)

General Description

The NM25C160 is a 16,384-bit CMOS EEPROM with an SPI compatible serial interface. The NM25C160 is designed for data storage in applications requiring both non-volatile memory and insystem data updates. This EEPROM is well suited for applications using the 68HC11 series of microcontrollers that support the SPI interface for high speed communication with peripheral devices via a serial bus to reduce pin count. The NM25C160 is implemented in Fairchild Semiconductor’s floating gate CMOS process that provides superior endurance and data retention.

The serial data transmission of this device requires four signal lines to control the device operation: Chip Select (CS), Clock (SCK), Data In (SI), and Serial Data Out (SO). All programming cycles are completely self-timed and do not require an erase before WRITE.

BLOCK WRITE protection is provided by programming the STATUS REGISTER with one of four levels of write protection. Additionally, separate WRITE enable and WRITE disable instructions are provided for data protection.

Hardware data protection is provided by the WP pin to protect against inadvertent programming. The HOLD pin allows the serial communication to be suspended without resetting the serial sequence.

Features

■2.1 MHz clock rate @ 2.7V to 5.5V

■16,384 bits organized as 2,048 x 8

■Multiple chips on the same 3-wire bus with separate chip select lines

■Self-timed programming cycle

■Simultaneous programming of 1 to 16 bytes at a time

■Status register can be polled during programming to monitor READY/BUSY

■Write Protect (WP) pin and write disable instruction for both hardware and software write protection

■Block write protect feature to protect against accidental writes

■Endurance: 1,000,000 data changes

■Data retention greater than 40 years

■Packages available: 8-pin DIP, 8-pin SO, or 8-pin TSSOP

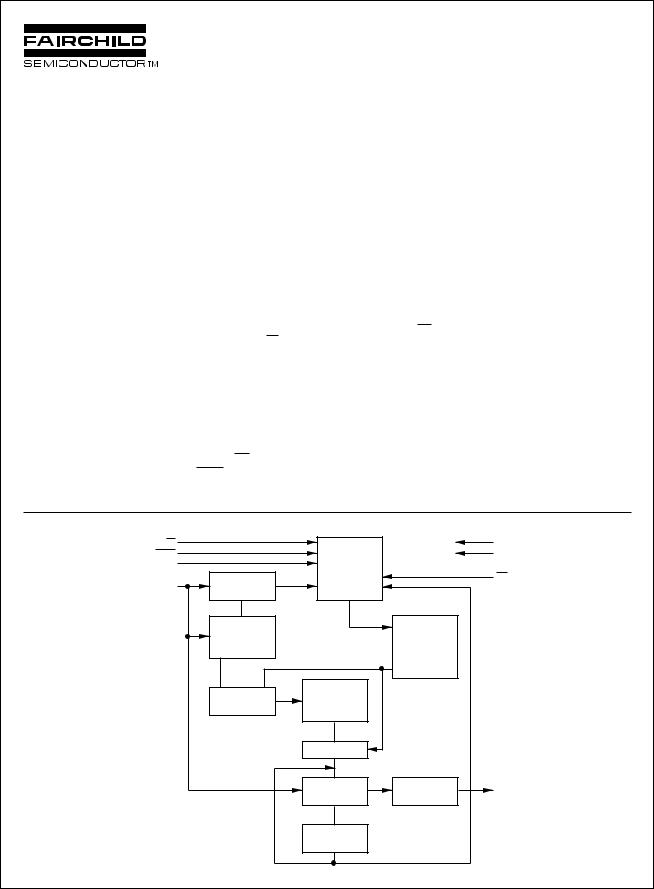

Block Diagram

CS |

|

Instruction |

|

VCC |

HOLD |

|

|

VSS |

|

|

Decoder |

|

||

SCK |

|

|

|

|

|

Control Logic |

|

|

|

|

|

|

WP |

|

SI |

Instruction |

and Clock |

|

|

|

|

|||

Register |

Generators |

|

|

|

|

|

|

||

|

Address |

Program |

High Voltage |

|

|

Enable |

|

||

|

Counter/ |

Generator |

|

|

|

|

|

||

|

Register |

|

and |

|

|

|

VPP |

Program |

|

|

|

Timer |

|

|

|

|

|

|

|

|

Decoder |

EEPROM Array |

|

|

|

16,384 Bits |

|

|

|

|

1 of 2048 |

|

|

|

|

(2048 x 8) |

|

|

|

|

|

|

|

|

|

|

Read/Write Amps |

|

|

|

|

Data In/Out Register |

Data Out |

SO |

|

|

8 Bits |

Buffer |

|

|

|

|

||

|

|

Non-Volatile |

|

|

|

|

Status Register |

|

|

|

|

|

|

DS012402-1 |

(SPI) Interface Periphrial (Serial |

CMOS Serial Bit-16K NM25C160 |

Synchronous |

EEPROM |

Bus) |

|

© 1999 Fairchild Semiconductor Corporation |

1 |

www.fairchildsemi.com |

NM25C160 Rev. D.1

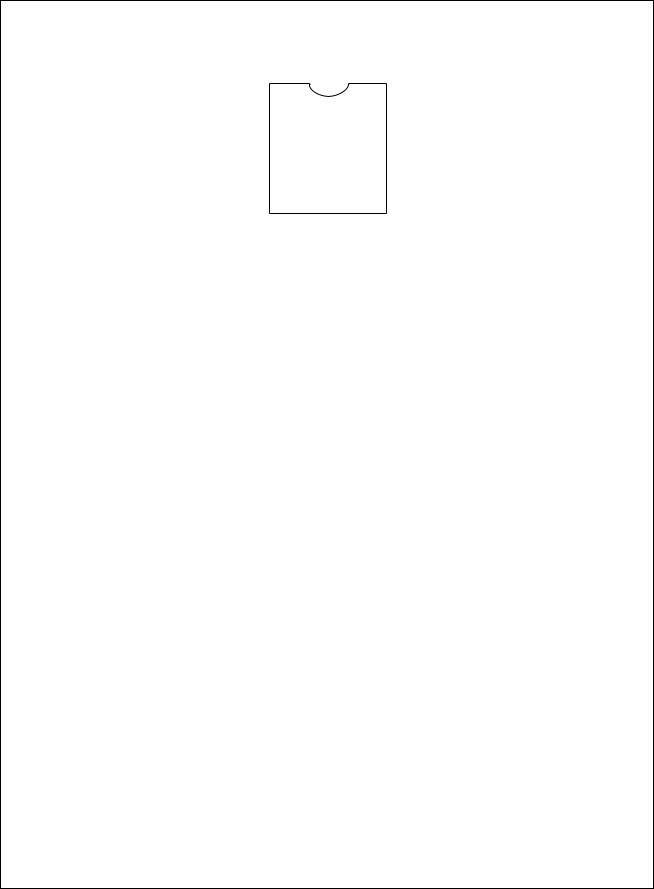

Connection Diagram

Dual-In-Line Package (N), SO Package (M8),

and TSSOP Package (MT8)

CS |

|

1 |

8 |

|

VCC |

|

|

||||

SO |

|

2 |

7 |

|

HOLD |

|

|

||||

|

|

|

NM25C160 |

|

|

WP |

|

3 |

6 |

|

SCK |

|

|

||||

VSS |

|

4 |

5 |

|

SI |

|

|

DS012402-2

Top View

See Package Number N08E (N), M08A (M8), and MTC08 (MT8)

Pin Names

|

|

|

|

|

|

|

|

|

CS |

Chip Select Input |

|||

|

|

|

|

|

|

|

|

|

SO |

Serial Data Output |

|||

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

WP |

Write Protect |

|||

|

|

|

|

|

|

|

|

|

VSS |

Ground |

|||

|

|

SI |

Serial Data Input |

|||

|

|

|

|

|

|

|

|

SCK |

Serial Clock Input |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

HOLD |

Suspends Serial Data |

|||||

|

|

|

|

|

|

|

|

VCC |

Power Supply |

||||

Ordering Information |

|

|

||||||||||||

NM 25 |

C |

XX LZ E XX |

Letter |

Description |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

Package |

N |

8-pin DIP |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

M8 |

8-pin SO |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

MT8 |

8-pin TSSOP |

|

|

|

|

|

|

|

|

|

|

Temp. Range |

None |

0 to 70°C |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

V |

-40 to +125°C |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

E |

-40 to +85°C |

|

|

|

|

|

|

|

|

|

Voltage Operating Range |

Blank |

4.5V to 5.5V |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

L |

2.7V to 4.5V |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

LZ |

2.7V to 4.5V and |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

<1μA Standby Current |

|

|

|

|

|

|

|

|

|

|

Density/Mode |

160 |

16K, mode 0 |

||

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

C |

CMOS technology |

|

|

|

|

|

|

|

|

|

|

|

Interface |

|||

|

|

|

|

|

|

|

|

|

|

|

25 |

SPI |

||

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

NM |

Fairchild Nonvolatile |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Memory Prefix |

(SPI) Interface Periphrial (Serial |

CMOS Serial Bit-16K NM25C160 |

Synchronous |

EEPROM |

Bus) |

|

2 |

www.fairchildsemi.com |

NM25C160 Rev. D.1

Standard Voltage 4.5 ≤ VCC ≤ 5.5V Specifications

Absolute Maximum Ratings (Note 1)

Ambient Storage Temperature |

-65°C to +150°C |

All Input or Output Voltage with |

|

Respect to Ground |

+6.5V to -0.3V |

Lead Temp. (Soldering, 10 sec.) |

+300°C |

ESD Rating |

2000V |

Operating Conditions

Ambient Operating Temperature |

|

NM25C160 |

0°C to +70°C |

NM25C160E |

-40°C to +85°C |

NM25C160V |

-40°C to +125°C |

Power Supply (VCC) |

4.5V to 5.5V |

DC and AC Electrical Characteristics 4.5V ≤ VCC ≤ 5.5V (unless otherwise specified)

Symbol |

|

|

|

|

|

|

|

Parameter |

|

|

|

|

|

Conditions |

Min |

Max |

Units |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ICC |

|

Operating Current |

|

|

|

|

= VIL |

|

3 |

mA |

|||||||||

|

|

|

|

|

CS |

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

μA |

||||||||

ICCSB |

|

Standby Current |

|

|

|

CS = VCC |

|

50 |

|||||||||||

IIL |

|

Input Leakage |

|

|

|

VIN = 0 to VCC |

-1 |

+1 |

μA |

||||||||||

IOL |

|

Output Leakage |

|

|

|

VOUT = GND to VCC |

-1 |

+1 |

μA |

||||||||||

VIL |

|

CMOS Input Low Voltage |

|

|

|

|

|

|

-0.3 |

VCC * 0.3 |

V |

||||||||

VIH |

|

CMOS Input High Voltage |

|

|

|

|

|

|

0.7 * VCC |

VCC + 0.3 |

V |

||||||||

VOL |

|

Output Low Voltage |

|

|

|

IOL = 1.6 mA |

|

0.4 |

V |

||||||||||

VOH |

|

Output High Voltage |

|

|

|

IOH = -0.8 mA |

VCC - 0.8 |

|

V |

||||||||||

fOP |

|

SCK Frequency |

|

|

|

|

|

|

|

|

2.1 |

MHz |

|||||||

tRI |

|

Input Rise Time |

|

|

|

|

|

|

|

|

2.0 |

μs |

|||||||

tFI |

|

Input Fall Time |

|

|

|

|

|

|

|

|

2.0 |

μs |

|||||||

tCLH |

|

Clock High Time |

|

|

|

(Note 2) |

190 |

|

ns |

||||||||||

tCLL |

|

Clock Low Time |

|

|

|

(Note 2) |

190 |

|

ns |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

tCSH |

|

Min CS High Time |

|

|

|

(Note 3) |

240 |

|

ns |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

tCSS |

|

CS Setup Time |

|

|

|

|

|

|

|

240 |

|

ns |

|||||||

tDIS |

|

Data Setup Time |

|

|

|

|

|

|

|

100 |

|

ns |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

tHDS |

|

HOLD Setup Time |

|

|

|

|

|

|

|

90 |

|

ns |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

tCSN |

|

CS Hold Time |

|

|

|

|

|

|

|

240 |

|

ns |

|||||||

tDIN |

|

Data Hold Time |

|

|

|

|

|

|

|

100 |

|

ns |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tHDN |

|

HOLD Hold Time |

|

|

|

|

|

|

|

90 |

|

ns |

|||||||

tPD |

|

Output Delay |

|

|

|

CL = 200 pF |

|

240 |

ns |

||||||||||

tDH |

|

Output Hold Time |

|

|

|

|

|

|

|

0 |

|

ns |

|||||||

tLZ |

|

|

|

|

to Output Low Z |

|

|

|

|

|

|

|

|

100 |

ns |

||||

|

|

HOLD |

|

|

|

|

|

|

|

|

|

||||||||

tDF |

|

Output Disable Time |

|

|

|

CL = 200 pF |

|

240 |

ns |

||||||||||

tHZ |

|

|

|

|

|

to Output High Z |

|

|

|

|

|

|

|

|

100 |

ns |

|||

|

HOLD |

|

|

|

|

|

|

|

|

|

|||||||||

tWP |

|

Write Cycle Time |

|

|

|

1–16 Bytes |

|

10 |

ms |

||||||||||

Capacitance TA = 25°C, f = 2.1/1 MHz (Note 4) |

|

AC Test Conditions |

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Output Load |

|

CL = 200 pF |

|||

Symbol |

|

|

|

|

|

|

Test |

|

Typ |

Max |

Units |

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Input Pulse Levels |

|

0.1 * VCC – 0.9 * VCC |

|||

COUT |

|

Output Capacitance |

|

3 |

8 |

pF |

|

||||||||||||

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Timing Measurement Reference Level |

0.3 * VCC - 0.7 * VCC |

||||

CIN |

|

Input Capacitance |

|

2 |

6 |

pF |

|||||||||||||

Note 1: Stress above those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions above those indicated in the operational sections of the specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Note 2: The fOP frequency specification specifies a minimum clock period of 1/fOP. Therefore, for every fOP clock cycle, tCLH + tCLL must be equal to or greater than 1/fOP. For example, if the 2.1MHz period = 476ns and tCLH = 190ns, tCLL must be 286ns.

Note 3: CS must be brought high for a minimum of tCSH between consecutive instruction cycles.

Note 4: This parameter is periodically sampled and not 100% tested.

(SPI) Interface Periphrial (Serial |

CMOS Serial Bit-16K NM25C160 |

Synchronous |

EEPROM |

Bus) |

|

3 |

www.fairchildsemi.com |

NM25C160 Rev. D.1

Loading...

Loading...