Samsung S6B0721X01-B0CY, S6B0721X01-B0CZ, S6B0721X01-xxX0, S6B0721X01-xxXN, S6B0721X11-B0CY Datasheet

...

S6B0721

132 SEG / 65 COM DRIVER & CONTROLLER FOR STN LCD

June.2000.

Ver. 0.1

Prepared by:  Jae-Su, Ko

Jae-Su, Ko

Ko1942@samsung.co.kr

Contents in this document are subject to change without notice. No part of this document may be reproduced or transmitted in any form or by any means, electronic or mechanical, for any purpose, without the express written permission of LCD Driver IC Team.

132 SEG / 65 COM DRIVER & CONTROLLER FOR STN LCD |

PRELIMINARY SPEC. VER. 0.1 |

S6B0721 |

|

|

|

S6B0721 Specification Revision History

Version |

Content |

Date |

|

|

|

0.0 |

Initial version |

Nov.1999 |

|

|

|

0.1 |

Read timing is changed (Figure 5) |

Jun.2000 |

|

|

|

2

S6B0721 |

PRELIMINARY SPEC. VER. 0.1 |

132 SEG / 65 COM DRIVER & CONTROLLER FOR STN LCD |

|

|

|

CONTENTS |

|

INTRODUCTION .................................................................................................................................................. |

1 |

FEATURES .......................................................................................................................................................... |

1 |

BLOCK DIAGRAM ............................................................................................................................................... |

3 |

PAD CONFIGURATION ....................................................................................................................................... |

4 |

PAD CENTER COORDINATES............................................................................................................................ |

5 |

PIN DESCRIPTION .............................................................................................................................................. |

7 |

POWER SUPPLY.......................................................................................................................................... |

7 |

LCD DRIVER SUPPLY.................................................................................................................................. |

7 |

SYSTEM CONTROL ..................................................................................................................................... |

8 |

MICROPROCESSOR INTERFACE ............................................................................................................. |

10 |

LCD DRIVER OUTPUTS ............................................................................................................................. |

12 |

FUNCTIONAL DESCRIPTION............................................................................................................................ |

13 |

MICROPROCESSOR INTERFACE ............................................................................................................. |

13 |

DISPLAY DATA RAM (DDRAM) .................................................................................................................. |

17 |

LCD DISPLAY CIRCUITS............................................................................................................................ |

20 |

LCD DRIVER CIRCUIT ............................................................................................................................... |

22 |

POWER SUPPLY CIRCUITS ...................................................................................................................... |

23 |

REFERECE CIRCUIT EXAMPLES.............................................................................................................. |

30 |

RESET CIRCUIT ......................................................................................................................................... |

32 |

INSTRUCTION DESCRIPTION........................................................................................................................... |

33 |

SPECIFICATIONS.............................................................................................................................................. |

47 |

ABSOLUTE MAXIMUM RATINGS............................................................................................................... |

47 |

DC CHARACTERISTICS............................................................................................................................. |

48 |

REFERENCE DATA.................................................................................................................................... |

51 |

AC CHARACTERISTICS ............................................................................................................................. |

53 |

REFERENCE APPLICATIONS........................................................................................................................... |

57 |

MICROPROCESSOR INTERFACE ............................................................................................................. |

57 |

CONNECTIONS BETWEEN S6B0721 AND LCD PANEL ............................................................................ |

58 |

TCP PIN LAYOUT (SAMPLE)...................................................................................................................... |

63 |

3

S6B0721 |

PRELIMINARY SPEC. VER. 0.1 |

132 SEG / 65 COM DRIVER & CONTROLLER FOR STN LCD |

|

|

|

INTRODUCTION

The S6B0721 is a driver & controller LSI for graphic dot-matrix liquid crystal display systems. It contains 65 commons and 132 segments driver circuits. This chip is connected directly to a microprocessor, accepts serial or 8-bit parallel display data and stores in an on-chip Display Data RAM of 65 x 132 bits. It provides a high-flexible display section due to 1-to-1 correspondence between on-chip display data RAM bits and LCD panel pixels. And it performs display data RAM read/write operation with no externally operating clock to minimize power consumption. In addition, because it contains power supply circuits necessary to drive liquid crystal, it is possible to make a display system with the fewest components.

FEATURES

Driver Output Circuits

−65 common outputs / 132 segment outputs

On-chip Display Data RAM

−Capacity: 65 x 132 = 8,580 bits

Applicable Duty Ratios

Duty ratio |

Applicable LCD bias |

Maximum display area |

|

|

|

1/65 |

1/7 or 1/9 |

65 × 132 |

|

|

|

1/49 |

1/6 or 1/8 |

49 × 132 |

|

|

|

1/33 |

1/5 or 1/6 |

33 × 132 |

|

|

|

Microprocessor Interface

−8-bit parallel bi-directional interface with 6800-series or 8080-series

−Serial interface (only write operation) available

Function Set

−Various instructions sets

−H/W, S/W reset capable

Built-in Analog Circuit

−On-chip oscillator circuit

−Voltage converter (x2, x3, x4, x5)

−Voltage regulator (temperature coefficient: -0.05%/°C, -0.2%/°C)

−Voltage follower

−Electronic contrast control function (64 steps)

Operating Voltage Range

−Supply voltage (VDD): 2.4 to 3.6 V

−LCD driving voltage (VLCD = V0 - VSS): 4.0 to 15.0 V

Low Power Consumption

−70 μΑ Typ. (VDD = 3V, x4 boosting, V0 = 11V, internal power supply ON)

−10 μΑ Max. (during power save [standby] mode)

Package Type

−Gold bump chip or TCP

1

132 SEG / 65 COM DRIVER & CONTROLLER FOR STN LCD PRELIMINARY SPEC. VER. 0.1 S6B0721

Series Specifications

Product code |

Internal TEMPS |

Temp. coefficient |

Package |

Chip thickness |

|

|

|

|

|

|

|

S6B0721X01-B0CZ |

0 |

-0.05%/°C |

|

670 μm |

|

S6B0721X01-B0CY |

(VSS connected) |

COG |

470 μm |

||

|

|||||

|

|

|

|

||

S6B0721X11-B0CZ |

1 |

-0.2%/°C |

670 μm |

||

|

|||||

S6B0721X11-B0CY |

(VDD connected) |

|

470 μm |

||

|

|

||||

|

|

|

|

|

|

S6B0721X01-xxX0 |

0 |

-0.05%/°C |

|

670 μm |

|

S6B0721X01-xxXN |

(VSS connected) |

TCP |

470 μm |

||

|

|||||

|

|

|

|

||

S6B0721X11-xxX0 |

1 |

-0.2%/°C |

670 μm |

||

|

|||||

S6B0721X11-xxXN |

(VDD connected) |

|

470 μm |

||

|

|

||||

|

|

|

|

|

* XX: TCP ordering number

2

S6B0721 |

PRELIMINARY SPEC. VER. 0.1 |

132 SEG / 65 COM DRIVER & CONTROLLER FOR STN LCD |

|

|

|

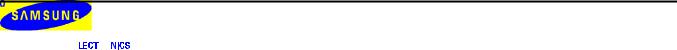

BLOCK DIAGRAM

|

|

COMS |

COM1 |

COM32 : |

SEG3 SEG2 SEG1 |

: |

SEG131 SEG130 : |

SEG132 |

COMS COM64 : COM33 |

|

VDD |

|

|

|

|

|

|

|

|

|

|

V0 |

|

|

|

|

|

|

|

|

|

|

V1 |

|

33 COMMON |

132 SEGMENT |

|

33 COMMON |

|

||||

V2 |

|

|

|

|||||||

|

DRIVER |

DRIVER CIRCUITS |

|

DRIVER |

|

|||||

V3 |

|

|

|

|||||||

|

CIRCUITS |

|

|

|

|

CIRCUITS |

|

|||

V4 |

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

VSS |

|

|

|

|

|

|

|

|

|

|

|

|

|

SEGMENT CONTROLLER |

COMMON CONTROLLER |

|

|||||

|

V / F |

|

|

|

|

|

|

|

|

|

HPM |

CIRCUIT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MS |

V0 |

PAGE |

I/O |

|

DISPLAY DATA RAM |

LINE |

|

DISPLAY |

CL |

||

ADDRESS |

|

ADDRESS |

|

M |

||||||

BUFFER |

65 X 132 = 8,580 Bits |

|

TIMING |

|||||||

|

CIRCUIT |

CIRCUIT |

|

FRS |

||||||

|

|

|

|

|

|

|

GENERATOR |

|||

VR |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

DISP |

||

|

|

|

|

|

|

|

|

CIRCUIT |

||

INTRS |

|

|

|

|

|

|

|

|

DUTY0 |

|

V / R |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

DUTY1 |

|

|

CIRCUIT |

|

|

|

|

|

|

|

|

|

|

|

|

COLUMN ADDRESS |

|

|

|

|

|||

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

CIRCUIT |

|

|

|

|

|

VOUT |

|

|

|

|

|

|

|

|

OSCILLATOR |

CLS |

|

|

|

|

|

|

|

|

|

||

C1- |

|

|

|

|

|

|

|

|

|

|

C1+ |

|

|

|

|

|

|

|

|

|

|

C2- |

V / C |

|

|

|

|

|

|

|

|

|

C2+ |

|

|

|

|

|

|

|

|

|

|

CIRCUIT |

|

|

|

|

|

|

|

|

|

|

C3- |

|

STATUS REGISTER |

INSTRUCTION REGISTER |

|

||||||

|

|

|

||||||||

C3+ |

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

DCDC5B |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

BUS HOLDER |

|

INSTRUCTION DECODER |

|

|||

|

|

|

MPU INTERFACE (PARALLEL & SERIAL) |

|

||||||

|

|

CS1B |

CS2 |

RD E RS |

MI RESETB PS WR RW |

DB3 DB4 DB5 DB6(SCLK) DB7(SID) |

DB2 |

DB0 DB1 |

|

|

Figure 1. Block Diagram

3

132 SEG / 65 COM DRIVER & CONTROLLER FOR STN LCD |

PRELIMINARY SPEC. VER. 0.1 |

S6B0721 |

|

|

|

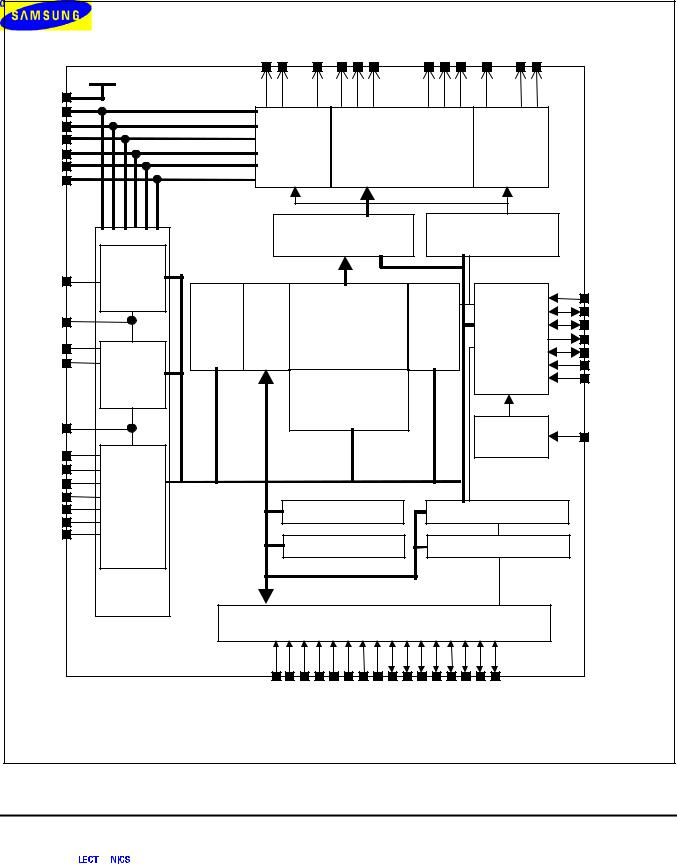

PAD CONFIGURATION

|

|

283 |

|

138 |

|

|

284 |

ð |

р рр ррррррррррррррррррр - - - - - - - - - -ррррррррррррррррррр рр р |

ð |

137 |

||

|

-ðððð |

S6B0721 |

Y |

|

-ðððð |

|

|

|

|

|

|||

|

- - |

(TOP VIEW) |

(0,0) |

X |

- - |

|

|

ррррр- |

|

ррррр- |

|

||

312 |

р рррррррррррррррррр |

- - - - - - - - - - |

рррррррррррррррррр р |

109 |

||

|

|

|

|

|||

|

|

1 |

|

108 |

|

|

Figure 2. S6B0721 Chip Configuration

Table 1. S6B0721 Pad Dimensions

Items |

Pad No. |

|

Size |

Unit |

|

|

|

|

|||

X |

|

Y |

|||

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

Chip size |

- |

9640 |

|

2020 |

|

|

|

|

|

|

|

|

1,108,109,137,138,283, |

|

90 |

|

|

|

284,312 |

|

|

||

|

|

|

|

|

|

Pad pitch |

|

|

|

|

|

2 to 107 |

|

70 |

|

||

|

|

|

|

|

|

|

110 to 136, 139 to 282 |

|

60 |

|

|

|

285 to 311 |

|

|

||

|

|

|

|

μm |

|

|

1,108 |

70 |

|

100 |

|

|

|

|

|||

|

|

|

|

|

|

|

2 to 107 |

50 |

|

100 |

|

|

|

|

|

|

|

Bumped pad size |

109,137,284,312 |

110 |

|

60 |

|

|

|

|

|

|

|

(Top size) |

110 to 136,285 to 311 |

110 |

|

45 |

|

|

|

|

|

|

|

|

139 to 282 |

45 |

|

110 |

|

|

|

|

|

|

|

|

138,283 |

60 |

|

110 |

|

|

|

|

|

|

|

Bumped pad height |

1 to 312 |

14(Typ.) |

|

||

|

|

|

|

|

|

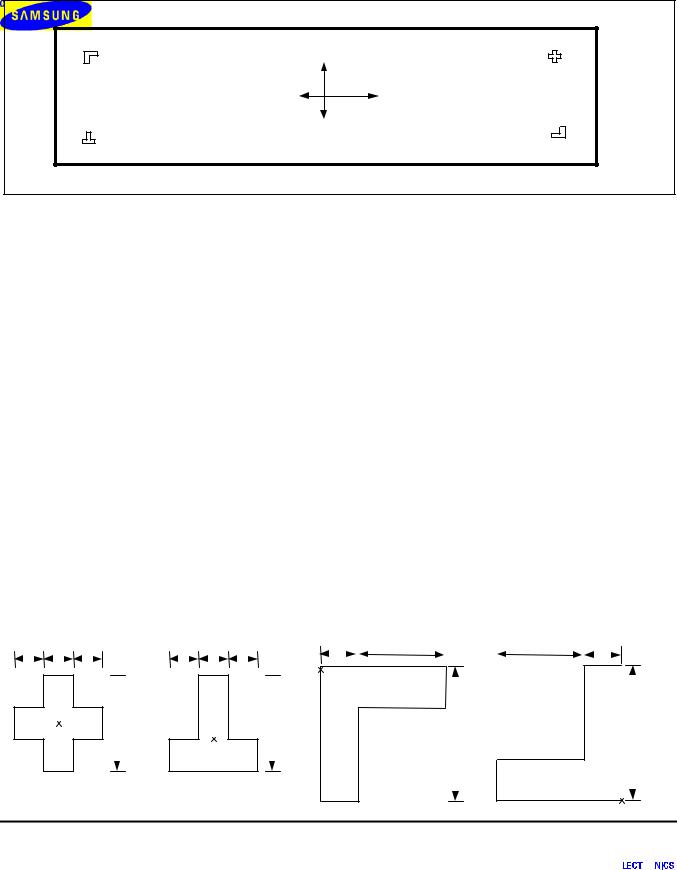

COG Align Key Coordinate |

ILB Align Key Coordinate |

|

|

|

|

|||||||||||||||||

30μm 30μm 30μm |

30μm 30μm 30μm |

42μm |

108μm |

108μm |

42μm |

|||||||||||||||||

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(+4089, +312)

mμ30 mμ30 mμ30

(-4094, -565)

mμ60 mμ30

(-4161, +473)

mμ42 mμ108

(+4161, -597)

mμ42 mμ108

4

S6B0721 PRELIMINARY SPEC. VER. 0.1 132 SEG / 65 COM DRIVER & CONTROLLER FOR STN LCD

PAD CENTER COORDINATES

|

|

|

|

|

Table 2. Pad Center Coordinates |

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

[Unit: μm] |

|

Pad |

Pad |

X |

Y |

|

Pad |

Pad |

X |

Y |

Pad |

Pad |

X |

Y |

No |

Name |

|

No |

Name |

No |

Name |

||||||

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

DUMMY |

-3765 |

|

-895 |

55 |

VDD |

35 |

-895 |

109 |

DUMMY |

4673 |

-850 |

2 |

FRS |

-3675 |

|

-895 |

56 |

VOUT |

105 |

-895 |

110 |

COMS |

4673 |

-780 |

|

|

|

|

|

|

|

|

|

|

|

|

|

3 |

M |

-3605 |

|

-895 |

57 |

VOUT |

175 |

-895 |

111 |

COM1 |

4673 |

-720 |

|

|

|

|

|

|

|

|

|

|

|

|

|

4 |

CL |

-3535 |

|

-895 |

58 |

VOUT |

245 |

-895 |

112 |

COM2 |

4673 |

-660 |

|

|

|

|

|

|

|

|

|

|

|

|

|

5 |

DISP |

-3465 |

|

-895 |

59 |

VOUT |

315 |

-895 |

113 |

COM3 |

4673 |

-600 |

|

|

|

|

|

|

|

|

|

|

|

|

|

6 |

VSS |

-3395 |

|

-895 |

60 |

C3+ |

385 |

-895 |

114 |

COM4 |

4673 |

-540 |

|

|

|

|

|

|

|

|

|

|

|

|

|

7 |

CS1B |

-3325 |

|

-895 |

61 |

C3+ |

455 |

-895 |

115 |

COM5 |

4673 |

-480 |

|

|

|

|

|

|

|

|

|

|

|

|

|

8 |

CS2 |

-3255 |

|

-895 |

62 |

C3+ |

525 |

-895 |

116 |

COM6 |

4673 |

-420 |

9 |

VDD |

-3185 |

|

-895 |

63 |

C3+ |

595 |

-895 |

117 |

COM7 |

4673 |

-360 |

10 |

RESETB |

-3115 |

|

-895 |

64 |

C3- |

665 |

-895 |

118 |

COM8 |

4673 |

-300 |

11 |

RS |

-3045 |

|

-895 |

65 |

C3- |

735 |

-895 |

119 |

COM9 |

4673 |

-240 |

12 |

VSS |

-2975 |

|

-895 |

66 |

C3- |

805 |

-895 |

120 |

COM10 |

4673 |

-180 |

13 |

RW_WR |

-2905 |

|

-895 |

67 |

C3- |

875 |

-895 |

121 |

COM11 |

4673 |

-120 |

|

|

|

|

|

|

|

|

|

|

|

|

|

14 |

E_RD |

-2835 |

|

-895 |

68 |

C1+ |

945 |

-895 |

122 |

COM12 |

4673 |

-60 |

|

|

|

|

|

|

|

|

|

|

|

|

|

15 |

VDD |

-2765 |

|

-895 |

69 |

C1+ |

1015 |

-895 |

123 |

COM13 |

4673 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

16 |

DB0 |

-2695 |

|

-895 |

70 |

C1+ |

1085 |

-895 |

124 |

COM14 |

4673 |

60 |

|

|

|

|

|

|

|

|

|

|

|

|

|

17 |

DB1 |

-2625 |

|

-895 |

71 |

C1+ |

1155 |

-895 |

125 |

COM15 |

4673 |

120 |

|

|

|

|

|

|

|

|

|

|

|

|

|

18 |

DB2 |

-2555 |

|

-895 |

72 |

C1- |

1225 |

-895 |

126 |

COM16 |

4673 |

180 |

|

|

|

|

|

|

|

|

|

|

|

|

|

19 |

DB3 |

-2485 |

|

-895 |

73 |

C1- |

1295 |

-895 |

127 |

COM17 |

4673 |

240 |

|

|

|

|

|

|

|

|

|

|

|

|

|

20 |

DB4 |

-2415 |

|

-895 |

74 |

C1- |

1365 |

-895 |

128 |

COM18 |

4673 |

300 |

|

|

|

|

|

|

|

|

|

|

|

|

|

21 |

DB5 |

-2345 |

|

-895 |

75 |

C1- |

1435 |

-895 |

129 |

COM19 |

4673 |

360 |

22 |

DB6 |

-2275 |

|

-895 |

76 |

C2+ |

1505 |

-895 |

130 |

COM20 |

4673 |

420 |

23 |

DB7 |

-2205 |

|

-895 |

77 |

C2+ |

1575 |

-895 |

131 |

COM21 |

4673 |

480 |

24 |

VSS |

-2135 |

|

-895 |

78 |

C2+ |

1645 |

-895 |

132 |

COM22 |

4673 |

540 |

25 |

DUMMY |

-2065 |

|

-895 |

79 |

C2+ |

1715 |

-895 |

133 |

COM23 |

4673 |

600 |

26 |

DUMMY |

-1995 |

|

-895 |

80 |

C2- |

1785 |

-895 |

134 |

COM24 |

4673 |

660 |

|

|

|

|

|

|

|

|

|

|

|

|

|

27 |

VDD |

-1925 |

|

-895 |

81 |

C2- |

1855 |

-895 |

135 |

COM25 |

4673 |

720 |

|

|

|

|

|

|

|

|

|

|

|

|

|

28 |

DUTY0 |

-1855 |

|

-895 |

82 |

C2- |

1925 |

-895 |

136 |

COM26 |

4673 |

780 |

|

|

|

|

|

|

|

|

|

|

|

|

|

29 |

DUTY1 |

-1785 |

|

-895 |

83 |

C2- |

1995 |

-895 |

137 |

DUMMY |

4673 |

850 |

30 |

VSS |

-1715 |

|

-895 |

84 |

VSS |

2065 |

-895 |

138 |

DUMMY |

4380 |

863 |

31 |

MS |

-1645 |

|

-895 |

85 |

VSS |

2135 |

-895 |

139 |

COM27 |

4290 |

863 |

32 |

CLS |

-1575 |

|

-895 |

86 |

VR |

2205 |

-895 |

140 |

COM28 |

4230 |

863 |

33 |

VDD |

-1505 |

|

-895 |

87 |

VR |

2275 |

-895 |

141 |

COM29 |

4170 |

863 |

34 |

MI |

-1435 |

|

-895 |

88 |

V0 |

2345 |

-895 |

142 |

COM30 |

4110 |

863 |

|

|

|

|

|

|

|

|

|

|

|

|

|

35 |

PS |

-1365 |

|

-895 |

89 |

V0 |

2415 |

-895 |

143 |

COM31 |

4050 |

863 |

|

|

|

|

|

|

|

|

|

|

|

|

|

36 |

VSS |

-1295 |

|

-895 |

90 |

V1 |

2485 |

-895 |

144 |

COM32 |

3990 |

863 |

|

|

|

|

|

|

|

|

|

|

|

|

|

37 |

VSS |

-1225 |

|

-895 |

91 |

V1 |

2555 |

-895 |

145 |

SEG1 |

3930 |

863 |

|

|

|

|

|

|

|

|

|

|

|

|

|

38 |

VSS |

-1155 |

|

-895 |

92 |

V2 |

2625 |

-895 |

146 |

SEG2 |

3870 |

863 |

|

|

|

|

|

|

|

|

|

|

|

|

|

39 |

VSS |

-1085 |

|

-895 |

93 |

V2 |

2695 |

-895 |

147 |

SEG3 |

3810 |

863 |

|

|

|

|

|

|

|

|

|

|

|

|

|

40 |

VSS |

-1015 |

|

-895 |

94 |

V3 |

2765 |

-895 |

148 |

SEG4 |

3750 |

863 |

|

|

|

|

|

|

|

|

|

|

|

|

|

41 |

VSS |

-945 |

|

-895 |

95 |

V3 |

2835 |

-895 |

149 |

SEG5 |

3690 |

863 |

|

|

|

|

|

|

|

|

|

|

|

|

|

42 |

VSS |

-875 |

|

-895 |

96 |

V4 |

2905 |

-895 |

150 |

SEG6 |

3630 |

863 |

43 |

VSS |

-805 |

|

-895 |

97 |

V4 |

2975 |

-895 |

151 |

SEG7 |

3570 |

863 |

44 |

VSS |

-735 |

|

-895 |

98 |

VSS |

3045 |

-895 |

152 |

SEG8 |

3510 |

863 |

45 |

VSS |

-665 |

|

-895 |

99 |

VSS |

3115 |

-895 |

153 |

SEG9 |

3450 |

863 |

46 |

VDD |

-595 |

|

-895 |

100 |

DUMMY |

3185 |

-895 |

154 |

SEG10 |

3390 |

863 |

47 |

VDD |

-525 |

|

-895 |

101 |

DCDC5B |

3255 |

-895 |

155 |

SEG11 |

3330 |

863 |

|

|

|

|

|

|

|

|

|

|

|

|

|

48 |

VDD |

-455 |

|

-895 |

102 |

VDD |

3325 |

-895 |

156 |

SEG12 |

3270 |

863 |

|

|

|

|

|

|

|

|

|

|

|

|

|

49 |

VDD |

-385 |

|

-895 |

103 |

HPM |

3395 |

-895 |

157 |

SEG13 |

3210 |

863 |

|

|

|

|

|

|

|

|

|

|

|

|

|

50 |

VDD |

-315 |

|

-895 |

104 |

INTRS |

3465 |

-895 |

158 |

SEG14 |

3150 |

863 |

|

|

|

|

|

|

|

|

|

|

|

|

|

51 |

VDD |

-245 |

|

-895 |

105 |

VSS |

3535 |

-895 |

159 |

SEG15 |

3090 |

863 |

|

|

|

|

|

|

|

|

|

|

|

|

|

52 |

VDD |

-175 |

|

-895 |

106 |

DUMMY |

3605 |

-895 |

160 |

SEG16 |

3030 |

863 |

53 |

VDD |

-105 |

|

-895 |

107 |

VDD |

3675 |

-895 |

161 |

SEG17 |

2970 |

863 |

|

|

|

|

|

|

|

|

|

|

|

|

|

54 |

VDD |

-35 |

|

-895 |

108 |

TESTCK |

3765 |

-895 |

162 |

SEG18 |

2910 |

863 |

|

|

|

|

|

|

|

|

|

|

|

|

|

5

132 SEG / 65 COM DRIVER & CONTROLLER FOR STN LCD PRELIMINARY SPEC. VER. 0.1 S6B0721

|

|

|

|

Table 2. Pad Center Coordinates (Continued) |

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

[Unit: μm] |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Pad |

Pad |

X |

Y |

Pad |

Pad |

X |

Y |

Pad |

Pad |

X |

Y |

|||

|

No |

Name |

|

No |

Name |

|

No |

Name |

|||||||

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

163 |

SEG19 |

2850 |

863 |

217 |

SEG73 |

-390 |

863 |

271 |

SEG127 |

-3630 |

863 |

||||

|

164 |

SEG20 |

2790 |

863 |

|

218 |

SEG74 |

-450 |

863 |

|

272 |

SEG128 |

-3690 |

863 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

165 |

SEG21 |

2730 |

863 |

|

219 |

SEG75 |

-510 |

863 |

|

273 |

SEG129 |

-3750 |

863 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

166 |

SEG22 |

2670 |

863 |

|

220 |

SEG76 |

-570 |

863 |

|

274 |

SEG130 |

-3810 |

863 |

|

|

167 |

SEG23 |

2610 |

863 |

|

221 |

SEG77 |

-630 |

863 |

|

275 |

SEG131 |

-3870 |

863 |

|

|

168 |

SEG24 |

2550 |

863 |

|

222 |

SEG78 |

-690 |

863 |

|

276 |

SEG132 |

-3930 |

863 |

|

|

169 |

SEG25 |

2490 |

863 |

|

223 |

SEG79 |

-750 |

863 |

|

277 |

COMS |

-3990 |

863 |

|

|

170 |

SEG26 |

2430 |

863 |

|

224 |

SEG80 |

-810 |

863 |

|

278 |

COM64 |

-4050 |

863 |

|

|

171 |

SEG27 |

2370 |

863 |

|

225 |

SEG81 |

-870 |

863 |

|

279 |

COM63 |

-4110 |

863 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

172 |

SEG28 |

2310 |

863 |

|

226 |

SEG82 |

-930 |

863 |

|

280 |

COM62 |

-4170 |

863 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

173 |

SEG29 |

2250 |

863 |

|

227 |

SEG83 |

-990 |

863 |

|

281 |

COM61 |

-4230 |

863 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

174 |

SEG30 |

2190 |

863 |

|

228 |

SEG84 |

-1050 |

863 |

|

282 |

COM60 |

-4290 |

863 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

175 |

SEG31 |

2130 |

863 |

|

229 |

SEG85 |

-1110 |

863 |

|

283 |

DUMMY |

-4380 |

863 |

|

|

176 |

SEG32 |

2070 |

863 |

|

230 |

SEG86 |

-1170 |

863 |

|

284 |

DUMMY |

-4673 |

850 |

|

|

177 |

SEG33 |

2010 |

863 |

|

231 |

SEG87 |

-1230 |

863 |

|

285 |

COM59 |

-4673 |

780 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

178 |

SEG34 |

1950 |

863 |

|

232 |

SEG88 |

-1290 |

863 |

|

286 |

COM58 |

-4673 |

720 |

|

|

179 |

SEG35 |

1890 |

863 |

|

233 |

SEG89 |

-1350 |

863 |

|

287 |

COM57 |

-4673 |

660 |

|

|

180 |

SEG36 |

1830 |

863 |

|

234 |

SEG90 |

-1410 |

863 |

|

288 |

COM56 |

-4673 |

600 |

|

|

181 |

SEG37 |

1770 |

863 |

|

235 |

SEG91 |

-1470 |

863 |

|

289 |

COM55 |

-4673 |

540 |

|

|

182 |

SEG38 |

1710 |

863 |

|

236 |

SEG92 |

-1530 |

863 |

|

290 |

COM54 |

-4673 |

480 |

|

|

183 |

SEG39 |

1650 |

863 |

|

237 |

SEG93 |

-1590 |

863 |

|

291 |

COM53 |

-4673 |

420 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

184 |

SEG40 |

1590 |

863 |

|

238 |

SEG94 |

-1650 |

863 |

|

292 |

COM52 |

-4673 |

360 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

185 |

SEG41 |

1530 |

863 |

|

239 |

SEG95 |

-1710 |

863 |

|

293 |

COM51 |

-4673 |

300 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

186 |

SEG42 |

1470 |

863 |

|

240 |

SEG96 |

-1770 |

863 |

|

294 |

COM50 |

-4673 |

240 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

187 |

SEG43 |

1410 |

863 |

|

241 |

SEG97 |

-1830 |

863 |

|

295 |

COM49 |

-4673 |

180 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

188 |

SEG44 |

1350 |

863 |

|

242 |

SEG98 |

-1890 |

863 |

|

296 |

COM48 |

-4673 |

120 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

189 |

SEG45 |

1290 |

863 |

|

243 |

SEG99 |

-1950 |

863 |

|

297 |

COM47 |

-4673 |

60 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

190 |

SEG46 |

1230 |

863 |

|

244 |

SEG100 |

-2010 |

863 |

|

298 |

COM46 |

-4673 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

191 |

SEG47 |

1170 |

863 |

|

245 |

SEG101 |

-2070 |

863 |

|

299 |

COM45 |

-4673 |

-60 |

|

|

192 |

SEG48 |

1110 |

863 |

|

246 |

SEG102 |

-2130 |

863 |

|

300 |

COM44 |

-4673 |

-120 |

|

|

193 |

SEG49 |

1050 |

863 |

|

247 |

SEG103 |

-2190 |

863 |

|

301 |

COM43 |

-4673 |

-180 |

|

|

194 |

SEG50 |

990 |

863 |

|

248 |

SEG104 |

-2250 |

863 |

|

302 |

COM42 |

-4673 |

-240 |

|

|

195 |

SEG51 |

930 |

863 |

|

249 |

SEG105 |

-2310 |

863 |

|

303 |

COM41 |

-4673 |

-300 |

|

|

196 |

SEG52 |

870 |

863 |

|

250 |

SEG106 |

-2370 |

863 |

|

304 |

COM40 |

-4673 |

-360 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

197 |

SEG53 |

810 |

863 |

|

251 |

SEG107 |

-2430 |

863 |

|

305 |

COM39 |

-4673 |

-420 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

198 |

SEG54 |

750 |

863 |

|

252 |

SEG108 |

-2490 |

863 |

|

306 |

COM38 |

-4673 |

-480 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

199 |

SEG55 |

690 |

863 |

|

253 |

SEG109 |

-2550 |

863 |

|

307 |

COM37 |

-4673 |

-540 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

200 |

SEG56 |

630 |

863 |

|

254 |

SEG110 |

-2610 |

863 |

|

308 |

COM36 |

-4673 |

-600 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

201 |

SEG57 |

570 |

863 |

|

255 |

SEG111 |

-2670 |

863 |

|

309 |

COM35 |

-4673 |

-660 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

202 |

SEG58 |

510 |

863 |

|

256 |

SEG112 |

-2730 |

863 |

|

310 |

COM34 |

-4673 |

-720 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

203 |

SEG59 |

450 |

863 |

|

257 |

SEG113 |

-2790 |

863 |

|

311 |

COM33 |

-4673 |

-780 |

|

|

204 |

SEG60 |

390 |

863 |

|

258 |

SEG114 |

-2850 |

863 |

|

312 |

DUMMY |

-4673 |

-850 |

|

|

205 |

SEG61 |

330 |

863 |

|

259 |

SEG115 |

-2910 |

863 |

|

|

|

|

|

|

|

206 |

SEG62 |

270 |

863 |

|

260 |

SEG116 |

-2970 |

863 |

|

|

|

|

|

|

|

207 |

SEG63 |

210 |

863 |

|

261 |

SEG117 |

-3030 |

863 |

|

|

|

|

|

|

|

208 |

SEG64 |

150 |

863 |

|

262 |

SEG118 |

-3090 |

863 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

209 |

SEG65 |

90 |

863 |

|

263 |

SEG119 |

-3150 |

863 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

210 |

SEG66 |

30 |

863 |

|

264 |

SEG120 |

-3210 |

863 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

211 |

SEG67 |

-30 |

863 |

|

265 |

SEG121 |

-3270 |

863 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

212 |

SEG68 |

-90 |

863 |

|

266 |

SEG122 |

-3330 |

863 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

213 |

SEG69 |

-150 |

863 |

|

267 |

SEG123 |

-3390 |

863 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

214 |

SEG70 |

-210 |

863 |

|

268 |

SEG124 |

-3450 |

863 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

215 |

SEG71 |

-270 |

863 |

|

269 |

SEG125 |

-3510 |

863 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

216 |

SEG72 |

-330 |

863 |

270 |

SEG126 |

-3570 |

863 |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

6

S6B0721 |

PRELIMINARY SPEC. VER. 0.1 |

132 SEG / 65 COM DRIVER & CONTROLLER FOR STN LCD |

|

|

|

PIN DESCRIPTION

POWER SUPPLY

|

|

Table 3. Power Supply Pin Description |

|

|

||||

|

|

|

|

|

|

|

|

|

Name |

I/O |

|

|

|

Description |

|

|

|

|

|

|

|

|

|

|

|

|

VDD |

Supply |

Power supply |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VSS |

Supply |

Ground |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LCD driver supply voltages |

|

|

|

|

||

|

|

The voltage determined by LCD pixel is impedance-converted by an operational amplifier |

||||||

|

|

for application. |

|

|

|

|

|

|

|

|

Voltages should have the following relationship; |

|

|

||||

|

|

V0 ³ V1 ³ V2 ³ V3 ³ V4 ³ VSS |

|

|

|

|

||

V0 |

|

When the internal power circuit is active, these voltages are generated as following table |

||||||

V1 |

|

according to the state of LCD Bias. |

|

|

|

|

||

|

|

|

|

|

|

|

|

|

V2 |

I/O |

LCD bias |

V1 |

|

V2 |

|

V3 |

V4 |

|

|

|

|

|

|

|

||

1/9 bias |

(8/9) x V0 |

|

(7/9) x V0 |

|

(2/9) x V0 |

(1/9) x V0 |

||

V3 |

|

|

|

|||||

|

|

|

|

|

|

|

|

|

V4 |

|

1/8 bias |

(7/8) x V0 |

|

(6/8) x V0 |

|

(2/8) x V0 |

(1/8) x V0 |

|

|

|

|

|

|

|

|

|

|

|

1/7 bias |

(6/7) x V0 |

|

(5/7) x V0 |

|

(2/7) x V0 |

(1/7) x V0 |

|

|

|

|

|

|

|

|

|

|

|

1/6 bias |

(5/6) x V0 |

|

(4/6) x V0 |

|

(2/6) x V0 |

(1/6) x V0 |

|

|

|

|

|

|

|

|

|

|

|

1/5 bias |

(4/5) x V0 |

|

(3/5) x V0 |

|

(2/5) x V0 |

(1/5) x V0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LCD DRIVER SUPPLY

|

|

Table 4. LCD Driver Supply Pin Description |

|

|

|

|

|

Name |

I/O |

Description |

|

|

|

|

|

C1- |

O |

Capacitor 1 negative connection pin for voltage converter |

|

|

|

|

|

C1+ |

O |

Capacitor 1 positive connection pin for voltage converter |

|

|

|

|

|

C2- |

O |

Capacitor 2 negative connection pin for voltage converter |

|

|

|

|

|

C2+ |

O |

Capacitor 2 positive connection pin for voltage converter |

|

|

|

|

|

C3- |

O |

Capacitor 3 negative connection pin for voltage converter |

|

|

|

|

|

C3+ |

O |

Capacitor 3 positive connection pin for voltage converter |

|

|

|

|

|

VOUT |

I/O |

Voltage converter input / output pin |

|

|

|

|

|

|

|

5 times boosting circuit enable input pin |

|

DCDC5B |

I |

When this pin is low in 4 times boosting circuit, the 5-times boosting voltage appears at |

|

|

|

VOUT. |

|

VR |

I |

V0 voltage adjustment pin |

|

It is valid only when on-chip resistors are not used (INTRS = “L”). |

|||

|

|

||

|

|

|

|

|

|

|

7

132 SEG / 65 COM DRIVER & CONTROLLER FOR STN LCD |

PRELIMINARY SPEC. VER. 0.1 |

S6B0721 |

|

|

|

SYSTEM CONTROL

|

|

|

Table 5. System Control Pin Description |

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

Name |

I/O |

|

|

|

|

Description |

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Master / Slave operation select pin |

|

|

|

|

|

|||||

|

|

− MS = "H": master operation |

|

|

|

|

|

|

|

|||

|

|

− MS = "L": slave operation |

|

|

|

|

|

|

|

|||

|

|

The following table depends on the MS status. |

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

OSC |

Power |

|

|

|

|

|

|

MS |

I |

MS |

CLS |

|

supply |

|

CL |

M |

FRS |

|

DISP |

|

|

circuit |

|

|

|||||||||

|

|

|

|

|

circuit |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

H |

H |

|

Enabled |

Enabled |

|

Output |

Output |

Output |

|

Output |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

L |

|

Disabled |

Enabled |

|

Input |

Output |

Output |

|

Output |

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

L |

- |

|

Disabled |

Disabled |

|

Input |

Input |

Output |

|

Input |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

||||||

|

|

Built-in oscillator circuit enable / disable select pin |

|

|

|

|

||||||

CLS |

I |

− CLS = “H”: enable |

|

|

|

|

|

|

|

|

||

|

|

− CLS = “L”: disable (external display clock input to CL pin) |

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|||

|

|

Display clock input / output pin |

|

|

|

|

|

|

|

|||

CL |

I/O |

When the S6B0721 is used in master/slave mode (multi-chip), the CL pins must be |

||||||||||

|

|

connected each other. |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|||

|

|

LCD AC signal input / output pin |

|

|

|

|

|

|

|

|||

|

|

When the S6B0721 is used in master/slave mode (multi-chip), the M pins must be |

||||||||||

M |

I/O |

connected each other. |

|

|

|

|

|

|

|

|

||

|

|

− MS = “H”: output |

|

|

|

|

|

|

|

|

||

|

|

− MS = “L”: input |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|||

FRS |

O |

Static driver segment output pin |

|

|

|

|

|

|

|

|||

This pin is used together with the M pin. |

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|||||

|

|

LCD display blanking control input / output |

|

|

|

|

|

|||||

DISP |

I/O |

When S6B0721 is used in master/slave mode (multi-chip), the DISP pins must be |

|

|||||||||

connected each other. |

|

|

|

|

|

|

|

|

||||

|

|

− MS = “H”: output |

|

|

|

|

|

|

|

|

||

|

|

− MS = “L”: input |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|||

|

|

Internal resistors select pin |

|

|

|

|

|

|

|

|||

|

|

This pin selects the resistors for adjusting V0 voltage level. |

|

|

|

|||||||

INTRS |

I |

− INTRS = "H": use the internal resistors. |

|

|

|

|

|

|||||

|

|

− INTRS = "L": use the external resistors. |

|

|

|

|

|

|||||

|

|

V0 voltage is controlled with VR pin and external resistive divider. |

|

|

|

|||||||

|

|

Power control pin of the power supply circuit for LCD driver |

|

|

|

|||||||

HPM |

I |

− HPM = "H": high power mode |

|

|

|

|

|

|

|

|||

− HPM = "L": normal mode |

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

||||

|

|

This pin is valid in master operation. |

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

8

S6B0721 |

PRELIMINARY SPEC. VER. 0.1 |

132 SEG / 65 COM DRIVER & CONTROLLER FOR STN LCD |

|

|

|

Table 5. System Control Pin Description (Continued)

Name |

I/O |

|

|

Description |

|

|

|

|

|

|

|

|

|

The LCD driver duty ratio depends on the following table |

|||

|

|

|

|

|

|

|

|

DUTY1 |

DUTY0 |

|

Duty ratio |

DUTY0 |

|

|

|

|

|

I |

L |

L |

|

1/33 |

|

DUTY1 |

|

|

|

|

|

|

L |

H |

|

1/49 |

|

|

|

|

|||

|

|

|

|

|

|

|

|

H |

L/H |

|

1/65 |

|

|

|

|

|

|

|

|

|

|

|

|

9

132 SEG / 65 COM DRIVER & CONTROLLER FOR STN LCD |

PRELIMINARY SPEC. VER. 0.1 |

S6B0721 |

|

|

|

MICROPROCESSOR INTERFACE

|

|

|

Table 6. Microprocessor Interface Pin Description |

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

Name |

I/O |

|

|

|

|

|

|

Description |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

RESETB |

I |

Reset input pin |

|

|

|

|

|

|

|

|

||

When RESETB is “L”, initialization is executed. |

|

|

|

|||||||||

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Parallel / Serial data input select input |

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PS |

Interface |

|

Chip |

|

Data / |

Data |

|

Read / Write |

Serial clock |

|

|

|

mode |

|

select |

instruction |

|

||||||

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

PS |

I |

H |

Parallel |

|

CS1B, |

|

RS |

DB0 to DB7 |

|

E_RD |

- |

|

|

CS2 |

|

|

RW_WR |

||||||||

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

L |

Serial |

|

CS1B, |

|

RS |

SID(DB7) |

|

Write only |

SCLK(DB6) |

|

|

|

|

CS2 |

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

*NOTE: In serial mode, it is impossible to read data from the on-chip RAM. And DB0 to |

||||||||||

|

|

DB5 are high impedance and E_RD and RW_WR must be fixed to either “H” or “L”. |

||||||||||

|

|

|

|

|

|

|

|

|

|

|||

|

|

Microprocessor interface selects input pin |

|

|

|

|

||||||

MI |

I |

− MI = "H": 6800-series MPU interface |

|

|

|

|

||||||

|

|

− MI = "L": 8080-series MPU interface |

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

CS1B |

|

Chip select input pins |

|

|

|

|

|

|

|

|

||

I |

Data / instruction I/O is enabled only when CS1B is “L” and CS2 is “H”. |

|

||||||||||

CS2 |

|

|||||||||||

|

When chip select is non-active, DB0 to DB7 may be high impedance. |

|

||||||||||

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

Register select input pin |

|

|

|

|

|

|

||||

RS |

I |

− RS = "H": DB0 to DB7 are display data |

|

|

|

|

||||||

|

|

− RS = "L": DB0 to DB7 are control data |

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

Read / Write execution control pin |

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|||

|

|

MI |

MPU type |

RW_WR |

|

|

|

Description |

|

|||

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

Read / Write control input pin |

|

|||

|

|

H |

6800-series |

RW |

|

− RW = “H”:read |

|

|

|

|||

RW_WR |

I |

|

|

|

|

|

|

− RW = “L”:write |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

Write enable clock input pin |

|

|||

|

|

L |

8080-series |

/WR |

|

The data ON DB0 to DB7 are latched at the rising |

||||||

|

|

|

|

|

|

|

|

edge of the /WR signal. |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

10

S6B0721 |

PRELIMINARY SPEC. VER. 0.1 |

132 SEG / 65 COM DRIVER & CONTROLLER FOR STN LCD |

|

|

|

Table 6. Microprocessor Interface Pin Description (Continued)

Name |

I/O |

|

|

|

Description |

|

|

|

|

|

|

|

|

Read / Write execution control pin |

|

||

|

|

|

|

|

|

|

|

MI |

MPU type |

E_RD |

Description |

|

|

|

|

|

|

|

|

|

|

|

Read / Write control input pin |

|

|

|

|

|

− RW = “H”: When E is “H”, DB0 to DB7 are in an |

E_RD |

I |

H |

6800-series |

E |

output status. |

|

|

|

− RW = “L”: The data on DB0 to DB7 are latched at |

||

|

|

|

|

|

|

|

|

|

|

|

the falling edge of the E signal. |

|

|

|

|

|

|

|

|

L |

8080-series |

/RD |

Read enable clock input pin |

|

|

When /RD is “L”, DB0 to DB7 are in an output status. |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

8-bit bi-directional data bus that is connected to the standard 8-bit microprocessor data |

|||

DB0 |

|

bus. When the serial interface selected (PS = "L"); |

|||

|

− DB0 to DB5: high impedance |

|

|||

to |

I/O |

|

|||

− DB6: serial input clock (SCLK) |

|

||||

DB7 |

|

|

|||

|

− DB7: serial input data (SID) |

|

|||

|

|

|

|||

|

|

When chip select is not active, DB0 to DB7 may be high impedance. |

|||

|

|

|

|

|

|

11

132 SEG / 65 COM DRIVER & CONTROLLER FOR STN LCD |

PRELIMINARY SPEC. VER. 0.1 |

S6B0721 |

|

|

|

LCD DRIVER OUTPUTS

Table 7. LCD Driver Outputs Pin Description

Name |

I/O |

|

|

|

Description |

|

||

|

|

|

|

|

|

|

|

|

|

|

LCD segment driver outputs |

|

|

|

|

||

|

|

The display data and the M signal control the output voltage of segment driver. |

||||||

|

|

|

|

|

|

|

|

|

|

|

Display data |

|

M |

|

Segment driver output voltage |

||

|

|

|

|

|

|

|||

|

|

|

Normal display |

Reverse display |

||||

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

SEG1 |

|

H |

|

H |

|

V0 |

V2 |

|

to |

O |

|

|

|

|

|

|

|

H |

|

L |

|

VSS |

V3 |

|||

SEG132 |

|

|

|

|||||

|

|

|

|

|

|

|

||

|

|

L |

|

H |

|

V2 |

V0 |

|

|

|

|

|

|

|

|

|

|

|

|

L |

|

L |

|

V3 |

VSS |

|

|

|

|

|

|

|

|

|

|

|

|

Power save mode |

|

|

VSS |

VSS |

||

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

||

|

|

LCD common driver outputs |

|

|

|

|

||

|

|

The internal scanning data and M signal control the output voltage of common driver. |

||||||

|

|

|

|

|

|

|||

|

|

Scan data |

|

M |

|

Common driver output voltage |

||

|

|

|

|

|

|

|

|

|

COM1 |

|

H |

|

H |

|

|

VSS |

|

|

|

|

|

|

|

|

||

|

H |

|

L |

|

|

V0 |

||

to |

O |

|

|

|

||||

|

|

|

|

|

|

|||

COM64 |

|

L |

|

H |

|

|

V1 |

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

L |

|

L |

|

|

V4 |

|

|

|

|

|

|

|

|

|

|

|

|

Power save mode |

|

|

|

VSS |

||

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

||

|

|

Common output for the icons |

|

|

|

|

||

COMS |

O |

The output signals of two pins are same. When not used, these pins should be left open. |

||||||

In multi-chip (master / slave) mode, all COMS pins on both master and slave units are the |

||||||||

|

|

|||||||

|

|

same signal. |

|

|

|

|

||

NOTE: DUMMY - These pins should be opened (floated). |

|

|

|

|||||

12

S6B0721 |

PRELIMINARY SPEC. VER. 0.1 |

132 SEG / 65 COM DRIVER & CONTROLLER FOR STN LCD |

|

|

|

FUNCTIONAL DESCRIPTION

MICROPROCESSOR INTERFACE

Chip Select Input

There are CS1B and CS2 pins for Chip Selection. The S6B0721 can interface with an MPU only when CS1B is “L” and CS2 is “H”. When these pins are set to any other combination, RS, E_RD, and RW_WR inputs are disabled and DB0 to DB7 are to be high impedance. And, in case of serial interface, the internal shift register and the counter are reset.

Parallel / Serial Interface

S6B0721 has three types of interface with an MPU, which are one serial and two parallel interfaces. This parallel or serial interface is determined by PS pin as shown in table 8.

Table 8. Parallel / Serial Interface Mode

PS |

Type |

CS1B |

CS2 |

MI |

Interface mode |

|

|

|

|

|

|

|

|

H |

Parallel |

CS1B |

CS2 |

H |

6800-series MPU mode |

|

|

|

|

||||

L |

8080-series MPU mode |

|

||||

|

|

|

|

|

||

|

|

|

|

|

|

|

L |

Serial |

CS1B |

CS2 |

*× |

Serial-mode |

|

|

|

|

|

|

|

|

|

|

|

|

|

*× : Don't care |

|

Parallel Interface (PS = "H")

The 8-bit bi-directional data bus is used in parallel interface and the type of MPU is selected by MI as shown in table 9. The type of data transfer is determined by signals at RS, E_RD and RW_WR as shown in table10.

Table 9. Microprocessor Selection for Parallel Interface

MI |

CS1B |

CS2 |

RS |

E_RD |

RW_WR |

DB0 to DB7 |

|

MPU bus |

|

|

|

|

|

|

|

|

|

H |

CS1B |

CS2 |

RS |

E |

RW |

DB0 to DB7 |

|

6800-series |

|

|

|

|

|

|

|

|

|

L |

CS1B |

CS2 |

RS |

/RD |

/WR |

DB0 to DB7 |

|

8080-series |

|

|

|

|

|

|

|

|

|

|

|

|

Table 10. Parallel Data Transfer |

|

|

|

||

|

|

|

|

|

|

|

||

Common |

6800-series |

8080-series |

|

|

|

|

||

|

|

|

|

|

|

Description |

|

|

RS |

E_RD |

RW_WR |

E_RD |

RW_WR |

|

|

||

(E) |

(RW) |

(/RD) |

(/WR) |

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

||

H |

H |

H |

L |

H |

|

Display data read out |

||

|

|

|

|

|

|

|

|

|

H |

H |

L |

H |

L |

|

Display data write |

|

|

|

|

|

|

|

|

|

||

L |

H |

H |

L |

H |

|

Register status read |

||

|

|

|

|

|

|

|||

L |

H |

L |

H |

L |

Writes to internal register (instruction) |

|||

|

|

|

|

|

|

|

|

|

13

132 SEG / 65 COM DRIVER & CONTROLLER FOR STN LCD |

PRELIMINARY SPEC. VER. 0.1 |

S6B0721 |

|

|

|

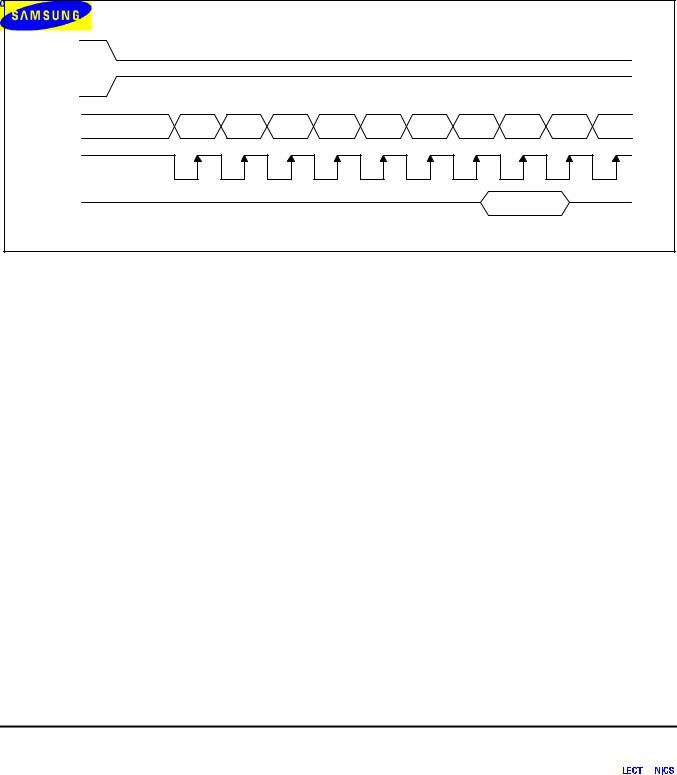

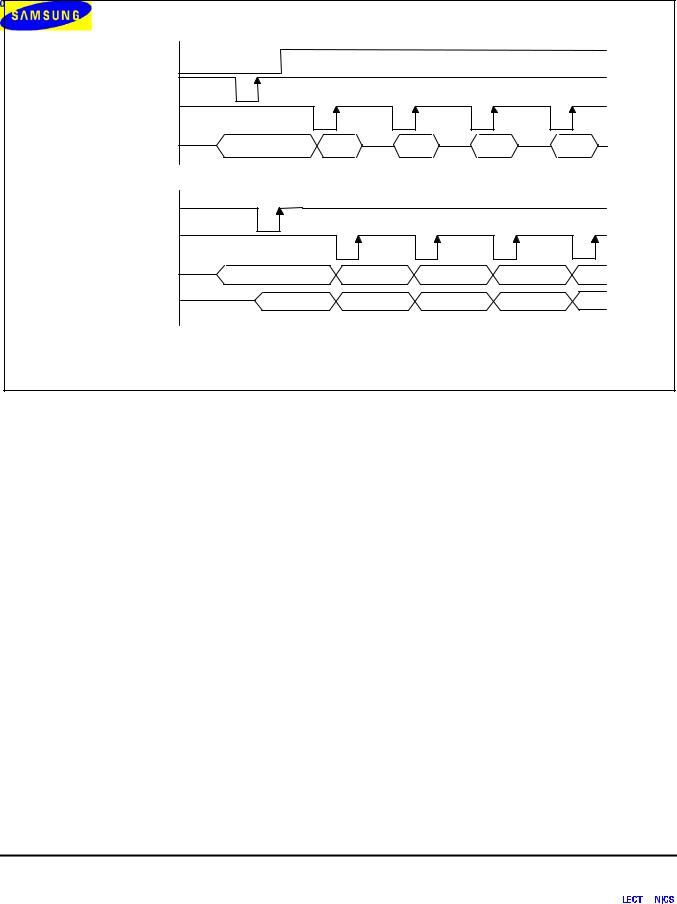

Serial Interface (PS = "L")

When the S6B0721 is active, serial data (DB7) and serial clock (DB6) inputs are enabled. And not active, the internal 8-bit shift register and the 3-bit counter are reset. Serial data can be read on the rising edge of serial clock going into DB6 and processed as 8-bit parallel data on the eighth serial clock. Serial data input is display data when RS is high and control data when RS is low. Since the clock signal (DB6) is easy to be affected by the external noise caused by the line length, the operation check on the actual machine is recommended.

CS1B |

|

|

|

|

|

|

|

|

|

|

CS2 |

|

|

|

|

|

|

|

|

|

|

SID |

DB7 |

DB6 |

DB5 |

DB4 |

DB3 |

DB2 |

DB1 |

DB0 |

DB7 |

DB6 |

SCLK |

|

|

|

|

|

|

|

|

|

|

RS |

|

|

|

|

|

|

|

|

|

|

Figure 3. Serial Interface Timing

Busy Flag

The Busy Flag indicates whether the S6B0721 is operating or not. When DB7 is “H” in read status operation, this device is in busy status and will accept only read status instruction. If the cycle time is correct, the microprocessor needs not to check this flag before each instruction, which improves the MPU performance.

14

S6B0721 |

PRELIMINARY SPEC. VER. 0.1 |

132 SEG / 65 COM DRIVER & CONTROLLER FOR STN LCD |

|

|

|

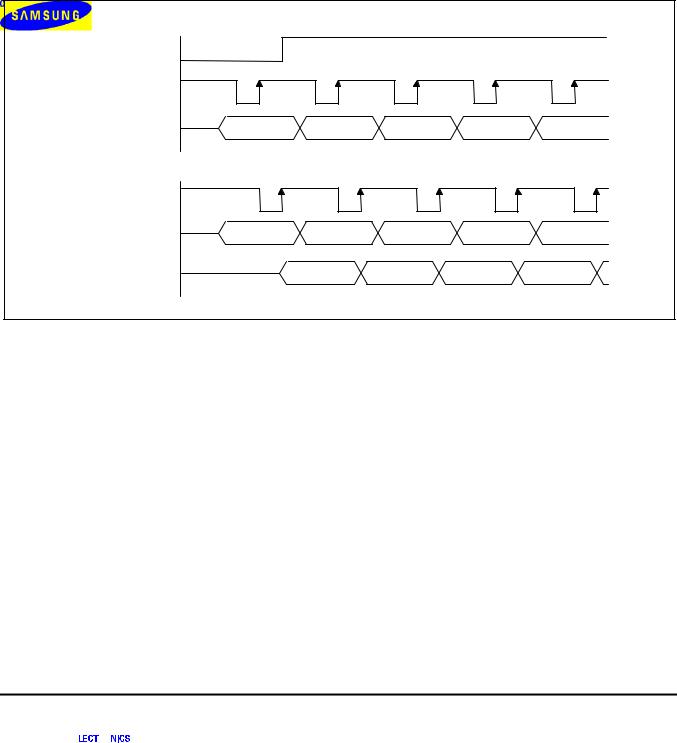

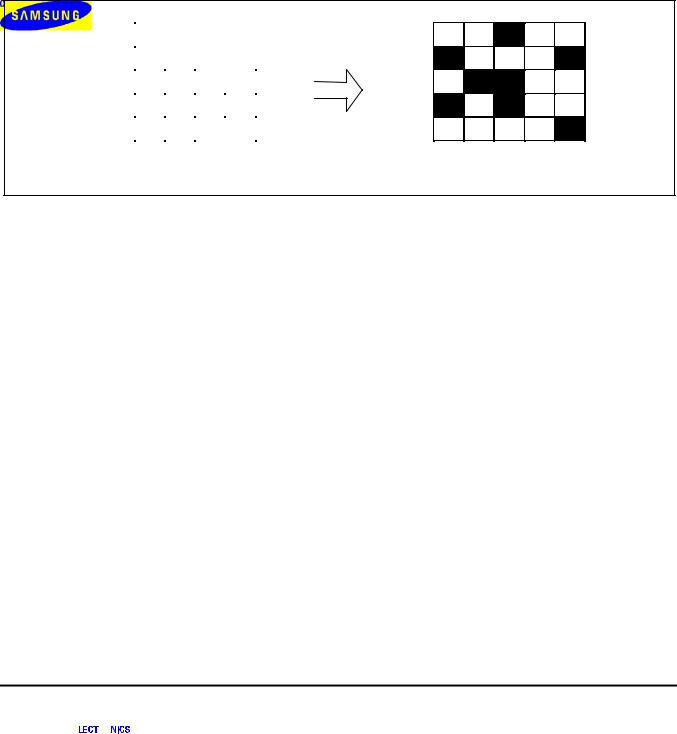

Data Transfer

The S6B0721 uses bus holder and internal data bus for Data Transfer with the MPU. When writing data from the MPU to on-chip RAM, data is automatically transferred from the bus holder to the RAM as shown in figure 4. And when reading data from on-chip RAM to the MPU, the data for the initial read cycle is stored in the bus holder (dummy read) and the MPU reads this stored data from bus holder for the next data read cycle as shown in figure 5. This means that a dummy read cycle must be inserted between each pair of address sets when a sequence of address sets is executed. Therefore, the data of the specified address cannot be output with the read display data instruction right after the address sets, but can be output at the second read of data.

MPU signals

RS |

|

|

|

|

|

/WR |

|

|

|

|

|

DB0 to DB7 |

N |

D(N) |

D(N+1) |

D(N+2) |

D(N+3) |

Internal signals

/WR |

|

|

|

|

|

BUS HOLDER |

N |