NXP PDTC115EE, PDTC115EEF, PDTC115EK, PDTC115EM, PDTC115ES Schematic [ru]

...

DISCRETE SEMICONDUCTORS

DATA SHEET

PDTC115E series

NPN resistor-equipped transistors; R1 = 100 kΩ, R2 = 100 kΩ

Product data sheet |

2004 Aug 06 |

Supersedes data of 2004 Apr 06 |

|

NXP Semiconductors |

Product data sheet |

|

|

|

|

NPN resistor-equipped transistors;

Ω Ω PDTC115E series

R1 = 100 k , R2 = 100 k

FEATURES

•Built-in bias resistors

•Simplified circuit design

•Reduction of component count

•Reduced pick and place costs.

APPLICATIONS

•General purpose switching and amplification

•Inverter and interface circuits

•Circuit driver.

PRODUCT OVERVIEW

QUICK REFERENCE DATA

SYMBOL |

PARAMETER |

TYP. |

MAX. |

UNIT |

|

|

|

|

|

VCEO |

collector-emitter |

− |

50 |

V |

|

voltage |

|

|

|

IO |

output current (DC) |

− |

20 |

mA |

R1 |

bias resistor |

100 |

− |

kΩ |

R2 |

bias resistor |

100 |

− |

kΩ |

|

|

|

|

|

DESCRIPTION

NPN resistor equipped transistor (see “Simplified outline, symbol and pinning” for package details).

TYPE NUMBER |

PACKAGE |

|

MARKING CODE |

PNP COMPLEMENT |

|

|

|

|

|||

PHILIPS |

|

EIAJ |

|||

|

|

|

|

||

|

|

|

|

|

|

PDTC115EE |

SOT416 |

|

SC-75 |

46 |

PDTA115EE |

PDTC115EEF |

SOT490 |

|

SC-89 |

49 |

PDTA115EEF |

|

|

|

|

|

|

PDTC115EK |

SOT346 |

|

SC-59 |

56 |

PDTA115EK |

PDTC115EM |

SOT883 |

|

SC-101 |

DV |

PDTA115EM |

PDTC115ES |

SOT54 (TO-92) |

|

SC-43 |

TC115E |

PDTA115ES |

|

|

|

|

|

|

PDTC115ET |

SOT23 |

|

− |

*44(1) |

PDTA115ET |

PDTC115EU |

SOT323 |

|

SC-70 |

*15(1) |

PDTA115EU |

Note

1.* = p: Made in Hong Kong.

*= t: Made in Malaysia.

*= W: Made in China.

2004 Aug 06 |

2 |

NXP Semiconductors |

Product data sheet |

|

|

NPN resistor-equipped transistors;

Ω Ω PDTC115E series R1 = 100 k , R2 = 100 k

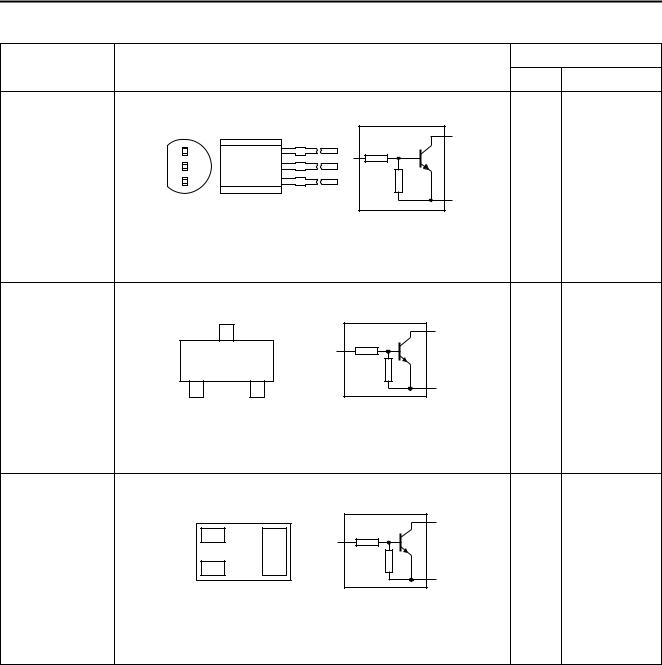

SIMPLIFIED OUTLINE, SYMBOL AND PINNING |

|

|

|

|

|

TYPE NUMBER |

SIMPLIFIED OUTLINE AND SYMBOL |

|

|

PINNING |

|

|

PIN |

DESCRIPTION |

|||

|

|

|

|

||

PDTC115ES |

|

|

|

1 |

base |

|

handbook, halfpage |

|

|

2 |

collector |

|

|

2 |

3 |

emitter |

|

|

1 |

R1 |

|

||

|

|

|

|

||

|

2 |

1 |

|

|

|

|

|

|

|

|

|

|

3 |

R2 |

|

|

|

|

|

|

3 |

|

|

|

|

MAM364 |

|

|

|

PDTC115EE |

|

|

|

1 |

base |

PDTC115EEF |

|

3 |

3 |

2 |

emitter |

PDTC115EK |

handbook, halfpage |

3 |

collector |

||

|

|

|

|

|

|

PDTC115ET |

|

|

R1 |

|

|

|

|

1 |

|

|

|

PDTC115EU |

|

|

R2 |

|

|

|

1 |

2 |

2 |

|

|

|

Top view |

|

MDB269 |

|

|

PDTC115EM |

|

1 |

base |

|

|

2 |

emitter |

handbook, halfpage |

3 |

3 |

collector |

|

|

|

|

2 |

R1 |

|

|

|

1 |

|

|

|

3 |

|

|

1 |

R2 |

|

|

|

|

|

|

|

2 |

|

|

bottom view |

|

|

|

|

MHC506 |

|

|

2004 Aug 06 |

3 |

NXP Semiconductors |

Product data sheet |

|

|

NPN resistor-equipped transistors;

Ω Ω PDTC115E series R1 = 100 k , R2 = 100 k

ORDERING INFORMATION

TYPE NUMBER |

|

PACKAGE |

|

|

|

|

|

||

NAME |

DESCRIPTION |

VERSION |

||

|

||||

|

|

|

|

|

PDTC115EE |

− |

plastic surface mounted package; 3 leads |

SOT416 |

|

PDTC115EEF |

− |

plastic surface mounted package; 3 leads |

SOT490 |

|

|

|

|

|

|

PDTC115EK |

− |

plastic surface mounted package; 3 leads |

SOT346 |

|

PDTC115EM |

− |

leadless ultra small plastic package; 3 solder lands; body |

SOT883 |

|

|

|

1.0 × 0.6 × 0.5 mm |

|

|

PDTC115ES |

− |

plastic single-ended leaded (through hole) package; 3 leads |

SOT54 |

|

PDTC115ET |

− |

plastic surface mounted package; 3 leads |

SOT23 |

|

PDTC115EU |

− |

plastic surface mounted package; 3 leads |

SOT323 |

|

|

|

|

|

LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC 60134).

SYMBOL |

PARAMETER |

CONDITIONS |

MIN. |

MAX. |

UNIT |

|

|

|

|

|

|

VCBO |

collector-base voltage |

open emitter |

− |

50 |

V |

VCEO |

collector-emitter voltage |

open base |

− |

50 |

V |

VEBO |

emitter-base voltage |

open collector |

− |

10 |

V |

VI |

input voltage |

|

|

|

|

|

positive |

|

− |

+40 |

V |

|

negative |

|

− |

−10 |

V |

|

|

|

|

|

|

IO |

output current (DC) |

|

− |

20 |

mA |

ICM |

peak collector current |

|

− |

100 |

mA |

Ptot |

total power dissipation |

Tamb ≤ 25 °C |

|

|

|

|

SOT54 |

note 1 |

− |

500 |

mW |

|

SOT23 |

note 1 |

− |

250 |

mW |

|

SOT346 |

note 1 |

− |

250 |

mW |

|

SOT323 |

note 1 |

− |

200 |

mW |

|

SOT416 |

note 1 |

− |

150 |

mW |

|

SOT883 |

notes 2 and 3 |

− |

250 |

mW |

|

SOT490 |

notes 1 and 2 |

− |

250 |

mW |

Tstg |

storage temperature |

|

−65 |

+150 |

°C |

Tj |

junction temperature |

|

− |

150 |

°C |

Tamb |

operating ambient |

|

−65 |

+150 |

°C |

|

temperature |

|

|

|

|

Notes |

|

|

|

|

|

1.Refer to standard mounting conditions.

2.Reflow soldering is the only recommended soldering method.

3.Refer to SOT883 standard mounting conditions; FR4 with 60 μm copper strip line.

2004 Aug 06 |

4 |

NXP Semiconductors |

Product data sheet |

|

|

NPN resistor-equipped transistors;

Ω Ω PDTC115E series R1 = 100 k , R2 = 100 k

THERMAL CHARACTERISTICS

SYMBOL |

PARAMETER |

CONDITIONS |

VALUE |

UNIT |

|

|

|

|

|

Rth(j-a) |

thermal resistance from junction to ambient |

in free air |

|

|

|

SOT54 |

note 1 |

250 |

K/W |

|

SOT23 |

note 1 |

500 |

K/W |

|

SOT346 |

note 1 |

500 |

K/W |

|

SOT323 |

note 1 |

625 |

K/W |

|

SOT416 |

note 1 |

833 |

K/W |

|

SOT833 |

notes 2 and 3 |

500 |

K/W |

|

SOT490 |

notes 1 and 2 |

500 |

K/W |

|

|

|

|

|

Notes

1.Refer to standard mounting conditions.

2.Reflow soldering is the only recommended soldering method.

3.Refer to SOT883 standard mounting conditions; FR4 with 60 μm copper strip line.

CHARACTERISTICS

Tamb = 25 °C unless otherwise specified.

SYMBOL |

PARAMETER |

CONDITIONS |

MIN. |

TYP. |

MAX. |

UNIT |

|

|

|

|

|

|

|

ICBO |

collector-base cut-off current |

VCB = 50 V; IE = 0 A |

− |

− |

100 |

nA |

ICEO |

collector-emitter cut-off current |

VCE = 30 V; IB = 0 A |

− |

− |

1 |

μA |

|

|

VCE = 30 V; IB = 0 A; Tj = 150 °C |

− |

− |

50 |

μA |

IEBO |

emitter-base cut-off current |

VEB = 5 V; IC = 0 A |

− |

− |

50 |

μA |

hFE |

DC current gain |

VCE = 5 V; IC = 5 mA |

80 |

− |

− |

|

VCEsat |

collector-emitter saturation voltage |

IC = 5 mA; IB = 0.25 mA |

− |

− |

150 |

mV |

Vi(off) |

input-off voltage |

IC = 100 μA; VCE = 5 V |

− |

1.1 |

0.5 |

V |

Vi(on) |

input-on voltage |

IC = 1 mA; VCE = 0.3 V |

3 |

1.5 |

− |

V |

R1 |

input resistor |

|

70 |

100 |

130 |

kΩ |

R2 |

resistor ratio |

|

0.8 |

1 |

1.2 |

|

------- |

|

|

|

|

|

|

R1 |

|

|

|

|

|

|

Cc |

collector capacitance |

IE = ie = 0 A; VCB = 10 V; |

− |

− |

2.5 |

pF |

|

|

f = 1 MHz |

|

|

|

|

2004 Aug 06 |

5 |

Loading...

Loading...