NXP LPC178x, LPC177x User Manual

LPC178x/7x

32-bit ARM Cortex-M3 microcontroller; up to 512 kB flash and 96 kB SRAM; USB Device/Host/OTG; Ethernet; LCD; EMC

Rev. 5 — 9 September 2014 |

Product data sheet |

1. General description

The LPC178x/7x is an ARM Cortex-M3 based microcontroller for embedded applications requiring a high level of integration and low power dissipation.

The ARM Cortex-M3 is a next generation core that offers better performance than the ARM7 at the same clock rate and other system enhancements such as modernized debug features and a higher level of support block integration. The ARM Cortex-M3 CPU incorporates a 3-stage pipeline and has a Harvard architecture with separate local instruction and data buses, as well as a third bus with slightly lower performance for peripherals. The ARM Cortex-M3 CPU also includes an internal prefetch unit that supports speculative branches.

The LPC178x/7x adds a specialized flash memory accelerator to accomplish optimal performance when executing code from flash. The LPC178x/7x operates at up to 120 MHz CPU frequency.

The peripheral complement of the LPC178x/7x includes up to 512 kB of flash program memory, up to 96 kB of SRAM data memory, up to 4032 byte of EEPROM data memory, External Memory Controller (EMC), LCD (LPC178x only), Ethernet, USB Device/Host/OTG, a General Purpose DMA controller, five UARTs, three SSP controllers, three I2C-bus interfaces, a Quadrature Encoder Interface, four general purpose timers, two general purpose PWMs with six outputs each and one motor control PWM, an ultra-low power RTC with separate battery supply and event recorder, a windowed watchdog timer, a CRC calculation engine, up to 165 general purpose I/O pins, and more.

The analog peripherals include one eight-channel 12-bit ADC and a 10-bit DAC.

The pinout of LPC178x/7x is intended to allow pin function compatibility with the LPC24xx and LPC23xx.

For additional documentation, see Section 18 “References”.

2.Features and benefits

Functional replacement for the LPC23xx and LPC24xx family devices.

System:

ARM Cortex-M3 processor, running at frequencies of up to 120 MHz. A Memory Protection Unit (MPU) supporting eight regions is included.

ARM Cortex-M3 built-in Nested Vectored Interrupt Controller (NVIC).

NXP Semiconductors |

LPC178x/7x |

|

32-bit ARM Cortex-M3 microcontroller |

Multilayer AHB matrix interconnect provides a separate bus for each AHB master. AHB masters include the CPU, USB, Ethernet, and the General Purpose DMA controller. This interconnect provides communication with no arbitration delays unless two masters attempt to access the same slave at the same time.

Split APB bus allows for higher throughput with fewer stalls between the CPU and DMA. A single level of write buffering allows the CPU to continue without waiting for completion of APB writes if the APB was not already busy.

Cortex-M3 system tick timer, including an external clock input option.

Standard JTAG test/debug interface as well as Serial Wire Debug and Serial WireTrace Port options.

Embedded Trace Macrocell (ETM) module supports real-time trace.

Boundary scan for simplified board testing.

Non-maskable Interrupt (NMI) input.

Memory:

Up to 512 kB on-chip flash program memory with In-System Programming (ISP) and In-Application Programming (IAP) capabilities. The combination of an enhanced flash memory accelerator and location of the flash memory on the CPU local code/data bus provides high code performance from flash.

Up to 96 kB on-chip SRAM includes:

64 kB of main SRAM on the CPU with local code/data bus for high-performance CPU access.

Two 16 kB peripheral SRAM blocks with separate access paths for higher throughput. These SRAM blocks may be used for DMA memory as well as for general purpose instruction and data storage.

Up to 4032 byte on-chip EEPROM.

LCD controller, supporting both Super-Twisted Nematic (STN) and Thin-Film Transistors (TFT) displays.

Dedicated DMA controller.

Selectable display resolution (up to 1024 768 pixels).

Supports up to 24-bit true-color mode.

External Memory Controller (EMC) provides support for asynchronous static memory devices such as RAM, ROM and flash, as well as dynamic memories such as single data rate SDRAM with an SDRAM clock of up to 80 MHz.

Eight channel General Purpose DMA controller (GPDMA) on the AHB multilayer matrix that can be used with the SSP, I2S, UART, CRC engine, Analog-to-Digital and Digital-to-Analog converter peripherals, timer match signals, GPIO, and for memory-to-memory transfers.

Serial interfaces:

Ethernet MAC with MII/RMII interface and associated DMA controller. These functions reside on an independent AHB.

USB 2.0 full-speed dual-port device/host/OTG controller with on-chip PHY and associated DMA controller.

Five UARTs with fractional baud rate generation, internal FIFO, DMA support, and RS-485/EIA-485 support. One UART (UART1) has full modem control I/O, and one UART (USART4) supports IrDA, synchronous mode, and a smart card mode conforming to ISO7816-3.

Three SSP controllers with FIFO and multi-protocol capabilities. The SSP controllers can be used with the GPDMA.

LPC178X_7X |

All information provided in this document is subject to legal disclaimers. |

© NXP Semiconductors N.V. 2014. All rights reserved. |

Product data sheet |

Rev. 5 — 9 September 2014 |

2 of 122 |

NXP Semiconductors |

LPC178x/7x |

|

32-bit ARM Cortex-M3 microcontroller |

Three enhanced I2C-bus interfaces, one with a true open-drain output supporting the full I2C-bus specification and Fast-mode Plus with data rates of 1 Mbit/s, two with standard port pins. Enhancements include multiple address recognition and monitor mode.

I2S-bus (Inter-IC Sound) interface for digital audio input or output. It can be used with the GPDMA.

CAN controller with two channels.

Digital peripherals:

SD/MMC memory card interface.

Up to 165 General Purpose I/O (GPIO) pins depending on the packaging with configurable pull-up/down resistors, open-drain mode, and repeater mode. All GPIOs are located on an AHB bus for fast access and support Cortex-M3 bit-banding. GPIOs can be accessed by the General Purpose DMA Controller. Any pin of ports 0 and 2 can be used to generate an interrupt.

Two external interrupt inputs configurable as edge/level sensitive. All pins on port 0 and port 2 can be used as edge sensitive interrupt sources.

Four general purpose timers/counters with a total of eight capture inputs and ten compare outputs. Each timer block has an external count input. Specific timer events can be selected to generate DMA requests.

Quadrature encoder interface that can monitor one external quadrature encoder.

Two standard PWM/timer blocks with external count input option.

One motor control PWM with support for three-phase motor control.

Real-Time Clock (RTC) with a separate power domain. The RTC is clocked by a dedicated RTC oscillator. The RTC block includes 20 bytes of battery-powered backup registers, allowing system status to be stored when the rest of the chip is powered off. Battery power can be supplied from a standard 3 V lithium button cell. The RTC will continue working when the battery voltage drops to as low as 2.1 V. An RTC interrupt can wake up the CPU from any reduced power mode.

Event Recorder that can capture the clock value when an event occurs on any of three inputs. The event identification and the time it occurred are stored in registers. The Event Recorder is located in the RTC power domain and can therefore operate as long as there is RTC power.

Windowed Watchdog Timer (WWDT). Windowed operation, dedicated internal oscillator, watchdog warning interrupt, and safety features.

CRC Engine block can calculate a CRC on supplied data using one of three standard polynomials. The CRC engine can be used in conjunction with the DMA controller to generate a CRC without CPU involvement in the data transfer.

Analog peripherals:

12-bit Analog-to-Digital Converter (ADC) with input multiplexing among eight pins, conversion rates up to 400 kHz, and multiple result registers. The 12-bit ADC can be used with the GPDMA controller.

10-bit Digital-to-Analog Converter (DAC) with dedicated conversion timer and GPDMA support.

Power control:

Four reduced power modes: Sleep, Deep-sleep, Power-down, and Deep power-down.

LPC178X_7X |

All information provided in this document is subject to legal disclaimers. |

© NXP Semiconductors N.V. 2014. All rights reserved. |

Product data sheet |

Rev. 5 — 9 September 2014 |

3 of 122 |

NXP Semiconductors |

LPC178x/7x |

|

32-bit ARM Cortex-M3 microcontroller |

The Wake-up Interrupt Controller (WIC) allows the CPU to automatically wake up from any priority interrupt that can occur while the clocks are stopped in Deep-sleep, Power-down, and Deep power-down modes.

Processor wake-up from Power-down mode via any interrupt able to operate during Power-down mode (includes external interrupts, RTC interrupt, PORT0/2 pin interrupt, and NMI).

Brownout detect with separate threshold for interrupt and forced reset.

On-chip Power-On Reset (POR).

Clock generation:

Clock output function that can reflect the main oscillator clock, IRC clock, RTC clock, CPU clock, USB clock, or the watchdog timer clock.

On-chip crystal oscillator with an operating range of 1 MHz to 25 MHz.

12 MHz Internal RC oscillator (IRC) trimmed to 1% accuracy that can optionally be used as a system clock.

An on-chip PLL allows CPU operation up to the maximum CPU rate without the need for a high-frequency crystal. May be run from the main oscillator or the internal RC oscillator.

A second, dedicated PLL may be used for USB interface in order to allow added flexibility for the Main PLL settings.

Versatile pin function selection feature allows many possibilities for using on-chip peripheral functions.

Unique device serial number for identification purposes.

Single 3.3 V power supply (2.4 V to 3.6 V). Temperature range of 40 C to 85 C.

Available as LQFP208, TFBGA208, TFBGA180, and LQFP144 package.

3.Applications

Communications:

Point-of-sale terminals, web servers, multi-protocol bridges

Industrial/Medical:

Automation controllers, application control, robotics control, HVAC, PLC, inverters, circuit breakers, medical scanning, security monitoring, motor drive, video intercom

Consumer/Appliance:

Audio, MP3 decoders, alarm systems, displays, printers, scanners, small appliances, fitness equipment

Automotive:

After-market, car alarms, GPS/fleet monitors

LPC178X_7X |

All information provided in this document is subject to legal disclaimers. |

© NXP Semiconductors N.V. 2014. All rights reserved. |

Product data sheet |

Rev. 5 — 9 September 2014 |

4 of 122 |

NXP Semiconductors |

LPC178x/7x |

||

|

|

32-bit ARM Cortex-M3 microcontroller |

|

4. Ordering information |

|

||

Table 1. Ordering information |

|

|

|

|

|

|

|

Type number |

Package |

|

|

|

|

|

|

|

Name |

Description |

Version |

LPC1788 |

|

|

|

|

|

|

|

LPC1788FBD208 |

LQFP208 |

plastic low profile quad flat package; 208 leads; body 28 28 1.4 mm |

SOT459-1 |

|

|

|

|

LPC1788FET208 |

TFBGA208 |

plastic thin fine-pitch ball grid array package; 208 balls; body |

SOT950-1 |

|

|

15 ´ 15 ´ 0.7 mm |

|

|

|

|

|

LPC1788FET180 |

TFBGA180 |

thin fine-pitch ball grid array package; 180 balls; body 12 ´ 12 ´ 0.8 mm |

SOT570-3 |

|

|

|

|

LPC1788FBD144 |

LQFP144 |

plastic low profile quad flat package; 144 leads; body 20 20 1.4 mm |

SOT486-1 |

|

|

|

|

LPC1787 |

|

|

|

|

|

|

|

LPC1787FBD208 |

LQFP208 |

plastic low profile quad flat package; 208 leads; body 28 28 1.4 mm |

SOT459-1 |

|

|

|

|

LPC1786 |

|

|

|

|

|

|

|

LPC1786FBD208 |

LQFP208 |

plastic low profile quad flat package; 208 leads; body 28 28 1.4 mm |

SOT459-1 |

|

|

|

|

LPC1785 |

|

|

|

|

|

|

|

LPC1785FBD208 |

LQFP208 |

plastic low profile quad flat package; 208 leads; body 28 28 1.4 mm |

SOT459-1 |

|

|

|

|

LPC1778 |

|

|

|

|

|

|

|

LPC1778FBD208 |

LQFP208 |

plastic low profile quad flat package; 208 leads; body 28 28 1.4 mm |

SOT459-1 |

|

|

|

|

LPC1778FET208 |

TFBGA208 |

plastic thin fine-pitch ball grid array package; 208 balls; body |

SOT950-1 |

|

|

15 ´ 15 ´ 0.7 mm |

|

|

|

|

|

LPC1778FET180 |

TFBGA180 |

thin fine-pitch ball grid array package; 180 balls; body 12 ´ 12 ´ 0.8 mm |

SOT570-3 |

|

|

|

|

LPC1778FBD144 |

LQFP144 |

plastic low profile quad flat package; 144 leads; body 20 20 1.4 mm |

SOT486-1 |

|

|

|

|

LPC1777 |

|

|

|

|

|

|

|

LPC1777FBD208 |

LQFP208 |

plastic low profile quad flat package; 208 leads; body 28 28 1.4 mm |

SOT459-1 |

|

|

|

|

LPC1776 |

|

|

|

|

|

|

|

LPC1776FBD208 |

LQFP208 |

plastic low profile quad flat package; 208 leads; body 28 28 1.4 mm |

SOT459-1 |

|

|

|

|

LPC1776FET180 |

TFBGA180 |

thin fine-pitch ball grid array package; 180 balls; body 12 ´ 12 ´ 0.8 mm |

SOT570-3 |

|

|

|

|

LPC1774 |

|

|

|

|

|

|

|

LPC1774FBD208 |

LQFP208 |

plastic low profile quad flat package; 208 leads; body 28 28 1.4 mm |

SOT459-1 |

|

|

|

|

LPC1774FBD144 |

LQFP144 |

plastic low profile quad flat package; 144 leads; body 20 20 1.4 mm |

SOT486-1 |

|

|

|

|

LPC178X_7X |

All information provided in this document is subject to legal disclaimers. |

© NXP Semiconductors N.V. 2014. All rights reserved. |

Product data sheet |

Rev. 5 — 9 September 2014 |

5 of 122 |

NXP Semiconductors |

LPC178x/7x |

|

32-bit ARM Cortex-M3 microcontroller |

Table 2. LPC178x/7x ordering options

All parts include two CAN channels, three SSP interfaces, three I2C interfaces, one I2S interface, DAC, and an 8-channel 12-bit ADC.

Type number |

Flash |

Main |

Peripheral |

Total |

EEPROM |

Ethernet |

USB |

UART |

EMC |

LCD |

QEI |

SD/ |

|

(kB) |

SRAM |

SRAM |

SRAM |

(byte) |

|

|

|

bus |

|

|

MMC |

|

|

(kB) |

(kB) |

(kB) |

|

|

|

|

width |

|

|

|

|

|

|

|

|

|

|

|

|

(bit) |

|

|

|

|

|

|

|

|

|

|

|

|

[1] |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LPC178x |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LPC1788FBD208 |

512 |

64 |

16 2 |

96 |

4032 |

Y |

H/O/D |

5 |

32 |

Y |

Y |

Y |

|

|

|

|

|

|

|

|

|

|

|

|

|

LPC1788FET208 |

512 |

64 |

16 2 |

96 |

4032 |

Y |

H/O/D |

5 |

32 |

Y |

Y |

Y |

|

|

|

|

|

|

|

|

|

|

|

|

|

LPC1788FET180 |

512 |

64 |

16 2 |

96 |

4032 |

Y |

H/O/D |

5 |

16 |

Y |

Y |

Y |

|

|

|

|

|

|

|

|

|

|

|

|

|

LPC1788FBD144 |

512 |

64 |

16 2 |

96 |

4032 |

Y |

H/O/D |

5 |

8 |

Y |

Y |

Y |

|

|

|

|

|

|

|

|

|

|

|

|

|

LPC1787FBD208 |

512 |

64 |

16 2 |

96 |

4032 |

N |

H/O/D |

5 |

32 |

Y |

Y |

Y |

|

|

|

|

|

|

|

|

|

|

|

|

|

LPC1786FBD208 |

256 |

64 |

16 |

80 |

4032 |

Y |

H/O/D |

5 |

32 |

Y |

Y |

Y |

|

|

|

|

|

|

|

|

|

|

|

|

|

LPC1785FBD208 |

256 |

64 |

16 |

80 |

4032 |

N |

H/O/D |

5 |

32 |

Y |

N |

Y |

|

|

|

|

|

|

|

|

|

|

|

|

|

LPC177x |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LPC1778FBD208 |

512 |

64 |

16 2 |

96 |

4032 |

Y |

H/O/D |

5 |

32 |

N |

Y |

Y |

|

|

|

|

|

|

|

|

|

|

|

|

|

LPC1778FET208 |

512 |

64 |

16 2 |

96 |

4032 |

Y |

H/O/D |

5 |

32 |

N |

Y |

Y |

|

|

|

|

|

|

|

|

|

|

|

|

|

LPC1778FET180 |

512 |

64 |

16 2 |

96 |

4032 |

Y |

H/O/D |

5 |

16 |

N |

Y |

Y |

|

|

|

|

|

|

|

|

|

|

|

|

|

LPC1778FBD144 |

512 |

64 |

16 2 |

96 |

4032 |

Y |

H/O/D |

5 |

8 |

N |

Y |

Y |

|

|

|

|

|

|

|

|

|

|

|

|

|

LPC1777FBD208 |

512 |

64 |

16 2 |

96 |

4032 |

N |

H/O/D |

5 |

32 |

N |

Y |

Y |

|

|

|

|

|

|

|

|

|

|

|

|

|

LPC1776FBD208 |

256 |

64 |

16 |

80 |

4032 |

Y |

H/O/D |

5 |

32 |

N |

Y |

Y |

|

|

|

|

|

|

|

|

|

|

|

|

|

LPC1776FET180 |

256 |

64 |

16 |

80 |

4032 |

Y |

H/O/D |

5 |

16 |

N |

Y |

Y |

|

|

|

|

|

|

|

|

|

|

|

|

|

LPC1774FBD208 |

128 |

32 |

8 |

40 |

2048 |

N |

D |

5 |

32 |

N |

N |

N |

|

|

|

|

|

|

|

|

|

|

|

|

|

LPC1774FBD144 |

128 |

32 |

8 |

40 |

2048 |

N |

D |

4[2] |

8 |

N |

N |

N |

[1]Maximum data bus width of the External Memory Controller (EMC) depends on package size. Smaller widths may be used.

[2]USART4 not available.

LPC178X_7X |

All information provided in this document is subject to legal disclaimers. |

© NXP Semiconductors N.V. 2014. All rights reserved. |

Product data sheet |

Rev. 5 — 9 September 2014 |

6 of 122 |

NXP Semiconductors |

LPC178x/7x |

|

32-bit ARM Cortex-M3 microcontroller |

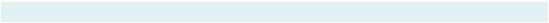

5. Block diagram

debug |

JTAG |

|

|

|

|

|

|

|

port |

|

interface |

|

|

|

|

|

|

EMULATION TRACE MODULE |

|

TEST/DEBUG |

|

|

LPC178x/7x |

|

|

|

|

|

|

|

|

|

CLOCK |

||

|

INTERFACE |

|

|

|

|

|

||

|

|

|

|

|

|

GENERATION, |

||

|

|

|

|

|

|

|

||

|

|

|

|

|

|

POWER CONTROL, |

||

|

ARM |

MPU |

|

GPDMA |

ETHERNET(1) |

USB |

SYSTEM |

|

CORTEX-M3 |

CONTROLLER |

DEVICE/ |

FUNCTIONS |

|||||

|

|

|

|

|

HOST(1)/OTG(1) |

clocks and |

||

|

|

|

|

|

|

|

|

|

|

I-code D-code |

system |

|

master |

master |

master |

controls |

|

slave |

bus |

bus |

bus |

|

|

|

slave |

|

|

|

|

|

|

|

|||

EMC |

|

|

|

|

|

|

|

ROM |

slave |

|

|

|

|

|

|

slave |

|

|

|

|

|

|

|

|

|

|

LCD(1) |

|

|

MULTILAYER AHB MATRIX |

|

SRAM |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

96/80/40 kB |

|

slave |

slave |

slave |

slave |

slave |

|

||

|

|

|

|

|

|

|||

HIGH-SPEED |

CRC |

|

AHB TO |

AHB TO |

FLASH |

|

||

|

GPIO |

|

|

4032 B/ |

||||

|

|

|

|

APB |

APB |

ACCELERATOR |

||

|

|

|

|

|

2048 B |

|||

|

|

|

|

|

BRIDGE 0 |

BRIDGE 1 |

FLASH |

|

|

APB slave group 0 |

|

EEPROM |

|||||

|

|

|

|

512/256/128/64 kB |

|

|||

|

|

|

|

|

|

|

|

|

|

|

SSP1 |

|

|

|

|

APB slave group 1 |

|

|

|

UART0/1 |

|

|

|

|

SSP0/2 |

|

|

|

|

|

|

|

|

|

|

|

|

I2C0/1 |

|

|

|

|

UART2/3 |

|

|

|

|

|

|

|

|

|

|

|

|

CAN 0/1 |

|

|

|

|

USART4(1) |

|

|

|

|

|

|

|

|

|

|

|

|

TIMER 0/1 |

|

|

|

|

I2C2 |

|

|

|

|

|

|

|

|

|

|

|

WINDOWED WDT |

|

|

|

|

SD/MMC(1) |

|

|

|

|

|

|

|

|

|

||

|

|

PWM0/1 |

|

|

|

|

TIMER2/3 |

|

|

|

|

|

|

|

|

|

|

|

|

12-bit ADC |

|

|

|

|

QUADRATURE ENCODER(1) |

|

|

|

|

|

|

|

|

|

|

|

PIN CONNECT |

|

|

|

|

DAC |

|

|

|

|

|

|

|

|

|

||

GPIO INTERRUPT CONTROL |

|

|

|

I2S |

|

|||

|

|

|

|

|

||||

|

EVENT RECORDER |

|

|

|

|

MOTOR CONTROL PWM |

||

|

|

|

|

|

|

|

||

|

32 kHz |

RTC |

|

|

|

SYSTEM CONTROL |

||

OSCILLATOR |

|

|

|

|

|

|||

|

|

|

|

|

|

|||

|

BACKUP REGISTERS |

|

|

|

|

|

||

|

RTC POWER DOMAIN |

|

|

|

|

= connected to GPDMA |

||

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

002aaf528 |

(1) Not available on all parts. See Table 2.

Fig 1. Block diagram

LPC178X_7X |

All information provided in this document is subject to legal disclaimers. |

© NXP Semiconductors N.V. 2014. All rights reserved. |

Product data sheet |

Rev. 5 — 9 September 2014 |

7 of 122 |

NXP Semiconductors |

LPC178x/7x |

|

32-bit ARM Cortex-M3 microcontroller |

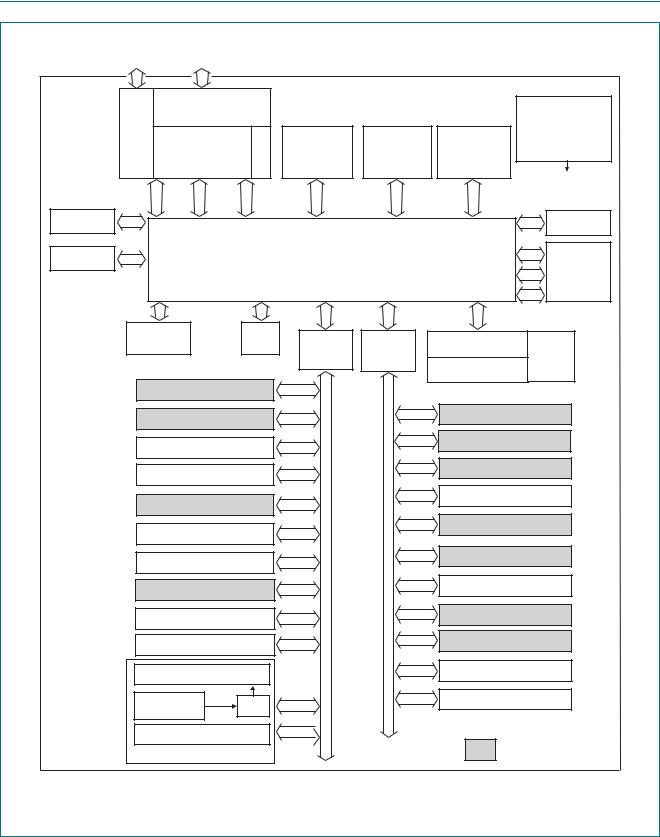

6.Pinning information

6.1Pinning

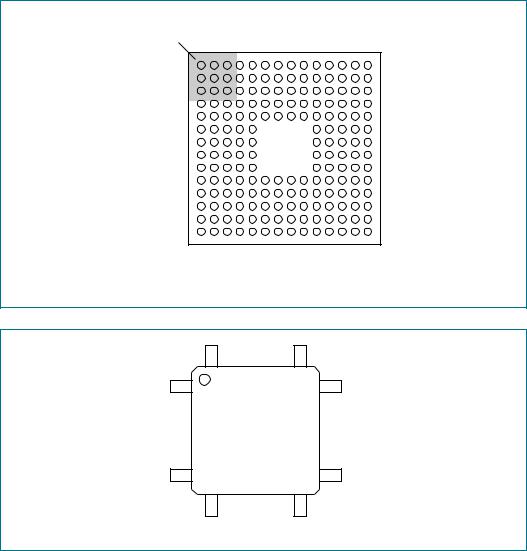

208 |

157 |

1 |

156 |

LPC178x/7xFBD208

52

53

104

105

002aaf518

Fig 2. Pin configuration (LQFP208)

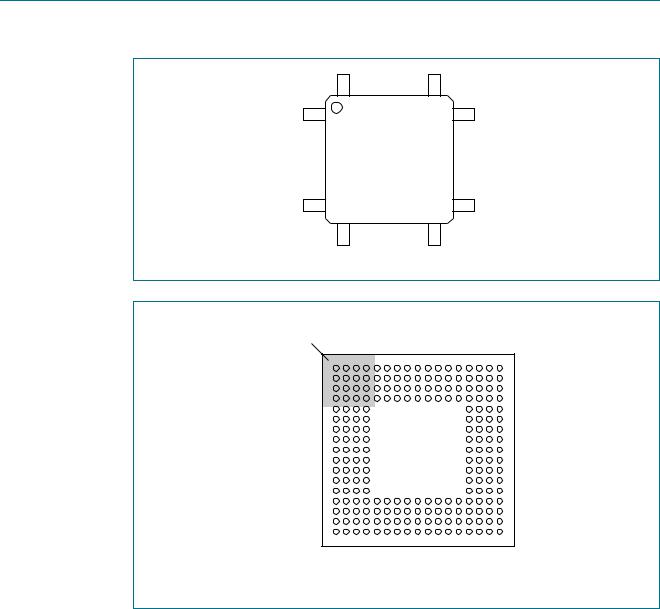

ball A1 |

|

|

|

|

|

|

|

|

index area |

2 |

4 |

6 |

8 |

10 12 |

14 16 |

|

|

1 |

3 |

5 |

7 |

9 |

11 |

13 |

15 |

17 |

A |

|

|

|

|

|

|

|

|

B |

|

|

|

|

|

|

|

|

C |

|

|

|

|

|

|

|

|

D |

|

|

|

|

|

|

|

|

E |

|

|

|

|

|

|

|

|

F |

|

|

|

|

|

|

|

|

G |

|

|

|

|

|

|

|

|

H |

|

|

LPC178x/7x |

|

|

|

||

J |

|

|

|

|

|

|||

K |

|

|

|

|

|

|

|

|

L |

|

|

|

|

|

|

|

|

M |

|

|

|

|

|

|

|

|

N |

|

|

|

|

|

|

|

|

P |

|

|

|

|

|

|

|

|

R |

|

|

|

|

|

|

|

|

T |

|

|

|

|

|

|

|

|

U |

|

|

|

|

|

|

|

|

002aaf529

Transparent top view

Fig 3. Pin configuration (TFBGA208)

LPC178X_7X |

All information provided in this document is subject to legal disclaimers. |

© NXP Semiconductors N.V. 2014. All rights reserved. |

Product data sheet |

Rev. 5 — 9 September 2014 |

8 of 122 |

NXP Semiconductors |

LPC178x/7x |

|

32-bit ARM Cortex-M3 microcontroller |

ball A1 |

LPC178x/7x |

index area |

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14

A

B

C

D

E

F

G

H

J

K

L

M

N

P

002aaf519

Transparent top view

Fig 4. Pin configuration (TFBGA180)

144 |

109 |

1 |

108 |

LPC178x/7x

36

37

Fig 5. Pin configuration (LQFP144)

72

73

002aaf520

6.2 Pin description

I/O pins on the LPC178x/7x are 5 V tolerant and have input hysteresis unless otherwise indicated in the table below. Crystal pins, power pins, and reference voltage pins are not 5 V tolerant. In addition, when pins are selected to be ADC inputs, they are no longer 5 V tolerant and the input voltage must be limited to the voltage at the ADC positive reference pin (VREFP).

All port pins Pn[m] are multiplexed, and the multiplexed functions appear in Table 3 in the order defined by the FUNC bits of the corresponding IOCON register up to the highest used function number. Each port pin can support up to eight multiplexed functions. IOCON register FUNC values which are reserved are noted as ‘R’ in the pin configuration table.

LPC178X_7X |

All information provided in this document is subject to legal disclaimers. |

© NXP Semiconductors N.V. 2014. All rights reserved. |

Product data sheet |

Rev. 5 — 9 September 2014 |

9 of 122 |

NXP Semiconductors |

LPC178x/7x |

|

32-bit ARM Cortex-M3 microcontroller |

Table 3. Pin description

Not all functions are available on all parts. See Table 2 (Ethernet, USB, LCD, QEI, SD/MMC, DAC pins) and Table 7 (EMC pins).

Symbol |

Pin LQFP208 |

Ball TFBGA208 |

Ball TFBGA180 |

Pin LQFP144 |

|

|

|

|

|

|

|

Description |

|

|

Reset state[1] |

|

|

Type[2] |

|

|

|

||||

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|||||||

P0[0] to |

|

|

|

|

|

|

|

|

I/O |

Port 0: Port 0 is a 32-bit I/O port with individual direction |

||

P0[31] |

|

|

|

|

|

|

|

|

|

|

|

controls for each bit. The operation of port 0 pins depends upon |

|

|

|

|

|

|

|

|

|

|

|

|

the pin function selected via the pin connect block. |

|

|

|

|

|

|

|

|

|

||||

P0[0] |

94 |

U15 |

M10 |

66 |

[3] |

I; |

I/O |

P0[0] — General purpose digital input/output pin. |

||||

|

|

|

|

|

|

PU |

|

|

|

|

||

|

|

|

|

|

|

I |

CAN_RD1 — CAN1 receiver input. |

|||||

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

O |

U3_TXD — Transmitter output for UART3. |

||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

I/O |

I2C1_SDA — I2C1 data input/output (this pin does not use a |

||

|

|

|

|

|

|

|

|

|

|

|

|

specialized I2C pad). |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

O |

U0_TXD — Transmitter output for UART0. |

||

|

|

|

|

|

|

|

|

|

||||

P0[1] |

96 |

T14 |

N11 |

67 |

[3] |

I; |

I/O |

P0[1] — General purpose digital input/output pin. |

||||

|

|

|

|

|

|

PU |

|

|

|

|

||

|

|

|

|

|

|

O |

CAN_TD1 — CAN1 transmitter output. |

|||||

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

I |

U3_RXD — Receiver input for UART3. |

||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

I/O |

I2C1_SCL — I2C1 clock input/output (this pin does not use a |

||

|

|

|

|

|

|

|

|

|

|

|

|

specialized I2C pad). |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

I |

U0_RXD — Receiver input for UART0. |

||

|

|

|

|

|

|

|

|

|

||||

P0[2] |

202 |

C4 |

D5 |

141 |

[3] |

I; |

I/O |

P0[2] — General purpose digital input/output pin. |

||||

|

|

|

|

|

|

PU |

|

|

|

|

||

|

|

|

|

|

|

O |

U0_TXD — Transmitter output for UART0. |

|||||

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

O |

U3_TXD — Transmitter output for UART3. |

||

|

|

|

|

|

|

|

|

|

||||

P0[3] |

204 |

D6 |

A3 |

142 |

[3] |

I; |

I/O |

P0[3] — General purpose digital input/output pin. |

||||

|

|

|

|

|

|

PU |

|

|

|

|

||

|

|

|

|

|

|

I |

U0_RXD — Receiver input for UART0. |

|||||

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

I |

U3_RXD — Receiver input for UART3. |

||

|

|

|

|

|

|

|

|

|

||||

P0[4] |

168 |

B12 |

A11 |

116 |

[3] |

I; |

I/O |

P0[4] — General purpose digital input/output pin. |

||||

|

|

|

|

|

|

PU |

|

|

||||

|

|

|

|

|

|

I/O |

I2S_RX_SCK — I2S Receive clock. It is driven by the master |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

and received by the slave. Corresponds to the signal SCK in the |

|

|

|

|

|

|

|

|

|

|

|

|

I2S-bus specification. |

|

|

|

|

|

|

|

|

|

I |

CAN_RD2 — CAN2 receiver input. |

||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

I |

T2_CAP0 — Capture input for Timer 2, channel 0. |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

- |

|

|

R — Function reserved. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

- |

|

|

R — Function reserved. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

- |

|

|

R — Function reserved. |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

O |

LCD_VD[0] — LCD data. |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

LPC178X_7X |

All information provided in this document is subject to legal disclaimers. |

© NXP Semiconductors N.V. 2014. All rights reserved. |

Product data sheet |

Rev. 5 — 9 September 2014 |

10 of 122 |

NXP Semiconductors |

LPC178x/7x |

|

32-bit ARM Cortex-M3 microcontroller |

Table 3. Pin description …continued

Not all functions are available on all parts. See Table 2 (Ethernet, USB, LCD, QEI, SD/MMC, DAC pins) and Table 7 (EMC pins).

Symbol |

Pin LQFP208 |

Ball TFBGA208 |

Ball TFBGA180 |

Pin LQFP144 |

|

Reset state[1] |

|

|

|

|

|

Description |

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

||||||||

|

|

|

|

Type[2] |

|

|

|

|||||

|

|

|

|

|

|

|||||||

P0[5] |

166 |

C12 |

B11 |

115 |

[3] |

I; |

I/O |

P0[5] — General purpose digital input/output pin. |

||||

|

|

|

|

|

|

PU |

|

|

||||

|

|

|

|

|

|

I/O |

I2S_RX_WS — I2S Receive word select. It is driven by the |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

master and received by the slave. Corresponds to the signal WS |

|

|

|

|

|

|

|

|

|

|

|

|

in the I2S-bus specification. |

|

|

|

|

|

|

|

|

|

O |

CAN_TD2 — CAN2 transmitter output. |

||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

I |

T2_CAP1 — Capture input for Timer 2, channel 1. |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

- |

|

|

R — Function reserved. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

- |

|

|

R — Function reserved. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

- |

|

|

R — Function reserved. |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

O |

LCD_VD[1] — LCD data. |

||

|

|

|

|

|

|

|

|

|

||||

P0[6] |

164 |

D13 |

D11 |

113 |

[3] |

I; |

I/O |

P0[6] — General purpose digital input/output pin. |

||||

|

|

|

|

|

|

PU |

|

|

||||

|

|

|

|

|

|

I/O |

I2S_RX_SDA — I2S Receive data. It is driven by the transmitter |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

and read by the receiver. Corresponds to the signal SD in the |

|

|

|

|

|

|

|

|

|

|

|

|

I2S-bus specification. |

|

|

|

|

|

|

|

|

|

I/O |

SSP1_SSEL — Slave Select for SSP1. |

||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

O |

T2_MAT0 — Match output for Timer 2, channel 0. |

||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

O |

U1_RTS — Request to Send output for UART1. Can also be |

||

|

|

|

|

|

|

|

|

|

|

|

|

configured to be an RS-485/EIA-485 output enable signal for |

|

|

|

|

|

|

|

|

|

|

|

|

UART1. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

- |

|

|

R — Function reserved. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

- |

|

|

R — Function reserved. |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

O |

LCD_VD[8] — LCD data. |

||

|

|

|

|

|

|

|

|

|

||||

P0[7] |

162 |

C13 |

B12 |

112 |

[4] |

I; IA |

I/O |

P0[7] — General purpose digital input/output pin. |

||||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

I/O |

I2S_TX_SCK — I2S transmit clock. It is driven by the master |

||

|

|

|

|

|

|

|

|

|

|

|

|

and received by the slave. Corresponds to the signal SCK in the |

|

|

|

|

|

|

|

|

|

|

|

|

I2S-bus specification. |

|

|

|

|

|

|

|

|

|

I/O |

SSP1_SCK — Serial Clock for SSP1. |

||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

O |

T2_MAT1 — Match output for Timer 2, channel 1. |

||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

I |

RTC_EV0 — Event input 0 to Event Monitor/Recorder. |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

- |

|

|

R — Function reserved. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

- |

|

|

R — Function reserved. |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

O |

LCD_VD[9] — LCD data. |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

LPC178X_7X |

All information provided in this document is subject to legal disclaimers. |

© NXP Semiconductors N.V. 2014. All rights reserved. |

Product data sheet |

Rev. 5 — 9 September 2014 |

11 of 122 |

NXP Semiconductors |

LPC178x/7x |

|

32-bit ARM Cortex-M3 microcontroller |

Table 3. Pin description …continued

Not all functions are available on all parts. See Table 2 (Ethernet, USB, LCD, QEI, SD/MMC, DAC pins) and Table 7 (EMC pins).

Symbol |

Pin LQFP208 |

Ball TFBGA208 |

Ball TFBGA180 |

Pin LQFP144 |

|

Reset state[1] |

|

|

|

|

|

|

Description |

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

||||||||

|

|

|

|

Type[2] |

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|||||||

P0[8] |

160 |

A15 |

C12 |

111 |

[4] |

I; IA |

I/O |

|

P0[8] — General purpose digital input/output pin. |

|||||

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

I/O |

I2S_TX_WS — I2S Transmit word select. It is driven by the |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

master and received by the slave. Corresponds to the signal WS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

in the I2S-bus specification. |

|

|

|

|

|

|

|

|

|

|

I/O |

SSP1_MISO — Master In Slave Out for SSP1. |

||||

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

O |

T2_MAT2 — Match output for Timer 2, channel 2. |

||||

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

I |

RTC_EV1 — Event input 1 to Event Monitor/Recorder. |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

- |

|

|

R — Function reserved. |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

- |

|

|

R — Function reserved. |

||

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

O |

LCD_VD[16] — LCD data. |

||||

|

|

|

|

|

|

|

|

|

|

|||||

P0[9] |

158 |

C14 |

A13 |

109 |

[4] |

I; IA |

I/O |

|

P0[9] — General purpose digital input/output pin. |

|||||

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

I/O |

I2S_TX_SDA — I2S transmit data. It is driven by the transmitter |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

and read by the receiver. Corresponds to the signal SD in the |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

I2S-bus specification. |

|

|

|

|

|

|

|

|

|

|

I/O |

SSP1_MOSI — Master Out Slave In for SSP1. |

||||

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

O |

T2_MAT3 — Match output for Timer 2, channel 3. |

||||

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

I |

RTC_EV2 — Event input 2 to Event Monitor/Recorder. |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

- |

|

|

R — Function reserved. |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

- |

|

|

R — Function reserved. |

||

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

O |

LCD_VD[17] — LCD data. |

||||

|

|

|

|

|

|

|

|

|

|

|||||

P0[10] |

98 |

T15 |

L10 |

69 |

[3] |

I; |

I/O |

|

P0[10] — General purpose digital input/output pin. |

|||||

|

|

|

|

|

|

PU |

|

|

|

|

|

|

||

|

|

|

|

|

|

O |

|

U2_TXD — Transmitter output for UART2. |

||||||

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

I/O |

|

I2C2_SDA — I2C2 data input/output (this pin does not use a |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

specialized I2C pad). |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

O |

|

T3_MAT0 — Match output for Timer 3, channel 0. |

|||

|

|

|

|

|

|

|

|

|

|

|||||

P0[11] |

100 |

R14 |

P12 |

70 |

[3] |

I; |

I/O |

|

P0[11] — General purpose digital input/output pin. |

|||||

|

|

|

|

|

|

PU |

|

|

|

|

|

|

||

|

|

|

|

|

|

I |

U2_RXD — Receiver input for UART2. |

|||||||

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

I/O |

I2C2_SCL — I2C2 clock input/output (this pin does not use a |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

specialized I2C pad). |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

O |

|

T3_MAT1 — Match output for Timer 3, channel 1. |

|||

|

|

|

|

|

|

|

|

|

|

|||||

P0[12] |

41 |

R1 |

J4 |

29 |

[5] |

I; |

I/O |

|

P0[12] — General purpose digital input/output pin. |

|||||

|

|

|

|

|

|

PU |

|

|

|

|

|

|

||

|

|

|

|

|

|

O |

|

USB_PPWR2 — Port Power enable signal for USB port 2. |

||||||

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

I/O |

SSP1_MISO — Master In Slave Out for SSP1. |

||||

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

I |

ADC0_IN[6] — A/D converter 0, input 6. When configured as an |

||||

|

|

|

|

|

|

|

|

|

|

|

|

ADC input, the digital function of the pin must be disabled. |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LPC178X_7X |

All information provided in this document is subject to legal disclaimers. |

© NXP Semiconductors N.V. 2014. All rights reserved. |

Product data sheet |

Rev. 5 — 9 September 2014 |

12 of 122 |

NXP Semiconductors |

LPC178x/7x |

|

32-bit ARM Cortex-M3 microcontroller |

Table 3. Pin description …continued

Not all functions are available on all parts. See Table 2 (Ethernet, USB, LCD, QEI, SD/MMC, DAC pins) and Table 7 (EMC pins).

Symbol |

Pin LQFP208 |

Ball TFBGA208 |

Ball TFBGA180 |

Pin LQFP144 |

|

Reset state[1] |

|

|

|

|

|

|

Description |

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

||||||||

|

|

|

|

Type[2] |

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|||||||

P0[13] |

45 |

R2 |

J5 |

32 |

[5] |

I; |

I/O |

|

P0[13] — General purpose digital input/output pin. |

|||||

|

|

|

|

|

|

PU |

|

|

|

|

|

|

||

|

|

|

|

|

|

O |

|

USB_UP_LED2 — USB port 2 GoodLink LED indicator. It is |

||||||

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

LOW when the device is configured (non-control endpoints |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

enabled), or when the host is enabled and has detected a |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

device on the bus. It is HIGH when the device is not configured, |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

or when host is enabled and has not detected a device on the |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

bus, or during global suspend. It transitions between LOW and |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

HIGH (flashes) when the host is enabled and detects activity on |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

the bus. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

I/O |

|

SSP1_MOSI — Master Out Slave In for SSP1. |

|||

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

I |

ADC0_IN[7] — A/D converter 0, input 7. When configured as an |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

ADC input, the digital function of the pin must be disabled. |

|

|

|

|

|

|

|

|

|

|

|

|||||

P0[14] |

69 |

T7 |

M5 |

48 |

[3] |

I; |

I/O |

|

P0[14] — General purpose digital input/output pin. |

|||||

|

|

|

|

|

|

PU |

|

|

|

|

|

|

||

|

|

|

|

|

|

O |

|

USB_HSTEN2 — Host Enabled status for USB port 2. |

||||||

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

I/O |

|

SSP1_SSEL — Slave Select for SSP1. |

|||

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

O |

USB_CONNECT2 — SoftConnect control for USB port 2. |

||||

|

|

|

|

|

|

|

|

|

|

|

|

Signal used to switch an external 1.5 k resistor under software |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

control. Used with the SoftConnect USB feature. |

|

|

|

|

|

|

|

|

|

|

|

|||||

P0[15] |

128 |

J16 |

H13 |

89 |

[3] |

I; |

I/O |

|

P0[15] — General purpose digital input/output pin. |

|||||

|

|

|

|

|

|

PU |

|

|

|

|

|

|

||

|

|

|

|

|

|

O |

|

U1_TXD — Transmitter output for UART1. |

||||||

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

I/O |

|

SSP0_SCK — Serial clock for SSP0. |

|||

|

|

|

|

|

|

|

|

|

|

|||||

P0[16] |

130 |

J14 |

H14 |

90 |

[3] |

I; |

I/O |

|

P0[16] — General purpose digital input/output pin. |

|||||

|

|

|

|

|

|

PU |

|

|

|

|

|

|

||

|

|

|

|

|

|

I |

|

U1_RXD — Receiver input for UART1. |

||||||

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

I/O |

SSP0_SSEL — Slave Select for SSP0. |

||||

|

|

|

|

|

|

|

|

|

|

|||||

P0[17] |

126 |

K17 |

J12 |

87 |

[3] |

I; |

I/O |

|

P0[17] — General purpose digital input/output pin. |

|||||

|

|

|

|

|

|

PU |

|

|

|

|

|

|

||

|

|

|

|

|

|

I |

|

U1_CTS — Clear to Send input for UART1. |

||||||

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

I/O |

|

SSP0_MISO — Master In Slave Out for SSP0. |

|||

|

|

|

|

|

|

|

|

|

|

|||||

P0[18] |

124 |

K15 |

J13 |

86 |

[3] |

I; |

I/O |

|

P0[18] — General purpose digital input/output pin. |

|||||

|

|

|

|

|

|

PU |

|

|

|

|

|

|

||

|

|

|

|

|

|

I |

|

U1_DCD — Data Carrier Detect input for UART1. |

||||||

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

I/O |

|

SSP0_MOSI — Master Out Slave In for SSP0. |

|||

|

|

|

|

|

|

|

|

|

|

|||||

P0[19] |

122 |

L17 |

J10 |

85 |

[3] |

I; |

I/O |

|

P0[19] — General purpose digital input/output pin. |

|||||

|

|

|

|

|

|

PU |

|

|

|

|

|

|

||

|

|

|

|

|

|

I |

|

U1_DSR — Data Set Ready input for UART1. |

||||||

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

O |

SD_CLK — Clock output line for SD card interface. |

||||

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

I/O |

I2C1_SDA — I2C1 data input/output (this pin does not use a |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

specialized I2C pad). |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LPC178X_7X |

All information provided in this document is subject to legal disclaimers. |

© NXP Semiconductors N.V. 2014. All rights reserved. |

Product data sheet |

Rev. 5 — 9 September 2014 |

13 of 122 |

NXP Semiconductors |

LPC178x/7x |

|

32-bit ARM Cortex-M3 microcontroller |

Table 3. Pin description …continued

Not all functions are available on all parts. See Table 2 (Ethernet, USB, LCD, QEI, SD/MMC, DAC pins) and Table 7 (EMC pins).

Symbol |

Pin LQFP208 |

Ball TFBGA208 |

Ball TFBGA180 |

Pin LQFP144 |

|

Reset state[1] |

|

|

|

|

|

Description |

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

||||||||

|

|

|

|

Type[2] |

|

|

|

|||||

|

|

|

|

|

|

|||||||

P0[20] |

120 |

M17 |

K14 |

83 |

[3] |

I; |

I/O |

P0[20] — General purpose digital input/output pin. |

||||

|

|

|

|

|

|

PU |

|

|

|

|

||

|

|

|

|

|

|

O |

U1_DTR — Data Terminal Ready output for UART1. Can also |

|||||

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

be configured to be an RS-485/EIA-485 output enable signal for |

|

|

|

|

|

|

|

|

|

|

|

|

UART1. |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

I/O |

SD_CMD — Command line for SD card interface. |

||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

I/O |

I2C1_SCL — I2C1 clock input/output (this pin does not use a |

||

|

|

|

|

|

|

|

|

|

|

|

|

specialized I2C pad). |

|

|

|

|

|

|

|

|

|

||||

P0[21] |

118 |

M16 |

K11 |

82 |

[3] |

I; |

I/O |

P0[21] — General purpose digital input/output pin. |

||||

|

|

|

|

|

|

PU |

|

|

|

|

||

|

|

|

|

|

|

I |

U1_RI — Ring Indicator input for UART1. |

|||||

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

O |

SD_PWR — Power Supply Enable for external SD card power |

||

|

|

|

|

|

|

|

|

|

|

|

|

supply. |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

O |

U4_OE — RS-485/EIA-485 output enable signal for UART4. |

||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

I |

CAN_RD1 — CAN1 receiver input. |

||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

I/O |

U4_SCLK — USART 4 clock input or output in synchronous |

||

|

|

|

|

|

|

|

|

|

|

|

|

mode. |

|

|

|

|

|

|

|

|

|

||||

P0[22] |

116 |

N17 |

L14 |

80 |

[6] |

I; |

I/O |

P0[22] — General purpose digital input/output pin. |

||||

|

|

|

|

|

|

PU |

|

|

|

|

||

|

|

|

|

|

|

O |

U1_RTS — Request to Send output for UART1. Can also be |

|||||

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

configured to be an RS-485/EIA-485 output enable signal for |

|

|

|

|

|

|

|

|

|

|

|

|

UART1. |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

I/O |

SD_DAT[0] — Data line 0 for SD card interface. |

||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

O |

U4_TXD — Transmitter output for USART4 (input/output in |

||

|

|

|

|

|

|

|

|

|

|

|

|

smart card mode). |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

O |

CAN_TD1 — CAN1 transmitter output. |

||

|

|

|

|

|

|

|

|

|

||||

P0[23] |

18 |

H1 |

F5 |

13 |

[5] |

I; |

I/O |

P0[23] — General purpose digital input/output pin. |

||||

|

|

|

|

|

|

PU |

|

|

|

|

||

|

|

|

|

|

|

I |

ADC0_IN[0] — A/D converter 0, input 0. When configured as an |

|||||

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

ADC input, the digital function of the pin must be disabled. |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

I/O |

I2S_RX_SCK — Receive Clock. It is driven by the master and |

||

|

|

|

|

|

|

|

|

|

|

|

|

received by the slave. Corresponds to the signal SCK in the |

|

|

|

|

|

|

|

|

|

|

|

|

I2S-bus specification. |

|

|

|

|

|

|

|

|

|

I |

T3_CAP0 — Capture input for Timer 3, channel 0. |

||

|

|

|

|

|

|

|

|

|

||||

P0[24] |

16 |

G2 |

E1 |

11 |

[5] |

I; |

I/O |

P0[24] — General purpose digital input/output pin. |

||||

|

|

|

|

|

|

PU |

|

|

|

|

||

|

|

|

|

|

|

I |

ADC0_IN[1] — A/D converter 0, input 1. When configured as an |

|||||

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

ADC input, the digital function of the pin must be disabled. |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

I/O |

I2S_RX_WS — Receive Word Select. It is driven by the master |

||

|

|

|

|

|

|

|

|

|

|

|

|

and received by the slave. Corresponds to the signal WS in the |

|

|

|

|

|

|

|

|

|

|

|

|

I2S-bus specification. |

|

|

|

|

|

|

|

|

|

I |

T3_CAP1 — Capture input for Timer 3, channel 1. |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

LPC178X_7X |

All information provided in this document is subject to legal disclaimers. |

© NXP Semiconductors N.V. 2014. All rights reserved. |

Product data sheet |

Rev. 5 — 9 September 2014 |

14 of 122 |

NXP Semiconductors |

LPC178x/7x |

|

32-bit ARM Cortex-M3 microcontroller |

Table 3. Pin description …continued

Not all functions are available on all parts. See Table 2 (Ethernet, USB, LCD, QEI, SD/MMC, DAC pins) and Table 7 (EMC pins).

Symbol |

Pin LQFP208 |

Ball TFBGA208 |

Ball TFBGA180 |

Pin LQFP144 |

|

Reset state[1] |

|

|

|

|

|

|

Description |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

Type[2] |

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|||||||

P0[25] |

14 |

F1 |

E4 |

10 |

[5] |

I; |

I/O |

|

P0[25] — General purpose digital input/output pin. |

|||||||

|

|

|

|

|

|

PU |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

I |

|

ADC0_IN[2] — A/D converter 0, input 2. When configured as an |

||||||||

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

ADC input, the digital function of the pin must be disabled. |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|