Philips LPC2104, LPC2105, LPC2106 Operation Manual

LPC2104/2105/2106

Single-chip 32-bit microcontrollers; 128 kB ISP/IAP Flash with 64 kB/32 kB/16 kB RAM

Rev. 05 — 22 December 2004 |

Product data |

1. General description

The LPC2104/2105/2106 are based on a 16/32 bit ARM7TDMI-S™ CPU with real-time emulation and embedded trace support, together with 128 kbytes (kB) of embedded high speed flash memory. A 128 bit wide memory interface and a unique accelerator architecture enable 32 bit code execution at maximum clock rate. For critical code size applications, the alternative 16-bit Thumb™ Mode reduces code by more than 30 % with minimal performance penalty.

Due to their tiny size and low power consumption, these microcontrollers are ideal for applications where miniaturization is a key requirement, such as access control and point-of-sale. With a wide range of serial communications interfaces and on-chip SRAM options up to 64 kB, they are very well suited for communication gateways and protocol converters, soft modems, voice recognition and low end imaging, providing both large buffer size and high processing power. Various 32 bit timers, PWM channels and 32 GPIO lines make these microcontrollers particularly suitable for industrial control and medical systems.

2. Features

2.1Key features

■16/32 bit ARM7TDMI-S processor.

■16/32/64 kB on-chip Static RAM.

■128 kB on-chip Flash Program Memory. 128 bit wide interface/accelerator enables high speed 60 MHz operation.

■In-System Programming (ISP) and In-Application Programming (IAP) via on-chip boot-loader software. Flash programming takes 1 ms per 512 byte line. Single sector or full chip erase takes 400 ms.

■Vectored Interrupt Controller with configurable priorities and vector addresses.

■EmbeddedICE-RT interface enables breakpoints and watch points. Interrupt service routines can continue to execute whilst the foreground task is debugged with the on-chip RealMonitor™ software.

■Embedded Trace Macrocell enables non-intrusive high speed real-time tracing of instruction execution.

■Multiple serial interfaces including two UARTs (16C550), Fast I2C (400 kbits/s) and SPI™.

■Two 32-bit timers (7 capture/compare channels), PWM unit (6 outputs), Real Time Clock and Watchdog.

■Up to thirty-two 5 V tolerant general purpose I/O pins in a tiny LQFP48 (7 × 7 mm2) package.

Philips Semiconductors |

LPC2104/2105/2106 |

|

Single-chip 32-bit microcontrollers |

■60 MHz maximum CPU clock available from programmable on-chip Phase-Locked Loop with settling time of 100 μs.

■On-chip crystal oscillator with an operating range of 1 MHz to 30 MHz.

■Two low power modes, Idle and Power-down.

■Processor wake-up from Power-down mode via external interrupt.

■Individual enable/disable of peripheral functions for power optimization.

■Dual power supply:

CPU operating voltage range of 1.65 V to 1.95 V (1.8 V ± 8.3 %).

I/O power supply range of 3.0 V to 3.6 V (3.3 V ± 10 %) with 5 V tolerant I/O pads.

3.Ordering information

Table 1: Ordering information

Type number |

Package |

|

|

|

Name |

Description |

Version |

LPC2104BBD48 |

LQFP48 |

plastic low profile quad flat package; 48 leads; |

SOT313-2 |

|

|

body 7 × 7 × 1.4 mm |

|

|

|

|

|

LPC2105BBD48 |

LQFP48 |

plastic low profile quad flat package; 48 leads; |

SOT313-2 |

|

|

body 7 × 7 × 1.4 mm |

|

|

|

|

|

LPC2106FBD48 |

LQFP48 |

plastic low profile quad flat package; 48 leads; |

SOT313-2 |

|

|

body 7 × 7 × 1.4 mm |

|

|

|

|

|

LPC2106FHN48 |

HVQFN48 |

plastic thermal enhanced very thin quad flat |

SOT619-1 |

|

|

package; no leads; 48 terminals; body |

|

|

|

7 × 7 × 0.85 mm |

|

|

|

|

|

3.1 Ordering options

Table 2: Part options

Type number |

Flash memory |

RAM |

Temperature range |

LPC2104BBD48 |

128 kB |

16 kB |

0 to +70, LQFP |

|

|

|

|

LPC2105BBD48 |

128 kB |

32 kB |

0 to +70, LQFP |

|

|

|

|

LPC2106FBD48 |

128 kB |

64 kB |

−40 to +85, LQFP |

|

|

|

|

LPC2106FHN48 |

128 kB |

64 kB |

−40 to +85, HVQFN |

|

|

|

|

9397 750 14476 |

© Koninklijke Philips Electronics N.V. 2004. All rights reserved. |

Product data |

Rev. 05 — 22 December 2004 |

2 of 32 |

Philips Semiconductors |

LPC2104/2105/2106 |

|

Single-chip 32-bit microcontrollers |

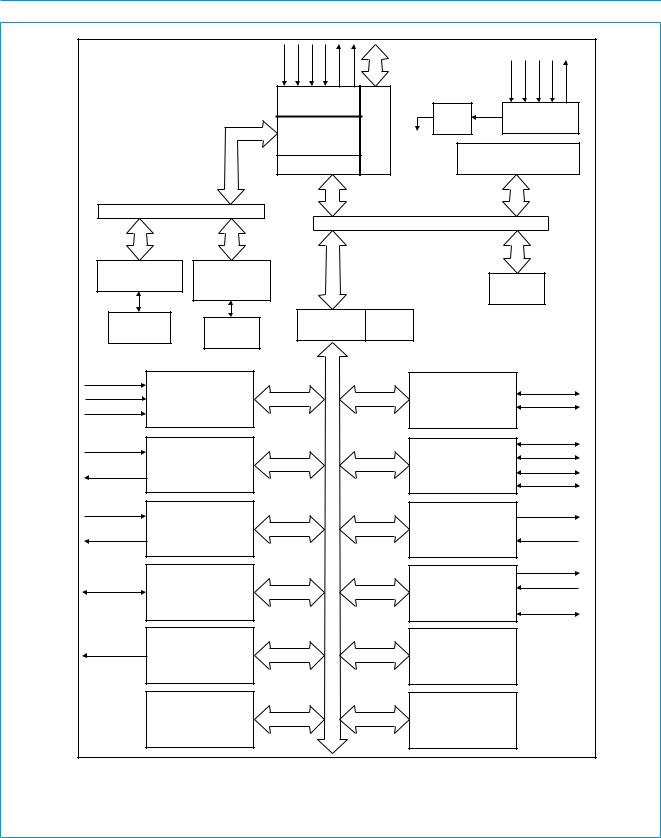

4. Block diagram

|

|

(1) |

(1) |

(1) |

(1) |

(1) |

|

|

|

|

|

|

|

TRST |

TMS |

TCK |

TDI |

TDO RTCK |

|

|

XTAL1 |

DD |

SS |

|

|

EMULATION TRACE MODULE |

|

XTAL2 RST V |

V |

||||||

|

|

|

TEST/DEBUG |

|

|

|

|

||||

|

|

|

INTERFACE |

|

|

SYSTEM |

|||||

|

|

|

|

|

|

|

|

PLL |

|||

|

|

|

|

|

|

|

|

FUNCTIONS |

|||

|

|

|

|

|

|

|

|

|

|||

|

|

ARM7TDMI-S |

system |

|

|

|

|||||

|

|

|

|

|

|

|

clock |

VECTORED INTERRUPT |

|||

|

|

|

|

|

|

|

|

||||

|

|

|

AHB BRIDGE |

|

CONTROLLER |

|

|||||

ARM7 LOCAL BUS |

|

|

|

|

|

AMBA AHB |

|

|

|||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

(Advanced High-performance Bus) |

|

|

|||

INTERNAL SRAM |

INTERNAL |

|

|

|

|

|

|

|

|

|

|

CONTROLLER |

FLASH |

|

|

|

|

|

|

AHB |

|

||

|

|

CONTROLLER |

|

|

|

|

|

|

DECODER |

|

|

16/32/64 kB |

|

128 kB |

|

AHB TO VPB |

VPB |

|

|

|

|

||

SRAM |

|

|

|

BRIDGE |

DIVIDER |

|

|

|

|||

|

FLASH |

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

APB(2) |

|

|

|

|

|

EINT0* |

|

|

|

|

|

|

|

|

|

SCL* |

|

EINT1* |

EXTERNAL |

|

|

|

|

|

|

I2C SERIAL |

|||

|

|

|

|

|

|

SDA* |

|||||

EINT2* |

INTERRUPTS |

|

|

|

|

|

|

INTERFACE |

|||

|

|

|

|

|

|

|

|

||||

CAP0..2* |

|

|

|

|

|

|

|

|

|

SCK* |

|

CAPTURE/ |

|

|

|

|

|

|

|

MOSI* |

|||

|

|

|

|

|

|

|

SPI SERIAL |

||||

|

COMPARE |

|

|

|

|

|

|

MISO* |

|||

MAT0..2* |

|

|

|

|

|

|

INTERFACE |

||||

|

TIMER 0 |

|

|

|

|

|

|

SSEL* |

|||

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

||

CAP0..3* |

CAPTURE/ |

|

|

|

|

|

|

|

TxD* |

||

|

|

|

|

|

|

|

|

|

|

||

MAT0..3* |

COMPARE |

|

|

|

|

|

|

UART0 |

RxD* |

||

|

TIMER 1 |

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TxD* |

|

GPIO (32 PINS) |

GENERAL |

|

|

|

|

|

|

UART1 |

RxD* |

||

|

|

|

|

|

|

|

|

|

|||

|

PURPOSE I/O |

|

|

|

|

|

|

MODEM CONTROL |

|||

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

(6 PINS)* |

|

PWM1..6* |

|

PWM0 |

|

|

|

|

|

|

WATCHDOG |

|

|

|

|

|

|

|

|

|

|

TIMER |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

REAL TIME |

|

|

|

|

|

|

SYSTEM |

|

|

|

|

|

CLOCK |

|

|

|

|

|

|

CONTROL |

|

|

*Shared with GPIO |

|

|

|

|

|

|

|

|

|

002aaa412 |

|

(1)When test/debug interface is used, GPIO/other function sharing these pins are not available.

(2)APB with Ready signal.

Fig 1. Block diagram.

9397 750 14476 |

© Koninklijke Philips Electronics N.V. 2004. All rights reserved. |

Product data |

Rev. 05 — 22 December 2004 |

3 of 32 |

Philips Semiconductors |

LPC2104/2105/2106 |

|

Single-chip 32-bit microcontrollers |

5.Pinning information

5.1Pinning

P0.19/MAT1.2/TCK 1 P0.20/MAT1.3/TDI 2 P0.21/PWM5/TDO 3 NC 4 VDD1.8 (CORE) 5 RST 6

VSS1 7 P0.27/TRACEPKT0/TRST 8 P0.28/TRACEPKT1/TMS 9 P0.29/TRACEPKT2/TCK 10 X1 11 X2 12

P0.18/CAP1.3/TMS |

|

P0.17/CAP1.2/TRST |

|

P0.16/EINT0/MAT0.2 |

|

P0.15/RI1/EINT2 |

|

P0.14/DCD1/EINT1 |

|

V |

|

NC |

|

P0.13/DTR1/MAT1.1 |

|

V |

|

P0.26/TRACESYNC |

|

P0.25/PIPESTAT2 |

|

P0.12/DSR1/MAT1.0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(I/O) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SS4 |

|

|

|

|

|

DD31- |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

48 |

|

47 |

|

46 |

|

45 |

|

44 |

|

43 |

|

42 |

|

41 |

|

40 |

|

39 |

|

38 |

|

37 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

36 P0.11/CTS1/CAP1.1

35 P0.10/RTS1/CAP1.0

34 P0.24/PIPESTAT1

33 P0.23/PIPESTAT0

32 P0.22/TRACECLK

31 VSS3

LPC2104/2105/2106

30 P0.9/RxD1/PWM6

29 P0.8/TxD1/PWM4

28 P0.7/SSEL/PWM2

27 DBGSEL

26 RTCK

25 NC

13 |

|

14 |

|

15 |

|

16 |

|

17 |

|

18 |

|

19 |

|

20 |

|

21 |

|

22 |

|

23 |

|

24 |

002aaa411 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P0.0/TxD0/PWM1 |

|

P0.1/RxD0/PWM3 |

|

P0.30/TRACEPKT3/TDI |

|

P0.31/EXTIN0/TDO |

|

(I/O) |

|

P0.2/SCL/CAP0.0 |

|

SS2 |

|

NC |

|

P0.3/SDA/MAT0.0 |

|

P0.4/SCK/CAP0.1 |

|

P0.5/MISO/MAT0.1 |

|

P0.6/MOSI/CAP0.2 |

|

|

|

|

|

V |

|

|

V |

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

DD32- |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Fig 2. Pinning.

9397 750 14476 |

© Koninklijke Philips Electronics N.V. 2004. All rights reserved. |

Product data |

Rev. 05 — 22 December 2004 |

4 of 32 |

Philips Semiconductors |

LPC2104/2105/2106 |

|||

|

|

|

|

Single-chip 32-bit microcontrollers |

|

5.2 |

Pin description |

||

Table 3: |

Pin description |

|

|

|

|

|

|

|

|

Symbol |

|

Pin |

Type |

Description |

P0.0 to P0.31 |

I/O |

Port 0: Port 0 is a 32-bit bi-directional I/O port with individual direction |

||

|

|

|

|

controls for each bit. The operation of port 0 pins depends upon the pin |

|

|

|

|

function selected via the Pin Connect Block. |

|

|

|

|

|

|

13 |

I/O |

P0.0 — Port 0 bit 0. |

|

|

|

|

|

|

|

|

|

O |

TxD0 — Transmitter output for UART 0. |

|

|

|

|

|

|

|

|

O |

PWM1 — Pulse Width Modulator output 1. |

|

|

|

|

|

|

14 |

I/O |

P0.1 — Port 0 bit 1. |

|

|

|

|

|

|

|

|

|

I |

RxD0 — Receiver input for UART 0. |

|

|

|

|

|

|

|

|

O |

PWM3 — Pulse Width Modulator output 3. |

|

|

|

|

|

|

18 |

I/O |

P0.2 — Port 0 bit 2. |

|

|

|

|

|

|

|

|

|

I/O |

SCL — I2C clock input/output. Open drain output (for I2C compliance). |

|

|

|

I |

CAP0.0 — Capture input for Timer 0, channel 0. |

|

|

|

|

|

|

21 |

I/O |

P0.3 — Port 0 bit 3. |

|

|

|

|

|

|

|

|

|

I/O |

SDA — I2C data input/output. Open drain output (for I2C compliance). |

|

|

|

O |

MAT0.0 — Match output for Timer 0, channel 0. |

|

|

|

|

|

|

22 |

I/O |

P0.4 — Port 0 bit 4. |

|

|

|

|

|

|

|

|

|

I/O |

SCK — Serial clock. SPI clock output from master or input to slave. |

|

|

|

|

|

|

|

|

I |

CAP0.1 — Capture input for Timer 0, channel 1. |

|

|

|

|

|

|

23 |

I/O |

P0.5 — Port 0 bit 5. |

|

|

|

|

|

|

|

|

|

I/O |

MISO — Master In Slave Out. Data input to SPI master or data output from |

|

|

|

|

SPI slave. |

|

|

|

|

|

|

|

|

O |

MAT0.1 — Match output for Timer 0, channel 1. |

|

|

|

|

|

|

24 |

I/O |

P0.6 — Port 0 bit 6. |

|

|

|

|

|

|

|

|

|

I/O |

MOSI — Master Out Slave In. Data output from SPI master or data input to |

|

|

|

|

SPI slave. |

|

|

|

|

|

|

|

|

I |

CAP0.2 — Capture input for Timer 0, channel 2. |

|

|

|

|

|

|

28 |

I/O |

P0.7 — Port 0 bit 7. |

|

|

|

|

|

|

|

|

|

I |

SSEL — Slave Select. Selects the SPI interface as a slave. |

|

|

|

|

|

|

|

|

O |

PWM2 — Pulse Width Modulator output 2. |

|

|

|

|

|

|

29 |

I/O |

P0.8 — Port 0 bit 8. |

|

|

|

|

|

|

|

|

|

O |

TxD1 — Transmitter output for UART 1. |

|

|

|

|

|

|

|

|

O |

PWM4 — Pulse Width Modulator output 4. |

|

|

|

|

|

|

30 |

I/O |

P0.9 — Port 0 bit 9. |

|

|

|

|

|

|

|

|

|

I |

RxD1 — Receiver input for UART 1. |

|

|

|

|

|

|

|

|

O |

PWM6 — Pulse Width Modulator output 6. |

9397 750 14476 |

© Koninklijke Philips Electronics N.V. 2004. All rights reserved. |

Product data |

Rev. 05 — 22 December 2004 |

5 of 32 |

Philips Semiconductors |

|

LPC2104/2105/2106 |

|||

|

|

|

|

|

Single-chip 32-bit microcontrollers |

Table 3: |

Pin description…continued |

|

|

||

|

|

|

|

|

|

Symbol |

|

Pin |

Type |

Description |

|

|

35 |

I/O |

P0.10 — Port |

0 bit 10. |

|

|

|

|

|

|

|

|

|

|

O |

RTS1 — Request to Send output for UART 1. |

|

|

|

|

|

|

|

|

|

|

I |

CAP1.0 — Capture input for Timer 1, channel 0. |

|

|

|

|

|

|

|

|

36 |

I/O |

P0.11 — Port |

0 bit 11. |

|

|

|

|

|

|

|

|

|

|

I |

CTS1 — Clear to Send input for UART 1. |

|

|

|

|

|

|

|

|

|

|

I |

CAP1.1 — Capture input for Timer 1, channel 1. |

|

|

|

|

|

|

|

|

37 |

I/O |

P0.12 — Port |

0 bit 12. |

|

|

|

|

|

|

|

|

|

|

I |

DSR1 — Data Set Ready input for UART 1. |

|

|

|

|

|

|

|

|

|

|

O |

MAT1.0 — Match output for Timer 1, channel 0. |

|

|

|

|

|

|

|

|

41 |

I/O |

P0.13 — Port |

0 bit 13. |

|

|

|

|

|

|

|

|

|

|

O |

DTR1 — Data Terminal Ready output for UART 1. |

|

|

|

|

|

|

|

|

|

|

O |

MAT1.1 — Match output for Timer 1, channel 1. |

|

|

|

|

|

|

|

|

44 |

I/O |

P0.14 — Port |

0 bit 14. |

|

|

|

|

|

|

|

|

|

|

I |

DCD1 — Data Carrier Detect input for UART 1. |

|

|

|

|

|

|

|

|

|

|

I |

EINT1 — External interrupt 1 input. |

|

|

|

|

|

|

|

|

45 |

I/O |

P0.15 — Port |

0 bit 15. |

|

|

|

|

|

|

|

|

|

|

I |

RI1 — Ring Indicator input for UART 1. |

|

|

|

|

|

|

|

|

|

|

O |

EINT2 — External interrupt 2 input. |

|

|

|

|

|

|

|

|

46 |

I/O |

P0.16 — Port |

0 bit 16. |

|

|

|

|

|

|

|

|

|

|

I |

EINT0 — External interrupt 0 input. |

|

|

|

|

|

|

|

|

|

|

O |

MAT0.2 — Match output for Timer 0, channel 2. |

|

|

|

|

|

|

|

|

47 |

I/O |

P0.17 — Port |

0 bit 17. |

|

|

|

|

|

|

|

|

|

|

I |

CAP1.2 — Capture input for Timer 1, channel 2. |

|

|

|

|

|

|

|

|

|

|

I |

TRST — Test Reset for JTAG interface, primary JTAG pin group. |

|

|

|

|

|

|

|

|

48 |

I/O |

P0.18 — Port 0 bit 18. |

||

|

|

|

|

|

|

|

|

|

I |

CAP1.3 — Capture input for Timer 1, channel 3. |

|

|

|

|

|

|

|

|

|

|

I |

TMS — Test Mode Select for JTAG interface, primary JTAG pin group. |

|

|

|

|

|

|

|

|

1 |

I/O |

P0.19 — Port 0 bit 19. |

||

|

|

|

|

|

|

|

|

|

O |

MAT1.2 — Match output for Timer 1, channel 2. |

|

|

|

|

|

|

|

|

|

|

I |

TCK — Test Clock for JTAG interface, primary JTAG pin group. |

|

|

|

|

|

|

|

|

2 |

I/O |

P0.20 — Port 0 bit 20. |

||

|

|

|

|

|

|

|

|

|

O |

MAT1.3 — Match output for Timer 1, channel 3. |

|

|

|

|

|

|

|

|

|

|

I |

TDI — Test Data In for JTAG interface, primary JTAG pin group |

|

|

|

|

|

|

|

|

3 |

I/O |

P0.21 — Port 0 bit 21. |

||

|

|

|

|

|

|

|

|

|

O |

PWM5 — Pulse Width Modulator output 5. |

|

|

|

|

|

|

|

|

|

|

O |

TDO — Test Data Out for JTAG interface, primary JTAG pin group. |

|

|

|

|

|

|

|

|

32 |

I/O |

P0.22 — Port 0 bit 22. |

||

|

|

|

|

|

|

|

|

|

O |

TRACECLK — Trace Clock. Standard I/O port with internal pull-up. |

|

|

|

|

|

|

|

|

33 |

I/O |

P0.23 — Port 0 bit 23. |

||

|

|

|

|

|

|

|

|

|

O |

PIPESTAT0 — Pipeline Status, bit 0. Standard I/O port with internal pull-up. |

|

|

|

|

|

|

|

|

34 |

I/O |

P0.24 — Port 0 bit 24. |

||

9397 750 14476 |

|

|

|

|

© Koninklijke Philips Electronics N.V. 2004. All rights reserved. |

Product data |

Rev. 05 — 22 December 2004 |

6 of 32 |

Philips Semiconductors |

LPC2104/2105/2106 |

|||||

|

|

|

|

|

|

Single-chip 32-bit microcontrollers |

Table 3: |

Pin description…continued |

|

||||

|

|

|

|

|

|

|

|

Symbol |

|

Pin |

Type |

Description |

|

|

|

|

|

|

O |

PIPESTAT1 — Pipeline Status, bit 1. Standard I/O port with internal pull-up. |

|

|

|

|

|

|

|

|

|

|

38 |

I/O |

P0.25 — Port 0 bit 25. |

|

|

|

|

|

|

|

|

|

|

|

|

|

O |

PIPESTAT2 — Pipeline Status, bit 2. Standard I/O port with internal pull-up. |

|

|

|

|

|

|

|

|

|

|

39 |

I/O |

P0.26 — Port 0 bit 26. |

|

|

|

|

|

|

|

|

|

|

|

|

|

O |

TRACESYNC — Trace Synchronization Standard I/O port with internal |

|

|

|

|

|

|

pull-up. |

|

|

|

|

|

|

|

|

|

|

8 |

I/O |

P0.27 — Port 0 bit 27. |

|

|

|

|

|

|

|

|

|

|

|

|

|

O |

TRACEPKT0 — Trace Packet, bit 0. Standard I/O port with internal pull-up. |

|

|

|

|

|

|

|

|

|

|

|

|

I |

TRST — Test Reset for JTAG interface, secondary JTAG pin group. |

|

|

|

|

|

|

|

|

|

|

9 |

I/O |

P0.28 — Port 0 bit 28. |

|

|

|

|

|

|

|

|

|

|

|

|

|

O |

TRACEPKT1 — Trace Packet, bit 1. Standard I/O port with internal pull-up. |

|

|

|

|

|

|

|

|

|

|

|

|

I |

TMS — Test Mode Select for JTAG interface, secondary JTAG pin group |

|

|

|

|

|

|

|

|

|

|

10 |

I/O |

P0.29 — Port 0 bit 29. |

|

|

|

|

|

|

|

|

|

|

|

|

|

O |

TRACEPKT2 — Trace Packet, bit 2. Standard I/O port with internal pull-up. |

|

|

|

|

|

|

|

|

|

|

|

|

I |

TCK — Test Clock for JTAG interface, secondary JTAG pin group. |

|

|

|

|

|

|

|

|

|

|

15 |

I/O |

P0.30 — Port 0 bit 30. |

|

|

|

|

|

|

|

|

|

|

|

|

|

O |

TRACEPKT3 — Trace Packet, bit 3. Standard I/O port with internal pull-up. |

|

|

|

|

|

|

|

|

|

|

|

|

I |

TDI — Test Data In for JTAG interface, secondary JTAG pin group. |

|

|

|

|

|

|

|

|

|

|

16 |

I/O |

P0.31 — Port 0 bit 31. |

|

|

|

|

|

|

|

|

|

|

|

|

|

I |

EXTIN0 — External Trigger Input. Standard I/O port with internal pull-up. |

|

|

|

|

|

|

|

|

|

|

|

|

O |

TDO — Test Data out for JTAG interface, secondary JTAG pin group. |

|

|

|

|

|

||

|

RTCK |

26 |

I/O |

Returned Test Clock output: Extra signal added to the JTAG port. Assists |

||

|

|

|

|

|

|

debugger synchronization when processor frequency varies. Also used |

|

|

|

|

|

|

during debug mode entry to select primary or secondary JTAG pins with the |

|

|

|

|

|

|

48-pin package. Bi-directional pin with internal pull-up. |

|

|

|

|

|

||

|

DBGSEL |

27 |

I |

Debug Select: When LOW, the part operates normally. When HIGH, debug |

||

|

|

|

|

|

|

mode is entered. Input pin with internal pull-down. |

|

|

|

|

|

|

|

|

|

|

6 |

I |

External Reset input: A LOW on this pin resets the device, causing I/O ports |

|

|

RST |

|||||

|

|

|

|

|

|

and peripherals to take on their default states, and processor execution to |

|

|

|

|

|

|

begin at address 0. |

|

|

|

|

|

||

|

X1 |

11 |

I |

Input to the oscillator circuit and internal clock generator circuits. |

||

|

|

|

|

|

||

|

X2 |

12 |

O |

Output from the oscillator amplifier. |

||

|

|

|

|

|

||

|

VSS1 - VSS4 |

7, 19, 31, 43 |

I |

Ground: 0 V reference. |

||

|

VDD1.8 |

5 |

I |

1.8 V Core Power Supply: This is the power supply voltage for internal |

||

|

|

|

|

|

|

circuitry. |

|

|

|

|

|

||

|

VDD3 |

17, 40 |

I |

3.3 V Pad Power Supply: This is the power supply voltage for the I/O ports. |

||

|

NC |

4, 20, 25, 42 |

- |

Not Connected: These pins are not connected in the 48 pin package. |

||

|

|

|

|

|

|

|

9397 750 14476 |

© Koninklijke Philips Electronics N.V. 2004. All rights reserved. |

Product data |

Rev. 05 — 22 December 2004 |

7 of 32 |

Philips Semiconductors |

LPC2104/2105/2106 |

|

Single-chip 32-bit microcontrollers |

6.Functional description

6.1Architectural overview

The ARM7TDMI-S is a general purpose 32-bit microprocessor, which offers high performance and very low power consumption. The ARM® architecture is based on Reduced Instruction Set Computer (RISC) principles, and the instruction set and related decode mechanism are much simpler than those of microprogrammed Complex Instruction Set Computers. This simplicity results in a high instruction throughput and impressive real-time interrupt response from a small and cost-effective processor core.

Pipeline techniques are employed so that all parts of the processing and memory systems can operate continuously. Typically, while one instruction is being executed, its successor is being decoded, and a third instruction is being fetched from memory.

The ARM7TDMI-S processor also employs a unique architectural strategy known as Thumb, which makes it ideally suited to high-volume applications with memory restrictions, or applications where code density is an issue.

The key idea behind Thumb is that of a super-reduced instruction set. Essentially, the ARM7TDMI-S processor has two instruction sets:

•The standard 32-bit ARM set.

•A 16-bit Thumb set.

The Thumb set’s 16-bit instruction length allows it to approach twice the density of standard ARM code while retaining most of the ARM’s performance advantage over a traditional 16-bit processor using 16-bit registers. This is possible because Thumb code operates on the same 32-bit register set as ARM code.

Thumb code is able to provide up to 65 % of the code size of ARM, and 160 % of the performance of an equivalent ARM processor connected to a 16-bit memory system.

6.2 On-Chip Flash program memory

The LPC2104/2105/2106 incorporate a 128 kB Flash memory system. This memory may be used for both code and data storage. Programming of the Flash memory may be accomplished in several ways. It may be programmed In System via the serial port. The application program may also erase and/or program the Flash while the application is running, allowing a great degree of flexibility for data storage field firmware upgrades, etc. When on-chip bootloader is used, 120 kB of Flash memory is available for user code.

The LPC2104/2105/2106 Flash memory provides a minimum of 100,000 erase/write cycles and 20 years of data retention.

6.3 On-Chip static RAM

On-Chip static RAM may be used for code and/or data storage. The SRAM may be accessed as 8-bits, 16-bits, and 32-bits. The LPC2104 provides a 16 kB static RAM, the LPC2105 provides a 32 kB static RAM, and the LPC2106 provides a 64 kB static RAM.

9397 750 14476 |

© Koninklijke Philips Electronics N.V. 2004. All rights reserved. |

Product data |

Rev. 05 — 22 December 2004 |

8 of 32 |

Philips Semiconductors |

LPC2104/2105/2106 |

|

Single-chip 32-bit microcontrollers |

6.4 Memory map

The LPC2104, LPC2105 and LPC2106 memory maps incorporate several distinct regions, as shown in the following figures.

In addition, the CPU interrupt vectors may be re-mapped to allow them to reside in either Flash memory (the default) or on-chip static RAM. This is described in Section 6.17 “System control”.

4.0 GB

3.75 GB

3.5 GB

3.0 GB

2.0 GB

1.0 GB

0.0 GB

AHB PERIPHERALS

VPB PERIPHERALS

RESERVED ADDRESS SPACE

BOOT BLOCK (RE-MAPPED FROM ON-CHIP FLASH MEMORY

RESERVED ADDRESS SPACE

16 KBYTE ON-CHIP STATIC RAM

RESERVED ADDRESS SPACE

128 KBYTE ON-CHIP FLASH MEMORY

0xFFFF FFFF

0xF000 0000 0xEFFF FFFF

0xE000 0000 0xDFFF FFFF

0xC000 0000

0x8000 0000 0x7FFF FFFF

0x7FFF E000 0x7FFF DFFF

0x4001 0000

0x4000 3FFF

0x4000 0000 0x3FFF FFFF

0x0002 0000

0x0001 FFFF

0x0000 0000

002aaa415

Fig 3. LPC2104 memory map.

9397 750 14476 |

© Koninklijke Philips Electronics N.V. 2004. All rights reserved. |

Product data |

Rev. 05 — 22 December 2004 |

9 of 32 |

Philips Semiconductors |

LPC2104/2105/2106 |

|

Single-chip 32-bit microcontrollers |

4.0 GB

3.75 GB

3.5 GB

3.0 GB

2.0 GB

1.0 GB

0.0 GB

AHB PERIPHERALS

VPB PERIPHERALS

RESERVED ADDRESS SPACE

BOOT BLOCK (RE-MAPPED FROM ON-CHIP FLASH MEMORY

RESERVED ADDRESS SPACE

32 KBYTE ON-CHIP STATIC RAM

RESERVED ADDRESS SPACE

128 KBYTE ON-CHIP FLASH MEMORY

0xFFFF FFFF

0xF000 0000 0xEFFF FFFF

0xE000 0000 0xDFFF FFFF

0xC000 0000

0x8000 0000 0x7FFF FFFF

0x7FFF E000 0x7FFF DFFF

0x4000 8000

0x4000 7FFF

0x4000 0000 0x3FFF FFFF

0x0002 0000

0x0001 FFFF

0x0000 0000

002aaa414

Fig 4. LPC2105 memory map.

9397 750 14476 |

© Koninklijke Philips Electronics N.V. 2004. All rights reserved. |

Product data |

Rev. 05 — 22 December 2004 |

10 of 32 |

Loading...

Loading...