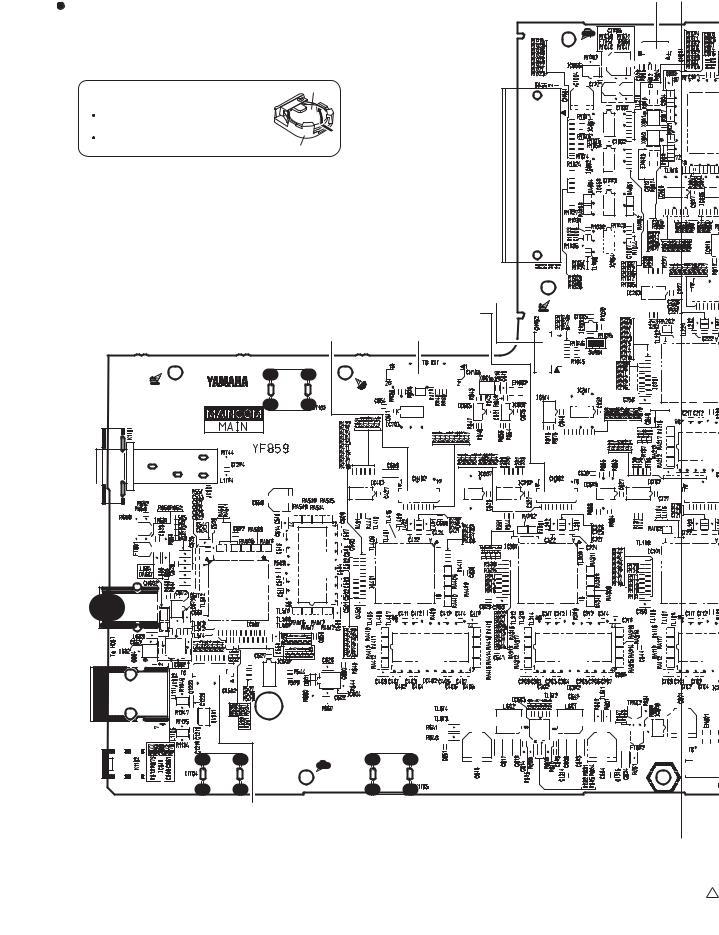

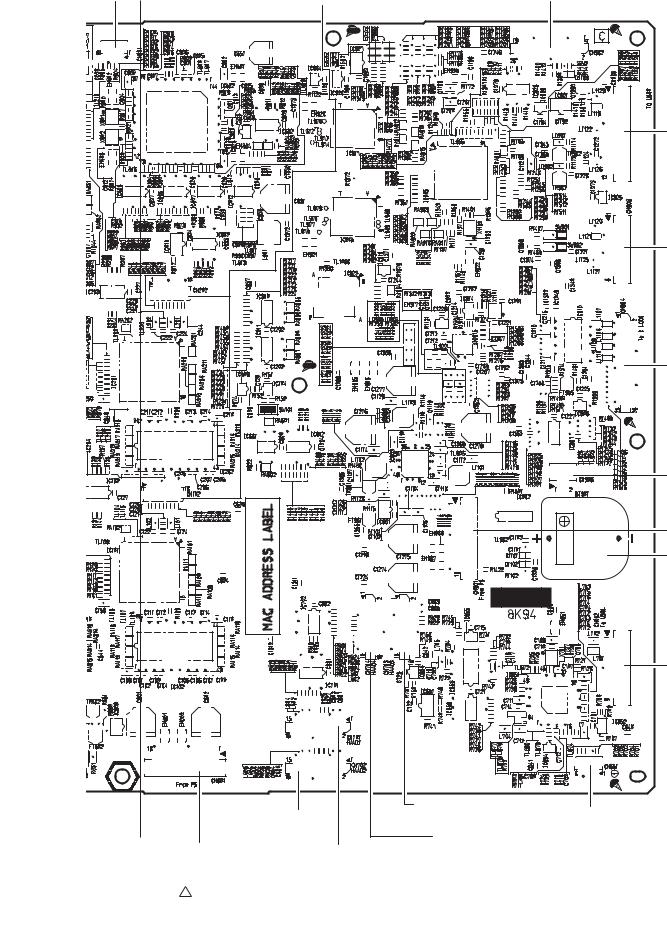

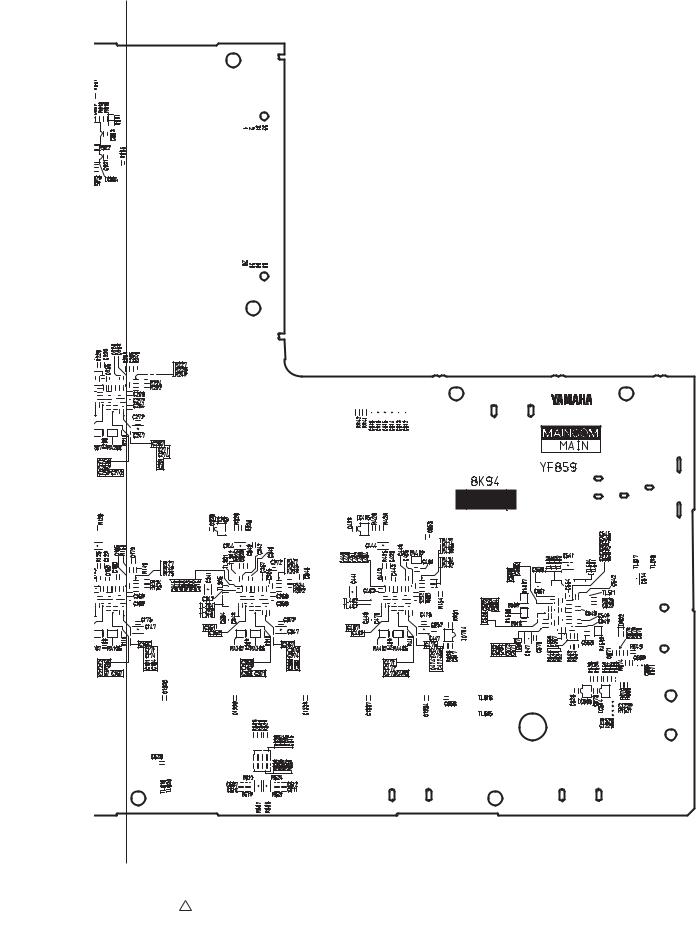

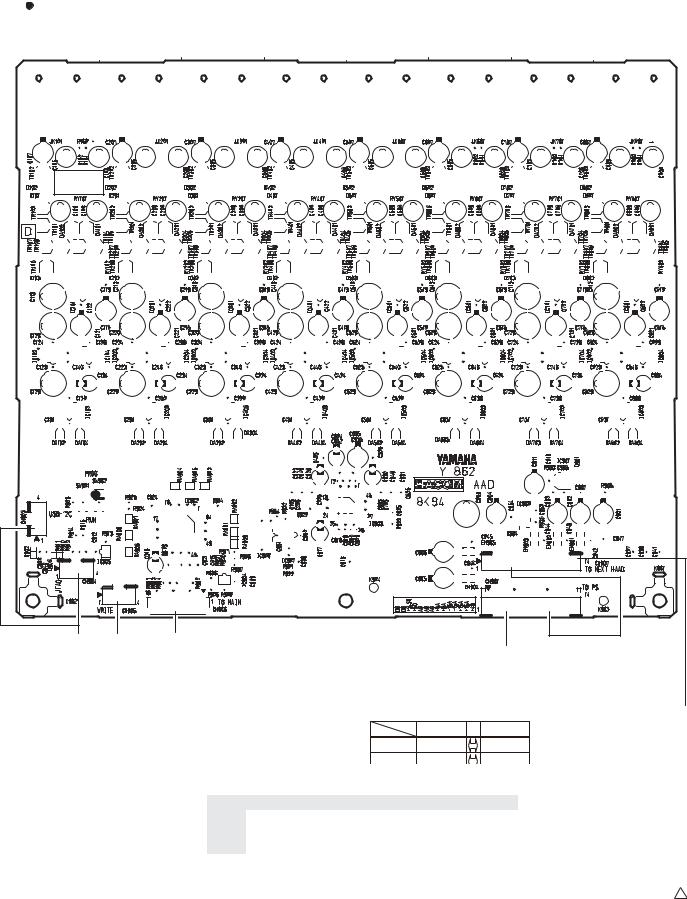

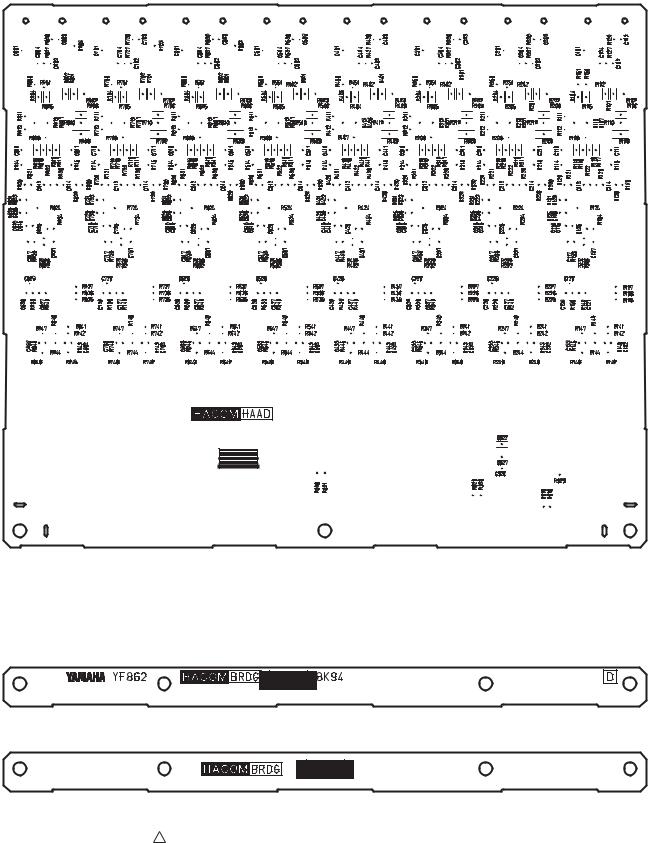

Yamaha TF-5, TF-3, TF-1 Service Manual

CS5368-CQZR (X8488A00) ADC (Analog to Digital Converter)

CS5368-CQZR (X8488A00) ADC (Analog to Digital Converter)

TF5/TF3/TF1

HAAD (HACOM): IC903

PIN |

NAME |

I/O |

FUNCTION |

PIN |

NAME |

I/O |

FUNCTION |

|||||

NO. |

NO. |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

AIN2+ |

I |

Differential Analog– Audio signals are |

24 |

LRCK/FS |

I/O |

Serial Audio Channel Clock– In I2S Mode, |

|||||

2 |

AIN2- |

I |

presented differently to the delta sigma |

|

|

|

|

|

|

|

Serial Audio Channel Select. When low, the |

|

|

|

|

modulators via the AIN+/- pins. |

|

|

|

|

|

|

|

odd channels are selected. |

|

3 |

GND |

I |

Ground– Ground reference. Must be |

|

|

|

|

|

|

|

In LJ Mode, Serial Audio Channel Select. |

|

|

|

|

connected to analog ground. |

|

|

|

|

|

|

|

When high, the odd channels are selected. |

|

4 |

VA |

I |

Analog Power– Positive power supply for |

|

|

|

|

|

|

|

In TDM Mode, a frame sync signal. When |

|

5 |

REF_GND |

I |

the analog section |

|

|

|

|

|

|

|

high, it marks the beginning of a new frame |

|

Reference Ground– For the internal sampling |

|

|

|

|

|

|

|

of serial audio samples. In Slave Mode, this |

||||

6 |

FILT+ |

O |

circuits. Must be connected to analog ground. |

|

|

|

|

|

|

|

pin acts as an input pin. |

|

Positive Voltage Reference– Reference |

25 |

|

SCLK |

I/O |

Main timing clock for the Serial Audio Interface– |

|||||||

7 |

VQ |

O |

voltage for internal sampling circuits. |

|

|

|

|

|

|

|

During Master Mode, this pin acts as an output, |

|

Quiescent Voltage– Filter connection for |

|

|

|

|

|

|

|

and during Slave Mode it acts as an input pin. |

||||

8 |

GND |

I |

the internal quiescent reference voltage. |

26 |

SDOUT4 |

O |

Serial Audio Data– Channels 7,8. |

|||||

Ground– Ground reference. Must be |

27 |

SDOUT2 |

O |

Serial Audio Data– Channels 3,4. |

||||||||

9 |

VA |

I |

connected to analog ground. |

28 |

|

|

VLS |

I |

Serial Audio Interface Power– Positive |

|||

Analog Power– Positive power supply for |

|

|

|

|

|

|

|

power for the serial audio interface. |

||||

10 |

GND |

I |

the analog section |

29 |

|

GND |

I |

Ground– Ground reference. Must be |

||||

Ground– Ground reference. Must be |

|

|

|

|

|

|

|

connected to analog ground. |

||||

11 |

AIN4+ |

I |

connected to analog ground. |

30 |

SDOUT1 |

O |

Serial Audio Data– Channels 1,2. |

|||||

|

31 |

SDOUT3 |

O |

Serial Audio Data– Channels 5,6. |

||||||||

12 |

AIN4- |

I |

|

32 |

|

GND |

I |

Ground– Ground reference. Must be |

||||

13 |

AIN3+ |

I |

Differential Analog– Audio signals are |

|

|

|

|

|

|

|

connected to analog ground. |

|

14 |

AIN3- |

I |

33 |

|

|

VD |

I |

Digital Power– Positive power supply for |

||||

presented differently to the delta sigma |

|

|

||||||||||

15 |

AIN7+ |

I |

|

|

|

|

|

|

|

the digital section. |

||

modulators via the AIN+/- pins. |

|

|

|

|

|

|

|

|||||

16 |

AIN7- |

I |

34 |

CLKMODE |

I |

CLKMODE– Setting this pin HIGH places |

||||||

|

||||||||||||

17 |

AIN8+ |

I |

|

|

|

|

|

|

|

|

a divide-by-1.5 circuit in the MCLK path to |

|

18 |

AIN8- |

I |

|

|

|

|

|

|

|

|

the core device circuitry. |

|

19 |

GND |

I |

Ground– Ground reference. Must be |

35 |

|

|

VLC |

I |

Control Port Interface Power– Positive |

|||

20 |

VX |

I |

connected to analog ground. |

|

|

|

|

|

|

|

power for the control port interface. |

|

Crystal Oscillator Power– Also powers control |

36 |

|

OVFL |

|

O |

Overflow– Detects an overflow condition |

||||||

21 |

XTI |

I/O |

logic to enable or disable oscillator circuits. |

|

|

|

|

|

|

|

on both left and right channels. |

|

Crystal Oscillator Connections– I/O pins |

37 |

|

DIF1 |

I |

DIF1, DIF0– Inputs of the audio interface |

|||||||

22 |

XTO |

I/O |

for an external crystal which may be used |

38 |

|

DIF0 |

I |

format. |

||||

23 |

MCLK |

I/O |

to generate MCLK. |

39 |

|

|

M1 |

I |

Mode Selection– Determines the |

|||

System Master Clock– When a crystal is |

40 |

|

|

M0 |

I |

operational mode of the device. |

||||||

|

|

|

used, this pin acts as a buffered MCLK |

41 |

|

|

RST |

|

I |

Reset– The device enters a low power |

||

|

|

|

Source (Output). When the oscillator function |

|

|

|

|

|

|

|

mode when low. |

|

|

|

|

is not used, this pin acts as an input for the |

42 |

|

MDIV |

I |

MCLK Divider– Setting this pin HIGH |

||||

|

|

|

system master clock. In this case, the XTI |

|

|

|

|

|

|

|

places a divide-by-2 circuit in the MCLK |

|

|

|

|

and XTO pins must be tied low. |

43 |

AIN6+ |

I |

path to the core device circuitry. |

|||||

|

|

|

|

|

||||||||

|

|

|

|

44 |

|

AIN6- |

I |

Differential Analog– Audio signals are |

||||

|

|

|

|

45 |

AIN5+ |

I |

||||||

|

|

|

|

presented differently to the delta sigma |

||||||||

|

|

|

|

46 |

|

AIN5- |

I |

|||||

|

|

|

|

|

modulators via the AIN+/- pins. |

|||||||

|

|

|

|

47 |

AIN1+ |

I |

||||||

|

|

|

|

|

||||||||

|

|

|

|

48 |

|

AIN1- |

I |

|

||||

AK4396VF-E2 (X8324A00) DAC (Digital to Analog Converter) |

DA1 (DACOM): IC901 |

|||||||

PIN |

NAME |

I/O |

FUNCTION |

PIN |

NAME |

I/O |

FUNCTION |

|

NO. |

NO. |

|||||||

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

1 |

DVSS |

- |

Digital ground |

15 |

TTL |

I |

CMOS/TTL level select |

|

2 |

DVDD |

- |

Digital power supply +3.3 V |

16 |

VREFL |

I |

Low level voltage reference input |

|

3 |

MCLK |

I |

Master clock input |

17 |

VREFH |

I |

High level voltage reference input |

|

4 |

PDN |

I |

Power-down mode |

18 |

AVDD |

- |

Analog power supply +5 V |

|

5 |

BICK |

I |

Audio serial data clock |

19 |

AVSS |

- |

Analog ground |

|

6 |

SDATA |

I |

Audio serial data input |

20 |

AOUTR- |

O |

Rch negative analog output |

|

7 |

LRCK |

I |

L/R clock |

21 |

AOUTR+ |

O |

Rch positive analog output |

|

8 |

SMUTE/CSN |

I |

Soft mute/Chip select |

22 |

AOUTL- |

O |

Lch negative analog output |

|

9 |

DFS0/CAD0 |

I |

Sampling speed mode select/Chip address 0 |

23 |

AOUTL+ |

O |

Lch positive analog output |

|

10 |

DEM0/CCLK |

I |

De-emphasis enable 0/Control data clock |

24 |

VCOM |

O |

Common voltage output |

|

11 |

DEM1/CDTI |

I |

De-emphasis enable 1/Control data input |

25 |

P/S |

I |

Parallel/serial select |

|

12 |

DIF0 |

I |

|

26 |

TST1/DZFL |

O |

Test 1/Lch zero input detect |

|

13 |

DIF1 |

I |

Digital input format |

27 |

TST2/CAD1 |

I |

Test 2/Chip address 1 |

|

14 |

DIF2 |

I |

|

28 |

ACKS/DZFR |

I/O |

Master clock auto setting mode/Rch zero input detect |

|

|

|

|

|

|

|

|

|

|

91

TF5/TF3/TF1

AM3352BZCZ60 (YF449B00) MICROPROCESSOR (MPU)

AM3352BZCZ60 (YF449B00) MICROPROCESSOR (MPU)

MAIN (MAINCOM): IC905

PIN |

Outer |

Name |

I/O |

Function |

PIN |

Outer |

Name |

I/O |

Function |

|

NO. |

No |

NO. |

No |

|||||||

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

1 |

A1 |

VSS |

GND |

GND |

82 |

E10 |

VDDSHV6 |

VCC |

VDD for I/O |

|

2 |

A2 |

VDD_MPU_MON |

I |

Voltage Monitor Input(Not Used) |

83 |

E11 |

VDDSHV6 |

VCC |

VDD for I/O |

|

3 |

A3 |

RESERVED |

O |

Not Used |

84 |

E12 |

VDDSHV6 |

VCC |

VDD for I/O |

|

4 |

A4 |

OSC1_OUT |

O |

OSC1(for Internal RTC) Output |

85 |

E13 |

VDDSHV6 |

VCC |

VDD for I/O |

|

5 |

A5 |

VSS_RTC |

GND |

GND |

86 |

E14 |

VDDS |

VCC |

VDDS |

|

6 |

A6 |

OSC1_IN |

I |

OSC1(for Internal RTC) Input |

87 |

E15 |

UART0_RXD |

BIDIRECT |

UART Receive Data |

|

7 |

A7 |

AIN3 |

I |

A/D Input |

88 |

E16 |

UART0_TXD |

BIDIRECT |

UART Transmit Data |

|

8 |

A8 |

AIN6 |

I |

A/D Input |

89 |

E17 |

I2C1_SCL |

BIDIRECT |

I2C Clock |

|

9 |

A9 |

VREFN |

I |

Analog Negative Reference Input |

90 |

E18 |

I2C1_SDA |

BIDIRECT |

I2C0 Data |

|

10 |

A10 |

NRESETIN_OUT |

BIDIRECT |

Active low Warm Reset |

91 |

F1 |

DDR_CASN |

O |

DDR SDRAM COLUMN ADDRESS STROBE OUTPUT (ACTIVE LOW) |

|

11 |

A11 |

TDO |

O |

JTAG TEST DATA OUTPUT |

92 |

F2 |

DDR_A11 |

O |

DDR SDRAM ROW/COLUMN ADDRESS Output |

|

12 |

A12 |

TCK |

I |

JTAG TEST CLOCK |

93 |

F3 |

DDR_A0 |

O |

DDR SDRAM ROW/COLUMN ADDRESS Output |

|

13 |

A13 |

SPI1_SCLK |

BIDIRECT |

SPI Clock |

94 |

F4 |

DDR_A10 |

O |

DDR SDRAM ROW/COLUMN ADDRESS Output |

|

14 |

A14 |

GPIO3[21] |

BIDIRECT |

GPIO |

95 |

F5 |

VDDS_DDR |

VCC |

VDDS for DDR |

|

15 |

A15 |

SPI1_CS1 |

BIDIRECT |

SPI Chip Select |

96 |

F6 |

VDD_CORE |

VCC |

VDD for Core |

|

16 |

A16 |

SPI0_CS0 |

BIDIRECT |

SPI Chip Select |

97 |

F7 |

VDD_CORE |

VCC |

VDD for Core |

|

17 |

A17 |

SPI0_SCLK |

BIDIRECT |

SPI Clock |

98 |

F8 |

VSS |

GND |

GND |

|

18 |

A18 |

VSS |

GND |

GND |

99 |

F9 |

VDDS |

VCC |

VDDS |

|

19 |

B1 |

DDR_A5 |

O |

DDR SDRAM ROW/COLUMN ADDRESS Output |

100 |

F10 |

VDD_MPU |

VCC |

VDD for MPU |

|

20 |

B2 |

DDR_WEN |

O |

DDR SDRAM WRITE ENABLE OUTPUT (ACTIVE LOW) |

101 |

F11 |

VDD_MPU |

VCC |

VDD for MPU |

|

21 |

B3 |

DDR_BA2 |

O |

DDR SDRAM BANK ADDRESS OUTPUT |

102 |

F12 |

VDD_MPU |

VCC |

VDD for MPU |

|

22 |

B4 |

ENZ_KALDO_1P8V |

I |

Active low enable input for internal CAP_VDD_RTC voltage regulator |

103 |

F13 |

VDD_MPU |

VCC |

VDD for MPU |

|

23 |

B5 |

RTC_PORZ |

I |

Active low RTC reset input |

104 |

F14 |

VDDSHV6 |

VCC |

VDD for I/O |

|

24 |

B6 |

AIN0 |

I |

A/D Input |

105 |

F15 |

USB1_DRVBUS |

BIDIRECT |

USB1 DRVBUS |

|

25 |

B7 |

AIN2 |

I |

A/D Input |

106 |

F16 |

USB0_DRVBUS |

BIDIRECT |

USB0 DRVBUS |

|

26 |

B8 |

AIN5 |

I |

A/D Input |

107 |

F17 |

GPIO2[26] |

BIDIRECT |

GPIO |

|

27 |

B9 |

VREFP |

I |

Analog Positive Reference Input |

108 |

F18 |

GPIO2[27] |

BIDIRECT |

GPIO |

|

28 |

B10 |

NTRST |

I |

JTAG TEST RESET (ACTIVE LOW) |

109 |

G1 |

DDR_ODT |

O |

ODT OUTPUT |

|

29 |

B11 |

TDI |

I |

JTAG TEST DATA INPUT |

110 |

G2 |

DDR_RESETN |

O |

R3/DDR3L RESET OUTPUT(Not Used) |

|

30 |

B12 |

GPIO3[18] |

BIDIRECT |

GPIO |

111 |

G3 |

DDR_CKE |

O |

DDR SDRAM CLOCK ENABLE OUTPUT |

|

31 |

B13 |

SPI1_D0 |

BIDIRECT |

SPI Data |

112 |

G4 |

DDR_RASN |

O |

DDR SDRAM ROW ADDRESS STROBE OUTPUT (ACTIVE LOW) |

|

32 |

B14 |

EMU1 |

BIDIRECT |

MISC EMULATION PIN |

113 |

G5 |

VDDS_DDR |

VCC |

VDDS for DDR |

|

33 |

B15 |

PWRONRSTn |

I |

Active low Power on Reset |

114 |

G6 |

VDD_CORE |

VCC |

VDD for Core |

|

34 |

B16 |

SPI0_D1 |

BIDIRECT |

SPI Data |

115 |

G7 |

VDD_CORE |

VCC |

VDD for Core |

|

35 |

B17 |

SPI0_D0 |

BIDIRECT |

SPI Data |

116 |

G8 |

VSS |

GND |

GND |

|

36 |

B18 |

NNMI |

I |

External Interrupt to ARM Cortext A8 core |

117 |

G9 |

VSS |

GND |

GND |

|

37 |

C1 |

DDR_A9 |

O |

DDR SDRAM ROW/COLUMN ADDRESS Output |

118 |

G10 |

VDD_CORE |

VCC |

VDD for Core |

|

38 |

C2 |

DDR_A4 |

O |

DDR SDRAM ROW/COLUMN ADDRESS Output |

119 |

G11 |

VSS |

GND |

GND |

|

39 |

C3 |

DDR_A3 |

O |

DDR SDRAM ROW/COLUMN ADDRESS Output |

120 |

G12 |

VSS |

GND |

GND |

|

40 |

C4 |

DDR_BA0 |

O |

DDR SDRAM BANK ADDRESS OUTPUT |

121 |

G13 |

VDD_MPU |

VCC |

VDD for MPU |

|

41 |

C5 |

EXT_WAKEUP |

I |

EXT_WAKEUP input |

122 |

G14 |

VDDSHV6 |

VCC |

VDD for I/O |

|

42 |

C6 |

PMIC_POWER_EN |

O |

PMIC_POWER_EN output(Not Used) |

123 |

G15 |

GPIO2[28] |

BIDIRECT |

GPIO |

|

43 |

C7 |

AIN1 |

I |

A/D Input |

124 |

G16 |

GPIO2[29] |

BIDIRECT |

GPIO |

|

44 |

C8 |

AIN4 |

I |

A/D Input |

125 |

G17 |

GPIO2[30] |

BIDIRECT |

GPIO |

|

45 |

C9 |

AIN7 |

I |

A/D Input |

126 |

G18 |

GPIO2[31] |

BIDIRECT |

GPIO |

|

46 |

C10 |

CAP_VBB_MPU |

VCC |

Cap for MPU Regulator |

127 |

H1 |

DDR_A1 |

O |

DDR SDRAM ROW/COLUMN ADDRESS Output |

|

47 |

C11 |

TMS |

I |

JTAG TEST MODE SELECT |

128 |

H2 |

DDR_CSN0 |

O |

DDR SDRAM CHIP SELECT OUTPUT |

|

48 |

C12 |

GPIO3[17] |

BIDIRECT |

GPIO |

129 |

H3 |

DDR_A13 |

O |

DDR SDRAM ROW/COLUMN ADDRESS Output |

|

49 |

C13 |

GPIO3[19] |

BIDIRECT |

GPIO |

130 |

H4 |

DDR_A14 |

O |

DDR SDRAM ROW/COLUMN ADDRESS Output |

|

50 |

C14 |

EMU0 |

BIDIRECT |

MISC EMULATION PIN |

131 |

H5 |

VDDS_DDR |

VCC |

VDDS for DDR |

|

51 |

C15 |

SPI0_CS1 |

BIDIRECT |

SPI Chip Select |

132 |

H6 |

VSS |

GND |

GND |

|

52 |

C16 |

I2C0_SCL |

BIDIRECT |

I2C Clock |

133 |

H7 |

VSS |

GND |

GND |

|

53 |

C17 |

I2C0_SDA |

BIDIRECT |

I2C0 Data |

134 |

H8 |

VSS |

GND |

GND |

|

54 |

C18 |

GPIO0[7] |

BIDIRECT |

GPIO |

135 |

H9 |

VSS |

GND |

GND |

|

55 |

D1 |

DDR_NCK |

O |

DDR SDRAM CLOCK OUTPUT (Differential-) |

136 |

H10 |

VSS |

GND |

GND |

|

56 |

D2 |

DDR_CK |

O |

DDR SDRAM CLOCK OUTPUT (Differential+) |

137 |

H11 |

VDD_CORE |

VCC |

VDD for Core |

|

57 |

D3 |

DDR_A15 |

O |

DDR SDRAM ROW/COLUMN ADDRESS Output |

138 |

H12 |

VSS |

GND |

GND |

|

58 |

D4 |

DDR_A8 |

O |

DDR SDRAM ROW/COLUMN ADDRESS Output |

139 |

H13 |

VDD_MPU |

VCC |

VDD for Core |

|

59 |

D5 |

DDR_A6 |

O |

DDR SDRAM ROW/COLUMN ADDRESS Output |

140 |

H14 |

VDDSHV4 |

VCC |

VDD for I/O |

|

60 |

D6 |

CAP_VDD_RTC |

VCC |

Cap for RTC |

141 |

H15 |

VDDS_PLL_MPU |

VCC |

VDDS for MPU PLL |

|

61 |

D7 |

VDDS_RTC |

VCC |

VDDS for RTC |

142 |

H16 |

GPIO3[0] |

BIDIRECT |

GPIO |

|

62 |

D8 |

VDDA_ADC |

VCC |

VDDA for ADC |

143 |

H17 |

RMII1_CRS_DV |

BIDIRECT |

RMII Carrier Sense / Data Valid |

|

63 |

D9 |

CAP_VDD_SRAM_CORE |

VCC |

Cap for SRAM Core VDD |

144 |

H18 |

RMII1_REFCLK |

BIDIRECT |

RMII Reference Clock |

|

64 |

D10 |

VDDS_SRAM_MPU_BB |

VCC |

VDDS for SRAM |

145 |

J1 |

DDR_D8 |

BIDIRECT |

DDR SDRAM DATA INPUT/OUTPUT |

|

65 |

D11 |

CAP_VDD_SRAM_MPU |

VCC |

Cap for VDD_SRAM_MPU |

146 |

J2 |

DDR_DQM1 |

O |

DDR WRITE ENABLE / DATA MASK FOR DATA[15:8] |

|

66 |

D12 |

SPI1_D1 |

BIDIRECT |

SPI Data |

147 |

J3 |

DDR_VTP |

I |

VTP Compensation Resistor |

|

67 |

D13 |

GPIO3[20] |

BIDIRECT |

GPIO |

148 |

J4 |

DDR_VREF |

I |

Voltage Reference Input |

|

68 |

D14 |

GPIO0[20] |

BIDIRECT |

GPIO |

149 |

J5 |

VDDS_DDR |

VCC |

VDDS for DDR |

|

69 |

D15 |

UART1_TXD |

BIDIRECT |

UART Transmit Data |

150 |

J6 |

VSS |

GND |

GND |

|

70 |

D16 |

UART1_RXD |

BIDIRECT |

UART Receive Data |

151 |

J7 |

VSS |

GND |

GND |

|

71 |

D17 |

I2C2_SCL |

BIDIRECT |

I2C Clock |

152 |

J8 |

VSS |

GND |

GND |

|

72 |

D18 |

I2C2_SDA |

BIDIRECT |

I2C0 Data |

153 |

J9 |

VSS |

GND |

GND |

|

73 |

E1 |

DDR_BA1 |

O |

DDR SDRAM BANK ADDRESS OUTPUT |

154 |

J10 |

VSS |

GND |

GND |

|

74 |

E2 |

DDR_A7 |

O |

DDR SDRAM ROW/COLUMN ADDRESS Output |

155 |

J11 |

VSS |

GND |

GND |

|

75 |

E3 |

DDR_A12 |

O |

DDR SDRAM ROW/COLUMN ADDRESS Output |

156 |

J12 |

VDD_CORE |

VCC |

VDD for Core |

|

76 |

E4 |

DDR_A2 |

O |

DDR SDRAM ROW/COLUMN ADDRESS Output |

157 |

J13 |

VDD_MPU |

VCC |

VDD for MPU |

|

77 |

E5 |

VDDS_DDR |

VCC |

VDDS for DDR |

158 |

J14 |

VDDSHV4 |

VCC |

VDD for I/O |

|

78 |

E6 |

VDDS |

VCC |

VDDS |

159 |

J15 |

RMII1_RXER |

BIDIRECT |

RMII Receive Data Error |

|

79 |

E7 |

VDDS_PLL_DDR |

VCC |

VDDS for DDR PLL |

160 |

J16 |

RMII1_TXEN |

BIDIRECT |

RMII Transmit Enable |

|

80 |

E8 |

VSSA_ADC |

GND |

GND(for ADC) |

161 |

J17 |

GPIO3[4] |

BIDIRECT |

GPIO |

|

81 |

E9 |

VDDS_SRAM_CORE_BG |

VCC |

VDDS for SRAM Core |

162 |

J18 |

UART4_RXD |

BIDIRECT |

UART Receive Data |

92

TF5/TF3/TF1

PIN |

Outer |

Name |

I/O |

Function |

PIN |

Outer |

Name |

I/O |

Function |

|

NO. |

No |

NO. |

No |

|||||||

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

163 |

K1 |

DDR_D9 |

BIDIRECT |

DDR SDRAM DATA INPUT/OUTPUT |

244 |

P10 |

VDDSHV2 |

VCC |

VDD for I/O |

|

164 |

K2 |

DDR_D10 |

BIDIRECT |

DDR SDRAM DATA INPUT/OUTPUT |

245 |

P11 |

VDDSHV2 |

VCC |

VDD for I/O |

|

165 |

K3 |

DDR_D11 |

BIDIRECT |

DDR SDRAM DATA INPUT/OUTPUT |

246 |

P12 |

VDDSHV3 |

VCC |

VDD for I/O |

|

166 |

K4 |

DDR_D12 |

BIDIRECT |

DDR SDRAM DATA INPUT/OUTPUT |

247 |

P13 |

VDDSHV3 |

VCC |

VDD for I/O |

|

167 |

K5 |

VDDS_DDR |

VCC |

VDDS for DDR |

248 |

P14 |

VDDS |

VCC |

VDDS |

|

168 |

K6 |

VDD_CORE |

VCC |

VDD for Core |

249 |

P15 |

USB0_VBUS |

I |

USB0 VBUS |

|

169 |

K7 |

VSS |

GND |

GND |

250 |

P16 |

USB0_ID |

I |

USB0 OTG ID |

|

170 |

K8 |

VDD_CORE |

VCC |

VDD for Core |

251 |

P17 |

USB1_ID |

I |

USB1 OTG ID (Not Used) |

|

171 |

K9 |

VSS |

GND |

GND |

252 |

P18 |

USB1_CE |

O |

USB1 Active high Charger Enable output (Not Used) |

|

172 |

K10 |

VSS |

GND |

GND |

253 |

R1 |

LCD_DATA0 / SYSBOOT0 |

BIDIRECT |

LCD data bus/BOOT Mode Set |

|

173 |

K11 |

VSS |

GND |

GND |

254 |

R2 |

LCD_DATA1 / SYSBOOT1 |

BIDIRECT |

LCD data bus/BOOT Mode Set |

|

174 |

K12 |

VDD_CORE |

VCC |

VDD for Core |

255 |

R3 |

LCD_DATA2 / SYSBOOT2 |

BIDIRECT |

LCD data bus/BOOT Mode Set |

|

175 |

K13 |

VDDS |

VCC |

VDDS |

256 |

R4 |

LCD_DATA3 / SYSBOOT3 |

BIDIRECT |

LCD data bus/BOOT Mode Set |

|

176 |

K14 |

VDDSHV5 |

VCC |

VDD for I/O |

257 |

R5 |

LCD HSYNC/GPIO2[23] |

BIDIRECT |

GPIO |

|

177 |

K15 |

UART4_TXD |

BIDIRECT |

UART Transmit Data |

258 |

R6 |

LCD_AC_BIAS_EN |

BIDIRECT |

LCD AC bias enable chip select |

|

178 |

K16 |

RMII1_TXD1 |

BIDIRECT |

RMII Transmit Data |

259 |

R7 |

GPIO2[2] |

BIDIRECT |

GPIO |

|

179 |

K17 |

RMII1_TXD0 |

BIDIRECT |

RMII Transmit Data |

260 |

R8 |

MMC1_DAT2 |

BIDIRECT |

MMC/SD/SDIO Data Bus |

|

180 |

K18 |

UART2_RXD |

BIDIRECT |

UART Receive Data |

261 |

R9 |

GPIO1[6] |

BIDIRECT |

GPIO |

|

181 |

L1 |

DDR_DQS1 |

BIDIRECT |

DDR DATA STROBE FOR DATA[15:8] (Differential+) |

262 |

R10 |

VDDS_PLL_CORE_LCD |

VCC |

VDDS for LCD PLL |

|

182 |

L2 |

DDR_DQSN1 |

BIDIRECT |

DDR DATA STROBE FOR DATA[15:8] (Differential-) |

263 |

R11 |

VDDS_OSC |

VCC |

VDDS for OSC |

|

183 |

L3 |

DDR_D13 |

BIDIRECT |

DDR SDRAM DATA INPUT/OUTPUT |

264 |

R12 |

GPIO1[13] |

BIDIRECT |

GPIO |

|

184 |

L4 |

DDR_D14 |

BIDIRECT |

DDR SDRAM DATA INPUT/OUTPUT |

265 |

R13 |

GPIO1[16] |

BIDIRECT |

GPIO |

|

185 |

L5 |

VDDS_DDR |

VCC |

VDDS for DDR |

266 |

R14 |

GPIO1[20] |

BIDIRECT |

GPIO |

|

186 |

L6 |

VDD_CORE |

VCC |

VDD for Core |

267 |

R15 |

VDDA3P3V_USB1 |

VCC |

VDDA for USB1(3.3V) |

|

187 |

L7 |

VDD_CORE |

VCC |

VDD for Core |

268 |

R16 |

VDDA1P8V_USB1 |

VCC |

VDDA for USB1(1.8V) |

|

188 |

L8 |

VDD_CORE |

VCC |

VDD for Core |

269 |

R17 |

USB1_DP |

BIDIRECT |

USB1 Data plus (Not Used) |

|

189 |

L9 |

VDD_CORE |

VCC |

VDD for Core |

270 |

R18 |

USB1_DM |

BIDIRECT |

USB1 Data minus (Not Used) |

|

190 |

L10 |

VSS |

GND |

GND |

271 |

T1 |

LCD_DATA4 / SYSBOOT4 |

BIDIRECT |

LCD data bus/BOOT Mode Set |

|

191 |

L11 |

VSS |

GND |

GND |

272 |

T2 |

LCD_DATA5 / SYSBOOT5 |

BIDIRECT |

LCD data bus/BOOT Mode Set |

|

192 |

L12 |

VSS |

GND |

GND |

273 |

T3 |

LCD_DATA6 / SYSBOOT6 |

BIDIRECT |

LCD data bus/BOOT Mode Set |

|

193 |

L13 |

VSS |

GND |

GND |

274 |

T4 |

LCD_DATA7 / SYSBOOT7 |

BIDIRECT |

LCD data bus/BOOT Mode Set |

|

194 |

L14 |

VDDSHV5 |

VCC |

VDD for I/O |

275 |

T5 |

LCD_DATA15 / SYSBOOT15 |

BIDIRECT |

LCD data bus/BOOT Mode Set |

|

195 |

L15 |

RMII1_RXD1 |

BIDIRECT |

RMII Receive Data |

276 |

T6 |

GPIO2[5] |

BIDIRECT |

GPIO |

|

196 |

L16 |

UART3_TXD |

BIDIRECT |

UART Transmit Data |

277 |

T7 |

GPIO2[3] |

BIDIRECT |

GPIO |

|

197 |

L17 |

UART3_RXD |

BIDIRECT |

UART Receive Data |

278 |

T8 |

MMC1_DAT3 |

BIDIRECT |

MMC/SD/SDIO Data Bus |

|

198 |

L18 |

UART2_TXD |

BIDIRECT |

UART Transmit Data |

279 |

T9 |

GPIO1[7] |

BIDIRECT |

GPIO |

|

199 |

M1 |

DDR_D15 |

BIDIRECT |

DDR SDRAM DATA INPUT/OUTPUT |

280 |

T10 |

GPIO0[23] |

BIDIRECT |

GPIO |

|

200 |

M2 |

DDR_DQM0 |

O |

DDR WRITE ENABLE / DATA MASK FOR DATA[7:0] |

281 |

T11 |

GPIO0[26] |

BIDIRECT |

GPIO |

|

201 |

M3 |

DDR_D0 |

BIDIRECT |

DDR SDRAM DATA INPUT/OUTPUT |

282 |

T12 |

GPIO1[12] |

BIDIRECT |

GPIO |

|

202 |

M4 |

DDR_D1 |

BIDIRECT |

DDR SDRAM DATA INPUT/OUTPUT |

283 |

T13 |

GPIO2[0] |

BIDIRECT |

GPIO |

|

203 |

M5 |

VPP |

NC |

(Not Used) |

284 |

T14 |

GPIO1[19] |

BIDIRECT |

GPIO |

|

204 |

M6 |

VSS |

GND |

GND |

285 |

T15 |

GPIO1[23] |

BIDIRECT |

GPIO |

|

205 |

M7 |

VSS |

GND |

GND |

286 |

T16 |

GPIO1[26] |

BIDIRECT |

GPIO |

|

206 |

M8 |

VSS |

GND |

GND |

287 |

T17 |

GPIO0[30] |

BIDIRECT |

GPIO |

|

207 |

M9 |

VSS |

GND |

GND |

288 |

T18 |

USB1_VBUS |

I |

USB1 VBUS (Not Used) |

|

208 |

M10 |

VSS |

GND |

GND |

289 |

U1 |

LCD_DATA8 / SYSBOOT8 |

BIDIRECT |

LCD data bus/BOOT Mode Set |

|

209 |

M11 |

VDD_CORE |

VCC |

VDD for Core |

290 |

U2 |

LCD_DATA9 / SYSBOOT9 |

BIDIRECT |

LCD data bus/BOOT Mode Set |

|

210 |

M12 |

VSS |

GND |

GND |

291 |

U3 |

LCD_DATA10 / SYSBOOT10 |

BIDIRECT |

LCD data bus/BOOT Mode Set |

|

211 |

M13 |

VDD_CORE |

VCC |

VDD for Core |

292 |

U4 |

LCD_DATA11 / SYSBOOT11 |

BIDIRECT |

LCD data bus/BOOT Mode Set |

|

212 |

M14 |

VSSA_USB |

GND |

GND(for USB Analog) |

293 |

U5 |

LCD VSYNC/GPIO2[22] |

BIDIRECT |

GPIO |

|

213 |

M15 |

USB0_CE |

O |

USB0 Active high Charger Enable output(Not Used) |

294 |

U6 |

GPIO2[4] |

BIDIRECT |

GPIO |

|

214 |

M16 |

RMII1_RXD0 |

BIDIRECT |

RMII Receive Data |

295 |

U7 |

MMC1_DAT0 |

BIDIRECT |

MMC/SD/SDIO Data Bus |

|

215 |

M17 |

MDIO_DATA |

BIDIRECT |

MDIO Data |

296 |

U8 |

GPIO1[4] |

BIDIRECT |

GPIO |

|

216 |

M18 |

MDIO_CLK |

O |

MDIO Clk |

297 |

U9 |

MMC1_CLK |

BIDIRECT |

MMC/SD/SDIO Clock |

|

217 |

N1 |

DDR_D2 |

BIDIRECT |

DDR SDRAM DATA INPUT/OUTPUT |

298 |

U10 |

GPIO0[22] |

BIDIRECT |

GPIO |

|

218 |

N2 |

DDR_D3 |

BIDIRECT |

DDR SDRAM DATA INPUT/OUTPUT |

299 |

U11 |

OSC0_OUT |

O |

High frequency oscillator output |

|

219 |

N3 |

DDR_D4 |

BIDIRECT |

DDR SDRAM DATA INPUT/OUTPUT |

300 |

U12 |

GPIO0[27] |

BIDIRECT |

GPIO |

|

220 |

N4 |

DDR_D5 |

BIDIRECT |

DDR SDRAM DATA INPUT/OUTPUT |

301 |

U13 |

GPIO1[15] |

BIDIRECT |

GPIO |

|

221 |

N5 |

VDDSHV6 |

VCC |

VDD for I/O |

302 |

U14 |

GPIO1[18] |

BIDIRECT |

GPIO |

|

222 |

N6 |

VDDS |

VCC |

VDDS |

303 |

U15 |

GPIO1[22] |

BIDIRECT |

GPIO |

|

223 |

N7 |

VSS |

GND |

GND |

304 |

U16 |

GPIO1[25] |

BIDIRECT |

GPIO |

|

224 |

N8 |

VDD_CORE |

VCC |

VDD for Core |

305 |

U17 |

GPIO0[31] |

BIDIRECT |

GPIO |

|

225 |

N9 |

VDD_CORE |

VCC |

VDD for Core |

306 |

U18 |

GPIO1[28] |

BIDIRECT |

GPIO |

|

226 |

N10 |

VSS |

GND |

GND |

307 |

V1 |

VSS |

GND |

GND |

|

227 |

N11 |

VSS |

GND |

GND |

308 |

V2 |

LCD_DATA12 / SYSBOOT12 |

BIDIRECT |

LCD data bus/BOOT Mode Set |

|

228 |

N12 |

VDD_CORE |

VCC |

VDD for Core |

309 |

V3 |

LCD_DATA13 / SYSBOOT13 |

BIDIRECT |

LCD data bus/BOOT Mode Set |

|

229 |

N13 |

VDD_CORE |

VCC |

VDD for Core |

310 |

V4 |

LCD_DATA14 / SYSBOOT14 |

BIDIRECT |

LCD data bus/BOOT Mode Set |

|

230 |

N14 |

VSSA_USB |

GND |

GND(for USB Analog) |

311 |

V5 |

LCD_PCLK |

BIDIRECT |

LCD pixel clock |

|

231 |

N15 |

VDDA3P3V_USB0 |

VCC |

VDDA for USB0(3.3V) |

312 |

V6 |

GPIO1[29] |

BIDIRECT |

GPIO |

|

232 |

N16 |

VDDA1P8V_USB0 |

VCC |

VDDA for USB0(1.8V) |

313 |

V7 |

MMC1_DAT1 |

BIDIRECT |

MMC/SD/SDIO Data Bus |

|

233 |

N17 |

USB0_DP |

BIDIRECT |

USB0 Data plus |

314 |

V8 |

GPIO1[5] |

BIDIRECT |

GPIO |

|

234 |

N18 |

USB0_DM |

BIDIRECT |

USB0 Data minus |

315 |

V9 |

MMC1_CMD |

BIDIRECT |

MMC/SD/SDIO Command |

|

235 |

P1 |

DDR_DQS0 |

BIDIRECT |

DDR DATA STROBE FOR DATA[7:0] (Differential+) |

316 |

V10 |

OSC0_IN |

I |

High frequency oscillator input |

|

236 |

P2 |

DDR_DQSN0 |

BIDIRECT |

DDR DATA STROBE FOR DATA[7:0] (Differential-) |

317 |

V11 |

VSS_OSC |

GND |

GND |

|

237 |

P3 |

DDR_D6 |

BIDIRECT |

DDR SDRAM DATA INPUT/OUTPUT |

318 |

V12 |

GPIO2[1] |

BIDIRECT |

GPIO |

|

238 |

P4 |

DDR_D7 |

BIDIRECT |

DDR SDRAM DATA INPUT/OUTPUT |

319 |

V13 |

GPIO1[14] |

BIDIRECT |

GPIO |

|

239 |

P5 |

VDDSHV6 |

VCC |

VDD for I/O |

320 |

V14 |

GPIO1[17] |

BIDIRECT |

GPIO |

|

240 |

P6 |

VDDSHV6 |

VCC |

VDD for I/O |

321 |

V15 |

GPIO1[21] |

BIDIRECT |

GPIO |

|

241 |

P7 |

VDDSHV1 |

VCC |

VDD for I/O |

322 |

V16 |

GPIO1[24] |

BIDIRECT |

GPIO |

|

242 |

P8 |

VDDSHV1 |

VCC |

VDD for I/O |

323 |

V17 |

GPIO1[27] |

BIDIRECT |

GPIO |

|

243 |

P9 |

VDDS |

VCC |

VDDS |

324 |

V18 |

VSS |

GND |

GND |

93

TF5/TF3/TF1

SN75LVDS84ADGGR (X4212A0R) LVDS TRANSMITTERS

SN75LVDS84ADGGR (X4212A0R) LVDS TRANSMITTERS

MAIN (MAINCOM): IC916

PIN |

NAME |

I/O |

FUNCTION |

PIN |

NAME |

I/O |

FUNCTION |

|

NO. |

NO. |

|||||||

|

|

|

|

|

|

|||

1 |

D4 |

I/O |

Data bus |

25 |

D20 |

I/O |

Data bus |

|

2 |

VCC |

- |

Power supply |

26 |

CLKIN |

I |

Input clock for CLKIN MIDI |

|

3 |

D5 |

I/O |

Data bus |

27 |

SHTDN |

|

|

|

4 |

D6 |

I/O |

28 |

PLLGND |

- |

Ground |

||

|

||||||||

5 |

GND |

- |

Ground |

29 |

PLLVCC |

- |

Power supply |

|

6 |

D7 |

I/O |

Data bus |

30 |

PLLGND |

- |

Goround |

|

7 |

D8 |

I/O |

31 |

LVDSGND |

- |

|||

|

|

|||||||

8 |

VCC |

- |

Power supply |

32 |

CLKOUTP |

O |

Clock output |

|

9 |

D9 |

I/O |

|

33 |

CLKOUTM |

O |

||

Data bus |

|

|||||||

10 |

D10 |

I/O |

34 |

Y2P |

|

|

||

|

|

|

||||||

11 |

GND |

- |

Ground |

35 |

Y2M |

|

|

|

12 |

D11 |

I/O |

Data bus |

36 |

LVDSGND |

- |

Ground |

|

13 |

D12 |

I/O |

37 |

LVDSVCC |

- |

Power supply |

||

|

||||||||

14 |

NC |

- |

Not used |

38 |

Y1P |

|

|

|

15 |

D13 |

I/O |

Data bus |

39 |

Y1M |

|

|

|

16 |

D14 |

I/O |

40 |

Y0P |

|

|

||

|

|

|

||||||

17 |

GND |

- |

Ground |

41 |

Y0M |

|

|

|

18 |

D15 |

I/O |

|

42 |

LVDSGND |

- |

Ground |

|

19 |

D16 |

I/O |

Data bus |

43 |

NC |

- |

Not used |

|

20 |

D17 |

I/O |

|

44 |

D0 |

I/O |

Data bus |

|

21 |

VCC |

- |

Power supply |

45 |

D1 |

I/O |

||

|

||||||||

22 |

D18 |

I/O |

Data bus |

46 |

GND |

- |

Ground |

|

23 |

D19 |

I/O |

47 |

D2 |

I/O |

|

||

|

Data bus |

|||||||

24 |

GND |

- |

Ground |

48 |

D3 |

I/O |

||

|

SN75LVDS86ADGGR (X6818A00) LVDS RECEIVER

SN75LVDS86ADGGR (X6818A00) LVDS RECEIVER

LCDC (PNCOM): IC602

PIN |

NAME |

I/O |

FUNCTION |

PIN |

NAME |

I/O |

FUNCTION |

|

NO. |

NO. |

|||||||

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

1 |

D17 |

I/O |

Data bus |

25 |

GND |

- |

Ground |

|

2 |

D18 |

I/O |

26 |

D1 |

I/O |

Data bus |

||

|

||||||||

3 |

GND |

- |

Ground |

27 |

D2 |

I/O |

||

|

||||||||

4 |

D19 |

I/O |

Data bus |

28 |

Vcc |

- |

Power supply |

|

5 |

D20 |

I/O |

29 |

D3 |

I/O |

|

||

|

|

|||||||

6 |

NC |

- |

Not used |

30 |

D4 |

I/O |

Data bus |

|

7 |

LVDSGND |

- |

Ground |

31 |

D5 |

I/O |

|

|

8 |

A0M |

I/O |

Serialization signals for D0 through D6 |

32 |

GND |

- |

Ground |

|

9 |

A0P |

I/O |

33 |

D6 |

I/O |

|

||

|

|

|||||||

10 |

A1M |

I/O |

Serialization signals for D7 through D13 |

34 |

D7 |

I/O |

Data bus |

|

11 |

A1P |

I/O |

35 |

D8 |

I/O |

|

||

|

|

|||||||

12 |

LVDSVcc |

- |

Power supply |

36 |

Vcc |

- |

Power supply |

|

13 |

LVDSGND |

- |

Ground |

37 |

D9 |

I/O |

Data bus |

|

14 |

A2M |

I/O |

Serialization signals for D14 through D20 |

38 |

GND |

- |

Ground |

|

15 |

A2P |

I/O |

39 |

D10 |

I/O |

|

||

|

|

|||||||

16 |

CLKINM |

I |

Serialization signals for clock signal |

40 |

D11 |

I/O |

Data bus |

|

17 |

CLKINP |

I |

41 |

D12 |

I/O |

|

||

|

|

|||||||

18 |

LVDSGND |

- |

Ground |

42 |

Vcc |

- |

Power supply |

|

19 |

PLLGND |

- |

Ground |

43 |

D13 |

I/O |

Data bus |

|

20 |

PLLVcc |

- |

Power supply |

44 |

GND |

- |

Ground |

|

21 |

PLLGND |

- |

Ground |

45 |

D14 |

I/O |

|

|

22 |

SHTDN |

I/O |

Output control signals for clock and data bus |

46 |

D15 |

I/O |

Data bus |

|

23 |

CLKOUT |

O |

Clock output |

47 |

D16 |

I/O |

|

|

24 |

D0 |

I/O |

Data bus |

48 |

Vcc |

- |

Power supply |

94

CS4385A-DQZR (YF811A00) DAC (Digital to Analog Converter)

CS4385A-DQZR (YF811A00) DAC (Digital to Analog Converter)

TF5/TF3/TF1

DA1 (DACOM): IC004 DA2: IC002

PIN |

NAME |

I/O |

FUNCTION |

PIN |

NAME |

I/O |

FUNCTION |

|||

NO. |

NO. |

|||||||||

|

|

|

|

|

|

|

|

|||

1 |

DSDA2 |

I |

|

21 |

VQ |

O |

Quiescent Voltage - Filter connection for |

|||

|

|

|

|

|

|

|

|

|

internal quiescent voltage. |

|

2 |

DSDB1 |

I |

Direct Stream Digital Input - Input for Direct |

22 |

MUTEC234 |

O |

Mute Control |

|||

|

|

|

|

|

Stream Digital serial audio data. |

23 |

AOUTB4- |

O |

|

|

3 |

DSDA1 |

I |

|

24 |

AOUTB4+ |

O |

|

|||

|

|

|

|

|

|

25 |

AOUTA4+ |

O |

|

|

4 |

|

VD |

I |

Digital Power - Positive power supply for the |

26 |

AOUTA4- |

O |

Differential Analog Output. |

||

|

|

|

|

|

digital section. |

27 |

AOUTB3- |

O |

||

|

|

|

|

|

|

|||||

5 |

GND |

I |

Ground |

28 |

AOUTB3+ |

O |

|

|||

6 |

MCLK |

I |

Master Clock - Clock source for the delta- |

29 |

AOUTA3+ |

O |

|

|||

|

|

|

|

|

sigma modulator and digital filters. |

30 |

AOUTA3- |

O |

|

|

7 |

LRCK |

I |

Left Right Clock - Determines which channel, |

31 |

GND |

I |

Ground |

|||

|

|

|

|

|

Left or Right, is currently active on the serial |

32 |

VA |

I |

Analog Power - Positive power supply for the |

|

|

|

|

|

|

audio data line. |

|

|

|

analog section. |

|

8 |

SDIN1 |

I |

Serial Audio Data Input - Input for two’s |

33 |

AOUTB2- |

O |

|

|||

|

|

|

|

|

complement serial audio data. |

34 |

AOUTB2+ |

O |

|

|

9 |

SCLK |

I |

Serial Clock - Serial clock for the serial audio |

35 |

AOUTA2+ |

O |

|

|||

|

|

|

|

|

interface. |

36 |

AOUTA2- |

O |

Differential Analog Output. |

|

10 |

M4(TST) |

I |

Mode Selection (Test) |

37 |

AOUTB1- |

O |

||||

|

||||||||||

11 |

SDIN2 |

I |

Serial Audio Data Input - Input for two’s |

38 |

AOUTB1+ |

O |

|

|||

|

|

|

|

|

complement serial audio data. |

39 |

AOUTA1+ |

O |

|

|

12 |

M3(TST) |

I |

Mode Selection (Test) |

40 |

AOUTA1- |

O |

|

|||

13 |

SDIN3 |

I |

Serial Audio Data Input - Input for two’s |

41 |

MUTEC1 |

O |

Mute Control |

|||

|

|

|

|

|

complement serial audio data. |

42 |

DSD_ |

I |

DSD Serial Clock - Serial clock for the Direct |

|

14 |

SDIN4 |

I |

Serial Audio Data Input - Input for two’s |

|

SCLK |

|

Stream Digital audio interface. |

|||

|

|

|

|

|

complement serial audio data. |

43 |

VLS |

I |

Serial Audio Interface Power - Determines |

|

15 |

|

M2 |

I |

Mode Selection (Serial Control Port Clock - |

|

|

|

the required signal level for the serial audio |

||

|

(SCL/CCLK) |

|

Serial clock for the serial control port) |

|

|

|

interface. |

|||

16 |

|

M1 |

I/O |

Mode Selection (Serial Control Data) |

44 |

DSDB4 |

I |

|

||

|

(SDA/CDIN) |

|

Mode Selection (Address Bit 0 (I²C) / Chip |

|

|

|

|

|||

17 |

|

M0 |

I |

Select (SPI) - AD0 is a chip address pin in |

45 |

DSDA4 |

I |

|

||

|

(AD0/CS) |

|

I²C Mode) |

|

|

|

Direct Stream Digital Input - Input for Direct |

|||

18 |

|

VLC |

I |

Control Port Power - Determines the required |

46 |

DSDB3 |

I |

|||

|

Stream Digital serial audio data. |

|||||||||

|

|

|

|

|

signal level for the control port. |

|

|

|

||

|

|

|

|

|

|

|

|

|

||

19 |

|

|

|

I |

Reset - The device enters a low power mode |

47 |

DSDA3 |

I |

|

|

|

RST |

|

||||||||

|

|

|

|

|

and all internal registers are reset to their |

|

|

|

|

|

|

|

|

|

|

default settings when low. |

48 |

DSDB2 |

I |

|

|

20 |

FILT+ |

O |

Positive Voltage Reference - Positive |

|

|

|

|

|||

|

|

|

|

|

reference voltage for the internal sampling |

|

|

|

|

|

|

|

|

|

|

circuits. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

95

TF5/TF3/TF1

MB9AF132LAPMC1 (YF746B00) MICROCONTROLLER (MCU)

MB9AF132LAPMC1 (YF746B00) MICROCONTROLLER (MCU)

HAAD (HACOM): IC902

PIN |

NAME |

I/O |

FUNCTION |

PIN |

NAME |

I/O |

FUNCTION |

|

NO. |

NO. |

|||||||

|

|

|

|

|

|

|||

1 |

VCC |

- |

Power supply |

41 |

AVCC |

- |

A/D converter analog power pin |

|

2 |

P50 |

I/O |

|

42 |

AVRH |

- |

A/D converter analog reference voltage input |

|

3 |

P51 |

I/O |

General-purpose I/O port 5 |

|

|

|

pin. |

|

4 |

P52 |

I/O |

|

43 |

AVSS |

- |

A/D converter GND pin |

|

5 |

P30 |

I/O |

|

44 |

SDA2_2 |

O |

Multi-function serial interface ch.2 output pin. |

|

6 |

P31 |

I/O |

|

|

|

|

This pin operates as SOT2 when it is used in |

|

7 |

P32 |

I/O |

|

|

|

|

a UART/CSIO (operation modes 0 to 2) and |

|

8 |

P33 |

I/O |

|

|

|

|

as SDA2 when it is used in an I2C (operation |

|

9 |

P39 |

I/O |

|

|

|

|

mode 4). |

|

10 |

P3A |

I/O |

General-purpose I/O port 3 |

45 |

SCL2_2 |

I/O |

Multi-function serial interface ch.2 clock I/ |

|

11 |

P3B |

I/O |

|

|

|

|

O pin. This pin operates as SCK2 when it is |

|

12 |

P3C |

I/O |

|

|

|

|

used in a UART/CSIO (operation modes 0 |

|

13 |

P3D |

I/O |

|

|

|

|

to 2) and as SCL2 when it is used in an I2C |

|

14 |

P3E |

I/O |

|

|

|

|

(operation mode 4). |

|

15 |

P3F |

I/O |

|

46 |

P23 |

I/O |

General-purpose I/O port 2 |

|

16 |

VSS |

- |

GND |

47 |

P22/SDA0_0 |

I/O |

General-purpose I/O port 2/Multi-function |

|

17 |

C |

- |

Power stabilization capacity pin |

|

|

|

serial interface ch.0 output pin. This pin |

|

18 |

VCC |

- |

Power supply |

|

|

|

operates as SOT0 when it is used in a UART/ |

|

19 |

P46 |

I/O |

General-purpose I/O port 4 |

|

|

|

CSIO (operation modes 0 to 2) and as SDA0 |

|

20 |

P47 |

I/O |

|

|

|

when it is used in an I2C (operation mode 4). |

||

|

|

|

|

|||||

21 |

INITX |

I |

External Reset Input pin. A reset is valid |

48 |

SIN0_0 |

I |

Multi-function serial interface ch.0 input pin. |

|

|

|

|

when INITX = L. |

49 |

P00/TRSTX |

I/O |

General-purpose I/O port 0/J-TAG reset Input |

|

22 |

P49 |

I/O |

|

|

|

|

pin. |

|

23 |

P4A |

I/O |

|

50 |

P01/TCK |

I/O |

General-purpose I/O port 0/J-TAG test clock |

|

24 |

P4B |

I/O |

General-purpose I/O port 4 |

|

|

|

input pin. |

|

25 |

P4C |

I/O |

51 |

P02/TDI |

I/O |

General-purpose I/O port 0/J-TAG test data |

||

|

||||||||

26 |

P4D |

I/O |

|

|

|

|

input pin. |

|

27 |

P4E |

I/O |

|

52 |

P03/TMS |

I/O |

General-purpose I/O port 0/J-TAG test mode |

|

28 |

PE0/MD1 |

I/O |

General-purpose I/O port E/Mode 1 pin. |

|

|

|

state input/output pin. |

|

|

|

|

During normal operation, input is not needed |

53 |

P04/TDO |

I/O |

General-purpose I/O port 0/J-TAG debug |

|

|

|

|

During serial programming to flash memory, |

|

|

|

data output pin. |

|

|

|

|

MD1 = L must be input. |

54 |

P0A |

I/O |

|

|

29 |

MD0 |

I |

Mode 0 pin. During normal operation, MD0 = |

55 |

P0B |

I/O |

General-purpose I/O port 0 |

|

|

|

|

L must be input During serial programming to |

56 |

P0C |

I/O |

||

|

|

|

|

|||||

|

|

|

flash memory, MD0 = H must be input. |

57 |

P0F |

I/O |

|

|

30 |

PE2 |

I/O |

General-purpose I/O port E |

58 |

P62 |

I/O |

|

|

31 |

PE3 |

I/O |

59 |

P61 |

I/O |

General-purpose I/O port 6 |

||

|

||||||||

32 |

VSS |

- |

GND |

60 |

P60 |

I/O |

|

|

33 |

VCC |

- |

Power supply |

61 |

P80 |

I/O |

|

|

34 |

P10 |

I/O |

|

62 |

P81 |

I/O |

General-purpose I/O port 8 |

|

35 |

P11 |

I/O |

|

63 |

P82 |

I/O |

|

|

36 |

P12 |

I/O |

|

64 |

VSS |

- |

GND |

|

37 |

P13 |

I/O |

General-purpose I/O port 1 |

|

|

|

|

|

38 |

P14 |

I/O |

|

|

|

|

|

|

39 |

P15 |

I/O |

|

|

|

|

|

|

40 |

P17 |

I/O |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

96

GL852G-MNG03 (YC486A00) USB 2.0 MTT HUB CONTROLLER

GL852G-MNG03 (YC486A00) USB 2.0 MTT HUB CONTROLLER

TF5/TF3/TF1

USBR (MAINCOM): IC002

PIN |

NAME |

I/O |

FUNCTION |

PIN |

NAME |

I/O |

FUNCTION |

|

NO. |

NO. |

|||||||

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

1 |

AVDD |

- |

Analog power supply +3.3 V |

25 |

SEL48# |

- |

Digital power supply +3.3 V |

|

2 |

AGND |

- |

Analog ground |

26 |

RESET# |

I |

External reset input |

|

3 |

DM0 |

I/O |

USB signals for USPORT |

27 |

TEST |

I |

Test signal |

|

4 |

DP0 |

I/O |

28 |

OVCUR4# |

I |

Over current indicator for DSPORT4 |

||

|

||||||||

5 |

DM1 |

I/O |

USB signals for DSPORT1 |

29 |

PWREN4# |

O |

Power enable output for DSPORT4 |

|

6 |

DP1 |

I/O |

30 |

OVCUR3# |

I |

Over current indicator for DSPORT3 |

||

|

||||||||

7 |

AVDD |

- |

Analog power supply +3.3 V |

31 |

PWREN3# |

O |

Power enable output for DSPORT3 |

|

8 |

AGND |

- |

Analog ground |

32 |

GREEN3 |

O |

Green LED indicator for DSPORT3 |

|

9 |

DM2 |

I/O |

USB signals for DSPORT2 |

33 |

AMBER3 |

O |

Amber LED indicator for DSPORT3 |

|

10 |

DP2 |

I/O |

34 |

DVDD |

- |

Digital power supply +3.3 V |

||

|

||||||||

11 |

RREF |

I/O |

Reference resistor connection |

35 |

GREEN2/EE_DO |

O |

Green LED indicator for DSPORT2 |

|

12 |

AVDD |

- |

Analog power supply +3.3 V |

36 |

AMBER2/EE_DI |

O |

Amber LED indicator for DSPORT2 |

|

13 |

AGND |

- |

Analog ground |

37 |

PSELF |

I |

SELF/BUS power setting |

|

14 |

X1 |

I |

12MHz crystal clock input |

38 |

DVDD |

- |

Digital power supply +3.3 V |

|

15 |

X2 |

O |

12MHz crystal clock output |

39 |

PGANG |

I/O |

Individual/gang mode setting |

|

16 |

AVDD |

- |

Analog power supply +3.3 V |

40 |

OVCUR2# |

I |

Over current indicator for DSPORT2 |

|

17 |

DM3 |

I/O |

USB signals for DSPORT3 |

41 |

PWREN2# |

O |

Power enable output for DSPORT2 |

|

18 |

DP3 |

I/O |

42 |

OVCUR1# |

I |

Over current indicator for DSPORT1 |

||

|

||||||||

19 |

AVDD |

- |

Analog power supply +3.3 V |

43 |

PWREN1# |

O |

Power enable output for DSPORT1 |

|

20 |

AGND |

- |

Analog ground |

44 |

SEL27# |

- |

Digital power supply +3.3 V |

|

21 |

DM4 |

I/O |

USB signals for DSPORT4 |

45 |

GREEN1/EE_SK |

O |

Green LED indicator for DSPORT1 |

|

22 |

DP4 |

I/O |

46 |

AMBER1/EE_CS |

O |

Amber LED indicator for DSPORT1 |

||

|

||||||||

23 |

GREEN4 |

O |

Green LED indicator for DSPORT4 |

47 |

V5 |

- |

Power Supply +5V |

|

24 |

AMBER4 |

O |

Amber LED indicator for DSPORT4 |

48 |

DVDD |

- |

Digital power supply +3.3 V |

LTC3615EUF#TRPBF (YD559A00) DC-DC CONVERTER

LTC3615EUF#TRPBF (YD559A00) DC-DC CONVERTER

MAIN (MAINCOM): IC603

PIN |

NAME |

I/O |

|

FUNCTION |

PIN |

NAME |

I/O |

FUNCTION |

NO. |

|

NO. |

||||||

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

1 |

ITH1 |

O |

Error Amplifi er Compensation of Channel 1 |

14 |

RUN1 |

I |

Enable Pin for Channel 1. |

|

2 |

FB1 |

I |

Voltage Feedback Input Pin for Channel 1 |

15 |

RT/SYNC |

I |

This pin provides three modes of setting the |

|

3 |

MODE |

I |

Mode Selection. |

16 |

PGOOD2 |

|

switching |

|

4 |

PHASE |

I |

Phase Shift Selection. |

O |

Power Good Output Pin for Channel 2. |

|||

5 |

FB2 |

I |

Voltage Feedback Input Pin for Channel 2 |

17 |

SRLIM |

I |

Slew Rate Limit. |

|

6 |

ITH2 |

O |

Error Amplifi er Compensation of Channel 2 |

18 |

PGOOD1 |

O |

Power Good Output Pin for Channel 1. |

|

7 |

TRACK/SS2 |

I |

Internal, External Soft-Start,External |

19 |

SW1 |

O |

Channel 1 Switching Node. |

|

|

|

|

Reference Input for Channel 2. |

20 |

SW1 |

O |

Channel 1 Switching Node. |

|

8 |

SGND |

- |

Signal Ground. |

21 |

PVIN1 |

I |

Channel 1 Power Supply Inputs. |

|

9 |

PVIN2 |

I |

Channel 2 |

Power Supply Inputs. |

22 |

PVIN1 |

I |

Channel 1 Power Supply Inputs. |

10 |

PVIN2 |

I |

Channel 2 |

Power Supply Inputs. |

23 |

SVIN |

I |

Signal Input Supply. |

11 |

SW2 |

O |

Channel 2 |

Switching Node. |

24 |

TRACK/SS1 |

I |

Internal, External Soft-Start,External |

12 |

SW2 |

O |

Channel 2 |

Switching Node. |

|

|

|

Reference Input for Channel 1. |

13 |

RUN2 |

I |

Enable Pin for Channel 2. |

25 |

PGND |

- |

Power Ground |

|

|

|

|

|

|

|

|

|

|

TLC5941PWPR (YD685A00) LED DRIVER

TLC5941PWPR (YD685A00) LED DRIVER

PNFD8 (PNFDCOM): IC200

PNC (PNCOM): IC007, IC008

PIN |

NAME |

I/O |

FUNCTION |

PIN |

NAME |

I/O |

FUNCTION |

|

NO. |

NO. |

|||||||

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

1 |

GND |

- |

Ground |

15 |

OUT8 |

O |

Constant-current output |

|

2 |

BLANK |

I |

Blank all outputs. |

16 |

OUT9 |

O |

Constant-current output |

|

3 |

XLAT |

I |

Data latch. |

17 |

OUT10 |

O |

Constant-current output |

|

4 |

SCLK |

I |

Serial data shift clock |

18 |

OUT11 |

O |

Constant-current output |

|

5 |

SIN |

I |

Serial data input |

19 |

OUT12 |

O |

Constant-current output |

|

6 |

MODE |

I |

Input mode-change pin. |

20 |

OUT13 |

O |

Constant-current output |

|

7 |

OUT0 |

O |

Constant-current output |

21 |

OUT14 |

O |

Constant-current output |

|

8 |

OUT1 |

O |

Constant-current output |

22 |

OUT15 |

O |

Constant-current output |

|

9 |

OUT2 |

O |

Constant-current output |

23 |

XERR |

O |

Error output. |

|

10 |

OUT3 |

O |

Constant-current output |

24 |

SOUT |

O |

Serial data output |

|

11 |

OUT4 |

O |

Constant-current output |

25 |

GSCLK |

I |

Reference clock for grayscale PWM control |

|

12 |

OUT5 |

O |

Constant-current output |

26 |

TEST |

I |

Test pin: Connect to VCC |

|

13 |

OUT6 |

O |

Constant-current output |

27 |

IREF |

I |

Reference current terminal |

|

14 |

OUT7 |

O |

Constant-current output |

28 |

VCC |

I |

Power supply voltage. |

|

|

|

|

|

|

|

|

|

97

TF5/TF3/TF1

M36BFYFG-7PP4(DBB) (YG822A00) MICROCONTROLLER (MCU)

M36BFYFG-7PP4(DBB) (YG822A00) MICROCONTROLLER (MCU)

PNFD8 (PNFDCOM): IC002

PNC (PNCOM): |

IC003 |

PIN |

NAME |

I/O |

FUNCTION |

|

|

||||

NO. |

IC002 |

|||

|

|

|||

|

|

|

||

1 |

PI4 |

I/O |

Input/Output port |

|

|

AIN4 |

I |

Analog input |

|

2 |

PI5 |

I/O |

Input/Output port |

|

|

AIN5 |

I |

Analog input |

|

3 |

PI6 |

I/O |

Input/Output port |

|

|

AIN6 |

I |

Analog input |

|

4 |

PI7 |

I/O |

Input/Output port |

|

|

AIN7 |

I |

Analog input |

|

5 |

PJ0 |

I/O |

Input/Output port |

|

|

INT9 |

I |

External interrupt pin |

|

|

AIN8 |

I |

Analog input |

|

6 |

PJ1 |

I/O |

Input/Output port |

|

|

INTA |

I |

External interrupt pin |

|

|

AIN9 |

I |

Analog input |

|

7 |

PJ2 |

I/O |

Input/Output port |

|

|

INTB |

I |

External interrupt pin |

|

|

AIN10 |

I |

Analog input |

|

8 |

PJ3 |

I/O |

Input/Output port |

|

|

INTC |

I |

External interrupt pin |

|

|

DMAREQ |

I |

DMA request pin |

|

|

AIN11 |

I |

Analog input |

|

9 |

PJ4 |

I/O |

Input/Output port |

|

|

AIN12 |

I |

Analog input |

|

10 |

PJ5 |

I/O |

Input/Output port |

|

|

AIN13 |

I |

Analog input |

|

11 |

PJ6 |

I/O |

Input/Output port |

|

|

AIN14 |

I |

Analog input |

|

12 |

PJ7 |

I/O |

Input/Output port |

|

|

AIN15 |

I |

Analog input |

|

13 |

VREFL |

- |

Supplying the AD converter with a reference power supply. |

|

|

|

|

(note) VREFL must be connected to GND even if AD converter is not used. |

|

14 |

VREFH |

- |

Supplying the AD converter with a reference power supply. |

|

|

|

|

(note) VREFH must be connected to power supply even if AD converter is not used. |

|

15 |

FTEST3 |

- |

TEST pin |

|

|

|

|

(note) TEST pin must be left OPEN. |

|

16 |

DVSS |

- |

Ground |

|

17 |

PE0 |

I/O |

Input/Output port |

|

|

A16 |

O |

Address bus |

|

|

INT4 |

I |

External interrupt pin |

|

|

TB0IN |

I |

Inputting the timer B capture trigger |

|

18 |

PE1 |

I/O |

Input/Output port |

|

|

RXD0 |

I |

SIO receive pin |

|

|

A17 |

O |

Address bus |

|

|

INT5 |

I |

External interrupt pin |

|

|

TB1IN |

I |

Inputting the timer B capture trigger |

|

19 |

PE2 |

I/O |

Input/Output port |

|

|

TXD0 |

O |

SIO transmit pin |

|

|

A18 |

O |

Address bus |

|

|

TB1OUT |

O |

Timer B output |

|

20 |

PE3 |

I/O |

Input/Output port |

|

|

SCLK0 |

I/O |

SIO clock pin |

|

|

A19 |

O |

Address bus |

|

|

/CTS0 |

I |

Handshake pin |

|

|

TB0OUT |

O |

Timer B output pin |

|

21 |

DVDD3 |

- |

Power supply pin +3.3D |

|

22 |

PE4 |

I/O |

Input/Output port |

|

|

SCLK1 |

I/O |

SIO clock pin |

|

|

A20 |

O |

Address bus |

|

|

/CTS1 |

I |

Handshake pin |

|

|

TB2OUT |

O |

Timer B output pin |

|

23 |

PE5 |

I/O |

Input/Output port |

|

|

TXD1 |

O |

SIO transmit pin |

|

|

A21 |

O |

Address bus |

|

24 |

PE6 |

I/O |

Input/Output port |

|

|

RXD1 |

I |

SIO receive pin |

|

|

A22 |

O |

Address bus |

|

25 |

PE7 |

I/O |

Input/Output port |

|

|

A23 |

O |

Address bus |

|

|

INT6 |

I |

External interrupt pin |

|

|

TB2IN |

I |

Inputting the timer B capture trigger |

|

26 |

DVSS |

- |

Ground |

|

27 |

PF0 |

I/O |

Input/Output port |

|

|

AD0 |

I/O |

Address data bus pin |

|

|

/CTS4 |

I |

Handshake pin |

PIN |

NAME |

|

I/O |

|

|

|

|

||

NO. |

IC002 |

|

IC003 |

|

|

|

|||

|

|

|

||

1 |

FDPOS4 |

|

NC |

I |

2 |

FDPOS5 |

|

NC |

I |

3 |

FDPOS6 |

|

NC |

I |

4 |

FDPOS7 |

|

NC |

I |

5 |

FDB0 |

|

FDB0 |

I/O |

6 |

FDB1 |

|

ENC2 |

I/O |

7 |

FDB2 |

|

ENC3 |

I/O |

8 |

FDB3 |

|

NC |

I/O |

9 |

FDB4 |

|

NC |

I/O |

10 |

FDB5 |

|

NC |

I/O |

11 |

FDB6 |

|

NC |

I/O |

12 |

FDB7 |

|

NC |

I/O |

13 |

VREFL |

|

VREFL |

- |

14 |

VREFH |

|

VREFH |

- |

15 |

FTEST3 |

|

FTEST3 |

- |

16 |

DVSS |

|

DVSS |

- |

17 |

NC |

|

LCDVC |

|

18 |

RXD0 |

|

RXD0 |

I |

19 |

FDPWM1/TXD0 |

|

TXD0 |

O |

20 |

FDPWM0 |

|

FDPWM0 |

|

21 |

DVDD3 |

|

DVDD3 |

- |

22 |

FDPWM2 |

|

LCDEN3 |

O |

23 |

LSSEL0/PE5 |

|

LSSEL0 |

|

24 |

LSSEL1 |

|

LSSEL1 |

|

25 |

LSSEL2 |

|

LSSEL2 |

|

26 |

DVSS |

|

DVSS |

- |

27 |

FDA0 |

|

NC |

|

|

|

|

|

|

98

TF5/TF3/TF1

PIN |

NAME |

I/O |

FUNCTION |

|

|

||||

NO. |

IC002 |

|||

|

|

|||

|

|

|

||

28 |

PF1 |

I/O |

Input/Output port |

|

|

AD1 |

I/O |

Address data bus pin |

|

|

TXD4 |

O |

UART transmit pin |

|

|

IROUT4 |

O |

lrDA1.0 transmit pin |

|

29 |

PF2 |

I/O |

Input/Output port |

|

|

AD2 |

I/O |

Address data bus pin |

|

|

RXD4 |

I |

UART receive pin |

|

|

IRIN4 |

I |

lrDA1.0 receive pin |

|

30 |

PF3 |

I/O |

Input/Output port |

|

|

AD3 |

I/O |

Address data bus pin |

|

|

/RTS4 |

O |

UART Modem control (/RTS) |

|

31 |

DVDD3 |

- |

Power supply pin +3.3D |

|

32 |

PF4 |

I/O |

Input/Output port |

|

|

AD4 |

I/O |

Address data bus pin |

|

|

INT0 |

I |

External interrupt pin |

|

|

DCD4 |

I |

Modem status (DCD) |

|

33 |

PF5 |

I/O |

Input/Output port |

|

|

AD5 |

I/O |

Address data bus pin |

|

|

ENCZ0 |

I |

Z-phase input pin |

|

|

RIN4 |

I |

Modem status (RIN) |

|

|

SCK1 |

I/O |

SIO mode clock pin |

|

34 |

PF6 |

I/O |

Input/Output port |

|

|

AD6 |

I/O |

Address data bus pin |

|

|

ENCB0 |

I |

B-phase input pin |

|

|

DSR4 |

I |

Modem status (DSR) |

|

|

SI1/SCL1 |

I/O |

SIO mode receive pin, I2C mode clock pin |

|

35 |

PF7 |

I/O |

Input/Output port |

|

|

AD7 |

I/O |

Address data bus pin |

|

|

ENCA0 |

I |

A-phase input pin |

|

|

DTR4 |

O |

Modem control (DTR) |

|

|

SO1/SDA1 |

I/O |

SIO mode transmit pin, I2C mode transmit/receive pin |

|

36 |

PG0 |

I/O |

Input/Output port |

|

|

AD8 |

I/O |

Address data bus pin |

|

|

MT0IN |

I |

Multi-purpose timer (IGBT mode) input pin |

|

37 |

PG1 |

I/O |