Samsung M393B1K70DH0-YH9 User Manual

Rev. 1.2, Aug. 2011

M393B5773DH0

M393B5273DH0

M393B5270DH0

M393B1K70DH0

M393B1K73DH0

M393B2K70DM0

240pin Registered DIMM

based on 2Gb D-die |

1.35V |

|

78FBGA with Lead-Free & Halogen-Free (RoHS compliant)

datasheet

SAMSUNG ELECTRONICS RESERVES THE RIGHT TO CHANGE PRODUCTS, INFORMATION AND

SPECIFICATIONS WITHOUT NOTICE.

Products and specifications discussed herein are for reference purposes only. All information discussed herein is provided on an "AS IS" basis, without warranties of any kind.

This document and all information discussed herein remain the sole and exclusive property of Samsung Electronics. No license of any patent, copyright, mask work, trademark or any other intellectual property right is granted by one party to the other party under this document, by implication, estoppel or otherwise.

Samsung products are not intended for use in life support, critical care, medical, safety equipment, or similar applications where product failure could result in loss of life or personal or physical harm, or any military or defense application, or any governmental procurement to which special terms or provisions may apply.

For updates or additional information about Samsung products, contact your nearest Samsung office.

All brand names, trademarks and registered trademarks belong to their respective owners.

2011 Samsung Electronics Co., Ltd. All rights reserved.

- 1 -

Registered DIMM

datasheet

Rev. 1.2

DDR3L SDRAM

Revision History

Revision No. |

History |

Draft Date |

Remark |

Editor |

1.0 |

- First Release |

Sep. 2010 |

- |

S.H.Kim |

1.01 |

- Corrected typo. |

Dec. 2010 |

- |

S.H.Kim |

1.1 |

- Corrected typo. |

Feb. 2011 |

- |

J.Y.Lee |

1.11 |

- Corrected typo. |

May. 2011 |

- |

J.Y.Lee |

1.12 |

- Corrected typo. |

Jun. 2011 |

- |

J.Y.Lee |

1.13 |

- Corrected typo. |

Jul. 2011 |

- |

J.Y.Lee |

1.2 |

- Changed input/output capacitance for 1333/1600Mbps of 1.35V |

Aug. 2011 |

- |

J.Y.Lee |

|

- Changed module thickness with Heat Spreader. |

|

|

|

- 2 -

Registered DIMM

datasheet

Rev. 1.2

DDR3L SDRAM

Table Of Contents

240pin Registered DIMM based on 2Gb D-die

1. DDR3L Registered DIMM Ordering Information ........................................................................................................... |

5 |

||||

2. Key Features................................................................................................................................................................. |

5 |

||||

3. Address Configuration .................................................................................................................................................. |

5 |

||||

4. Registered DIMM Pin Configurations (Front side/Back side)........................................................................................ |

6 |

||||

5. Pin Description ............................................................................................................................................................. |

7 |

||||

6. ON DIMM Thermal Sensor ........................................................................................................................................... |

7 |

||||

7. Input/Output Functional Description.............................................................................................................................. |

8 |

||||

8. Pinout Comparison Based On Module Type................................................................................................................. |

9 |

||||

9. Registering Clock Driver Specification.......................................................................................................................... |

10 |

||||

9.1 Timing & Capacitance values .................................................................................................................................. |

10 |

||||

9.2 Clock driver Characteristics..................................................................................................................................... |

10 |

||||

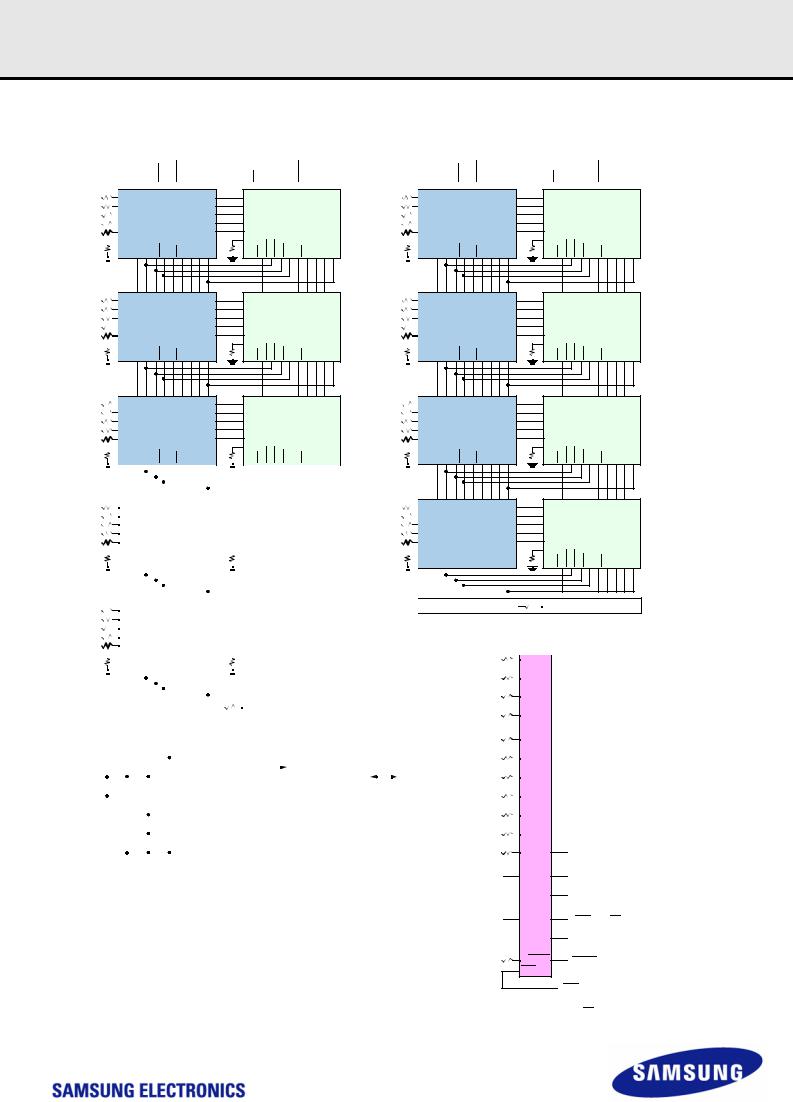

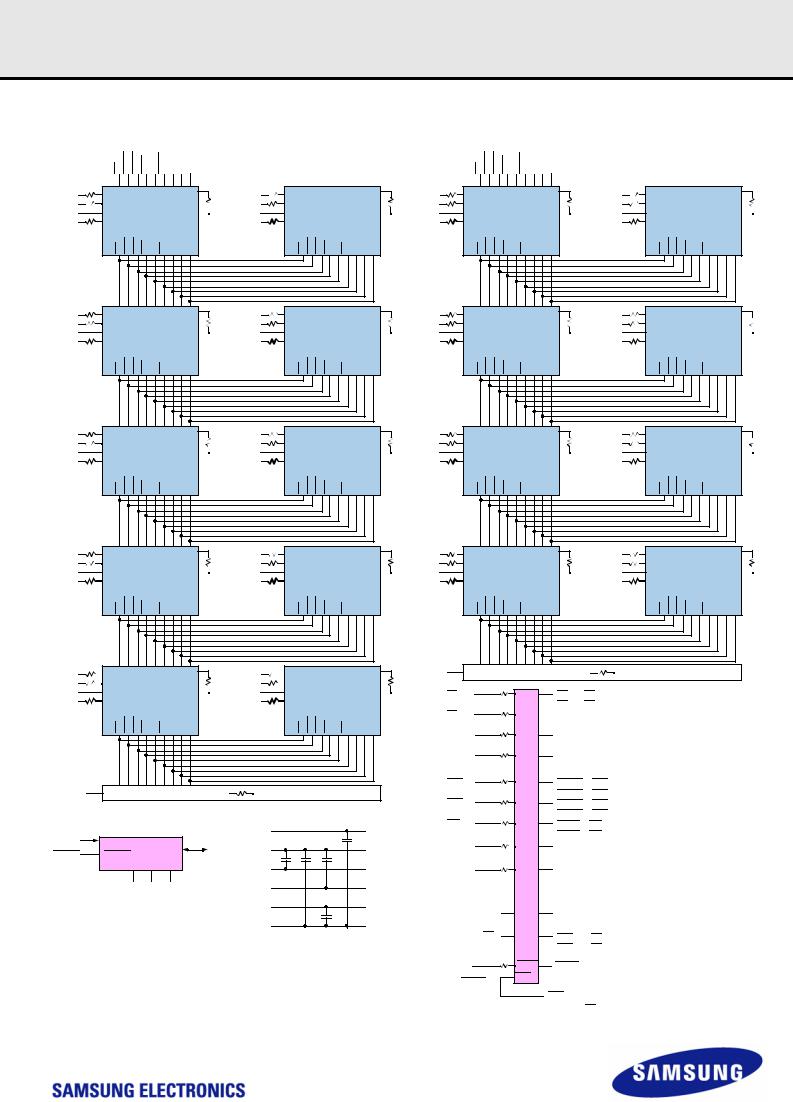

10. |

Function Block Diagram:............................................................................................................................................. |

11 |

|||

10.1 |

2GB, 256Mx72 Module (Populated as 1 rank of x8 DDR3 SDRAMs) ................................................................... |

11 |

|||

10.2 |

4GB, 512Mx72 Module (Populated as 2 ranks of x8 DDR3 SDRAMs) ................................................................. |

12 |

|||

10.3 |

4GB, 512Mx72 Module (Populated as 1 rank of x4 DDR3 SDRAMs) ................................................................... |

13 |

|||

10.4 |

8GB, 1Gx72 Module (Populated as 2 ranks of x4 DDR3 SDRAMs) ..................................................................... |

14 |

|||

10.5 |

8GB, 1Gx72 Module (Populated as 4 ranks of x8 DDR3 SDRAMs) .................................................................... |

16 |

|||

10.6 |

16GB, 2Gx72 Module (Populated as 4 ranks of x4 DDR3 SDRAMs) ................................................................... |

17 |

|||

11. |

Absolute Maximum Ratings ........................................................................................................................................ |

22 |

|||

11.1 |

Absolute Maximum DC Ratings............................................................................................................................. |

22 |

|||

11.2 |

DRAM Component Operating Temperature Range .............................................................................................. |

22 |

|||

12. |

AC & DC Operating Conditions................................................................................................................................... |

22 |

|||

12.1 |

Recommended DC Operating Conditions ............................................................................................................. |

22 |

|||

13. |

AC & DC Input Measurement Levels .......................................................................................................................... |

23 |

|||

13.1 |

AC & DC Logic Input Levels for Single-ended Signals.......................................................................................... |

23 |

|||

13.2 |

VREF Tolerances.................................................................................................................................................... |

25 |

|||

13.3 |

AC and DC Logic Input Levels for Differential Signals .......................................................................................... |

26 |

|||

|

13.3.1. Differential Signals Definition ......................................................................................................................... |

26 |

|||

|

13.3.2. Differential Swing Requirement for Clock (CK - |

CK) |

.............................................and Strobe (DQS - DQS) |

26 |

|

|

13.3.3. Single-ended Requirements for Differential Signals ...................................................................................... |

28 |

|||

|

13.3.4. Differential Input Cross Point Voltage ............................................................................................................ |

29 |

|||

13.4 |

Slew Rate Definition for Single Ended Input Signals............................................................................................. |

30 |

|||

13.5 |

Slew rate definition for Differential Input Signals ................................................................................................... |

30 |

|||

14. |

AC & DC Output Measurement Levels ....................................................................................................................... |

30 |

|||

14.1 |

Single Ended AC and DC Output Levels............................................................................................................... |

30 |

|||

14.2 |

Differential AC and DC Output Levels ................................................................................................................... |

30 |

|||

14.3 |

Single-ended Output Slew Rate ............................................................................................................................ |

31 |

|||

14.4 |

Differential Output Slew Rate ................................................................................................................................ |

32 |

|||

15. |

IDD specification definition.......................................................................................................................................... |

33 |

|||

16. |

IDD SPEC Table ......................................................................................................................................................... |

35 |

|||

17. |

Input/Output Capacitance ........................................................................................................................................... |

38 |

|||

18. |

Electrical Characteristics and AC timing ..................................................................................................................... |

39 |

|||

18.1 |

Refresh Parameters by Device Density................................................................................................................. |

39 |

|||

18.2 |

Speed Bins and CL, tRCD, tRP, tRC and tRAS for Corresponding Bin ................................................................ |

39 |

|||

18.3 |

Speed Bins and CL, tRCD, tRP, tRC and tRAS for Corresponding Bin ................................................................ |

39 |

|||

|

18.3.1. Speed Bin Table Notes .................................................................................................................................. |

42 |

|||

19. |

Timing Parameters by Speed Grade .......................................................................................................................... |

43 |

|||

19.1 |

Jitter Notes ............................................................................................................................................................ |

46 |

|||

19.2 |

Timing Parameter Notes........................................................................................................................................ |

47 |

|||

20. |

Physical Dimensions................................................................................................................................................... |

48 |

|||

20.1 |

256Mbx8 based 256Mx72 Module (1 Rank) - M393B5773DH0............................................................................ |

48 |

|||

|

20.1.1. x72 DIMM, populated as one physical rank of x8 DDR3 SDRAMs................................................................ |

48 |

|||

- 3 -

Registered DIMM

datasheet

Rev. 1.2

DDR3L SDRAM

20.2 |

256Mbx8 based 512Mx72 Module (2 Ranks) - M393B5273DH0 .......................................................................... |

49 |

|

20.2.1. x72 DIMM, populated as two physical ranks of x8 DDR3 SDRAMs .............................................................. |

49 |

||

20.3 |

512Mbx4 based 512Mx72 Module (1 Rank) - M393B5270DH0............................................................................ |

50 |

|

20.3.1. x72 |

DIMM, populated as one physical rank of x4 DDR3 SDRAMs................................................................ |

50 |

|

20.4 |

512Mbx4 based 1Gx72 Module (2 Ranks) - M393B1K70DH0.............................................................................. |

51 |

|

20.4.1. x72 |

DIMM, populated as two physical ranks of x4 DDR3 SDRAMs .............................................................. |

51 |

|

20.5 |

256Mbx8 based 1Gx72 Module (4 Ranks) - M393B1K73DH0.............................................................................. |

52 |

|

20.5.1. x72 |

DIMM, populated as four physical ranks of x8 DDR3 SDRAMs.............................................................. |

52 |

|

20.6 |

1Gbx4(DDP) based 2Gx72 Module (4 Ranks) - M393B2K70DM0........................................................................ |

53 |

|

20.6.1. x72 |

DIMM, populated as four physical ranks of x4 DDR3 SDRAMs.............................................................. |

53 |

|

20.6.2. Heat Spreader Design Guide ......................................................................................................................... |

54 |

||

- 4 -

Registered DIMM

datasheet

Rev. 1.2

DDR3L SDRAM

1. DDR3L Registered DIMM Ordering Information

Part Number2 |

Density |

Organization |

Component Composition |

Number of |

Height |

|

Rank |

||||||

|

|

|

|

|

||

M393B5773DH0-YF8/H9/K0 |

2GB |

256Mx72 |

256Mx8(K4B2G0846D-HY##)*9 |

1 |

30mm |

|

|

|

|

|

|

|

|

M393B5273DH0-YF8/H9/K0 |

4GB |

512Mx72 |

256Mx8(K4B2G0846D-HY##)*18 |

2 |

30mm |

|

|

|

|

|

|

|

|

M393B5270DH0-YF8/H9/K0 |

4GB |

512Mx72 |

512Mx4(K4B2G0446D-HY##)*18 |

1 |

30mm |

|

|

|

|

|

|

|

|

M393B1K70DH0-YF8/H9/K0 |

8GB |

1Gx72 |

512Mx4(K4B2G0446D-HY##)*36 |

2 |

30mm |

|

|

|

|

|

|

|

|

M393B1K73DH0-YF8/H9 |

8GB |

1Gx72 |

256Mx8(K4B2G0846D-HY##)*36 |

4 |

30mm |

|

|

|

|

|

|

|

|

M393B2K70DM0-YF8/H9 |

16GB |

2Gx72 |

DDP 1Gx4(K4B4G0446D-MY##)*36 |

4 |

30mm |

|

|

|

|

|

|

|

NOTE :

1."##" - F8/H9/K0

2.F8(1066Mbps 7-7-7) / H9(1333Mbps 9-9-9) / K0(1600Mbps 11-11-11)

-DDR3-1600(11-11-11) is backward compatible to DDR3-1333(9-9-9), DDR3-1066(7-7-7)

-DDR3-1333(9-9-9) is backward compatible to DDR3-1066(7-7-7)

2. Key Features

Speed |

DDR3-800 |

DDR3-1066 |

DDR3-1333 |

DDR3-1600 |

Unit |

|

6-6-6 |

7-7-7 |

9-9-9 |

11-11-11 |

|||

|

|

|||||

tCK(min) |

2.5 |

1.875 |

1.5 |

1.25 |

ns |

|

|

|

|

|

|

|

|

CAS Latency |

6 |

7 |

9 |

11 |

nCK |

|

|

|

|

|

|

|

|

tRCD(min) |

15 |

13.125 |

13.5 |

13.75 |

ns |

|

|

|

|

|

|

|

|

tRP(min) |

15 |

13.125 |

13.5 |

13.75 |

ns |

|

|

|

|

|

|

|

|

tRAS(min) |

37.5 |

37.5 |

36 |

35 |

ns |

|

|

|

|

|

|

|

|

tRC(min) |

52.5 |

50.625 |

49.5 |

48.75 |

ns |

|

|

|

|

|

|

|

•JEDEC standard 1.35V(1.28V~1.45V) & 1.5V(1.425V~1.575V) Power Supply

•VDDQ = 1.35V(1.28V~1.45V) & 1.5V(1.425V~1.575V)

•400MHz fCK for 800Mb/sec/pin, 533MHz fCK for 1066Mb/sec/pin, 667MHz fCK for 1333Mb/sec/pin, 800MHz fCK for 1600Mb/sec/pin

•8 independent internal bank

•Programmable CAS Latency: 6,7,8,9,10,11

•Programmable Additive Latency(Posted CAS) : 0, CL - 2, or CL - 1 clock

•Programmable CAS Write Latency(CWL) = 5(DDR3-800), 6(DDR3-1066), 7(DDR3-1333) and 8(DDR3-1600)

•8-bit pre-fetch

•Burst Length: 8 (Interleave without any limit, sequential with starting address “000” only), 4 with tCCD = 4 which does not allow seamless read or write [either On the fly using A12 or MRS]

•Bi-directional Differential Data Strobe

•Internal(self) calibration : Internal self calibration through ZQ pin (RZQ : 240 ohm ± 1%)

•On Die Termination using ODT pin

•Average Refresh Period 7.8us at lower then TCASE 85°C, 3.9us at 85°C < TCASE ≤ 95°C

•Asynchronous Reset

3. Address Configuration

Organization |

Row Address |

Column Address |

Bank Address |

Auto Precharge |

512Mx4(2Gb) based Module |

A0-A14 |

A0-A9, A11 |

BA0-BA2 |

A10/AP |

|

|

|

|

|

256Mx8(2Gb) based Module |

A0-A14 |

A0-A9 |

BA0-BA2 |

A10/AP |

|

|

|

|

|

1Gx4(4Gb DDP) based Module |

A0-A14 |

A0-A9, A11 |

BA0-BA2 |

A10/AP |

|

|

|

|

|

- 5 -

Registered DIMM

datasheet

Rev. 1.2

DDR3L SDRAM

4. Registered DIMM Pin Configurations (Front side/Back side)

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Pin |

Front |

Pin |

Back |

Pin |

|

|

Front |

|

Pin |

|

|

|

Back |

Pin |

Front |

Pin |

Back |

|||||||||||||||||||

|

VREFDQ |

|

VSS |

|

|

|

|

|

|

|

|

|

|

|

NC,DQS17 |

82 |

|

DQ33 |

202 |

VSS |

||||||||||||||||

1 |

121 |

42 |

|

|

DQS8 |

|

162 |

|

||||||||||||||||||||||||||||

|

|

|

|

,TDQS17 |

|

|||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

2 |

|

VSS |

122 |

DQ4 |

43 |

|

|

DQS8 |

|

163 |

|

|

|

|

VSS |

83 |

|

VSS |

203 |

DM4,DQS13 |

||||||||||||||||

|

|

|

|

|

|

|

|

|

,TDQS13 |

|||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VSS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

NC,DQS13 |

||||

3 |

|

DQ0 |

123 |

DQ5 |

44 |

|

|

|

|

164 |

|

CB6,NC |

84 |

DQS4 |

204 |

|||||||||||||||||||||

|

|

|

|

|

|

,TDQS13 |

||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4 |

|

DQ1 |

124 |

VSS |

45 |

|

CB2,NC |

|

165 |

|

CB7,NC |

85 |

DQS4 |

205 |

VSS |

|||||||||||||||||||||

5 |

|

VSS |

125 |

DM0,DQS9 |

46 |

|

CB3,NC |

|

166 |

|

|

|

|

VSS |

86 |

|

VSS |

206 |

DQ38 |

|||||||||||||||||

|

,TDQS9 |

|

|

|

|

|

|

|

||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

NC,DQS9 |

47 |

|

|

|

VSS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

6 |

|

DQS0 |

126 |

|

|

|

|

167 |

|

NC(TEST) |

87 |

|

DQ34 |

207 |

DQ39 |

|||||||||||||||||||||

|

,TDQS9 |

|

|

|

|

|

|

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

7 |

|

DQS0 |

127 |

VSS |

48 |

|

VTT, NC |

|

168 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

88 |

|

DQ35 |

208 |

VSS |

||||||||

|

|

|

RESET |

|

||||||||||||||||||||||||||||||||

8 |

|

VSS |

128 |

DQ6 |

|

|

|

|

|

|

|

|

|

KEY |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

89 |

|

VSS |

209 |

DQ44 |

|||

9 |

|

DQ2 |

129 |

DQ7 |

49 |

|

VTT, NC |

|

169 |

|

CKE1, NC |

90 |

|

DQ40 |

210 |

DQ45 |

||||||||||||||||||||

10 |

|

DQ3 |

130 |

VSS |

50 |

|

|

CKE0 |

|

170 |

|

|

|

|

VDD |

91 |

|

DQ41 |

211 |

VSS |

||||||||||||||||

11 |

|

VSS |

131 |

DQ12 |

51 |

|

|

|

VDD |

|

171 |

|

|

|

|

|

NC |

92 |

|

VSS |

212 |

DM5,DQS14 |

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

,TDQS14 |

|||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

NC,DQS14 |

12 |

|

DQ8 |

132 |

DQ13 |

52 |

|

|

|

BA2 |

|

172 |

|

|

|

|

A14 |

93 |

DQS5 |

213 |

|||||||||||||||||

|

|

|

|

|

|

|

|

|

,TDQS14 |

|||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

13 |

|

DQ9 |

133 |

VSS |

53 |

|

|

|

|

|

|

|

|

|

173 |

|

|

|

|

VDD |

94 |

|

DQS5 |

214 |

VSS |

|||||||||||

|

Err_Out/NC |

|

|

|

||||||||||||||||||||||||||||||||

|

|

VSS |

|

DM1,DQS10 |

|

|

|

|

VDD |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VSS |

|

|

||||||

14 |

|

134 |

54 |

|

|

|

|

174 |

|

A12/BC |

95 |

|

215 |

DQ46 |

||||||||||||||||||||||

|

,TDQS10 |

|

|

|

|

|

|

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

NC,DQS10 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

15 |

|

DQS1 |

135 |

55 |

|

|

|

A11 |

|

175 |

|

|

|

|

|

A9 |

96 |

|

DQ42 |

216 |

DQ47 |

|||||||||||||||

|

,TDQS10 |

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

16 |

|

DQS1 |

136 |

VSS |

56 |

|

|

|

|

A7 |

|

176 |

|

|

|

|

VDD |

97 |

|

DQ43 |

217 |

VSS |

||||||||||||||

17 |

|

VSS |

137 |

DQ14 |

57 |

|

|

|

VDD |

|

177 |

|

|

|

|

|

|

A8 |

98 |

|

VSS |

218 |

DQ52 |

|||||||||||||

18 |

|

DQ10 |

138 |

DQ15 |

58 |

|

|

|

|

A5 |

|

178 |

|

|

|

|

|

A6 |

99 |

|

DQ48 |

219 |

DQ53 |

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

19 |

|

DQ11 |

139 |

VSS |

59 |

|

|

|

|

A4 |

|

179 |

|

|

|

|

VDD |

100 |

|

DQ49 |

220 |

VSS |

||||||||||||||

20 |

|

VSS |

140 |

DQ20 |

60 |

|

|

|

VDD |

|

180 |

|

|

|

|

|

|

A3 |

101 |

|

VSS |

221 |

DM6,DQS15 |

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

,TDQS15 |

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

NC,DQS15 |

21 |

|

DQ16 |

141 |

DQ21 |

61 |

|

|

|

|

A2 |

|

181 |

|

|

|

|

|

A1 |

102 |

DQS6 |

222 |

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

,TDQS15 |

|||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

22 |

|

DQ17 |

142 |

VSS |

62 |

|

|

|

VDD |

|

182 |

|

|

|

|

VDD |

103 |

DQS6 |

223 |

VSS |

||||||||||||||||

23 |

|

VSS |

143 |

DM2,DQS11 |

63 |

|

NC, CK1 |

|

183 |

|

|

|

|

VDD |

104 |

|

VSS |

224 |

DQ54 |

|||||||||||||||||

|

,TDQS11 |

|

|

|

|

|

|

|

||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

NC,DQS11 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

24 |

|

DQS2 |

144 |

64 |

|

NC, CK1 |

|

184 |

|

|

|

|

CK0 |

105 |

|

DQ50 |

225 |

DQ55 |

||||||||||||||||||

|

,TDQS11 |

|

|

|

|

|

|

|

||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

25 |

|

DQS2 |

145 |

VSS |

65 |

|

|

|

VDD |

|

185 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

106 |

|

DQ51 |

226 |

VSS |

||||||

|

|

|

|

|

|

CK0 |

|

|||||||||||||||||||||||||||||

26 |

|

VSS |

146 |

DQ22 |

66 |

|

|

|

VDD |

|

186 |

|

|

|

|

VDD |

107 |

|

VSS |

227 |

DQ60 |

|||||||||||||||

27 |

|

DQ18 |

147 |

DQ23 |

67 |

|

VREFCA |

|

187 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

108 |

|

DQ56 |

228 |

DQ61 |

||||||||

|

|

EVENT,NC |

|

|||||||||||||||||||||||||||||||||

28 |

|

DQ19 |

148 |

VSS |

68 |

|

NC/Par_In |

|

188 |

|

|

|

|

|

|

A0 |

109 |

|

DQ57 |

229 |

VSS |

|||||||||||||||

29 |

|

VSS |

149 |

DQ28 |

69 |

|

|

|

VDD |

|

189 |

|

|

|

|

VDD |

110 |

|

VSS |

230 |

DM7/DQS16 |

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

TDQS16 |

||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DM7,DQS16 |

30 |

|

DQ24 |

150 |

DQ29 |

70 |

|

A10/AP |

|

190 |

|

|

|

|

BA1 |

111 |

DQS7 |

231 |

|||||||||||||||||||

|

|

|

|

|

|

|

,TDQS16 |

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

31 |

|

DQ25 |

151 |

VSS |

71 |

|

|

|

BA0 |

|

191 |

|

|

|

|

VDD |

112 |

|

DQS7 |

232 |

VSS |

|||||||||||||||

|

|

VSS |

|

DM3,DQS12 |

|

|

|

|

VDD |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VSS |

|

|

||||||

32 |

|

152 |

72 |

|

|

|

|

192 |

|

|

|

|

RAS |

113 |

|

233 |

DQ62 |

|||||||||||||||||||

|

,TDQS12 |

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

NC,DQS12 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

33 |

|

DQS3 |

153 |

73 |

|

|

|

|

WE |

|

193 |

|

|

|

|

|

|

S0 |

114 |

|

DQ58 |

234 |

DQ63 |

|||||||||||||

|

,TDQS12 |

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

34 |

|

DQS3 |

154 |

VSS |

74 |

|

|

|

|

|

|

|

|

194 |

|

|

|

|

VDD |

115 |

|

DQ59 |

235 |

VSS |

||||||||||||

|

|

|

CAS |

|

|

|

|

|

||||||||||||||||||||||||||||

35 |

|

VSS |

155 |

DQ30 |

75 |

|

|

|

VDD |

|

195 |

|

|

|

ODT0 |

116 |

|

VSS |

236 |

VDDSPD |

||||||||||||||||

36 |

|

DQ26 |

156 |

DQ31 |

76 |

|

|

|

|

S1,NC |

|

196 |

|

|

|

|

A13 |

117 |

|

SA0 |

237 |

SA1 |

||||||||||||||

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

37 |

|

DQ27 |

157 |

VSS |

77 |

|

ODT1,NC |

|

197 |

|

|

|

|

VDD |

118 |

|

SCL |

238 |

SDA |

|||||||||||||||||

38 |

|

VSS |

158 |

CB4,NC |

78 |

|

|

|

VDD |

|

198 |

|

|

|

|

|

S3,NC |

119 |

|

SA2 |

239 |

VSS |

||||||||||||||

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||

39 |

CB0,NC |

159 |

CB5,NC |

79 |

|

|

|

|

S2,NC |

|

199 |

|

|

|

|

VSS |

120 |

|

VTT |

240 |

VTT |

|||||||||||||||

|

|

|

|

|

|

|||||||||||||||||||||||||||||||

40 |

CB1,NC |

160 |

VSS |

80 |

|

|

|

VSS |

|

200 |

|

|

|

DQ36 |

|

|

|

|

|

|

||||||||||||||||

41 |

|

VSS |

161 |

DM8,DQS17 |

81 |

|

|

DQ32 |

|

201 |

|

|

|

DQ37 |

|

|

|

|

|

|

||||||||||||||||

|

TDQS17,NC |

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

NOTE : NC = No internal Connection

SAMSUNG ELECTRONICS CO., Ltd. reserves the right to change products and specifications without notice.

- 6 -

Registered DIMM

datasheet

Rev. 1.2

DDR3L SDRAM

5. Pin Description

Pin Name |

Description |

Number |

|

Pin Name |

Description |

Number |

|||||||||||||||

|

|

|

CK0 |

Clock Input, positive line |

1 |

|

|

ODT[1:0] |

On Die Termination Inputs |

2 |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

Clock Input, negative line |

1 |

|

|

DQ[63:0] |

Data Input/Output |

64 |

||||

|

|

|

CK0 |

||||||||||||||||||

|

|

|

|

|

|

|

|

||||||||||||||

CKE[1:0] |

Clock Enables |

2 |

|

|

CB[7:0] |

Data check bits Input/Output |

8 |

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

Row Address Strobe |

1 |

|

DQS[8:0] |

Data strobes |

9 |

|||||

|

|

|

RAS |

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

Column Address Strobe |

1 |

|

|

|

|

|

|

|

Data strobes, negative line |

9 |

|

|

|

CAS |

DQS[8:0] |

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DM[8:0]/ |

Data Masks/ Data strobes, |

9 |

||||

|

|

|

|

WE |

Write Enable |

1 |

|

DQS[17:9] |

|||||||||||||

|

|

|

|

|

Termination data strobes |

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

TDQS[17:9] |

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

[17:9] |

Data strobes, negative line, Termination data |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DQS |

|

||||||

|

|

S[3:0] |

Chip Selects |

4 |

9 |

||||||||||||||||

|

|

TDQS[17:9] |

strobes |

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

A[9:0],A11, |

Address Inputs |

2\14 |

|

|

|

RFU |

Reserved for Future Use |

2 |

|||||||||||||

A[15:13] |

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Reserved for optional hardware temperature |

|

|

A10/AP |

Address Input/Autoprecharge |

1 |

|

|

|

EVENT |

1 |

|||||||||||||

|

|

|

|

sensing |

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Memory bus test toll (Not Connected and Not |

1 |

|

A12/BC |

Address Input/Burst chop |

1 |

|

|

|

TEST |

||||||||||||||

|

|

|

|

Usable on DIMMs) |

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

BA[2:0] |

SDRAM Bank Addresses |

3 |

|

|

|

|

|

|

|

Register and SDRAM control pin |

1 |

|||||||||

|

|

RESET |

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

SCL |

Serial Presence Detect (SPD) Clock Input |

1 |

|

|

|

VDD |

Power Supply |

22 |

||||||||||

|

|

|

SDA |

SPD Data Input/Output |

1 |

|

|

|

VSS |

Ground |

59 |

||||||||||

|

SA[2:0] |

SPD Address Inputs |

3 |

|

|

VREFDQ |

Reference Voltage for DQ |

1 |

|||||||||||||

|

Par_In |

Parity bit for the Address and Control bus |

1 |

|

|

VREFCA |

Reference Voltage for CA |

1 |

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

Parity error found on the Address and Control |

1 |

|

|

|

VTT |

Termination Voltage |

4 |

|||

|

Err_Out |

|

|

|

|||||||||||||||||

|

bus |

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VDDSPD |

SPD Power |

1 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Total |

240 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

NOTE :

*The VDD and VDDQ pins are tied common to a single power-plane on these designs.

6. ON DIMM Thermal Sensor

SCL |

|

|

|

SDA |

EVENT

WP/EVENT

WP/EVENT

R1 |

|

SA0 |

SA1 |

SA2 |

||

0 Ω |

|

|||||

|

R2 |

|

|

|

|

|

|

0 Ω SA0 |

|

|

|

|

|

|

SA1 |

SA2 |

||||

|

||||||

|

|

|

|

|

|

|

NOTE : 1. All Samsung RDIMM support Thermal sensor on DIMM

2.When the SPD and the thermal sensor are placed on the module, R1 is placed but R2 is not. When only the SPD is placed on the module, R2 is placed but R1 is not.

[ Table 1 ] Temperature Sensor Characteristics

Grade |

Range |

Temperature Sensor Accuracy |

Units |

NOTE |

|||

Min. |

Typ. |

Max. |

|||||

|

|

|

|

||||

|

75 < Ta < 95 |

- |

+/- 0.5 |

+/- 1.0 |

|

- |

|

|

|

|

|

|

|

|

|

B |

40 < Ta < 125 |

- |

+/- 1.0 |

+/- 2.0 |

°C |

- |

|

|

|

|

|

|

|

|

|

|

-20 < Ta < 125 |

- |

+/- 2.0 |

+/- 3.0 |

|

- |

|

|

|

|

|

|

|

|

|

|

Resolution |

|

0.25 |

|

°C /LSB |

- |

|

|

|

|

|

|

|

|

|

|

|

- 7 - |

|

|

|

|

|

Registered DIMM

datasheet

Rev. 1.2

DDR3L SDRAM

7. Input/Output Functional Description

|

|

Symbol |

Type |

Polarity |

|

|

|

|

|

|

|

|

|

Function |

||||||||||||||||||||||||||||||

|

|

|

|

|

|

CK0 |

Input |

Positive |

Positive line of the differential pair of system clock inputs that drives input to the on-DIMM Clock Driver. |

|||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

Edge |

||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Input |

Negative |

Negative line of the differential pair of system clock inputs that drives the input to the on-DIMM Clock Driver. |

||||||||||||||||||||||||||

|

|

|

|

|

|

CK0 |

||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Edge |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CKE HIGH activates, and CKE LOW deactivates internal clock signals, and device input buffers |

||||||||||||||||||||||||||

|

|

CKE[1:0] |

Input |

Active High |

and output drivers of the SDRAMs. Taking CKE LOW provides PRECHARGE POWER-DOWN |

|||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

and SELF REFRESH operation (all banks idle), or ACTIVE POWER DOWN (row ACTIVE in any bank) |

||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Enables the associated SDRAM command decoder when low and disables decoder when high. |

||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

When decoder is disabled, new commands are ignored and previous operations continue. |

||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

These input signals also disable all outputs (except CKE and ODT) of the register(s) on the DIMM when both |

||||||||||||||||||||||||||

|

|

|

|

S[3:0] |

Input |

Active Low |

||||||||||||||||||||||||||||||||||||||

|

|

|

|

inputs are high. When both S[1:0] are high, all register outputs (except CKE, ODT and Chip select) remain in |

||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

the previous state. For modules supporting 4 ranks, S[3:2] operate similarly to S[1:0] for a second set of reg- |

||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ister outputs. |

||||||||||||||||||||||||||

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||

|

|

ODT[1:0] |

Input |

Active High |

On-Die Termination control signals |

|||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Input |

Active Low |

When sampled at the positive rising edge of the clock, |

CAS, |

|

RAS, |

and |

WE |

define the operation to be exe- |

|||||||||||||||||||||

|

RAS, |

CAS, |

WE |

|||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

cuted by the SDRAM. |

||||||||||||||||||||||||||

|

|

|

VREFDQ |

Supply |

|

Reference voltage for DQ0-DQ63 and CB0-CB7 |

||||||||||||||||||||||||||||||||||||||

|

|

|

VREFCA |

Supply |

|

Reference voltage for A0-A15, BA0-BA2, |

|

|

|

|

|

|

|

|

|

|

|

|

|

CKE0, CKE1, Par_In, ODT0 and ODT1. |

||||||||||||||||||||||||

|

|

RAS, |

CAS, |

WE, |

S0, |

S1, |

||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Selects which SDRAM bank of eight is activated. |

||||||||||||||||||||||||||

|

|

|

BA[2:0] |

Input |

|

BA0 - BA2 define to which bank an Active, Read, Write or Precharge command is being applied. Bank |

||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

address also determines mode register is to be accessed during an MRS cycle. |

||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Provided the row address for Active commands and the column address and Auto Precharge bit for Read/ |

||||||||||||||||||||||||||

|

|

A[15:13, |

|

|

Write commands to select one location out of the memory array in the respective bank. A10 is sampled dur- |

|||||||||||||||||||||||||||||||||||||||

|

|

|

|

ing a Precharge command to determine whether the Precharge applies to one bank (A10 LOW) or all banks |

||||||||||||||||||||||||||||||||||||||||

|

|

12/BC,11, |

Input |

|

||||||||||||||||||||||||||||||||||||||||

|

|

|

(A10 HIGH). If only one bank is to be precharged, the bank is selected by BA. A12 is also utilized for BL 4/8 |

|||||||||||||||||||||||||||||||||||||||||

|

|

10/AP,9:0] |

|

|

||||||||||||||||||||||||||||||||||||||||

|

|

|

|

identification for "BL on the fly" during CAS command. The address inputs also provide the op-code during |

||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Mode Register Set commands. |

||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

DQ[63:0], |

I/O |

|

Data and Check Bit Input/Output pins |

|||||||||||||||||||||||||||||||||||||||

|

|

|

CB[7:0] |

|

||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Active High Masks write data when high, issued concurrently with input data. |

||||||||||||||||||||||||||

|

|

|

DM[8:0] |

|

|

VDD, VSS Supply Power and ground for the DDR SDRAM input buffers and core logic. |

||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VTT Supply Termination Voltage for Address/Command/Control/Clock nets. |

||||||||||||||||||||||||||

|

|

DQS[17:0] |

I/O |

|

Positive Edge Positive line of the differential data strobe for input and output data. |

|||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||

|

|

DQS[17:0] |

I/O |

|

Negative Edge Negative line of the differential data strobe for input and output data. |

|||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TDQS/TDQS |

is applicable for X8 DRAMs only. When enabled via Mode Register A11=1 in MR1, DRAM will |

|||||||||||||||||||||||||

|

TDQS[17:9], |

OUT |

|

enable the same termination resistance function on TDQS/TDQS that is applied to DQS/DQS. When dis- |

||||||||||||||||||||||||||||||||||||||||

|

TDQS[17:9] |

|

abled via mode register A11=0 in MR1, DM/TDQS will provide the data mask function and TDQS is not used. |

|||||||||||||||||||||||||||||||||||||||||

|

|

|

||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

X4/X16 DRAMs must disable the TDQS function via mode register A11=0 in MR1 |

||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||

|

|

|

SA[2:0] |

IN |

|

These signals are tied at the system planar to either VSS or VDDSPD to configure the serial SPD EEPROM |

||||||||||||||||||||||||||||||||||||||

|

|

|

|

address range. |

||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||

|

|

|

|

|

SDA |

I/O |

|

This bidirectional pin is used to transfer data into or out of the SPD EEPROM. A resistor must be |

||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

connected from the SDA bus line to VDDSPD on the system planar to act as a pull-up. |

||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||

|

|

|

|

|

|

SCL |

IN |

|

This signal is used to clock data into and out of the SPD EEPROM. A resistor may be connected |

|||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

from the SCL bus time to VDDSPD on the system planar to act as a pull-up. |

|||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

OUT |

|

This signal indicates that a thermal event has been detected in the thermal sensing device.The system |

||||||||||||||||||||||||||

|

|

|

EVENT |

(open |

Active Low |

|||||||||||||||||||||||||||||||||||||||

|

|

|

should guarantee the electrical level requirement is met for the EVENT pin on TS/SPD part. |

|||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

drain) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VDDSPD |

Supply |

|

Serial EEPROM positive power supply wired to a separate power pin at the connector which supports from |

||||||||||||||||||||||||||||||||||||||

|

|

|

|

3.0 Volt to 3.6 Volt (nominal 3.3V) operation. |

||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

The |

RESET |

pin is connected to the |

RESET |

pin on the register and to the |

RESET |

pin on the DRAM. When |

||||||||||||||||||||

|

|

|

RESET |

|

|

IN |

|

low, all register outputs will be driven low and the Clock Driver clocks to the DRAMs and register(s) will be set |

||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

to low level (the Clock Driver will remain synchronized with the input clock) |

||||||||||||||||||||||||||

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||

|

|

|

Par_In |

IN |

|

Parity bit for the Address and Control bus. ("1" : Odd, "0" : Even) |

||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

OUT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Parity error detected on the Address and Control bus. A resistor may be connected from Err_Out |

|||||||||||||||||||||||||||

|

|

|

Err_Out |

(open |

|

|||||||||||||||||||||||||||||||||||||||

|

|

|

|

bus line to VDD on the system planar to act as a pull up. |

||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

drain) |

|

|||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||

|

|

|

|

TEST |

|

|

Used by memory bus analysis tools (unused (NC) on memory DIMMs) |

|||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

- 8 -

Registered DIMM

datasheet

Rev. 1.2

DDR3L SDRAM

8. Pinout Comparison Based On Module Type

|

|

|

|

|

|

|

|

|

|

|

|

RDIMM |

|

|

|

|

|

UDIMM |

||||

|

Pin |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

Signal |

|

|

NOTE |

Signal |

NOTE |

||||||||||||||

|

|

|

|

|

|

|

||||||||||||||||

48, 49 |

|

|

|

VTT |

Additional connection for Termination Voltage for |

|

NC |

Not used on UDIMMs |

||||||||||||||

|

|

|

Address/Command/Control/Clock nets. |

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

120, 240 |

|

|

|

VTT |

Termination Voltage for Address/Command/Con- |

|

VTT |

Termination Voltage for Address/Command/Con- |

||||||||||||||

|

|

|

trol/Clock nets. |

|

trol/Clock nets. |

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

Connected to the register on all RDIMMs NC Not |

|

|

|

|

|

|

||||

53 |

|

Err_Out |

|

NC |

NC Not used on UDIMMs |

|||||||||||||||||

|

used on UDIMMs |

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

63 |

|

|

|

|

NC |

Not used on RDIMMs |

|

CK1 |

Used for 2 rank UDIMMs, not used on single-rank |

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

UDIMMs, but terminated |

|||||

64 |

|

|

|

|

NC |

|

CK1 |

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|||||||||||||

68 |

|

|

|

Par_In |

Connected to the register on all RDIMMs |

|

NC |

Not used on RDIMMs |

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Used for dual-rank UDIMMs, not connected |

76 |

|

|

|

|

|

S1 |

Connected to the register on all RDIMMs |

|

S1 |

|||||||||||||

|

|

|

|

|

|

on single-rank UDIMMs |

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

77 |

|

ODT1, NC |

Connected to the register on dualand quadrank |

ODT1,NC |

Used for dual-rank UDIMMs, not connected |

|||||||||||||||||

|

RDIMMs; NC on single-rank RDIMMs |

on single-rank UDIMMs |

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

79 |

|

|

|

|

|

|

|

|

|

|

Connected to the register on quad-rank |

|

|

|

|

|

|

|||||

|

|

S2, NC |