Philips saa7199b DATASHEETS

INTEGRATED CIRCUITS

SAA7199B

Digital Video Encoder (DENC)

GENLOCK-capable

Product specification |

1996 Sep 27 |

Supersedes data of April 1993

File under Integrated Circuits, IC22

Philips Semiconductors |

Product specification |

|

|

Digital Video Encoder (DENC)

SAA7199B

GENLOCK-capable

FEATURES

∙Monolithic integrated CMOS video encoder circuit

∙Standard MPU (12 lines) and I2C-bus interfaces for controls

∙Three 8-bit signal inputs PD7 to PD0 for RGB respectively YUV or indexed colour signals (Tables 19 to 26)

∙Square pixel and CCIR input data rates

∙Band limited composite sync pulses

∙Three 256 × 8 colour look-up tables (CLUTs) for example for gamma correction

∙External subcarrier from a digital decoder (SAA7151B or SAA7191B)

∙Multi-purpose key for real time format switching

∙Autonomous internal blanking

∙Optional GENLOCK operation with adjustable horizontal sync timing and adjustable subcarrier phase

∙Stable GENLOCK operation in VCR standard playback mode

∙Optional still video capture extension

∙Three suitable video 9-bit digital-to-analog converters

∙Composite analog output signals CVBS, Y and C for PAL/NTSC

∙Line 21 data insertion possible.

GENERAL DESCRIPTION

The SAA7199B encodes digital baseband colour/video data into analog Y, C and CVBS signals (S-video included). Pixel clock and data are line-locked to the horizontal scanning frequency of the video signal.

The circuit can be used in a square pixel or in a consumer TV application. Flexibility is provided by programming facilities via MPU-bus (parallel) or I2C-bus (serial).

QUICK REFERENCE DATA

SYMBOL |

PARAMETER |

MIN. |

TYP. |

MAX. |

UNIT |

|

|

|

|

|

|

VDDD |

digital supply voltage (pins 2, 21 and 41) |

4.5 |

5.0 |

5.5 |

V |

VDDA |

analog supply voltage (pins 64, 66, 70 and 72) |

4.75 |

5.0 |

5.25 |

V |

IP(tot) |

total supply current |

− |

− |

200 |

mA |

VI |

input signal levels |

TTL-compatible |

|

||

Vo |

analog output voltage Y, C and CVBS without load (peak-to-peak value) |

− |

2 |

− |

V |

RL |

output load resistance |

90 |

− |

− |

Ω |

ILE |

LF integral linearity error in output signal (9-bit DAC) |

− |

− |

±1 |

LSB |

|

|

|

|

|

|

DLE |

LF differential linearity error in output signal (9-bit DAC) |

− |

− |

±0.5 |

LSB |

|

|

|

|

|

|

Tamb |

operating ambient temperature |

0 |

− |

70 |

°C |

ORDERING INFORMATION

TYPE |

|

PACKAGE |

|

|

|

|

|

NUMBER |

NAME |

DESCRIPTION |

VERSION |

|

|||

|

|

|

|

SAA7199BWP |

PLCC84 |

plastic leaded chip carrier; 84 leads |

SOT189-2 |

|

|

|

|

1996 Sep 27 |

2 |

27Sep 1996 |

|

|

|

|

|

|

|

|

pagewidth full ook, |

|

|

|

|

|

|

|

|

|

|

|

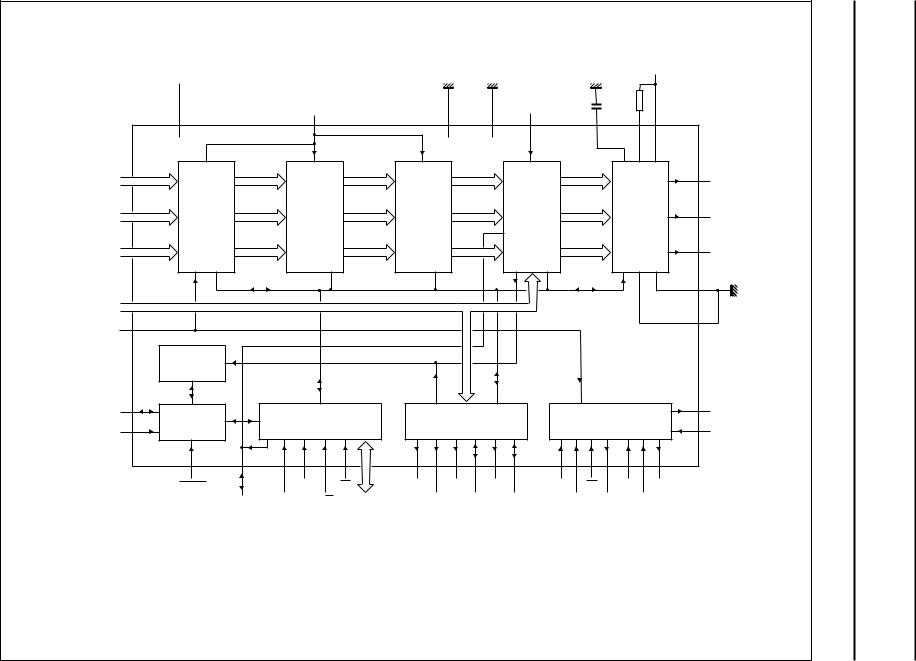

+5 V |

DIAGRAMBLOCK |

capable-GENLOCK |

EncoderVideoDigital |

|

|

|

|

+5 V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MPK |

|

|

VSSD1 to VSSD3 |

|

|

|

KEY |

|

|

|

|

|

|

VDDA1 to |

|

|

|

||

|

|

|

VDDD1 to VDDD3 |

|

|

|

|

|

TP |

VrefH |

|

|

|

|

VDDA4 |

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

CUR |

|

|

|

|

||||||||||

|

|

|

2, 21, 41 |

|

32 |

|

|

|

|

|

1, 22, 42 |

53 |

73 |

|

|

63 |

|

71 |

66, 70, |

|

|

|

|||

|

3 × 8-bit input data |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

72, 64 |

|

|

|

|

PD1(7 to 0)(1) |

11 to 4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

65 |

|

|

|

|

(digital red) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

PD2(7 to 0)(1) |

19 to 12 |

INPUT |

|

|

CLUTS |

|

|

|

|

|

|

|

|

|

|

|

|

|

TRIPLE |

67 |

|

|

(DENC) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DACs |

|

|

|||||||

|

(digital green) |

|

|

|

3 ¥ |

|

|

MATRIX |

|

|

|

|

ENCODER |

|

|

|

Y |

|

|

||||||

|

|

INTERFACE |

|

|

|

|

|

|

|

|

|

|

|

OUTPUT |

|

|

|

||||||||

|

|

|

|

|

256 ¥ 8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

outputs to |

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

RTCI |

|

|

|

|

|

BUFFERS |

|

|

||||||

|

PD3(7 to 0)(1) |

31 to 24 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

monitor/TV |

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

69 |

|

|

|

||

|

(digital blue) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CVBS |

|

|

|

|

|

|

|

|

|

|

internal control bus |

|

|

|

|

|

|

|

|

|

|

|

68 |

VSSA |

|

|

||

|

CVBS(7 to 0) |

83 to 76 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

20 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

62 |

|

|

|

3 |

LDV |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VrefL |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

STATUS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SAA7199B |

|

|

|

|

||

|

|

|

REGISTER |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SDA |

47 |

I2C-BUS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

60 |

XTALO |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

I2C-bus |

48 |

|

CONTROL INTERFACE |

|

SYNC PROCESSING |

|

CLOCK INTERFACE |

59 |

|

|

|

|||||||||||||

|

CONTROL |

|

|

|

|

|

|

||||||||||||||||||

|

SCL |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

XTALI |

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

54 |

57 |

33 |

34 |

35 |

36 |

46 to 43, |

75 |

74 |

61 |

84 |

58 |

3 |

56 |

55 |

23 |

51 |

50 |

49 |

52 |

|

|

|

|

|

|

40 to 37 |

|

|

|

|||||||||||||||||||

|

|

|

|

RTCI/ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

RESET |

GPSW |

|

A1 |

|

CS |

HCL |

LFCO |

|

SLT |

|

CREF |

CB |

CLKSEL |

CLKO |

|

|

|

|||||

|

|

|

|

|

A0 |

R/W |

D(7 to 0) |

HSY |

HSN |

VSN/CSYN |

LLC |

PIXCLK |

CLKIN |

|

MEH416 |

|

|

||||||||

|

|

|

|

|

to/from microcontroller |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

(1) RGB respectively input formats YUV and indexed colour (Tables 19 to 26). |

SAA7199B |

|

|

Fig.1 Block diagram. |

|

Semiconductors Philips

specification Product

Philips Semiconductors |

Product specification |

|

|

Digital Video Encoder (DENC)

SAA7199B

GENLOCK-capable

PINNING

|

SYMBOL |

PIN |

DESCRIPTION |

|||

|

|

|

|

|||

|

VSSD1 |

1 |

digital ground 1 (0 V) |

|||

|

VDDD1 |

2 |

digital supply 1 (5 V) |

|||

|

VSN/CSYN |

3 |

vertical sync output (3-state), conditionally composite sync output; active LOW or active HIGH |

|||

|

|

|

|

|||

|

PD1(0) |

4 |

data 1 input: digital signal R (red) respectively V signal; bit 0 (formats in Tables 19 to 25) |

|||

|

|

|

|

|||

|

PD1(1) |

5 |

data 1 input: digital signal R (red) respectively V signal; bit 1 (formats in Tables 19 to 25) |

|||

|

|

|

|

|||

|

PD1(2) |

6 |

data 1 input: digital signal R (red) respectively V signal; bit 2 (formats in Tables 19 to 25) |

|||

|

|

|

|

|||

|

PD1(3) |

7 |

data 1 input: digital signal R (red) respectively V signal; bit 3 (formats in Tables 19 to 25) |

|||

|

|

|

|

|||

|

PD1(4) |

8 |

data 1 input: digital signal R (red) respectively V signal; bit 4 (formats in Tables 19 to 25) |

|||

|

|

|

|

|||

|

PD1(5) |

9 |

data 1 input: digital signal R (red) respectively V signal; bit 5 (formats in Tables 19 to 25) |

|||

|

|

|

|

|||

|

PD1(6) |

10 |

data 1 input: digital signal R (red) respectively V signal; bit 6 (formats in Tables 19 to 25) |

|||

|

|

|

|

|||

|

PD1(7) |

11 |

data 1 input: digital signal R (red) respectively V signal; bit 7 (formats in Tables 19 to 25) |

|||

|

|

|

|

|||

|

PD2(0) |

12 |

data 2 input: digital signal G (green) respectively Y signal or indexed colour data; bit 0 |

|||

|

|

|

|

(formats in Tables 19 to 25) |

||

|

|

|

|

|||

|

PD2(1) |

13 |

data 2 input: digital signal G (green) respectively Y signal or indexed colour data; bit 1 |

|||

|

|

|

|

(formats in Tables 19 to 25) |

||

|

|

|

|

|||

|

PD2(2) |

14 |

data 2 input: digital signal G (green) respectively Y signal or indexed colour data; bit 2 |

|||

|

|

|

|

(formats in Tables 19 to 25) |

||

|

|

|

|

|||

|

PD2(3) |

15 |

data 2 input: digital signal G (green) respectively Y signal or indexed colour data; bit 3 |

|||

|

|

|

|

(formats in Tables 19 to 25) |

||

|

|

|

|

|||

|

PD2(4) |

16 |

data 2 input: digital signal G (green) respectively Y signal or indexed colour data; bit 4 |

|||

|

|

|

|

(formats in Tables 19 to 25) |

||

|

|

|

|

|||

|

PD2(5) |

17 |

data 2 input: digital signal G (green) respectively Y signal or indexed colour data; bit 5 |

|||

|

|

|

|

(formats in Tables 19 to 25) |

||

|

|

|

|

|||

|

PD2(6) |

18 |

data 2 input: digital signal G (green) respectively Y signal or indexed colour data; bit 6 |

|||

|

|

|

|

(formats in Tables 19 to 25) |

||

|

|

|

|

|||

|

PD2(7) |

19 |

data 2 input: digital signal G (green) respectively Y signal or indexed colour data; bit 7 |

|||

|

|

|

|

(formats in Tables 19 to 25) |

||

|

|

|

|

|

||

|

LDV |

20 |

load data clock input signal to input interface (samples PDn(7 to 0), |

|

MPK, KEY and RTCI) |

|

|

CB, |

|||||

|

|

|

||||

VDDD2 |

21 |

digital supply 2 (5 V) |

||||

VSSD2 |

22 |

digital ground 2 (0 V) |

||||

|

|

|

23 |

composite blanking input; active LOW |

||

|

CB |

|

||||

|

|

|

|

|||

|

PD3(0) |

24 |

data 3 input: digital signal B (blue) respectively U signal; bit 0 (formats in Tables 19 to 25) |

|||

|

|

|

|

|||

|

PD3(1) |

25 |

data 3 input: digital signal B (blue) respectively U signal; bit 1 (formats in Tables 19 to 25) |

|||

|

|

|

|

|||

|

PD3(2) |

26 |

data 3 input: digital signal B (blue) respectively U signal; bit 2 (formats in Tables 19 to 25) |

|||

|

|

|

|

|||

|

PD3(3) |

27 |

data 3 input: digital signal B (blue) respectively U signal; bit 3 (formats in Tables 19 to 25) |

|||

|

|

|

|

|||

|

PD3(4) |

28 |

data 3 input: digital signal B (blue) respectively U signal; bit 4 (formats in Tables 19 to 25) |

|||

|

|

|

|

|||

|

PD3(5) |

29 |

data 3 input: digital signal B (blue) respectively U signal; bit 5 (formats in Tables 19 to 25) |

|||

|

|

|

|

|||

|

PD3(6) |

30 |

data 3 input: digital signal B (blue) respectively U signal; bit 6 (formats in Tables 19 to 25) |

|||

|

|

|

|

|||

|

PD3(7) |

31 |

data 3 input: digital signal B (blue) respectively U signal; bit 7 (formats in Tables 19 to 25) |

|||

|

|

|

|

|||

|

MPK |

32 |

multi-purpose key input; active HIGH |

|||

|

|

|

|

|||

|

A0 |

33 |

subaddress bit A0 input for microcontroller access (Table 3) |

|||

|

|

|

|

|

|

|

1996 Sep 27 |

4 |

Philips Semiconductors |

Product specification |

|

|

Digital Video Encoder (DENC)

SAA7199B

GENLOCK-capable

|

SYMBOL |

PIN |

DESCRIPTION |

||||

|

|

|

|

||||

|

A1 |

34 |

subaddress bit A1 input for microcontroller access (Table 3) |

||||

|

|

|

|

|

|

||

|

|

|

|

|

|

35 |

read/write not input signal from microcontroller |

|

R/W |

|

|

||||

|

|

|

|

|

|||

|

|

|

|

|

|

36 |

chip select input for parallel interface; active LOW |

|

CS |

|

|

||||

|

|

|

|

||||

|

D0 |

37 |

bidirectional port from/to microcontroller; bit D0 |

||||

|

|

|

|

||||

|

D1 |

38 |

bidirectional port from/to microcontroller; bit D1 |

||||

|

|

|

|

||||

|

D2 |

39 |

bidirectional port from/to microcontroller; bit D2 |

||||

|

|

|

|

||||

|

D3 |

40 |

bidirectional port from/to microcontroller; bit D3 |

||||

|

|

|

|

||||

|

VDDD3 |

41 |

digital supply 3 (5 V) |

||||

VSSD3 |

42 |

digital ground 3 |

|||||

D4 |

43 |

bidirectional port from/to microcontroller; bit D4 |

|||||

|

|

|

|||||

D5 |

44 |

bidirectional port from/to microcontroller; bit D5 |

|||||

|

|

|

|||||

D6 |

45 |

bidirectional port from/to microcontroller; bit D6 |

|||||

|

|

|

|||||

D7 |

46 |

bidirectional port from/to microcontroller; bit D7 |

|||||

|

|

|

|||||

SDA |

47 |

I2C-bus data input/output |

|||||

|

SCL |

48 |

I2C-bus clock input |

||||

|

CLKIN |

49 |

external clock signal input (maximum frequency 60 MHz) |

||||

|

|

|

|

||||

|

CLKSEL |

50 |

clock source select input |

||||

|

|

|

|

||||

|

PIXCLK |

51 |

CLKO/2 or conditionally CLKO output signal |

||||

|

|

|

|

||||

|

CLKO |

52 |

selected clock output signal (LLC or CLKIN) |

||||

|

|

|

|

||||

|

TP |

53 |

test pin; connected to ground |

||||

|

|

|

|

||||

|

|

|

|

|

|

54 |

reset input; active LOW |

|

RESET |

|

|||||

|

|

|

|

||||

|

LLC |

55 |

line-locked clock input signal from external clock generation circuit (CGC) |

||||

|

|

|

|

||||

|

CREF |

56 |

clock qualifier input of external CGC |

||||

|

|

|

|

||||

|

GPSW/RTCI |

57 |

general purpose switch output (set via I2C-bus or MPU-bus); real time control input, defined |

||||

|

|

|

|

|

|

|

by I2C or MPU programming |

|

SLT |

58 |

GENLOCK output flag (3-state): HIGH = sync lost in GENLOCK mode; LOW = otherwise |

||||

|

|

|

|

||||

|

XTALI |

59 |

crystal oscillator input (26.8 or 24.576 MHz) |

||||

|

|

|

|

||||

|

XTALO |

60 |

crystal oscillator output |

||||

|

|

|

|

||||

|

LFCO |

61 |

line frequency control output signal for external CGC |

||||

|

|

|

|

||||

|

VrefL |

62 |

reference voltage LOW of DACs (resistor chains) |

||||

VrefH |

63 |

reference voltage HIGH of DACs (resistor chains) |

|||||

VDDA4 |

64 |

analog supply 4 for resistor chains of the DACs (5 V) |

|||||

C |

65 |

chrominance analog output signal |

|||||

|

|

|

|||||

VDDA1 |

66 |

analog supply 1 for output buffer amplifier of DAC1 (5 V) |

|||||

Y |

67 |

luminance analog output signal |

|||||

|

|

|

|||||

VSSA |

68 |

analog ground (0 V) |

|||||

CVBS |

69 |

CVBS analog output signal |

|||||

|

|

|

|||||

VDDA2 |

70 |

analog supply 2 for output buffer amplifier of DAC2 (5 V) |

|||||

CUR |

71 |

current input for analog output buffers |

|||||

|

|

|

|||||

VDDA3 |

72 |

analog supply 3 for output buffer amplifier of DAC3 (5 V) |

|||||

KEY |

73 |

key input signal to insert CVBS input signal into encoded CVBS output signal; active HIGH |

|||||

|

|

|

|

|

|

|

|

1996 Sep 27 |

5 |

Philips Semiconductors |

Product specification |

|

|

Digital Video Encoder (DENC)

SAA7199B

GENLOCK-capable

SYMBOL |

PIN |

DESCRIPTION |

|

|

|

HSY |

74 |

horizontal sync indicator output signal; active HIGH (3-state output to ADC) |

|

|

|

HCL |

75 |

horizontal clamping output; active HIGH (3-state output) |

|

|

|

CVBS0 |

76 |

digital CVBS input signal; bit 0 |

|

|

|

CVBS1 |

77 |

digital CVBS input signal; bit 1 |

|

|

|

CVBS2 |

78 |

digital CVBS input signal; bit 2 |

|

|

|

CVBS3 |

79 |

digital CVBS input signal; bit 3 |

|

|

|

CVBS4 |

80 |

digital CVBS input signal; bit 4 |

|

|

|

CVBS5 |

81 |

digital CVBS input signal; bit 5 |

|

|

|

CVBS6 |

82 |

digital CVBS input signal; bit 6 |

|

|

|

CVBS7 |

83 |

digital CVBS input signal; bit 7 |

|

|

|

HSN |

84 |

horizontal sync output; active LOW or active HIGH for 60/66/72 × PIXCLK at |

|

|

12.27/13.5/14.75 MHz (3-state output) |

|

|

|

1996 Sep 27 |

6 |

Philips Semiconductors |

Product specification |

|

|

Digital Video Encoder (DENC)

SAA7199B

GENLOCK-capable

|

PD1(7) |

PD1(6) |

PD1(5) |

PD1(4) |

PD1(3) |

PD1(2) |

PD1(1) |

PD1(0) |

VSN/CSYN |

DDD1 |

SSD1 |

HSN |

CVBS7 |

CVBS6 |

CVBS5 |

CVBS4 |

CVBS3 |

CVBS2 |

CVBS1 |

CVBS0 |

HCL |

|

|

V |

V |

|

|||||||||||||||||||

|

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

84 |

83 |

82 |

81 |

80 |

79 |

78 |

77 |

76 |

75 |

|

PD2(0) |

12 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

74 |

HSY |

PD2(1) |

13 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

73 |

KEY |

PD2(2) |

14 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

72 |

VDDA3 |

PD2(3) |

15 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

71 |

CUR |

PD2(4) |

16 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

70 |

VDDA2 |

PD2(5) |

17 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

69 |

CVBS |

PD2(6) |

18 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

68 |

VSSA |

PD2(7) |

19 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

67 |

Y |

LDV |

20 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

66 |

VDDA1 |

VDDD2 |

21 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

65 |

C |

VSSD2 |

22 |

|

|

|

|

|

|

|

|

SAA7199B |

|

|

|

|

|

|

|

|

64 |

VDDA4 |

||

CB |

23 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

63 |

VrefH |

PD3(0) |

24 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

62 |

VrefL |

PD3(1) |

25 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

61 |

LFCO |

PD3(2) |

26 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

60 |

XTALO |

PD3(3) |

27 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

59 |

XTALI |

PD3(4) |

28 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

58 |

SLT |

PD3(5) |

29 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

57 |

RTCI/ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

GPSW |

|||

PD3(6) |

30 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

56 |

CREF |

PD3(7) |

31 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

55 |

LLC |

MKP |

32 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

54 |

RESET |

|

33 |

34 |

35 |

36 |

37 |

38 |

39 |

40 |

41 |

42 |

43 |

44 |

45 |

46 |

47 |

48 |

49 |

50 |

51 |

52 |

53 |

|

|

A0 |

A1 |

R/W |

CS |

D0 |

D1 |

D2 |

D3 |

DDD3 |

SSD3 |

D4 |

D5 |

D6 |

D7 |

SDA |

SCL |

CLKIN |

CLKSEL |

PIXCLK |

CLKO |

TP |

MEH417 |

|

|

|||||||||||||||||||||

|

V |

V |

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

Fig.2 |

Pin configuration. |

|

|

|

|

|

|

|

|

||||

1996 Sep 27 |

|

|

|

|

|

|

|

|

|

7 |

|

|

|

|

|

|

|

|

|

|

|

|

Philips Semiconductors |

Product specification |

|

|

Digital Video Encoder (DENC)

SAA7199B

GENLOCK-capable

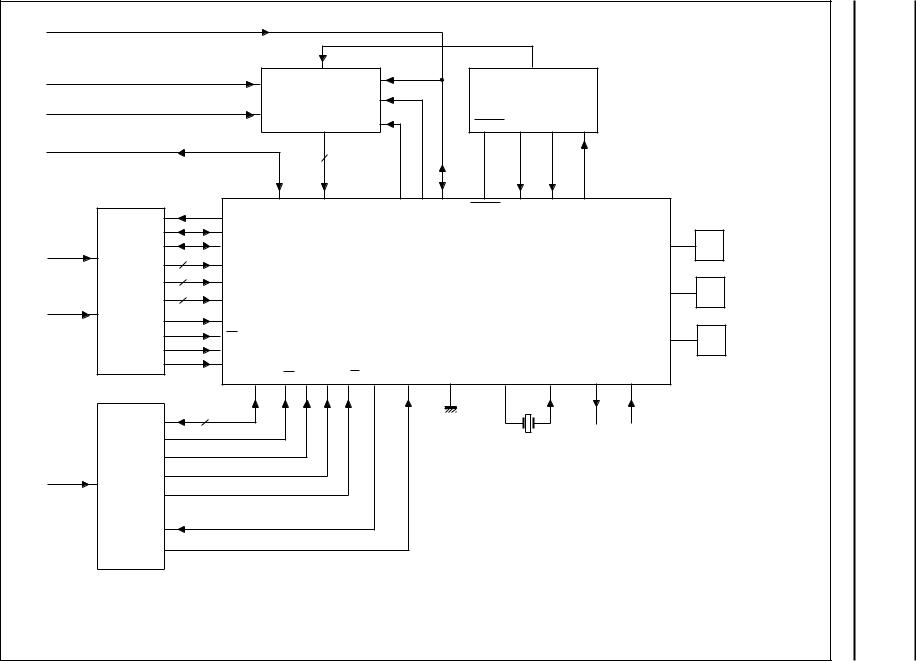

FUNCTIONAL DESCRIPTION

The SAA7199B is a digital video encoder that translates digital RGB, YUV or 8-bit indexed colour signals into the analog PAL/NTSC output signals Y (luminance), C (4.43/3.58 MHz chrominance) and CVBS (composite signal including sync).

Four different modes are selectable (Table 18):

Stand-alone mode (horizontal and vertical timings are generated)

Slave mode (stand-alone unit that accepts external horizontal and vertical timing), and optional real time information for subcarrier/clock from a digital colour decoder

GENLOCK mode (GENLOCK capabilities are achieved in conjunction with determined ICs)

Test mode (only clock signal is required).

The input data rate (pixel sequence) has an integer relationship to the number of horizontal clock cycles (Table 1). A sufficient stable external clock signal ensures correct encoding. The generated clock frequency in the GENLOCK mode may deviate by ±7% depending on the reference signal which is corresponding to its input sync signal. The clock will be nominal in the GENLOCK mode when the reference signal is absent (nominal with crystal oscillator accuracy for TV time constants, and nominal

±1.4% for VCR time constants).

The on-chip colour conversion matrix provides “CCIR 601” code-compatible transcoding of RGB to YUV data.

RGB data out of bounds, with respect to “CCIR 601” specification, can be clipped to prevent over-loading of the colour modulator. RGB data input can be either in linear colour space or in gamma-corrected colour space.

YUV data must be gamma-corrected in accordance with “CCIR 601”. This circuit operates primarily in a 24-bit colour space (3 × 8-bit) but can also accommodate different data formats (4 : 1 : 1, 4 : 2 : 2 and 4 : 4 : 4) plus 8-bit indexed pseudo-colour space operations (FMT-bits in Table 8).

RGB CLUTs on-chip provide gamma-correction and/or other CLUT functions. They consist of programmable tables to be loaded independently, and they generate 24-bit gamma-corrected output signals from 24-bit data of one of the input formats or from 8-bit indexed pseudo-colour data.

Required modulation is performed. The digital YUV data is encoded in accordance with standards “RS-170A” (composite NTSC) and “CCIR 624-4” (composite PAL-B/G). S-video output signal is available (Y/C) also some sub-standard output signals (STD-bits in Table 12).

A 7.5 IRE set-up level is automatically selected in the 60 Hz mode, but not selected in the 50 Hz mode.

The analog signal outputs can drive directly into terminated 75 Ω coaxial lines, a passive external filter is recommended (Figs 3, 13 and 14). Analog post-filtering is required (LP in Fig.3).

GENLOCK to an external reference signal is achieved by addition of a video ADC and a clock generator combination. Thus, the system is enabled to lock on a stable video source or to a stable VCR source (normal playback). The SAA7199B, the ADC and the clock generator combination (Fig.3) form a control loop achieving a highly stable line-locked clock. The clock has to be generated by a crystal oscillator without this availability. The GENLOCK mode is not available in a single device set-up.

Control interface

The SAA7199B supports a standard parallel MPU interface and the serial I2C-bus interface. The MPU has direct access to internal control registers and colour tables. Update is possible at any time, excluding coincident internal reading and external writing of the same cell (the current pixel value could be destroyed).

The two interfaces of Table 2 are selected automatically. However, the I2C-bus control is inactive when the MPU interface is selected by CS = LOW. No simultaneous access may occur. I2C-bus and MPU control complement each other and have access to common registers controlled via a common internal bus. The programmer can use virtually identical programs.

The internal memory space is devided into the look-up table and the control table, each with its own 8-bit address register used as a pointer for specific location.

This address register is provided with auto-incrementation and can be written by only one addressing.

The look-up table contains three banks of 256 bytes. Therefore, each read or write cycle must access all three banks in a pre-determined order. The support logic is part of the control interface.

1996 Sep 27 |

8 |

Philips Semiconductors |

Product specification |

|

|

Digital Video Encoder (DENC)

SAA7199B

GENLOCK-capable

Timing (see Fig.3)

The reference to generate internal clocks from LLC in GENLOCK operation with SAA7197 is CREF

LLC CREF = ----------- .

2

In this event input CLKSEL is HIGH and the SRC-bit = 1.

In non-GENLOCK operation the signal from CLKIN is used and LDV is clock reference (input CLKSEL = 0;

SCR-bit = CPR-bit = 0).

Pins LLC and CLKIN are tied together when no switching between LLC and CLKIN is applied. In Fig.3 it is assumed that LLC and CLKIN are double the pixel clock frequency of CREF and LDV respectively.

CREF must be at the same frequency (or constant HIGH or LOW) when LLC is at pixel clock frequency. CPR-bit = 1 if CLKIN is at pixel clock frequency.

The buffered CLKO signal is always delayed. LLC or CLKIN signals are in accordance with CLKSEL.

Mapping

The method of mapping external control signals on to the internal bus is simple. The MPU-bus contains the signals as shown in Table 4 (names in chip-internal nomenclature).

Bit allocation

The Bit Allocation Map (BAM) shows the individual control signals, used to control the different operational modes of the circuit. The I2C-bus is normally used for control.

The SAA7199B also has an MPU-bus interface for direct microcontroller connection. The BAM shown in Table 6 resembles the I2C-bus type but can be also used for the parallel bus; the control registers are indexed from

00H to 0FH. Auto-incrementation is applied.

Digital-to-analog converters

The converters use a combination of resistor chains with low-impedance output buffers. The bottom output voltage is 200 mV to reduce integral non-linearity errors.

The analog signal, without load on output pin, is between 0.2 and 2.2 V. Figure 16 shows the application for

1.23 V/75 Ω outputs, using the serial 25 + 22 Ω resistors.

Each digital-to-analog converter has its own supply pin for the purpose of decoupling. VDDA4 is the supply voltage for the resistor chains of the three DACs. The accuracy of this supply voltage directly influences the output amplitudes.

The current CUR into pin 71 is 0.3 mA (VDDA4 = 5 V; R64-71 = 20 kΩ); a larger current improves the bandwidth

but increases the integral non-linearity.

Table 1 Pixel relationships

ACTIVE PIXELS |

FIELD RATE |

MULTIPLES OF LINE |

PIXCLK OUTPUT SIGNAL |

CRYSTAL |

PER LINE |

(Hz) |

FREQUENCY |

(MHz) |

(MHz) |

|

|

|

|

|

640 (square) |

60 |

780 |

12.27 |

26.8 |

|

|

|

|

|

720 |

60 |

858 |

13.5 |

24.576 |

|

|

|

|

|

768 |

50 |

944 |

14.75 |

26.8 |

|

|

|

|

|

720 |

50 |

864 |

13.5 |

24.576 |

|

|

|

|

|

Table 2 Access to the control interface

|

|

|

|

SYMBOL |

DESCRIPTION |

|

|

|

|||||

SDA |

I2C-bus serial data line (bidirectional) |

|||||

|

SCL |

I2C-bus clock line |

||||

|

A1, A0 |

MPU-bus address inputs |

||||

|

|

|

|

|

||

|

|

|

|

|

|

read/write control input |

|

R/W |

|

|

|||

|

|

|

|

|||

|

|

|

|

|

|

chip select input; I2C-bus disabled when LOW |

|

CS |

|

|

|||

|

GPSW |

general purpose switch output (bit of control register) |

||||

|

|

|

||||

|

|

|

|

|

|

reset input signal; active-LOW |

|

RESET |

|

||||

|

|

|

|

|

|

|

1996 Sep 27 |

9 |

Philips Semiconductors |

Product specification |

|

|

Digital Video Encoder (DENC)

SAA7199B

GENLOCK-capable

Table 3 |

Address assignment |

|

|

|

|

|

|

|

|

ADDRESS INPUTS |

I2C-BUS SUBADDRESS |

SELECTION |

||

|

|

|

||

A1 |

|

A0 |

||

|

|

|

||

|

|

|

|

|

0 |

|

0 |

00 |

ADR-CLUT (address register of look-up tables) |

|

|

|

|

|

0 |

|

1 |

01 |

DATA-CLUT |

|

|

|

|

|

1 |

|

0 |

02 |

ADR-CTRL (index register of control table) |

|

|

|

|

|

1 |

|

1 |

03 |

DATA-CTRL |

|

|

|

|

|

Table 4 Signals on the internal bus

|

|

|

|

|

SYMBOL |

|

|

|

|

|

|

|

DESCRIPTION |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

select read/write (read = 1; write = 0) |

||||||

R/W |

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

control table/look-up table (control table = 1; look-up table = 0) |

||||||

C/T |

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

select data/address (data = 1; address = 0) |

||||||

D/A |

|

|

|

||||||||||

|

|

|

|||||||||||

DI/DO (0 to 7) |

data bus on port inputs/outputs D7 to D0 |

||||||||||||

|

|

|

|

||||||||||

EN |

|

enable from control interface to synchronize data transfer |

|||||||||||

|

|

|

|||||||||||

Table 5 Signals on the internal bus |

|

||||||||||||

|

|

|

|

||||||||||

INTERNAL PARALLEL BUS |

|

PARALLEL INTERFACE |

I2C-BUS INTERFACE |

||||||||||

|

|

|

|

|

|

|

|

|

|

(pin 35) |

LSB of slave address byte (read = HIGH; write = LOW) |

||

R/W |

|

|

R/W |

||||||||||

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

A1 (pin 34) |

X 4 subaddresses after decoding |

|||||

C/T |

|

|

|||||||||||

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

A0 (pin 33) |

X 4 subaddresses after decoding |

|||||

A/T |

|

|

|||||||||||

|

|

|

|||||||||||

DI/DO (0 to 7) |

D7 to D0 |

data bits D7 to D0 for each subaddress |

|||||||||||

|

|

|

|

|

|

||||||||

EN |

|

|

|

|

|

|

|

enable by every 9th clock of sample of SCL |

|||||

|

CS |

and R/W |

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

(control of serial-to-parallel conversion) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1996 Sep 27 |

10 |

27Sep1996 |

RTCO (from SAA7151B or SAA7191B) |

|

|

|

pagewidthfull ook, |

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|||

|

CVBS1 |

|

(1) |

|

CLK |

|

GPSW |

(1) |

LLC2A |

|

|

|

|

|

VIN0 |

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

CVBS2 |

|

|

TDA8708A (ADC) |

|

|

|

SAA7197 (CGC) |

|

||

|

|

|

|

VIN1 |

D(7 to 0) |

|

|

|

RESET CREF LLCA |

LFCO |

|

|

|

|

|

|

|

|

|

||||

|

I2C-bus controls |

|

|

8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SDA |

CVBS(7 to 0) |

|

HCL HSY GPSW RESET CREF |

LLC |

LFCO |

||

|

|

|

PIXCLK |

SCL |

|

|

|

RTCI (2) |

|

|

|

|

|

|

HSN |

|

|

|

|

|

|

|

|

|

data |

|

VSN |

|

|

|

|

|

|

|

C |

|

|

8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PD1(7 to 0) |

|

|

|

|

|

|

|

|

|

|

RAM |

8 |

|

|

|

|

|

|

|

|

|

|

PD2(7 to 0) input |

|

|

|

|

|

|

|

||

|

|

INTERFACE |

8 |

data |

|

|

|

SAA7199B |

|

Y |

|

|

controls |

|

PD3(7 to 0) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

11 |

|

|

LDV |

|

|

|

|

|

|

|

|

|

|

CB |

|

|

|

|

|

|

|

CVBS |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

KEY |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MPK |

|

|

|

|

|

|

|

|

|

|

|

D(7 to 0) CS |

A1 A0 R/W |

SLT |

CLKSEL |

TP |

XTALO |

XTALI |

CLKO CLKIN |

|

|

|

|

8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

pixel frequency |

|

|

|

|

|

|

|

|

|

|

|

in non-GENLOCK |

|

|

|

|

|

|

|

|

|

|

|

mode |

|

controls |

MPU |

|

|

|

|

|

|

|

|

(fpix or 2fpix) |

|

|

INTERFACE |

|

|

|

|

|

|

|

|

|

(1)Not necessary in GENLOCK mode.

(2)RTCI optional (GPSW not possible).

Fig.3 System configuration.

analog outputs (passive filters optional)

LP  C

C

LP  Y

Y

LP  CVBS

CVBS

MHA 418

capable-GENLOCK |

Encoder Video Digital |

|

(DENC) |

SAA7199B

Semiconductors Philips

specification Product

Philips Semiconductors |

Product specification |

|

|

Digital Video Encoder (DENC)

SAA7199B

GENLOCK-capable

Table 6 Bit allocation map (I2C-bus access in Table 17)

INDEX |

|

|

|

|

DATA BYTE |

|

|

|

DF(1) |

||

|

|

|

|

|

|

|

|

|

|

|

|

BINARY |

|

HEX |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

Input processing |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

0000 0000 |

|

00 |

VTBY |

FMT2 |

FMT1 |

FMT0 |

SCBW |

CCIR |

MOD1 |

MOD0 |

5C |

|

|

|

|

|

|

|

|

|

|

|

|

0000 0001 |

|

01 |

TRER7 |

TRER6 |

TRER5 |

TRER4 |

TRER3 |

TRER2 |

TRER1 |

TRER0 |

XX |

|

|

|

|

|

|

|

|

|

|

|

|

0000 0010 |

|

02 |

TREG7 |

TREG6 |

TREG5 |

TREG4 |

TREG3 |

TREG2 |

TREG1 |

TREG0 |

XX |

|

|

|

|

|

|

|

|

|

|

|

|

0000 0011 |

|

03 |

TREB7 |

TREB6 |

TREB5 |

TREB4 |

TREB3 |

TREB2 |

TREB1 |

TREB0 |

XX |

|

|

|

|

|

|

|

|

|

|

|

|

Sync processing |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

0000 0100 |

|

04 |

SYSEL1 |

SYSEL0 |

SCEN |

VTRC |

NINT |

HPLL |

HLCK(2) |

OEF(2) |

10 |

0000 0101 |

|

05 |

0 |

0 |

GDC5 |

GDC4 |

GDC3 |

GDC2 |

GDC1 |

GDC0 |

21 |

|

|

|

|

|

|

|

|

|

|

|

|

0000 0110 |

|

06 |

IDEL7 |

IDEL6 |

IDEL5 |

IDEL4 |

IDEL3 |

IDEL2 |

IDEL1 |

IDEL0 |

52 |

|

|

|

|

|

|

|

|

|

|

|

|

0000 0111 |

|

07 |

0 |

0 |

PSO5 |

PSO4 |

PSO3 |

PSO2 |

PSO1 |

PSO0 |

32 |

|

|

|

|

|

|

|

|

|

|

|

|

Control, clock and output formatter |

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

0000 1000 |

|

08 |

DD |

KEYE |

SRC |

CPR |

COKI |

IM |

GPSW |

SRSN |

64 |

|

|

|

|

|

|

|

|

|

|

|

|

0000 1001 |

|

09 |

0 |

BAME |

MPKC1 |

MPKC0 |

IEPI |

RTSC |

RTIN |

RTCE |

02 |

|

|

|

|

|

|

|

|

|

|

|

|

0000 1010(3) |

|

0A(3) |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

00 |

0000 1011(3) |

|

0B(3) |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

00 |

Encoder control |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

0000 1100 |

|

0C |

CHPS7 |

CHPS6 |

CHPS5 |

CHPS4 |

CHPS3 |

CHPS2 |

CHPS1 |

CHPS0 |

XX(4) |

0000 1101 |

|

0D |

FSCO7 |

FSCO6 |

FSCO5 |

FSCO4 |

FSCO3 |

FSCO2 |

FSCO1 |

FSCO0 |

00 |

|

|

|

|

|

|

|

|

|

|

|

|

0000 1110 |

|

0E |

0 |

0 |

0 |

CLCK(2) |

STD3 |

STD2 |

STD1 |

STD0 |

0C |

0000 1111(3) |

|

0F(3) |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

Notes

1.DF is the default value for a typical programming example: GENLOCK mode for a VCR; non-gamma-corrected RGB data (real time keying is possible). SLT will be set if there is no horizontal lock.NTSC-M standard with normal colour bandwidth and 12.2727 MHz pixel rate. CSYN signal will be provided, arriving 8 pixel clocks earlier, to compensate pipeline delay in the previous RAM interface. The encoded CVBS is 12 clocks earlier than the CVBS reference on the input of the previous ADC. The CLUTs are bypassed at MPK = HIGH in real time.

2.Read only bits.

3.Reserved.

4.Adjust as required.

1996 Sep 27 |

12 |

Loading...

Loading...