Philips SAA5561PS, SAA5530PS, SAA5532PS, SAA5533PS, SAA5562PS Datasheet

...

INTEGRATED CIRCUITS

DATA SHEET

SAA55xx

Enhanced TV microcontrollers with On-Screen Display (OSD)

Preliminary specification |

|

1999 Aug 02 |

|||||

File under Integrated Circuits, IC02 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Philips Semiconductors Preliminary specification

Enhanced TV microcontrollers with |

|

SAA55xx |

||

On-Screen Display (OSD) |

|

|||

|

|

|||

|

|

|

||

|

|

|

||

CONTENTS |

17 |

MEMORY INTERFACE |

||

1 |

FEATURES |

17.1 |

Memory structure |

|

17.2 |

Memory mapping |

|||

2 |

GENERAL DESCRIPTION |

|||

17.3 |

Addressing memory |

|||

3 |

QUICK REFERENCE DATA |

17.4 |

Page clearing |

|

4 |

ORDERING INFORMATION |

18 |

DATA CAPTURE |

|

5 |

BLOCK DIAGRAM |

18.1 |

Data Capture features |

|

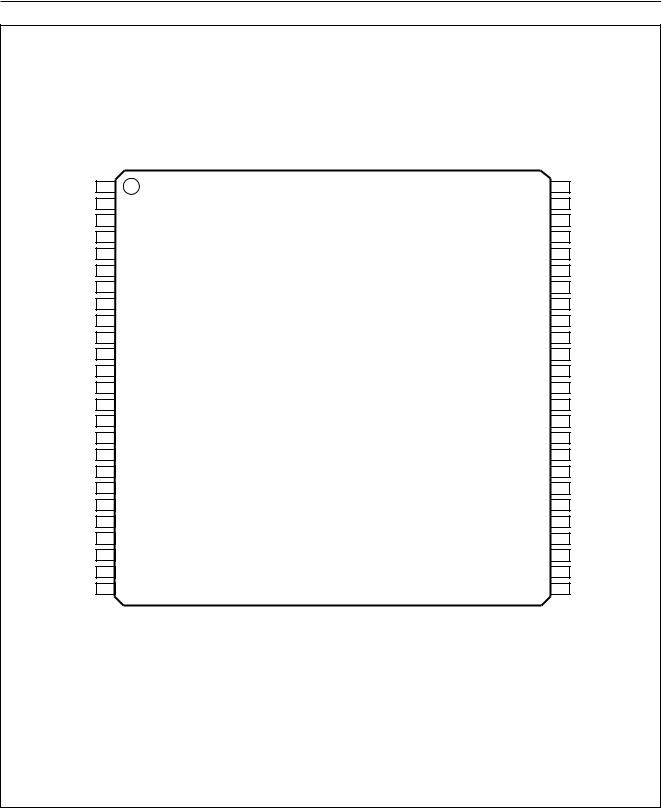

6 |

PINNING INFORMATION |

19 |

DISPLAY |

|

6.1 |

Pinning |

19.1 |

Display features |

|

6.2 |

Pin description |

19.2 |

Display modes |

|

7 |

MICROCONTROLLER |

19.3 |

Display feature descriptions |

|

19.4 |

Character and attribute coding |

|||

7.1 |

Microcontroller features |

|||

19.5 |

Screen and global controls |

|||

|

|

|||

8 |

MEMORY ORGANIZATION |

19.6 |

Screen colour |

|

8.1 |

ROM bank switching |

19.7 |

Text display controls |

|

19.8 |

Soft scroll action |

|||

8.2 |

Security bits - program and verify |

|||

19.9 |

Display positioning |

|||

8.3 |

RAM organisation |

|||

19.10 |

Character set |

|||

8.4 |

Data memory |

|||

19.11 |

ROM addressing |

|||

8.5 |

SFR memory |

|||

19.12 |

Redefinable characters |

|||

8.6 |

Character set feature bits |

|||

19.13 |

Display synchronization |

|||

8.7 |

External (Auxiliary) memory |

|||

19.14 |

Video/data switch (Fast Blanking) polarity |

|||

9 |

POWER-ON RESET |

|||

19.15 |

Video/Data switch adjustment |

|||

10 |

REDUCED POWER MODES |

|||

19.16 |

RGB brightness control |

|||

10.1 |

Idle mode |

19.17 |

Contrast reduction |

|

10.2 |

Power-down mode |

20 |

MEMORY MAPPED REGISTERS (MMR) |

|

10.3 |

Standby mode |

21 |

LIMITING VALUES |

|

11 |

I/O FACILITY |

|||

22 |

CHARACTERISTICS |

|||

|

|

|||

11.1I/O ports

11.2Port type

11.3Port alternative functions

11.4LED support

12 INTERRUPT SYSTEM

12.1Interrupt enable structure

12.2Interrupt enable priority

12.3Interrupt vector address

12.4Level/edge interrupt

13TIMER/COUNTER

14WATCHDOG TIMER

14.1Watchdog Timer operation

15 PULSE WIDTH MODULATORS

15.1PWM control

15.2Tuning Pulse Width Modulator (TPWM)

15.3Software ADC (SAD)

16 I2C-BUS SERIAL I/O

16.1I2C-bus port selection

23 QUALITY AND RELIABILITY

23.1Group A

23.2Group B

23.3Group C

24APPLICATION INFORMATION

25EMC GUIDELINES

26REFERENCES

27PACKAGE OUTLINE

28SOLDERING

28.1Introduction to soldering through-hole mount packages

28.2Soldering by dipping or by solder wave

28.3Manual soldering

28.4Suitability of through-hole mount IC packages for dipping and wave soldering methods

29DEFINITIONS

30LIFE SUPPORT APPLICATIONS

31PURCHASE OF PHILIPS I2C COMPONENTS

1999 Aug 02 |

2 |

Philips Semiconductors |

Preliminary specification |

|

|

Enhanced TV microcontrollers with

SAA55xx

On-Screen Display (OSD)

1 FEATURES

∙Single-chip microcontroller with integrated OSD

∙Versions available with integrated data capture

∙OTP memory for both program ROM and character sets

∙Single power supply: 3.0 to 3.6 V

∙5 V tolerant digital inputs and I/O

∙29 I/O ports via individual addressable controls

∙Programmable I/O for push-pull, open-drain and quasi-bidirectional

∙Two port lines with 8 mA sink (at <0.4 V) capability, for direct drive of LED

∙Single crystal oscillator for microcontroller, OSD and data capture

∙Power reduction modes: Idle and Power-down

∙Byte level I2C-bus interface with dual port I/O

∙32 Dynamically Redefinable Characters for OSDs

∙Special graphic characters allowing four colours per character

∙Selectable character height 9, 10, 13 and 16 TV lines

∙Pin compatibility throughout family

∙Operating temperature: −20 to +70 °C.

3 QUICK REFERENCE DATA

2 GENERAL DESCRIPTION

The SAA55xx family of microcontrollers are a derivative of the Philips industry-standard 80C51 microcontroller and are intended for use as the central control mechanism in a television receiver. They provide control functions for the television system, On-Screen Display (OSD) and some versions include an integrated data capture and display function.

The data capture hardware has the capability of decoding and displaying both 525 and 625-line World System Teletext (WST), Closed Caption (CC) information, Video Programming Information (VPS) and Wide Screen Signalling (WSS) information. The same display hardware is used both for Teletext, Closed Caption and On-Screen Display, which means that the display features available give greater flexibility to differentiate the TV set.

The SAA55xx family offers a range of functionality from non-text, 16-kbyte program ROM and 256-byte RAM, to a 10 page text version, 128-kbyte program ROM and 2.25-kbyte RAM.

SYMBOL |

PARAMETER |

MIN. |

TYP. |

MAX. |

UNIT |

|

|

|

|

|

|

Supply |

|

|

|

|

|

|

|

|

|

|

|

VDDX |

any supply voltage (VDD to VSS) |

3.0 |

3.3 |

3.6 |

V |

IDDP |

periphery supply current |

1 |

− |

− |

mA |

IDDC |

core supply current |

− |

15 |

18 |

mA |

IDDC(id) |

Idle mode core supply current |

− |

4.6 |

6 |

mA |

IDDC(pd) |

Power-down mode core supply current |

− |

0.76 |

1 |

mA |

IDDA |

analog supply current |

− |

45 |

48 |

mA |

IDDA(id) |

Idle mode analog supply current |

− |

0.87 |

1.0 |

mA |

IDDA(pd) |

Power-down mode analog supply current |

− |

0.45 |

0.7 |

mA |

fxtal |

crystal frequency |

− |

12 |

− |

MHz |

Tamb |

operating ambient temperature |

−20 |

− |

+70 |

°C |

Tstg |

storage temperature |

−55 |

− |

+125 |

°C |

1999 Aug 02 |

3 |

Philips Semiconductors |

Preliminary specification |

|

|

Enhanced TV microcontrollers with

SAA55xx

On-Screen Display (OSD)

4 ORDERING INFORMATION

TYPE NUMBER(1) |

|

PACKAGE(2) |

|

ROM |

RAM |

TEXT |

|

|

|

|

|||||

NAME |

DESCRIPTION |

VERSION |

PAGES |

||||

|

|

|

|||||

|

|

|

|

||||

|

|

|

|

|

|

|

|

SAA5530PS/nnnn |

SDIP52 |

plastic shrink dual in-line package; |

SOT247-1 |

16-kbyte |

256-byte |

1 |

|

|

|

52 leads (600 mil) |

|

|

|

|

|

SAA5531PS/nnnn |

|

|

32-kbyte |

512-byte |

1 |

||

|

|

|

|||||

|

|

|

|

|

|

|

|

SAA5532PS/nnnn |

|

|

|

48-kbyte |

750-byte |

1 |

|

|

|

|

|

|

|

|

|

SAA5533PS/nnnn |

|

|

|

64-kbyte |

1-kbyte |

1 |

|

|

|

|

|

|

|

|

|

SAA5561PS/nnnn |

|

|

|

32-kbyte |

750-byte |

10 |

|

|

|

|

|

|

|

|

|

SAA5562PS/nnnn |

|

|

|

48-kbyte |

1-kbyte |

10 |

|

|

|

|

|

|

|

|

|

SAA5563PS/nnnn |

|

|

|

64-kbyte |

1.2-kbyte |

10 |

|

|

|

|

|

|

|

|

|

SAA5564PS/nnnn |

|

|

|

96-kbyte |

1.5-kbyte |

10 |

|

|

|

|

|

|

|

|

|

SAA5565PS/nnnn |

|

|

|

128-kbyte |

2.25-kbyte |

10 |

|

|

|

|

|

|

|

|

Notes

1.‘nnnn’ is a four digit number uniquely referencing the microcontroller program mask.

2.For details of the LQFP100 package, please contact your local regional sales office for availability.

1999 Aug 02 |

4 |

Philips Semiconductors |

Preliminary specification |

|

|

Enhanced TV microcontrollers with

SAA55xx

On-Screen Display (OSD)

5 BLOCK DIAGRAM

I2C-bus, general I/O |

|

|

|

|

TV CONTROL |

|

|

|

||||||||||

|

|

|

|

AND |

|

|

|

|||||||||||

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

INTERFACE |

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ROM |

|

|

|

MICROPROCESSOR |

|

|

|

|

SRAM |

|||||||||

(16 TO 128-KBYTE) |

|

|

|

|

|

|

(80C51) |

|

|

|

(256-BYTE) |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

DRAM |

|

|

|

|

|

|

MEMORY |

|

|

|

||||||||

(3 TO 12-KBYTE) |

|

|

|

|

|

INTERFACE |

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CVBS |

|

|

|

DATA |

|

|

|

|

|

|

DISPLAY |

|

G |

|||||

|

|

|

|

|

|

|

|

|

||||||||||

|

|

CAPTURE |

|

|

|

|

|

|

|

B |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VDS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DATA |

|

|

|

|

|

|

DISPLAY |

|

VSYNC |

|||||

|

|

|

|

|

|

|

|

|

|

|

||||||||

CVBS |

|

|

CAPTURE |

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

TIMING |

|

HSYNC |

||||||||

|

|

|

TIMING |

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MBK950 |

|

|

|

Fig.1 Block diagram (top level architecture).

1999 Aug 02 |

5 |

Philips Semiconductors |

Preliminary specification |

|

|

Enhanced TV microcontrollers with

SAA55xx

On-Screen Display (OSD)

6 PINNING INFORMATION

6.1Pinning

P2.0/TPWM |

|

|

|

|

|

|

1 |

|

52 |

P1.5/SDA1 |

|||

|

|

|

|

|

|

|

P2.1/PWM0 |

2 |

|

51 |

P1.4/SCL1 |

||

|

|

|

|

|

|

|

P2.2/PWM1 |

3 |

|

50 |

P1.7/SDA0 |

||

|

|

|

|

|

|

|

P2.3/PWM2 |

4 |

|

49 |

P1.6/SCL0 |

||

|

|

|

|

|

|

|

P2.4/PWM3 |

5 |

|

48 |

P1.3/T1 |

||

|

|

|

|

|

|

|

P2.5/PWM4 |

6 |

|

47 |

P1.2/INT0 |

||

|

|

|

|

|

|

|

P2.6/PWM5 |

7 |

|

46 |

P1.1/T0 |

||

|

|

|

|

|

|

|

P2.7/PWM6 |

8 |

|

45 |

P1.0/INT1 |

||

|

|

|

|

|

|

|

P3.0/ADC0 |

9 |

|

44 |

VDDP |

||

|

|

|

|

|

|

|

P3.1/ADC1 |

10 |

|

43 |

RESET |

||

|

|

|

|

|

|

|

P3.2/ADC2 |

11 |

|

42 |

XTALOUT |

||

|

|

|

|

|

|

|

P3.3/ADC3 |

12 |

|

41 |

XTALIN |

||

|

|

|

|

|

|

|

VSSC |

13 |

SAA55xx |

40 |

OSCGND |

||

|

|

|

|

|

|

|

P0.0 |

14 |

|

39 |

VDDC |

||

|

|

|

|

|

|

|

P0.1 |

15 |

|

38 |

VSSP |

||

|

|

|

|

|

|

|

P0.2 |

16 |

|

37 |

VSYNC |

||

|

|

|

|

|

|

|

P0.3 |

17 |

|

36 |

HSYNC |

||

|

|

|

|

|

|

|

P0.4 |

18 |

|

35 |

VDS |

||

|

|

|

|

|

|

|

P0.5 |

19 |

|

34 |

R |

||

|

|

|

|

|

|

|

P0.6 |

20 |

|

33 |

G |

||

|

|

|

|

|

|

|

P0.7 |

21 |

|

32 |

B |

||

|

|

|

|

|

|

|

VSSA |

22 |

|

31 |

VDDA |

||

|

|

|

|

|

|

|

CVBS0 |

23 |

|

30 |

P3.4/PWM7 |

||

|

|

|

|

|

|

|

CVBS1 |

24 |

|

29 |

COR |

||

|

|

|

|

|

|

|

SYNC_FILTER |

25 |

|

28 |

VPE |

||

|

|

|

|

|

|

|

IREF |

26 |

|

27 |

FRAME |

||

|

|

|

|

|

|

|

|

|

MBK951 |

|

|

|

|

Fig.2 SDIP52 pin configuration.

1999 Aug 02 |

6 |

Philips Semiconductors |

Preliminary specification |

|

|

Enhanced TV microcontrollers with

SAA55xx

On-Screen Display (OSD)

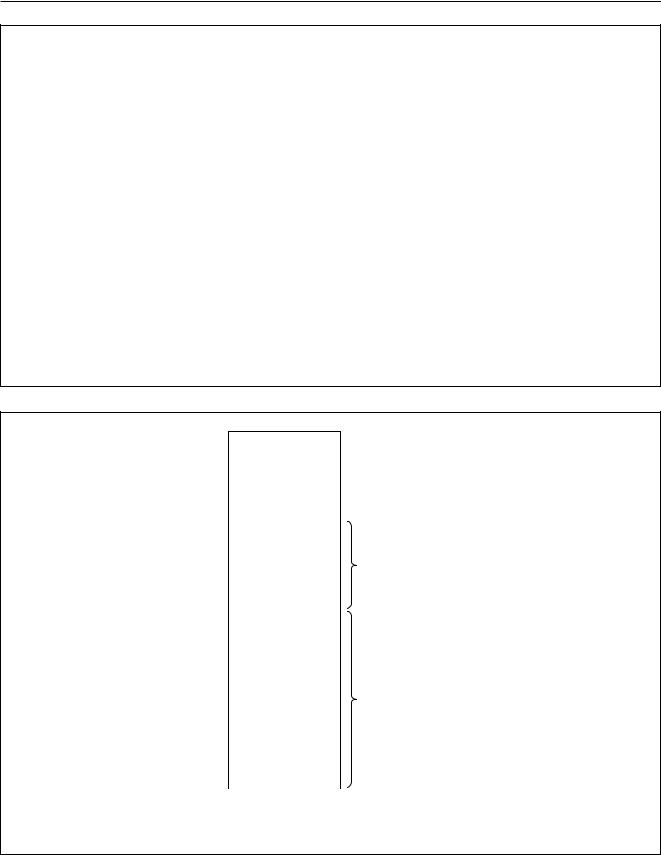

handbook, full pagewidth

P2.7/PWM6 1 P3.0/ADC0 2 n.c. 3 P3.1/ADC1 4 P3.2/ADC2 5 P3.3/ADC3 6 n.c. 7 n.c. 8 n.c. 9 n.c. 10

VSSC 11

VSSP 12

P0.5 13

n.c. 14

n.c. 15

P0.0 16

P0.1 17

P0.2 18

n.c. 19

n.c. 20

n.c. 21

P0.3 22

n.c. 23

P0.4 24

P3.7 25

P2.0/TPWM |

|

n.c. |

|

P2.6/PWM5 |

|

P2.5/PWM4 |

|

P2.4/PWM3 |

|

P2.3/PWM2 |

|

P2.2/PWM1 |

|

P2.1/PWM0 |

|

n.c. |

|

n.c. |

|

n.c. |

|

n.c. |

|

n.c. |

|

n.c. |

|

n.c. |

|

n.c. |

|

P1.5/SDA1 |

|

P1.4/SCL1 |

|

P1.7/SDA0 |

|

P1.6/SCL0 |

|

P1.3/T1 |

|

P1.2/INT0 |

|

P1.1/T0 |

|

n.c. |

|

P1.0/INT1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

100 |

|

99 |

|

98 |

|

97 |

|

96 |

|

95 |

|

94 |

|

93 |

|

92 |

|

91 |

|

90 |

|

89 |

|

88 |

|

87 |

|

86 |

|

85 |

|

84 |

|

83 |

|

82 |

|

81 |

|

80 |

|

79 |

|

78 |

|

77 |

|

76 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SAA55xx

26 |

|

27 |

|

28 |

|

29 |

|

30 |

|

31 |

|

32 |

|

33 |

|

34 |

|

35 |

|

36 |

|

37 |

|

38 |

|

39 |

|

40 |

|

41 |

|

42 |

|

43 |

|

44 |

|

45 |

|

46 |

|

47 |

|

48 |

|

49 |

|

50 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

n.c. |

|

n.c. |

|

P0.6 |

|

P0.7 |

|

SSA |

CVBS0 |

|

CVBS1 |

|

n.c. |

|

SYNC FILTER |

|

IREF |

|

n.c. |

|

n.c. |

|

n.c. |

|

n.c. |

|

n.c. |

|

FRAME |

|

VPE |

|

COR |

|

P3.4/PWM7 |

|

DDA |

B |

|

G |

|

R |

|

n.c. |

|

n.c. |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

V |

|

|

|

|

|

|

|

|

|

|||||||||

75 VDDP

74 n.c.

73 RESET

72 n.c.

71 XTALOUT

70 XTALIN

69 OSCGND

68 n.c.

67 n.c.

66 n.c.

65 n.c.

64 n.c.

63 VDDC

62 VPE_2

61 n.c.

60 VSSP

59 P3.6

58 n.c.

57 n.c.

56 n.c.

55 VSYNC

54 P3.5

53 HSYNC

52 VDS

51 n.c.

GSA001

Fig.3 LQFP100 pin configuration.

1999 Aug 02 |

7 |

Philips Semiconductors |

Preliminary specification |

|

|

Enhanced TV microcontrollers with

SAA55xx

On-Screen Display (OSD)

6.2Pin description

Table 1 SDIP52 and LQFP100 packages

SYMBOL |

|

PIN |

TYPE |

DESCRIPTION |

|

|

|

||||

SDIP52 |

LQFP100 |

||||

|

|

|

|||

|

|

|

|

|

|

P2.0/TPWM |

1 |

100 |

I/O |

Port 2. 8-bit programmable bidirectional port with |

|

|

|

|

|

alternative functions. |

|

P2.1/PWM0 |

2 |

93 |

I/O |

||

|

|||||

|

|

|

|

|

|

P2.2/PWM1 |

3 |

94 |

I/O |

P2.0/TPWM is the output for the 14-bit high |

|

|

|

|

|

precision PWM; P2.1/PWM0 to P2.7/PWM6 are the |

|

P2.3/PWM2 |

4 |

95 |

I/O |

||

outputs for the 6-bit PWMs 0 to 6. |

|||||

|

|

|

|

||

P2.4/PWM3 |

5 |

96 |

I/O |

||

|

|||||

|

|

|

|

|

|

P2.5/PWM4 |

6 |

97 |

I/O |

|

|

|

|

|

|

|

|

P2.6/PWM5 |

7 |

98 |

I/O |

|

|

|

|

|

|

|

|

P2.7/PWM6 |

8 |

1 |

I/O |

|

|

|

|

|

|

|

|

P3.0/ADC0 |

9 |

2 |

I/O |

Port 3. 8-bit programmable bidirectional port with |

|

|

|

|

|

alternative functions. |

|

P3.1/ADC1 |

10 |

4 |

I/O |

||

|

|||||

|

|

|

|

|

|

P3.2/ADC2 |

11 |

5 |

I/O |

P3.0/ADC0 to P3.3/ADC3 are the inputs for the |

|

|

|

|

|

software ADC facility and P3.4/PWM7 is the output |

|

P3.3/ADC3 |

12 |

6 |

I/O |

||

for the 6-bit PWM7. P3.5 to P3.7 have no alternative |

|||||

|

|

|

|

||

P3.4/PWM7 |

30 |

44 |

I/O |

||

functions and are only available with the LQFP100 |

|||||

|

|

|

|

||

P3.5 |

− |

54 |

I/O |

||

package. |

|||||

|

|

|

|

||

P3.6 |

− |

59 |

I/O |

|

|

|

|

|

|

|

|

P3.7 |

− |

25 |

I/O |

|

|

|

|

|

|

|

|

VSSC |

13 |

11 |

− |

core ground |

|

P0.0 |

14 |

16 |

I/O |

Port 0. 8-bit programmable bidirectional port. |

|

|

|

|

|

|

|

P0.1 |

15 |

17 |

I/O |

P0.5 and P0.6 have 8 mA current sinking capability |

|

|

|

|

|

||

P0.2 |

16 |

18 |

I/O |

for direct drive of LEDs. |

|

|

|

|

|

|

|

P0.3 |

17 |

22 |

I/O |

|

|

|

|

|

|

|

|

P0.4 |

18 |

24 |

I/O |

|

|

|

|

|

|

|

|

P0.5 |

19 |

13 |

I/O |

|

|

|

|

|

|

|

|

P0.6 |

20 |

28 |

I/O |

|

|

|

|

|

|

|

|

P0.7 |

21 |

29 |

I/O |

|

|

|

|

|

|

|

|

VSSA |

22 |

30 |

− |

analog ground |

|

CVBS0 |

23 |

31 |

I |

Composite video input. A positive-going 1 V |

|

|

|

|

|

(peak-to-peak) input is required. |

|

|

|

|

|

|

|

CVBS1 |

24 |

32 |

I |

connected via a 100 nF capacitor |

|

|

|

|

|

|

|

SYNC_FILTER |

25 |

34 |

I |

CVBS sync filter input. This pin should be |

|

|

|

|

|

connected to VSSA via a 100 nF capacitor. |

|

IREF |

26 |

35 |

I |

Reference current input for analog circuits, |

|

|

|

|

|

connected to VSSA via a 24 kΩ resistor. |

|

FRAME |

27 |

41 |

O |

De-interlace output synchronized with the VSYNC |

|

|

|

|

|

pulse to produce a non-interlaced display by |

|

|

|

|

|

adjustment of the vertical deflection circuits. |

|

|

|

|

|

|

|

VPE |

28 |

42 |

I |

OTP programming voltage |

|

|

|

|

|

|

1999 Aug 02 |

8 |

Philips Semiconductors |

Preliminary specification |

|

|

Enhanced TV microcontrollers with

SAA55xx

On-Screen Display (OSD)

|

SYMBOL |

|

PIN |

TYPE |

DESCRIPTION |

||

|

|

|

|||||

|

SDIP52 |

LQFP100 |

|||||

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

29 |

43 |

O |

Open-drain, active LOW output which allows |

|

COR |

|||||||

|

|

|

|

|

|

selective contrast reduction of the TV picture to |

|

|

|

|

|

|

|

enhance a mixed mode display. |

|

|

|

|

|

|

|||

VDDA |

31 |

45 |

− |

+3.3 V analog power supply |

|||

B |

32 |

46 |

O |

pixel rate output of the BLUE colour information |

|||

|

|

|

|

|

|||

G |

33 |

47 |

O |

pixel rate output of the GREEN colour information |

|||

|

|

|

|

|

|||

R |

34 |

48 |

O |

pixel rate output of the RED colour information |

|||

|

|

|

|

|

|||

VDS |

35 |

52 |

O |

video/data switch push-pull output for dot rate fast |

|||

|

|

|

|

|

|

blanking |

|

|

|

|

|

|

|||

HSYNC |

36 |

53 |

I |

Schmitt triggered input for a TTL-level version of the |

|||

|

|

|

|

|

|

horizontal sync pulse; the polarity of this pulse is |

|

|

|

|

|

|

|

programmable by register bit TXT1.H POLARITY. |

|

|

|

|

|

|

|||

VSYNC |

37 |

55 |

I |

Schmitt triggered input for a TTL-level version of the |

|||

|

|

|

|

|

|

vertical sync pulse; the polarity of this pulse is |

|

|

|

|

|

|

|

programmable by register bit TXT1.V POLARITY. |

|

|

|

|

|

|

|||

VSSP |

38 |

12, 60 |

− |

periphery ground |

|||

VDDC |

39 |

63 |

− |

+3.3 V core power supply |

|||

OSCGND |

40 |

69 |

− |

crystal oscillator ground |

|||

|

|

|

|

|

|||

XTALIN |

41 |

70 |

I |

12 MHz crystal oscillator input |

|||

|

|

|

|

|

|||

XTALOUT |

42 |

71 |

O |

12 MHz crystal oscillator output |

|||

|

|

|

|

|

|||

RESET |

43 |

73 |

I |

If the reset input is HIGH for at least 2 machine |

|||

|

|

|

|

|

|

cycles (24 oscillator periods) while the oscillator is |

|

|

|

|

|

|

|

running, the device is reset; this pin should be |

|

|

|

|

|

|

|

connected to VDDP via a capacitor. |

|

VDDP |

44 |

75 |

− |

+3.3 V periphery power supply |

|||

P1.0/INT1 |

45 |

76 |

I/O |

Port 1. 8-bit programmable bidirectional port with |

|||

|

|

|

|

|

|

alternative functions. |

|

P1.1/T0 |

46 |

78 |

I/O |

||||

|

|||||||

|

|

|

|

P1.0/INT1 is external interrupt 1 which can be |

|||

P1.2/INT0 |

47 |

79 |

I/O |

||||

|

|

|

|

|

|

triggered on the rising and falling edge of the pulse. |

|

P1.3/T1 |

48 |

80 |

I/O |

||||

P1.1/T0 is the Counter/Timer 0. P1.2/INT0 is |

|||||||

|

|

|

|

|

|

||

P1.6/SCL0 |

49 |

81 |

I/O |

||||

external interrupt 0. P1.3/T1 is the Counter/Timer 1. |

|||||||

|

|

|

|

|

|

||

P1.7/SDA0 |

50 |

82 |

I/O |

||||

P1.6/SCL0 is the serial clock input for the I2C-bus |

|||||||

P1.4/SCL1 |

51 |

83 |

I/O |

and P1.7/SDA0 is the serial data port for the |

|||

|

|

|

|

|

|

I2C-bus. P1.4/SCL1 is the serial clock input for the |

|

P1.5/SDA1 |

52 |

58 |

I/O |

||||

I2C-bus and P1.5/SDA1 is the serial data port for the |

|||||||

|

|

|

|

|

|

||

|

|

|

|

|

|

I2C-bus. |

|

VPE-2 |

− |

62 |

I |

OTP programming voltage |

|||

|

|

|

|

|

|||

n.c. |

− |

3, 7 to 10,14, 15, 19 to 21, |

− |

not connected |

|||

|

|

|

|

23, 26, 27, 33, 36 to 40, |

|

|

|

|

|

|

|

49 to 51, 56 to 58, 61, |

|

|

|

|

|

|

|

64 to 68, 72, 74, 77, |

|

|

|

|

|

|

|

85 to 92, 99 |

|

|

|

|

|

|

|

|

|

|

|

1999 Aug 02 |

9 |

Philips Semiconductors |

Preliminary specification |

|

|

Enhanced TV microcontrollers with

SAA55xx

On-Screen Display (OSD)

7 MICROCONTROLLER

The functionality of the microcontroller used on this device is described here with reference to the industry standard 80C51 microcontroller. A full description of its functionality can be found in “Handbook IC20, 80C51-Based 8-bit

Microcontrollers”.

7.1Microcontroller features

∙80C51 microcontroller core standard instruction set and timing

∙1 μs machine cycle

∙Maximum 128K × 8-bit Program ROM

∙Maximum of 12K × 8-bit Auxiliary RAM

∙Interrupt Controller for individual enable/disable with two level priority

∙Two 16-bit Timer/Counter registers

∙Watchdog Timer

∙Auxiliary RAM page pointer

∙16-bit Data pointer

∙Idle and Power-down mode

∙29 general I/O lines

∙Eight 6-bit Pulse Width Modulator (PWM) outputs for control of TV analog signals

∙One 14-bit PWM for Voltage Synthesis Tuner (VST) control

∙8-bit ADC with 4 multiplexed inputs

∙2 high current outputs for directly driving LEDs etc.

∙I2C byte level bus interface with dual ports.

Table 2 ROM bank selection

ROMBK1 |

ROMBK0 |

0 TO 32-kbyte |

32 TO 64-kbyte |

|

|

|

|

0 |

0 |

common |

Bank 0 |

|

|

|

|

0 |

1 |

common |

Bank 1 |

|

|

|

|

1 |

0 |

common |

Bank 2 |

|

|

|

|

1 |

1 |

reserved |

reserved |

|

|

|

|

8.2Security bits - program and verify

SAA55xx devices have a set of security bits allied with each section of the device, i.e. Program ROM, Character ROM and Packet 26 ROM. The security bits are used to prevent the ROM from being overwritten once programmed, and also the contents being verified once programmed. The security bits are one-time programmable and cannot be erased.

The SAA55xx memory and security bits are structured as shown in Fig.5. The SAA55xx security bits are set as shown in Fig.6 for production programmed devices and are set as shown in Fig.7 for production blank devices.

8.3RAM organisation

The internal Data RAM is organised into two areas, Data memory and Special Function Registers (SFRs) as shown in Fig.8.

8.4Data memory

The Data memory is 256 × 8 bits and occupies the address range 00H to FFH when using indirect addressing and 00H to 7FH when using direct addressing. The SFRs occupy the address range 80H to FFH and are accessible using direct addressing only.

8 MEMORY ORGANIZATION

The device has the capability of a maximum of 128-kbyte Program ROM and 12-kbyte Data RAM internally.

The lower 128 bytes of Data memory are mapped as shown in Fig.9. The lowest 24 bytes are grouped into

4 banks of 8 registers, the next 16 bytes above the register banks form a block of bit addressable memory space.

8.1ROM bank switching

The 64-kbyte device has a continuous address space from 0 to 64 kbytes. The 128-kbyte memory is arranged in four banks of 32 kbytes. One of the 32-kbyte banks is common and is always addressable. The other three banks

(Bank 0, Bank 1 and Bank 2) can be accessed by selecting the right bank via the SFR ROMBK bits; see Table 2.

The ROM bank switching is handled and supported by the compiler and linker development tools.

The upper 128 bytes is not allocated for any special area or functions.

Table 3 Bank selection

RS1 |

RS0 |

BANK |

|

|

|

0 |

0 |

Bank 0 |

|

|

|

0 |

1 |

Bank 1 |

|

|

|

1 |

0 |

Bank 2 |

|

|

|

1 |

1 |

Bank 3 |

|

|

|

1999 Aug 02 |

10 |

Philips Semiconductors |

Preliminary specification |

|

|

Enhanced TV microcontrollers with

SAA55xx

On-Screen Display (OSD)

FFFFH |

|

FFFFH |

|

FFFFH |

BANK 0 |

|

BANK 1 |

|

BANK 2 |

(32-KBYTE) |

|

(32-KBYTE) |

|

(32-KBYTE) |

8000H |

|

8000H |

|

8000H |

|

|

|

|

|

7FFFH

COMMON (32-KBYTE)

0000H

MBK952

Fig.4 ROM bank switching memory map.

MEMORY

PROGRAM ROM

USER ROM (128K x 8-BIT)

CHARACTER ROM

USER ROM (9K x 12-BIT)

PACKET 26 ROM

USER ROM (4K x 8-BIT)

SECURITY BITS INTERACTION

USER ROM PROGRAMMING |

VERIFY |

(ENABLE/DISABLE) |

(ENABLE/DISABLE) |

|

|

|

|

USER ROM PROGRAMMING |

VERIFY |

(ENABLE/DISABLE) |

(ENABLE/DISABLE) |

|

|

|

|

USER ROM PROGRAMMING |

VERIFY |

(ENABLE/DISABLE) |

(ENABLE/DISABLE) |

|

|

|

|

MBK953

Fig.5 |

Memory and security bit structures. |

|

|

1999 Aug 02 |

11 |

Philips Semiconductors |

Preliminary specification |

|

|

Enhanced TV microcontrollers with

SAA55xx

On-Screen Display (OSD)

|

MEMORY |

|

|

|

SECURITY BITS SET |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

USER ROM PROGRAMMING |

VERIFY |

|

|

|

|

|

|

(ENABLE/DISABLE) |

(ENABLE/DISABLE) |

|

|

|

|

|

|

|

|

|

|

PROGRAM ROM |

|

|

|

DISABLED |

ENABLED |

|

|

|

|

|

|

|

||

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CHARACTER ROM |

|

|

|

DISABLED |

ENABLED |

|

|

|

|

|

|

|

||

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PACKET 26 ROM |

|

|

|

DISABLED |

ENABLED |

|

|

|

|

|

|

|

||

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MBK954 |

|

|

Fig.6 |

Security bits for production devices. |

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MEMORY |

|

|

|

SECURITY BITS SET |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

USER ROM PROGRAMMING |

VERIFY |

|

|

|

|

|

|

(ENABLE/DISABLE) |

(ENABLE/DISABLE) |

|

|

|

|

|

|

|

|

|

|

PROGRAM ROM |

|

|

|

ENABLED |

ENABLED |

|

|

|

|

|

|

|

||

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CHARACTER ROM |

|

|

|

ENABLED |

ENABLED |

|

|

|

|

|

|

|

||

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PACKET 26 ROM |

|

|

|

ENABLED |

ENABLED |

|

|

|

|

|

|

|

||

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MBK955 |

|

Fig.7 Security bits for production blank devices.

1999 Aug 02 |

12 |

Philips Semiconductors |

Preliminary specification |

|

|

Enhanced TV microcontrollers with

SAA55xx

On-Screen Display (OSD)

|

DATA |

SPECIAL |

||

|

FUNCTION |

|

||

|

MEMORY |

|

||

|

REGISTERS |

|

||

|

|

|

||

FFH |

|

|

|

|

|

|

|

||

|

|

|

||

|

accessible |

accessible |

||

upper 128 bytes |

by indirect |

by direct |

||

addressing |

addressing |

|||

|

||||

|

only |

only |

||

80H |

|

|

|

|

7FH |

|

|

|

|

|

|

|

||

|

accessible |

|

|

|

lower 128 bytes |

by direct |

|

|

|

and indirect |

|

|

||

|

|

|

||

|

addressing |

|

|

|

00H |

|

MBK956 |

||

|

|

|||

Fig.8 Internal Data memory.

7FH

|

|

30H |

|

|

|

2FH |

|

|

|

|

bit-addressable space |

|

|

|

(bit addresses 00H to 7FH) |

|

|

20H |

|

R7 |

1FH |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R0 |

18H |

|

|

R7 |

17H |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R0 |

10H |

4 banks of 8 registers |

|

R7 |

0FH |

(R0 to R7) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R0 |

08H |

|

|

R7 |

07H |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R0 |

0 |

MGM677 |

|

Fig.9 Lower 128 bytes of internal RAM.

1999 Aug 02 |

13 |

02 Aug 1999

14

_

8.5SFR memory

The Special Function Register (SFR) space is used for port latches, timer, peripheral control, acquisition control, display control, etc. These registers can only be accessed by direct addressing. Sixteen of the addresses in the SFR space are both bit and byte addressable. The bit addressable SFRs are those whose address ends in 0H or 8H. A summary of the SFR map in address order is shown in Table 4.

A description of each of the SFR bits is shown in Table 5 which presents the SFRs in alphabetical order.

Table 4 SFR memory map

ADD |

R/W |

NAME |

7 |

6 |

|

5 |

4 |

3 |

2 |

|

1 |

0 |

RESET |

||

|

|

|

|

|

|

|

|

|

|

|

|

||||

80H |

R/W |

P0 |

P07 |

P06 |

P05 |

P04 |

P03 |

P02 |

P01 |

P00 |

FFH |

||||

|

|

|

|

|

|

|

|

|

|

|

|

||||

81H |

R/W |

SP |

SP7 |

SP6 |

SP5 |

SP4 |

SP3 |

SP2 |

SP1 |

SP0 |

07H |

||||

|

|

|

|

|

|

|

|

|

|

|

|

||||

82H |

R/W |

DPL |

DPL7 |

DPL6 |

DPL5 |

DPL4 |

DPL3 |

DPL2 |

DPL1 |

DPL0 |

00H |

||||

|

|

|

|

|

|

|

|

|

|

|

|

||||

83H |

R/W |

DPH |

DPH7 |

DPH6 |

DPH5 |

DPH4 |

DPH3 |

DPH2 |

DPH1 |

DPH0 |

00H |

||||

|

|

|

|

|

|

|

|

|

|

|

|

||||

87H |

R/W |

PCON |

0 |

ARD |

RFI |

WLE |

GF1 |

GF0 |

PD |

IDL |

00H |

||||

|

|

|

|

|

|

|

|

|

|

|

|

||||

88H |

R/W |

TCON |

TF1 |

TR1 |

TF0 |

TR0 |

IE1 |

IT1 |

IE0 |

IT0 |

00H |

||||

89H |

R/W |

TMOD |

GATE |

|

|

|

M1 |

M0 |

GATE |

|

|

|

M1 |

M0 |

00H |

C/T |

|

C/T |

|||||||||||||

8AH |

R/W |

TL0 |

TL07 |

TL06 |

TL05 |

TL04 |

TL03 |

TL02 |

TL01 |

TL00 |

00H |

||||

|

|

|

|

|

|

|

|

|

|

|

|

||||

8BH |

R/W |

TL1 |

TL17 |

TL16 |

TL15 |

TL14 |

TL13 |

TL12 |

TL11 |

TL10 |

00H |

||||

|

|

|

|

|

|

|

|

|

|

|

|

||||

8CH |

R/W |

TH0 |

TH07 |

TH06 |

TH05 |

TH04 |

TH03 |

TH02 |

TH01 |

TH00 |

00H |

||||

|

|

|

|

|

|

|

|

|

|

|

|

||||

8DH |

R/W |

TH1 |

TH17 |

TH16 |

TH15 |

TH14 |

TH13 |

TH12 |

TH11 |

TH10 |

00H |

||||

|

|

|

|

|

|

|

|

|

|

|

|

||||

90H |

R/W |

P1 |

P17 |

P16 |

P15 |

P14 |

P13 |

P12 |

P11 |

P10 |

FFH |

||||

|

|

|

|

|

|

|

|

|

|

|

|

||||

96H |

R/W |

P0CFGA |

P0CFGA7 |

P0CFGA6 |

P0CFGA5 |

P0CFGA4 |

P0CFGA3 |

P0CFGA2 |

P0CFGA1 |

P0CFGA0 |

FFH |

||||

|

|

|

|

|

|

|

|

|

|

|

|

||||

97H |

R/W |

P0CFGB |

P0CFGB7 |

P0CFGB6 |

P0CFGB5 |

P0CFGB4 |

P0CFGB3 |

P0CFGB2 |

P0CFGB1 |

P0CFGB0 |

00H |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

98H |

R/W |

SADB |

0 |

0 |

|

0 |

DC_COMP |

SAD3 |

SAD2 |

SAD1 |

SAD0 |

00H |

|||

|

|

|

|

|

|

|

|

|

|

|

|

||||

9EH |

R/W |

P1CFGA |

P1CFGA7 |

P1CFGA6 |

P1CFGA5 |

P1CFGA4 |

P1CFGA3 |

P1CFGA2 |

P1CFGA1 |

P1CFGA0 |

FFH |

||||

9FH |

R/W |

P1CFGB |

P1CFGB7 |

P1CFGB6 |

P1CFGB5 |

P1CFGB4 |

P1CFGB3 |

P1CFGB2 |

P1CFGB1 |

P1CFGB0 |

00H |

||||

|

|

|

|

|

|

|

|

|

|

|

|

||||

A0H |

R/W |

P2 |

P27 |

P26 |

P25 |

P24 |

P23 |

P22 |

P21 |

P20 |

FFH |

||||

|

|

|

|

|

|

|

|

|

|

|

|

||||

A6H |

R/W |

P2CFGA |

P2CFGA7 |

P2CFGA6 |

P2CFGA5 |

P2CFGA4 |

P2CFGA3 |

P2CFGA2 |

P2CFGA1 |

P2CFGA0 |

FFH |

||||

|

|

|

|

|

|

|

|

|

|

|

|

||||

A7H |

R/W |

P2CFGB |

P2CFGB7 |

P2CFGB6 |

P2CFGB5 |

P2CFGB4 |

P2CFGB3 |

P2CFGB2 |

P2CFGB1 |

P2CFGB0 |

00H |

||||

|

|

|

|

|

|

|

|

|

|

|

|

||||

A8H |

R/W |

IE |

EA |

EBUSY |

ES2 |

ECC |

ET1 |

EX1 |

ET0 |

EX0 |

00H |

||||

|

|

|

|

|

|

|

|

|

|

|

|

||||

B0H |

R/W |

P3 |

P37 |

P36 |

P35 |

P34 |

P33 |

P32 |

P31 |

P30 |

FFH |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

with microcontrollers TV Enhanced

(OSD) Display Screen-On

SAA55xx

Semiconductors Philips

specification Preliminary

|

_ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1999 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ADD |

R/W |

NAME |

7 |

6 |

5 |

|

4 |

|

3 |

2 |

1 |

0 |

RESET |

||||

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

Aug |

B2H |

R/W |

TXT18 |

NOT3 |

NOT2 |

|

NOT1 |

|

NOT0 |

0 |

0 |

BS1 |

BS0 |

00H |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

B3H |

R/W |

TXT19 |

TEN |

TC2 |

|

TC1 |

|

TC0 |

0 |

0 |

TS1 |

TS0 |

00H |

||||

02 |

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

B4H |

R/W |

TXT20 |

DRCS |

OSD |

0 |

|

0 |

|

OSD LANG |

OSD LAN2 |

OSD LAN1 |

OSD LAN0 |

00H |

||||

|

|

|

|||||||||||||||

|

|

|

|

ENABLE |

PLANES |

|

|

|

|

|

|

|

ENABLE |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

B5H |

R/W |

TXT21 |

DISP |

DISP |

CHAR SIZE1 |

|

CHAR |

I2C PORT 1 |

CC ON |

I2C PORT 0 |

CC/TXT |

02H |

||||

|

|

|

|

LINES1 |

LINES0 |

|

|

|

|

|

SIZE0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

B6H |

R |

TXT22 |

GPF7 |

GPF6 |

|

GPF5 |

|

GPF4 |

GPF3 |

GPF2 |

GPF1 |

1 |

XXH |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

B7H |

R/W |

CCLIN |

0 |

0 |

0 |

|

|

CS4 |

CS3 |

CS2 |

CS1 |

CS0 |

15H |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

B8H |

R/W |

IP |

0 |

PBUSY |

|

PES2 |

|

PCC |

PT1 |

PX1 |

PT0 |

PX0 |

00H |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

B9H |

R/W |

TXT17 |

0 |

FORCE |

|

FORCE |

|

FORCE |

FORCE |

SCREEN |

SCREEN |

SCREEN |

00H |

|||

|

|

|

|

|

ACQ1 |

|

ACQ0 |

|

DISP1 |

DISP0 |

COL2 |

COL1 |

COL0 |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

BAH |

R |

WSS1 |

0 |

0 |

0 |

|

WSS<3:0> |

WSS3 |

WSS2 |

WSS1 |

WSS0 |

00H |

||||

|

|

|

|

|

|

|

|

|

|

ERROR |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

BBH |

R |

WSS2 |

0 |

0 |

0 |

|

WSS<7:4> |

WSS7 |

WSS6 |

WSS5 |

WSS4 |

00H |

||||

|

|

|

|

|

|

|

|

|

|

ERROR |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

BCH |

R |

WSS3 |

WSS<13:11> |

WSS13 |

|

WSS12 |

|

WSS11 |

WSS<10:8> |

WSS10 |

WSS9 |

WSS8 |

00H |

|||

15 |

|

|

|

ERROR |

|

|

|

|

|

|

|

|

ERROR |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

BEH |

R/W |

P3CFGA |

1 |

1 |

1 |

|

P3CFGA4 |

P3CFGA3 |

P3CFGA2 |

P3CFGA1 |

P3CFGA0 |

FFH |

||||

|

BFH |

R/W |

P3CFGB |

0 |

0 |

0 |

|

P3CFGB4 |

P3CFGB3 |

P3CFGB2 |

P3CFGB1 |

P3CFGB0 |

00H |

||||

|

C0H |

R/W |

TXT0 |

X24 POSN |

DISPLAY |

|

AUTO |

DISABLE |

DISPLAY |

DISABLE |

VPS ON |

INV ON |

00H |

||||

|

|

|

|

|

X24 |

|

FRAME |

HEADER |

STATUS |

FRAME |

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

ROLL |

ROW ONLY |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

C1H |

R/W |

TXT1 |

EXT PKT |

8-BIT |

|

ACQ OFF |

X26 OFF |

FULL |

FIELD |

H |

V |

00H |

||||

|

|

|

|

OFF |

|

|

|

|

|

|

|

|

FIELD |

POLARITY |

POLARITY |

POLARITY |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

C2H |

R/W |

TXT2 |

ACQ BANK |

REQ3 |

|

REQ2 |

|

REQ1 |

REQ0 |

SC2 |

SC1 |

SC0 |

00H |

|||

|

C3H |

W |

TXT3 |

− |

− |

|

− |

|

PRD4 |

PRD3 |

PRD2 |

PRD1 |

PRD0 |

00H |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C4H |

R/W |

TXT4 |

OSD BANK |

QUAD |

|

|

|

|

DISABLE |

B MESH |

C MESH |

TRANS |

SHADOW |

00H |

||

|

EAST/WEST |

|

|||||||||||||||

|

|

|

|

ENABLE |

WIDTH |

|

|

|

|

DOUBLE |

ENABLE |

ENABLE |

ENABLE |

ENABLE |

|

||

|

|

|

|

|

ENABLE |

|

|

|

|

HEIGHT |

|

|

|

|

|

||

|

C5H |

R/W |

TXT5 |

BKGND OUT |

BKGND IN |

|

|

OUT |

|

|

IN |

TEXT OUT |

TEXT IN |

PICTURE |

PICTURE |

03H |

|

|

COR |

COR |

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ON OUT |

ON IN |

|

with microcontrollers TV Enhanced

(OSD) Display Screen-On

SAA55xx

Semiconductors Philips

specification Preliminary

|

_ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1999 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ADD |

R/W |

NAME |

7 |

|

6 |

|

|

5 |

4 |

|

|

3 |

2 |

1 |

0 |

|

RESET |

|||||||||

|

|

|

|

|

|

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

C6H |

R/W |

TXT6 |

BKGND OUT |

BKGND IN |

|

|

OUT |

|

|

|

IN |

TEXT OUT |

TEXT IN |

PICTURE |

PICTURE |

03H |

|||||||||

Aug |

COR |

COR |

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ON OUT |

|

ON IN |

|

||

02 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C7H |

R/W |

TXT7 |

STATUS |

|

CURSOR |

|

REVEAL |

BOTTOM |

DOUBLE |

BOX ON 24 |

BOX ON |

BOX ON 0 |

00H |

|||||||||||||

|

|

|

||||||||||||||||||||||||

|

|

|

|

ROW TOP |

|

|

ON |

|

|

|

|

|

|

|

HEIGHT |

|

1-23 |

|

|

|

|

|||||

|

|

|

|

|

|

|

|

/TOP |

|

|

|

|

|

|||||||||||||

|

C8H |

R/W |

TXT8 |

(reserved) |

|

|

|

|

|

|

(reserved) |

DISABLE |

PKT 26 |

WSS |

WSS ON |

CVBS1/ |

00H |

|||||||||

|

FLICKER |

|

||||||||||||||||||||||||

|

|

|

|

0 |

|

|

STOP ON |

|

0 |

SPANISH |

RECEIVED |

RECEIVED |

|

|

CVBS0 |

|

|

|||||||||

|

C9H |

R/W |

TXT9 |

CURSOR |

|

|

CLEAR |

|

A0 |

|

|

R4 |

R3 |

R2 |

R1 |

|

R0 |

00H |

||||||||

|

|

|

|

FREEZE |

|

MEMORY |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

CAH |

R/W |

TXT10 |

0 |

|

0 |

|

|

|

C5 |

|

|

C4 |

C3 |

C2 |

C1 |

|

C0 |

00H |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

CBH |

R/W |

TXT11 |

D7 |

|

|

D6 |

|

D5 |

|

|

D4 |

D3 |

D2 |

D1 |

|

D0 |

00H |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

CCH |

R |

TXT12 |

|

|

|

|

SPANISH |

ROM VER3 |

ROM VER2 |

ROM VER1 |

ROM VER0 |

1 |

|

VIDEO |

XXXX |

||||||||||

|

525/625 |

|

|

|

||||||||||||||||||||||

|

|

|

|

SYNC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SIGNAL |

XX1X |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

QUALITY |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

CDH |

R/W |

TXT14 |

0 |

|

0 |

|

|

0 |

|

|

− |

PAGE3 |

PAGE2 |

PAGE1 |

|

PAGE0 |

00H |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

CEH |

R/W |

TXT15 |

0 |

|

0 |

|

|

0 |

|

|

− |

BLOCK3 |

BLOCK2 |

BLOCK1 |

BLOCK0 |

00H |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

D0H |

R/W |

PSW |

C |

|

|

AC |

|

F0 |

|

RS1 |

RS0 |

OV |

− |

|

P |

00H |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

16 |

D2H |

R/W |

TDACL |

TD7 |

|

|

TD6 |

|

TD5 |

|

TD4 |

TD3 |

TD2 |

TD1 |

|

TD0 |

00H |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D3H |

R/W |

TDACH |

TPWE |

1 |

|

|

|

TD13 |

|

TD12 |

TD11 |

TD10 |

TD9 |

|

TD8 |

40H |

|||||||||

|

D4H |

R/W |

PWM7 |

PW7E |

1 |

|

|

|

PW7V5 |

|

PW7V4 |

PW7V3 |

PW7V2 |

PW7V1 |

PW7V0 |

40H |

||||||||||

|

D5H |

R/W |

PWM0 |

PW0E |

1 |

|

|

|

PW0V5 |

|

PW0V4 |

PW0V3 |

PW0V2 |

PW0V1 |

PW0V0 |

40H |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

D6H |

R/W |

PWM1 |

PW1E |

1 |

|

|

|

PW1V5 |

|

PW1V4 |

PW1V3 |

PW1V2 |

PW1V1 |

PW1V0 |

40H |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

D7H |

R |

CCDAT1 |

CCD17 |

|

|

CCD16 |

|

CCD15 |

|

CCD14 |

CCD13 |

CCD12 |

CCD11 |

|

CCD10 |

00H |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

D8H |

R/W |

S1CON |

CR2 |

|

|

ENSI |

|

STA |

|

STO |

SI |

AA |

CR1 |

|

CR0 |

00H |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

D9H |

R |

S1STA |

STAT4 |

|

|

STAT3 |

|

STAT2 |

|

STAT1 |

STAT0 |

0 |

0 |

0 |

|

F8H |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

DAH |

R/W |

S1DAT |

DAT7 |

|

|

DAT6 |

|

DAT5 |

|

DAT4 |

DAT3 |

DAT2 |

DAT1 |

|

DAT0 |

00H |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

DBH |

R/W |

S1ADR |

ADR6 |

|

|

ADR5 |

|

ADR4 |

|

ADR3 |

ADR2 |

ADR1 |

ADR0 |

|

GC |

00H |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

DCH |

R/W |

PWM3 |

PW3E |

1 |

|

|

|

PW3V5 |

|

PW3V4 |

PW3V3 |

PW3V2 |

PW3V1 |

PW3V0 |

40H |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

DDH |

R/W |

PWM4 |

PW4E |

1 |

|

|

|

PW4V5 |

|

PW4V4 |

PW4V3 |

PW4V2 |

PW4V1 |

PW4V0 |

40H |

||||||||||

|

DEH |

R/W |

PWM5 |

PW5E |

1 |

|

|

|

PW5V5 |

|

PW5V4 |

PW5V3 |

PW5V2 |

PW5V1 |

PW5V0 |

40H |

||||||||||

|

DFH |

R/W |

PWM6 |

PW6E |

1 |

|

|

|

PW6V5 |

|

PW6V4 |

PW6V3 |

PW6V2 |

PW6V1 |

PW6V0 |

40H |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

E0H |

R/W |

ACC |

ACC7 |

|

|

ACC6 |

|

ACC5 |

|

ACC4 |

ACC3 |

ACC2 |

ACC1 |

|

ACC0 |

00H |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

with microcontrollers TV Enhanced

(OSD) Display Screen-On

SAA55xx

Semiconductors Philips

specification Preliminary

|

_ |

|

|

|

|

|

|

|

|

|

|

|

|

1999 |

|

|

|

|

|

|

|

|

|

|

|

|

|

ADD |

R/W |

NAME |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

RESET |

||

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Aug |

E4H |

R/W |

PWM2 |

PW2E |

1 |

PW2V5 |

PW2V4 |

PW2V3 |

PW2V2 |

PW2V1 |

PW2V0 |

40H |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

E7H |

R |

CCDAT2 |

CCD27 |

CCD26 |

CCD25 |

CCD24 |

CCD23 |

CCD22 |

CCD21 |

CCD20 |

00H |

||

02 |

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||

E8H |

R/W |

SAD |

VHI |

CH1 |

CH0 |

ST |

SAD7 |

SAD6 |

SAD5 |

SAD4 |

00H |

||

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

F0H |

R/W |

B |

B7 |

B6 |

B5 |

B4 |

B3 |

B2 |

B1 |

B0 |

00H |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

F7H |

W |

WDTKEY |

WKEY7 |

WKEY6 |

WKEY5 |

WKEY4 |

WKEY3 |

WKEY2 |

WKEY1 |

WKEY0 |

00H |

|

|

F8H |

R/W |

TXT13 |

VPS |

PAGE |

525 |

525 TEXT |

625 TEXT |

PKT 8/30 |

FASTEXT |

0 |

XXXX |

|

|

|

|

|

RECEIVED |

CLEARING |

DISPLAY |

|

|

|

|

|

XXX0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

FAH |

R/W |

XRAMP |

XRAMP7 |

XRAMP6 |

XRAMP5 |

XRAMP4 |

XRAMP3 |

XRAMP2 |

XRAMP1 |

XRAMP0 |

00H |

|

|

FBH |

R/W |

ROMBK |

STANDBY |

0 |

0 |

0 |

0 |

0 |

ROMBK1 |

ROMBK0 |

00H |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

FFH |

R/W |

WDT |

WDV7 |

WDV6 |

WDV5 |

WDV4 |

WDV3 |