Philips SAA5261PS-017, SAA5261PS-101, SAA5261PS-102, SAA5261PS-103, SAA5261PS-104 Datasheet

...

INTEGRATED CIRCUITS

DATA SHEET

SAA5261; SAA5262; SAA5263

10-page intelligent teletext decoders

Product specification |

|

1998 Apr 22 |

|||||

File under Integrated Circuits, IC02 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Philips Semiconductors |

Product specification |

|

|

10-page intelligent teletext decoders |

SAA5261; SAA5262; SAA5263 |

|

|

|

|

FEATURES

SAA5261, SAA5262 and SAA5263

∙Complete 625-line teletext decoder in a single integrated circuit thereby reducing printed-circuit board area and cost

∙Automatic detection of transmitted pages so that only existing pages will be selected by page-up and page-down once inventory validated

∙Automatic detection of transmitted Fastext links or service information (packet 8/30)

∙On-screen display for user interface (menus, etc.) using teletext and dedicated menu icons

∙Video Programming System (VPS) decoding

∙Wide Screen Signalling (WSS) decoding

∙8-page Fastext decoder

∙6-page TOP decoder in addition to capture of Basic TOP Table (BTT) and 3 Additional Information Table (AIT) pages

∙4-page user defined list mode

∙Yugoslavian, Cyrillic, Greek/Turkish, Thai, Arabic/Hebrew, Pan-European and Arabic/English/French language coverage

∙High level command interface via I2C-bus giving easy control from a low software overhead

∙High level command interface is backward compatible to SAFARI interface

∙625 and 525 line display

∙RGB interface to standard colour decoder ICs, push-pull output drive

∙Versatile 8-bit open-drain I/O expander

∙Single 12 MHz crystal oscillator for reduced cost

∙+5 V power supply.

SAA5262 and SAA5263

∙Automatic Channel Installation (ACI)

∙Enhanced SAFARI interface providing additional commands.

SAA5263

∙ Electronic Programme Guide (EPG) feature.

GENERAL DESCRIPTION

The SAA526xPS ICs are single-chip 10-page 625-line World System Teletext (WST) decoders with a high level command interface, SAFARI compatible.

It has been designed so that the overall system cost is kept to a minimum. This has been achieved through the capability of the device to be driven from a single +5 V power supply, low cost 12 MHz crystal oscillator and the high level command interface, which offers the benefit of low software overhead in the TV microcontroller.

The SAA526xPS offers automatic detection of Fastext or TOP transmissions. The device also incorporates a facility to detect the pages in the transmission, which allows only transmitted pages to be selected by page-up and page-down.

SAA5262 and SAA5263 provide Automatic Channel Installation (ACI) information.

SAA5263 provides access to Electronic Programme Guide (EPG) information.

1998 Apr 22 |

2 |

Philips Semiconductors |

|

|

Product specification |

||

|

|

|

|

|

|

10-page intelligent teletext decoders |

SAA5261; SAA5262; SAA5263 |

||||

|

|

|

|

|

|

ORDERING INFORMATION |

|

|

|

|

|

|

|

|

|

|

|

TYPE NUMBER |

|

|

PACKAGE |

|

|

|

|

|

|

|

|

NAME |

|

DESCRIPTION |

|

VERSION |

|

|

|

|

|||

|

|

|

|

|

|

SAA5261PS |

SDIP52 |

plastic shrink dual in-line package; 52 leads (600 mil) |

|

SOT247-1 |

|

|

|

|

|

|

|

SAA5262PS |

SDIP52 |

plastic shrink dual in-line package; 52 leads (600 mil) |

|

SOT247-1 |

|

|

|

|

|

|

|

SAA5263PS |

SDIP52 |

plastic shrink dual in-line package; 52 leads (600 mil) |

|

SOT247-1 |

|

|

|

|

|

|

|

QUICK REFERENCE DATA

SYMBOL |

PARAMETER |

MIN. |

TYP. |

MAX. |

UNIT |

|

|

|

|

|

|

VDDD |

digital supply voltage |

4.5 |

5.0 |

5.5 |

V |

IDDD(M) |

microcontroller supply current |

− |

20 |

35 |

mA |

IDDA |

analog supply current |

− |

35 |

50 |

mA |

IDDD(T) |

teletext supply current |

− |

50 |

80 |

mA |

fxtal |

crystal frequency |

− |

12 |

− |

MHz |

Tamb |

operating ambient temperature |

−20 |

− |

+70 |

°C |

1998 Apr 22 |

3 |

Philips Semiconductors |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Product specification |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

10-page intelligent teletext decoders |

|

|

SAA5261; SAA5262; SAA5263 |

|||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

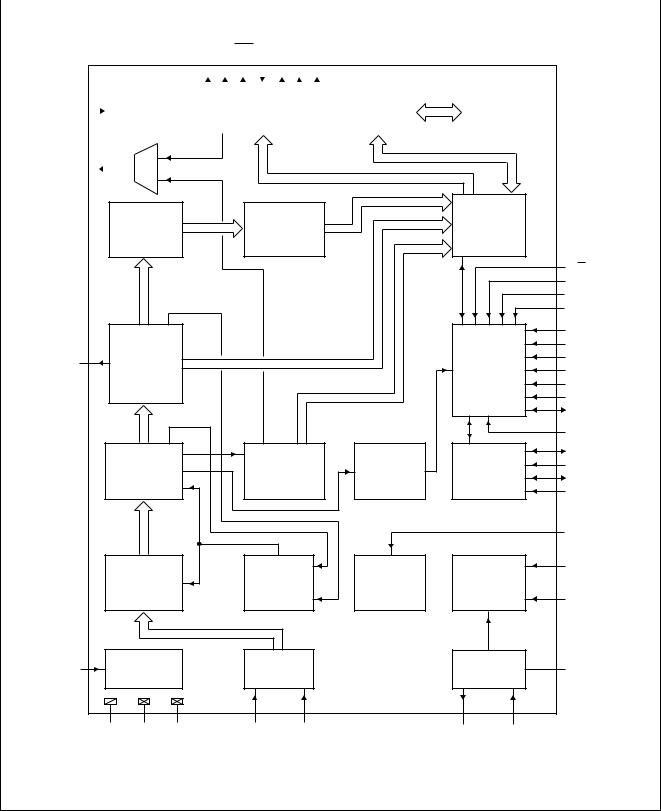

BLOCK DIAGRAM |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

PON |

RGBREF |

G |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

VDS |

|

COR |

|

B |

|

|

R |

|

|

VDDA |

VDDD(T) |

VDDD(M) |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

35 |

|

30 |

29 |

|

31 |

|

32 |

|

33 |

|

34 |

|

38 |

|

39 |

|

44 |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

43 |

POWER-ON |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DRAM |

|

|

10 k × 8 |

|

|

|

|||||

|

|

|

|

|

DISPLAY |

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

RESET |

|

RESET |

|

|

|

|

|

|

|

|

|

|

|

REFRESH |

|

|

DRAM |

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AND TIMING |

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

9 to 12 |

|||

27 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

res |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

FRAME |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

24 TO 18 |

|

PACKET 26 |

|

MEMORY |

|

|

|||

|

HAMMING |

|

PROCESSING |

|

INTERFACE |

|

|

|||

|

DECODER |

|

ENGINE |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

52 |

E/W |

|

|

|

|

|

|

|

|

|

20 |

|

|

|

|

|

|

|

|

|

|

PDI |

|

|

|

|

|

|

|

|

|

|

16 |

|

|

|

|

|

|

|

|

|

|

SA |

|

|

|

|

|

|

|

|

|

|

48 |

|

|

|

|

|

|

SAA526xPS |

|

|

|

DISLCBD |

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

17 |

FP |

|

|

|

|

|

|

|

|

|

47 |

|

|

TELETEXT |

|

|

|

|

|

|

DIS8/30 |

||

21 |

|

|

|

|

|

|

18 |

|||

|

|

|

|

|

|

HSMODE |

||||

ACQUISITION |

|

|

|

|

|

|

||||

PL |

|

|

|

|

SYSTEM |

46 |

||||

|

AND |

|

|

|

|

DISDSR |

||||

|

|

|

|

|

|

CONTROLLER |

19 |

|||

|

DECODING |

|

|

|

|

VSMODE |

||||

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

45 |

|||

|

|

|

|

|

|

|

|

|

PUINL |

|

|

|

|

|

|

|

|

|

|

1-8 |

|

|

|

|

|

|

|

|

|

|

V0-V7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

51 |

ME8/30T |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VPS |

WSS |

|

|

15 |

SDA1 |

|

SERIAL-TO- |

|

|

|

|

14 |

||||

|

|

ACQUISITION |

ACQUISITION |

I2C-BUS |

SCL1 |

|||||

|

PARALLEL |

|

50 |

|||||||

|

|

|

AND |

AND |

INTERFACE |

SDA2 |

||||

|

CONVERTER |

|

|

49 |

||||||

|

|

DECODING |

DECODING |

|

|

SCL2 |

||||

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

25 |

BLACK |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TELETEXT |

|

|

|

36 |

HSYNC |

|

|

DATA SLICER |

|

INPUT CLAMP |

DISPLAY |

|

|||||

|

|

|

OR |

|

|

|||||

|

AND CLOCK |

|

|

AND SYNC |

CLOCK |

|

|

|||

|

|

VPS |

37 |

|

||||||

|

REGENERATOR |

|

SEPARATOR |

GENERATOR |

|

|||||

|

|

CONTROL |

VSYNC |

|||||||

|

|

|

|

|

|

|

|

|||

26 |

ANALOG- |

|

ANALOG- |

|

12 MHz |

40 |

OSCGND |

|||

Iref |

REFERENCE |

|

TO-DIGITAL |

|

CLOCK |

|

||||

|

GENERATOR |

|

CONVERTER |

|

GENERATOR |

|

|

|||

|

22 |

13 |

28 |

23 |

24 |

|

42 |

41 |

|

MGL418 |

|

|

|

|

|

|

|

|

|

|

|

VSSA |

VSSD1 VSSD2 |

CVBS1 |

CVBS2 |

|

XTALO |

XTALI |

|

|

||

Fig.1 Block diagram.

1998 Apr 22 |

4 |

Philips Semiconductors |

|

Product specification |

|||

|

|

|

|

|

|

|

10-page intelligent teletext decoders |

SAA5261; SAA5262; SAA5263 |

|||

|

|

|

|

|

|

PINNING |

|

|

|

||

|

|

|

|

|

|

|

SYMBOL |

PIN |

|

DESCRIPTION |

|

|

|

|

|

||

|

V0 |

1 |

versatile open-drain input/output bit 0 (should be tied HIGH) |

||

|

|

|

|

||

|

V1 |

2 |

versatile open-drain input/output bit 1 (should be tied HIGH) |

||

|

|

|

|

||

|

V2 |

3 |

versatile open-drain input/output bit 2 (should be tied HIGH) |

||

|

|

|

|

||

|

V3 |

4 |

versatile open-drain input/output bit 3 (should be tied HIGH) |

||

|

|

|

|

||

|

V4 |

5 |

versatile open-drain input/output bit 4 (should be tied HIGH) |

||

|

|

|

|

||

|

V5 |

6 |

versatile open-drain input/output bit 5 (should be tied HIGH) |

||

|

|

|

|

||

|

V6 |

7 |

versatile open-drain input/output bit 6 (should be tied HIGH) |

||

|

|

|

|

||

|

V7 |

8 |

versatile open-drain input/output bit 7 (should be tied HIGH) |

||

|

|

|

|

|

|

|

res |

9 |

reserved |

|

|

|

|

|

|

|

|

|

res |

10 |

reserved |

|

|

|

|

|

|

|

|

|

res |

11 |

reserved |

|

|

|

|

|

|

|

|

|

res |

12 |

reserved |

|

|

|

|

|

|

|

|

|

VSSD1 |

13 |

digital ground 1 |

|

|

|

SCLK1 |

14 |

serial clock input 1 (NVRAM) |

|

|

|

|

|

|

|

|

|

SDAT1 |

15 |

serial data input/output 1 (NVRAM) |

|

|

|

|

|

|

||

|

SA |

16 |

slave address input: LOW selects 58H; HIGH selects 60H |

||

|

|

|

|

||

|

FP |

17 |

field polarity input: LOW selects first half line; HIGH selects second half line at the start of an |

||

|

|

|

|

even field |

|

|

|

|

|

||

|

HSMODE |

18 |

horizontal sync mode control input: LOW selects HSYNC on rising edge |

||

|

|

|

|

||

|

VSMODE |

19 |

vertical sync mode control input. LOW selects VSYNC on rising edge |

||

|

|

|

|

||

|

PDI |

20 |

power-down imminent input: this input should be pulled LOW to indicate that the system is |

||

|

|

|

|

about to lose power |

|

|

|

|

|

||

|

PL |

21 |

phase-lock output: HIGH indicates that the system is phase-locked to the CVBS input |

||

|

|

|

|

|

|

|

VSSA |

22 |

analog ground |

|

|

|

CVBS1 |

23 |

CVBS input: this signal is applied via a 100 nF capacitor (nominal input 1 V (p-p) |

||

|

|

|

|

||

|

CVBS2 |

24 |

this pin should be connected to ground if unused |

||

|

|

|

|

||

|

BLACK |

25 |

black level input: a 100 nF capacitor should be connected to VSSA |

||

|

Iref |

26 |

reference current input for analog circuits: for correct operation a 27 kΩ resistor should be |

||

|

|

|

|

connected to VSSA |

|

|

FRAME |

27 |

Frame output for use in non-interlaced displays: during teletext off, teletext mixed with TV |

||

|

|

|

|

picture and subtitles this pin is inactive. In full teletext mode this pin provides a 25 Hz square |

|

|

|

|

|

wave. FRAME = 1 = odd, FRAME = 0 = even. |

|

|

|

|

|

|

|

|

VSSD2 |

28 |

digital ground 2 |

|

|

|

|

|

29 |

contrast reduction: active LOW output which allows selective contrast reduction of the |

|

|

COR |

|

|||

|

|

|

|

television picture to enhance a mixed mode display |

|

|

|

|

|

||

|

PON |

30 |

picture on output: HIGH indicates that a TV picture is present and that the SAA526xPS is in |

||

|

|

|

|

TV mode, mix mode, subtitle mode or news flash mode |

|

|

|

|

|

||

|

RGBREF |

31 |

RGB reference input: drive level reference for RGB outputs |

||

|

|

|

|

||

|

B |

32 |

blue dot rate character output of the blue colour information: the high voltage level is defined |

||

|

|

|

|

by the RGBREF pin (can source 4 mA) |

|

|

|

|

|

|

|

1998 Apr 22 |

5 |

Philips Semiconductors |

|

Product specification |

|||

|

|

|

|

|

|

10-page intelligent teletext decoders |

SAA5261; SAA5262; SAA5263 |

||||

|

|

|

|

|

|

|

|

|

|

||

SYMBOL |

PIN |

|

DESCRIPTION |

||

|

|

|

|||

G |

33 |

green dot rate character output of the green colour information: the high voltage level is |

|||

|

|

|

|

defined by the RGBREF pin (can source 4 mA) |

|

|

|

|

|||

R |

34 |

red dot rate character output of the red colour information: the high voltage level is defined by |

|||

|

|

|

|

the RGBREF pin (can source 4 mA) |

|

|

|

|

|||

VDS |

35 |

push-pull output for blanking the TV picture |

|||

|

|

|

|||

HSYNC |

36 |

horizontal sync input: the polarity of this pulse is set by input HSMODE |

|||

|

|

|

|||

VSYNC |

37 |

vertical sync input: the polarity of this pulse is set by input VSMODE |

|||

|

|

|

|

||

VDDA |

38 |

analog supply voltage (+5 V) |

|

||

VDDD(T) |

39 |

digital supply voltage for teletext circuits (+5 V) |

|||

OSCGND |

40 |

ground for crystal oscillator |

|

||

|

|

|

|

||

XTALI |

41 |

12 MHz crystal oscillator input |

|

||

|

|

|

|

||

XTALO |

42 |

12 MHz crystal oscillator output |

|

||

|

|

|

|

||

RESET |

43 |

reset input |

|

||

|

|

|

|||

VDDD(M) |

44 |

digital supply voltage for microcontroller (+5 V) |

|||

PUINL |

45 |

power-up in list mode control input: LOW selects auto TOP/Fastext on power-up; HIGH |

|||

|

|

|

|

selects LIST mode on power-up |

|

|

|

|

|||

DISDSR |

46 |

disable default status row input: LOW enables display of status row |

|||

|

|

|

|||

DIS8/30 |

47 |

disable packet 8/30 display input: LOW enables display of packet 8/30 |

|||

|

|

|

|||

DISLCBD |

48 |

disable Link Control Byte (LCB) decode input: LOW enables decoding of the LCB in Fastext |

|||

|

|

|

|

||

SCLK2 |

49 |

serial clock input (I2C-bus) |

|

||

SDAT2 |

50 |

serial data input/output (I2C-bus) |

|

||

ME8/30T |

51 |

mesh 8/30 and time displays input: HIGH will select a meshed display for the packet 8/30 and |

|||

|

|

|

|

time |

|

|

|

|

|||

|

|

|

52 |

East/West language select input: LOW selects West language |

|

E/W |

|

||||

|

|

|

|

|

|

1998 Apr 22 |

6 |

Philips Semiconductors |

Product specification |

|

|

10-page intelligent teletext decoders |

SAA5261; SAA5262; SAA5263 |

|

|

V0 |

|

|

|

|

|

|

|

|

1 |

|

52 |

E/W |

|||||

V1 |

|

|

|

|

|

|

|

|

2 |

|

51 |

ME8/30T |

|||||

|

|

|

|

|

|

|

|

|

V2 |

3 |

|

50 |

SDA2 |

||||

|

|

|

|

|

|

|

|

|

V3 |

4 |

|

49 |

SCL2 |

||||

|

|

|

|

|

|

|

|

|

V4 |

5 |

|

48 |

DISLCBD |

||||

|

|

|

|

|

|

|

|

|

V5 |

6 |

|

47 |

DIS8/30 |

||||

|

|

|

|

|

|

|

|

|

V6 |

7 |

|

46 |

DISDSR |

||||

|

|

|

|

|

|

|

|

|

V7 |

8 |

|

45 |

PUINL |

||||

|

|

|

|

|

|

|

|

|

res |

9 |

|

44 |

VDDD(M) |

||||

|

|

|

|

|

|

|

|

|

res |

10 |

|

43 |

RESET |

||||

|

|

|

|

|

|

|

|

|

res |

11 |

|

42 |

XTALO |

||||

|

|

|

|

|

|

|

|

|

res |

12 |

|

41 |

XTALI |

||||

|

|

|

|

|

|

|

|

|

VSSD1 |

13 |

SAA526xPS |

40 |

OSCGND |

||||

|

|

|

|

|

|

|

|

|

SCL1 |

14 |

|

39 |

VDDD(T) |

||||

|

|

|

|

|

|

|

|

|

SDA1 |

15 |

|

38 |

VDDA |

||||

|

|

|

|

|

|

|

|

|

SA |

16 |

|

37 |

VSYNC |

||||

|

|

|

|

|

|

|

|

|

FP |

17 |

|

36 |

HSYNC |

||||

|

|

|

|

|

|

|

|

|

HSMODE |

18 |

|

35 |

VDS |

||||

|

|

|

|

|

|

|

|

|

VSMODE |

19 |

|

34 |

R |

||||

|

|

|

|

|

|

|

|

|

PDI |

20 |

|

33 |

G |

||||

|

|

|

|

|

|

|

|

|

PL |

21 |

|

32 |

B |

||||

|

|

|

|

|

|

|

|

|

VSSA |

22 |

|

31 |

RGBREF |

||||

|

|

|

|

|

|

|

|

|

CVBS1 |

23 |

|

30 |

PON |

||||

|

|

|

|

|

|

|

|

|

CVBS2 |

24 |

|

29 |

|

COR |

|

||

|

|

|

|

|

|

|

|

|

BLACK |

25 |

|

28 |

VSSD2 |

||||

|

|

|

|

|

|

|

|

|

Iref |

26 |

|

27 |

FRAME |

||||

|

|

|

|

|

|

|

|

|

|

|

MGL417 |

|

|

|

|

|

|

Fig.2 Pin configuration.

1998 Apr 22 |

7 |

Philips Semiconductors |

Product specification |

|

|

10-page intelligent teletext decoders |

SAA5261; SAA5262; SAA5263 |

|

|

HIGH LEVEL COMMAND INTERFACE

The I2C-bus interface is used to pass control commands and data between the SAA526xPS and the television microcontroller. The interface uses high level commands, which are backward compatible with the SAFARI interface.

The formats for the I2C-bus transmission are as follows:

Table 1 |

User command |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

START |

|

I2C-bus |

|

WRITE |

ACK |

COMMAND |

|

ACK |

|

STOP |

|

|||||||

|

|

ADDRESS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Table 2 |

System command |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

START |

|

I2C-bus |

|

WRITE |

ACK |

COMMAND |

|

ACK |

PARAMETER |

|

ACK |

|

STOP |

|||||

|

|

ADDRESS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Table 3 |

System read |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

START |

|

I2C-bus |

|

READ |

ACK |

|

DATA |

|

|

|

|

NACK |

|

|

STOP |

|

||

|

|

ADDRESS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Table 4 |

I2C-bus address |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PIN 16 = LOW |

|

|

|

|

|

|

|

PIN 16 = HIGH |

|

|

|

|

||||

|

|

|

|

|

|

|

|

|||||||||||

ADDRESS |

|

DESCRIPTION |

|

|

ADDRESS |

|

DESCRIPTION |

|||||||||||

|

|

|

|

|

|

|

|

|

||||||||||

|

01 01 100 |

|

read = 1; write = 0 |

|

|

0110 000 |

|

read = 1; write = 0 |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Table 5 |

Control commands |

|

||

|

|

|

||

COMMAND |

DATA |

COMMAND |

||

BYTE |

||||

BYTE |

DESCRIPTION |

|||

(HEX) |

||||

|

|

|||

|

|

|

|

|

03 |

|

− |

picture |

|

|

|

|

|

|

04 |

|

− |

TV status |

|

|

|

|

|

|

07 |

|

− |

time |

|

|

|

|

|

|

10 |

|

− |

program 0 |

|

|

|

|

|

|

11 |

|

− |

program 1 |

|

|

|

|

|

|

12 |

|

− |

program 2 |

|

|

|

|

|

|

13 |

|

− |

program 3 |

|

|

|

|

|

|

14 |

|

− |

program 4 |

|

|

|

|

|

|

15 |

|

− |

program 5 |

|

|

|

|

|

|

16 |

|

− |

program 6 |

|

|

|

|

|

|

17 |

|

− |

program 7 |

|

|

|

|

|

|

18 |

|

− |

program 8 |

|

|

|

|

|

|

19 |

|

− |

program 9 |

|

|

|

|

|

|

1A |

|

− |

program 10 |

|

|

|

|

|

|

1B |

|

− |

program 11 |

|

|

|

|

|

|

1C |

|

− |

program 12 |

|

|

|

|

|

|

1D |

|

− |

program 13 |

|

|

|

|

|

|

1E |

|

− |

program 14 |

|

|

|

|

|

|

COMMAND |

DATA |

COMMAND |

|

BYTE |

|||

BYTE |

DESCRIPTION |

||

(HEX) |

|||

|

|

||

|

|

|

|

1F |

− |

program 15 |

|

|

|

|

|

20 |

− |

red |

|

|

|

|

|

21 |

− |

green |

|

|

|

|

|

22 |

− |

yellow |

|

|

|

|

|

23 |

− |

subtitle |

|

|

|

|

|

24 |

− |

text status |

|

|

|

|

|

25 |

− |

hold |

|

|

|

|

|

26 |

− |

reveal |

|

|

|

|

|

27 |

− |

cancel |

|

|

|

|

|

28 |

− |

index |

|

|

|

|

|

29 |

− |

list toggle |

|

|

|

|

|

2B |

− |

reveal toggle |

|

|

|

|

|

2C |

− |

store |

|

|

|

|

|

2D |

− |

previous |

|

|

|

|

|

2F |

− |

subcode |

|

|

|

|

|

30 |

− |

digit 1 |

|

|

|

|

|

31 |

− |

digit 2 |

|

|

|

|

|

32 |

− |

digit 3 |

|

|

|

|

1998 Apr 22 |

8 |

Philips Semiconductors |

Product specification |

|

|

10-page intelligent teletext decoders |

SAA5261; SAA5262; SAA5263 |

|

|

COMMAND |

DATA |

COMMAND |

|||

BYTE |

|||||

BYTE |

DESCRIPTION |

||||

(HEX) |

|||||

|

|

|

|

||

|

|

|

|

|

|

33 |

|

|

− |

digit 4 |

|

|

|

|

|

|

|

34 |

|

|

− |

digit 5 |

|

|

|

|

|

|

|

35 |

|

|

− |

digit 6 |

|

|

|

|

|

|

|

36 |

|

|

− |

digit 7 |

|

|

|

|

|

|

|

37 |

|

|

− |

digit 8 |

|

|

|

|

|

|

|

38 |

|

|

− |

digit 9 |

|

|

|

|

|

|

|

39 |

|

|

− |

digit 0 |

|

|

|

|

|

|

|

3A |

|

|

− |

size |

|

|

|

|

|

|

|

3B |

|

|

− |

up |

|

|

|

|

|

|

|

3C |

|

|

− |

down |

|

|

|

|

|

|

|

3D |

|

|

− |

cyan |

|

|

|

|

|

|

|

3E |

|

|

− |

mix |

|

|

|

|

|

|

|

3F |

|

|

− |

text |

|

|

|

|

|

||

4A |

|

0 |

read PAL + line |

||

|

|

|

|||

89 |

00 to 41 |

select list |

|||

|

|

|

|||

91 |

00 to 03 or |

force mode |

|||

|

00 to 80 |

|

|||

|

|

|

|

||

92 |

|

00 |

read broadcast status |

||

|

|

|

|||

93 |

00 or 01 |

read network |

|||

|

|

|

|

identification |

|

|

|

|

|

||

94 |

|

0 |

read PCS byte |

||

|

|

|

|||

98 |

OSD data |

OSD mode on |

|||

|

|

|

|

||

99 |

|

0 |

OSD mode off |

||

|

|

|

|

||

9A |

|

0 |

OSD display on |

||

|

|

|

|

||

9B |

|

0 |

OSD display off |

||

|

|

|

|

||

9C |

|

0 |

OSD cursor on |

||

|

|

|

|

||

9D |

|

0 |

OSD cursor off |

||

|

|

|

|||

9E |

0, row, column |

OSD position |

|||

|

|

|

|||

9F |

0 followed by |

OSD data write |

|||

|

20 bytes |

|

|||

|

|

|

|||

A0 |

00 to FF |

bitwise parameter or |

|||

|

|

|

|

V7 to V0 |

|

|

|

|

|||

A1 |

00 to FF |

bitwise parameter |

|||

|

|

|

|

and V7 to V0 |

|

|

|

|

|||

A2 |

00 to FF |

returns V7 to V0 on |

|||

|

|

|

|

I2C-bus read |

|

A3 |

PWM |

|

PWM |

PWM control |

|

|

No. |

|

data |

|

|

|

|

|

|

|

|

B0 |

reg |

|

data |

or text register |

|

|

|

|

|

|

|

B1 |

reg |

|

data |

and text register |

|

|

|

|

|

|

|

B2 |

reg |

|

data |

read text register |

|

|

|

|

|

|

|

B8 |

|

0 |

quick list |

||

|

|

|

|

|

|

COMMAND |

DATA |

COMMAND |

|

BYTE |

|||

BYTE |

DESCRIPTION |

||

(HEX) |

|||

|

|

||

|

|

|

|

SAA5262 and SAA5263 only |

|

||

|

|

|

|

B9 |

0 |

get time |

|

|

|

|

|

C0 |

0 = disable |

set ACI mode |

|

|

|

|

|

|

1 = enable |

|

|

|

|

|

|

C1 |

0 |

get ACI status |

|

|

|

|

|

C2 |

0 |

select next ACI channel |

|

|

|

|

|

C3 |

information type |

get ACI information |

|

|

|

|

|

D0 |

0 |

get device version |

|

|

|

|

|

D1 |

page type and |

set page number |

|

|

page number |

|

|

|

|

|

|

D2 |

page type |

get page number |

|

|

|

|

|

D3 |

page type and |

set language |

|

|

language |

|

|

|

|

|

|

D4 |

page type |

get language |

|

|

|

|

|

D5 |

row 24 control |

enable/disable row 24 |

|

|

|

|

|

D6 |

start column |

set row 24 contents |

|

|

and |

|

|

|

length string |

|

|

|

|

|

|

D7 |

string type, |

set string contents |

|

|

index length |

|

|

|

and string |

|

|

|

|

|

|

D8 |

option type and |

set option |

|

|

values |

|

|

|

|

|

|

D9 |

movement type |

move cursor |

|

|

|

|

|

SAA5263 only |

|

||

|

|

|

|

C8 |

EPG mode |

set EPG mode |

|

|

|

|

|

C9 |

0 |

get EPG status |

|

|

|

|

|

CA |

number and list |

set EPG feature list |

|

|

of features |

|

|

|

|

|

|

CB |

0 |

get number of EPG |

|

|

|

CNIs found |

|

|

|

|

|

CC |

CNI index |

get found EPG CNIs |

|

|

|

|

|

CD |

number and list |

set EPG CNI list |

|

|

of CNIs |

|

|

|

|

|

|

CE |

table type, item |

get EPG item |

|

|

type and string |

information |

|

|

index |

|

|

|

|

|

|

1998 Apr 22 |

9 |

Loading...

Loading...