MITSUBISHI PS21562-P Technical data

MITSUBISHI SEMICONDUCTOR <Dual-In-Line Package Intelligent Power Module>

PS21562-P

TRANSFER-MOLD TYPE

INSULATED TYPE

PS21562-P

INTEGRATED POWER FUNCTIONS

600V/5A low-loss 5th generation inverter bridge for three

phase DC-to-AC power conversion

INTEGRATED DRIVE, PROTECTION AND SYSTEM CONTROL FUNCTIONS

•For upper-leg IGBTS :Drive circuit, High voltage isolated high-speed level shifting, Control supply under-voltage (UV) protection.

•For lower-leg IGBTS : Drive circuit, Control supply under-voltage protection (UV), Short circuit protection (SC).

•Fault signaling : Corresponding to an SC fault (Lower-leg IGBT) or a UV fault (Lower-side supply).

•Input interface : 3, 5V line CMOS/TTL compatible. (High Active)

•UL Approved : Yellow Card No. E80276

APPLICATION

AC100V~200V inverter drive for small power motor control.

Fig. 1 PACKAGE OUTLINES

Dimensions in mm

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TERMINAL CODE |

|

|

|

1.778 × |

26 (=46.228) |

|

|

|

A |

|

|

|

|

|

° |

) |

|

|

|

|

|

|

|

|

(0.278) |

1 |

VUFS |

|

|

1.778± 0.15 |

|

|

|

|

|

|

|

|

|

|

(0~3 |

5 |

HEAT SINK SIDE |

|

|

|

2 |

(UPG) |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3.556 |

|

3 |

VUFB |

||

|

|

|

|

|

|

|

|

0.5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

(2.056) |

(0.5) |

4 |

VP1 |

|

28 27 26 25 24 23 22 21 20 19 18 16 |

1513 |

1210 |

9 8 7 |

6 5 4 |

3 2 1 |

|

|

|

|

|

|

|

|

|

|

|

3.556 |

TERMINAL |

|

|

5 |

(COM) |

||||

(φ 2 DEPTH 2) |

|

|

|

|

|

|

|

|

|

|

|

|

|

6 |

UP |

|||||||||||

|

|

17 |

14 |

11 |

|

|

|

(17.6) |

17.4 |

|

|

|

|

|

|

|

|

|

|

(R0. |

||||||

30 |

Type name , Lot No. |

|

|

φ 3.3 |

|

|

|

|

|

|

|

|

|

|

|

|

7 |

VVFS |

||||||||

29 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

75) |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

8 |

(VPG) |

|

30.5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

9 |

VVFB |

35 |

34 |

33 |

32 |

|

31 |

|

|

15.25 |

|

(17.6) |

17.4 |

(6.5) |

|

(3.5) |

|

|

|

|

|

|

|

|

PATTERN |

10 |

VP1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

14 |

(WPG) |

||||||||||||

|

|

|

|

|

|

B |

|

B |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

11 |

(COM) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

35° |

|

|

|

|

|

|

PCB |

12 |

VP |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(1) |

13 |

VWFS |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1.2 |

|

1.75 |

|

1.2 |

(1.5) |

SLIT |

15 |

VWFB |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

7.62± |

0.3 |

(4.62) |

|

|

|

0.5 |

|

|

|

|

|

|

(1.5) |

|

|

|

|

|

|

(ex. PCB LAYOUT) Note1) |

16 |

VP1 |

|||

|

|

7.62 × 4 (=30.48) |

|

|

|

|

|

|

|

|

|

|

|

1.25 |

|

|

|

|

DETAIL A |

|

|

17 |

(COM) |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

18 |

WP |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2.5 |

|

|

|

|

|

|

|

|||||

|

|

|

(41) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

19 |

(UNG) |

|

|

|

|

42± 0.15 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

20 |

VNO Note2) |

|

|

|

49 |

|

|

|

|

|

|

|

|

1 |

|

|

|

|

0.5 |

|

|

1 |

|

0.5 |

|

|

21 |

UN |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(0.5) |

|

|

|

|

|

22 |

VN |

|||

|

|

|

C |

D |

|

|

|

|

|

(0.75) |

|

|

(1) |

|

(0.4) |

|

0.5 |

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0.5 |

|

|

23 |

WN |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(45 |

|

(45° |

|

|

24 |

FO |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

25 |

CFO |

||

|

|

|

|

|

|

|

|

6.5 |

10.5 |

|

|

|

|

|

|

|

|

|

|

°) |

(0.5) |

) |

(0.5) |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

27 |

VNC |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

°) |

|

|

) |

|

|

|

|

|

|

26 |

CIN |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

° |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(15 |

|

(30 |

|

|

|

|

|

|

|

|

|

|

|

|

(φ 3.8) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

28 |

VN1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

29 |

(WNG) |

||

|

|

|

|

|

|

|

|

|

|

|

DETAIL C |

DETAIL D |

|

|

TERMINAL 32, 35 |

TERMINAL 1,28 |

|

30 |

(VNG) |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

31 |

P |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

HEAT SINK SIDE |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

32 |

U |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

33 |

V |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

34 |

W |

|

|

|

φ 3.3 |

|

|

|

|

All outer lead terminals are with Pb-free solder plating. |

|

|

35 |

N |

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

B-B |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Note 1 : In order to get enough creepage distance between the terminals, please take some countermeasure such as a slit on PCB. 2 : The 20th terminal VNO is treated as a NC in DIP-IPM ver.2, it should be connected with the terminal N outside in PS21562-P.

Sep. 2005

MITSUBISHI SEMICONDUCTOR <Dual-In-Line Package Intelligent Power Module>

PS21562-P

TRANSFER-MOLD TYPE

INSULATED TYPE

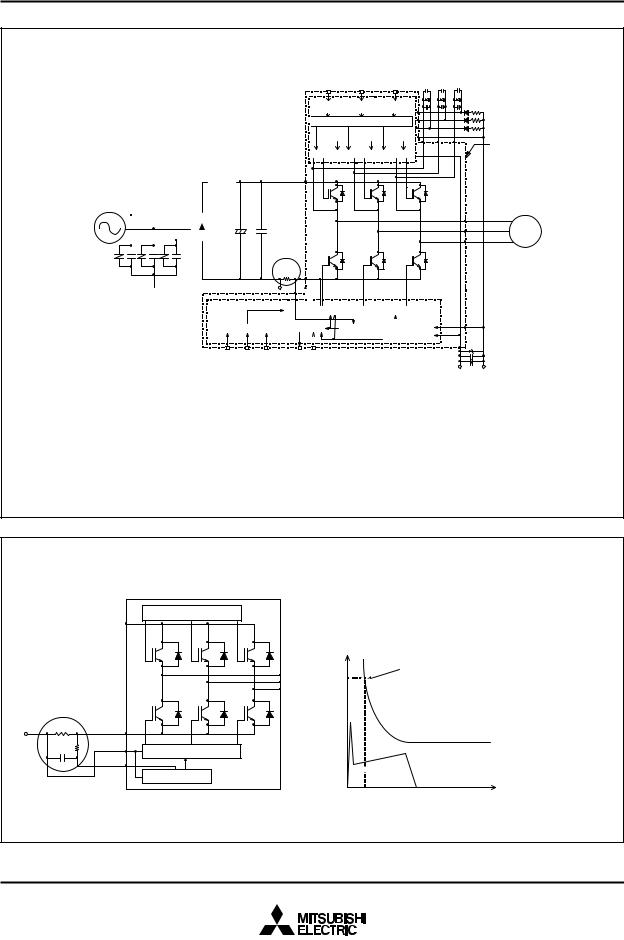

Fig. 2 INTERNAL FUNCTIONS BLOCK DIAGRAM (TYPICAL APPLICATION EXAMPLE)

C1 : Tight tolerance, temp-compensated electrolytic type (Note : The capacitance value depends on the PWM control scheme used in the applied system).

C2 : 0.22~2µ F R-category ceramic capacitor for noise filtering.

High-side input (PWM) (3, 5V line) (Note 1,2)

Input signal |

Input signal |

Input signal |

conditioning |

conditioning |

conditioning |

Level shifter

Level shifter

Level shifter

Level shifter

Level shifter

Level shifter

Protection |

|

Protection |

|

Protection |

circuit (UV) |

|

circuit (UV) |

|

circuit (UV) |

–CBU |

CBU+ |

–CBV |

CBV+ |

–CBW |

CBW+ |

|

|

|

|

|

C2 |

|

|

|

|

|

(Note 8) |

|

|

|

|

|

C1 |

|

|

|

|

|

(Note 6) |

|

|

|

|

|

Inrush current |

|

|

|

|

|

|

Drive circuit |

Drive circuit |

|

Drive circuit |

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

limiter circuit |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

AC line input |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

H-side IGBTS |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

(Note 4) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

C |

|

|

|

|

|

|

|

|

|

Fig. 3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

Z |

|

|

|

|

|

|

|

|

|

|

|

|

(Note 7) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

N1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

N |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

VNC |

|

|

|

|

|

VNO |

|

|

|

|

|

|

|

|

|

|

|

|

L-side IGBTS |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CIN |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Z : ZNR (Surge absorber) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

C : AC filter (Ceramic capacitor 2.2~6.5nF) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Drive circuit |

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

(Note : Additionally, an appropriate line-to line |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Control supply |

|

||||||||

surge absorber circuit may become necessary |

|

|

|

Input signal conditioning |

|

|

Fo logic |

|

|

|

Protection |

|

|

|

Under-Voltage |

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

circuit |

|

|

|

protection |

|

||||||||||

depending on the application environment). |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

Low-side input (PWM) |

|

|

FO CFO |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

(3, 5V line) (Note 1, 2) |

Fault output (5V line) |

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

(Note 3, 5) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VNC |

||||||||

DIP-IPM

U |

|

|

V |

M |

|

W |

||

|

||

|

AC line output |

(Note 8)

(Note 8)

VD

(15V line)

Note1: Input logic is high-active. There is a 2.5kΩ (min) pull-down resistor built-in each input circuit. When using an external CR filter, please make it satisfy the input threshold voltage.

2:By virtue of integrating an application specific type HVIC inside the module, direct coupling to MCU terminals without any opto-coupler or transformer isolation is possible. (see also Fig. 8)

3: This output is open drain type. The signal line should be pulled up to the positive side of the 5V power supply with approximately 10kΩ resistance. (see also Fig. 8)

4:The wiring between the power DC link capacitor and the P, N1 terminals should be as short as possible to protect the DIP-IPM against catastrophic high surge voltages. For extra precaution, a small film type snubber capacitor (0.1~0.22µ F, high voltage type) is recommended to be mounted close to these P-N1 DC power input pins.

5: Fo output pulse width should be decided by putting external capacitor between CFO and VNC terminals. (Example : CFO=22nF → tFO=1.8ms (Typ.))

6:High voltage (600V or more) and fast recovery type (less than 100ns) diodes should be used in the bootstrap circuit.

7:The terminal VNO should be connected to the terminal N outside of DIP-IPM.

8:To prevent ICs from surge destruction, it is recommended to insert a Zener diode (24V, 1W) nearby each pair of supply terminals.

Fig. 3 EXTERNAL PART OF THE DIP-IPM PROTECTION CIRCUIT |

|

||||||

|

|

|

|

DIP-IPM |

Short Circuit Protective Function (SC) : |

|

|

|

|

|

|

|

|

||

|

|

|

|

Drive circuit |

SC protection is achieved by sensing the L-side DC-Bus current (through the external |

||

|

|

|

P |

shunt resistor) after allowing a suitable filtering time (defined by the RC circuit). |

|||

|

|

|

|

||||

|

|

|

|

When the sensed shunt voltage exceeds the SC trip-level, all the L-side IGBTs are turned |

|||

|

|

|

|

|

|||

|

|

|

|

|

OFF and a fault signal (Fo) is output. Since the SC fault may be repetitive, it is |

||

|

|

|

|

|

recommended to stop the system when the Fo signal is received and check the fault. |

||

|

|

|

|

|

IC (A) |

|

|

|

|

|

|

H-side IGBTS |

|

SC Protection |

|

|

|

|

|

|

Trip Level |

|

|

|

|

|

|

U |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

V |

|

|

|

|

|

|

|

W |

|

|

|

|

|

|

|

L-side IGBTS |

|

|

|

External protection circuit |

|

|

|

|

|

|

|

N1 |

Shunt Resistor |

A |

N |

|

|

|

|

|

(Note 1) |

|

|

|

|

|

|

|

C R |

|

VNC |

Drive circuit |

|

|

|

|

|

|

CIN |

|

|

|

|

|

|

|

B |

|

|

Collector current |

|

|

C |

|

|

Protection circuit |

|

waveform |

|

|

|

(Note 2) |

|

|

0 |

|

|

|

|

|

|

|

|

||

Note1: In the recommended external protection circuit, please select the RC time constant in the range 1.5~2.0µ s. |

2 |

tw ( s) |

|||||

2: |

To prevent erroneous protection operation, the wiring of A, B, C should be as short as possible. |

|

|

|

|||

Sep. 2005

MITSUBISHI SEMICONDUCTOR <Dual-In-Line Package Intelligent Power Module>

PS21562-P

TRANSFER-MOLD TYPE

INSULATED TYPE

MAXIMUM RATINGS (Tj = 25° C, unless otherwise noted)

INVERTER PART

|

Symbol |

Parameter |

Condition |

Ratings |

Unit |

VCC |

Supply voltage |

Applied between P-N |

450 |

V |

|

VCC(surge) |

Supply voltage (surge) |

Applied between P-N |

500 |

V |

|

VCES |

Collector-emitter voltage |

|

600 |

V |

|

± IC |

Each IGBT collector current |

Tf = 25° C |

5 |

A |

|

± |

ICP |

Each IGBT collector current (peak) |

° |

10 |

A |

|

|

Tf = 25 C, less than 1ms |

|||

PC |

Collector dissipation |

° |

16.7 |

W |

|

|

Tf = 25 C, per 1 chip |

||||

Tj |

Junction temperature |

(Note 1) |

–20~+125 |

° C |

|

Note 1 : The maximum junction temperature rating of the power chips integrated within the DIP-IPM is 150° C (@ Tf ≤ 100° C) however, to ensure safe operation of the DIP-IPM, the average junction temperature should be limited to Tj(ave) ≤ 125° C (@ Tf ≤ 100° C).

CONTROL (PROTECTION) PART

Symbol |

Parameter |

Condition |

Ratings |

Unit |

|

VD |

Control supply voltage |

Applied between VP1-VNC, VN1-VNC |

20 |

V |

|

VDB |

Control supply voltage |

Applied between VUFB-VUFS, VVFB-VVFS, |

20 |

V |

|

VWFB-VWFS |

|||||

|

|

|

|

||

VIN |

Input voltage |

Applied between UP, VP, WP, UN, VN, |

–0.5~VD+0.5 |

V |

|

WN-VNC |

|||||

|

|

|

|

||

VFO |

Fault output supply voltage |

Applied between FO-VNC |

–0.5~VD+0.5 |

V |

|

IFO |

Fault output current |

Sink current at FO terminal |

1 |

mA |

|

VSC |

Current sensing input voltage |

Applied between CIN-VNC |

–0.5~VD+0.5 |

V |

TOTAL SYSTEM

Symbol |

Parameter |

Condition |

Ratings |

Unit |

|

VCC(PROT) |

Self protection supply voltage limit |

VD = 13.5~16.5V, Inverter part |

400 |

V |

|

|

(short circuit protection capability) |

Tj = 125° C, non-repetitive, less than 2 s |

|

|

|

Tf |

Module case operation temperature |

(Note 2) |

–20~+100 |

° C |

|

Tstg |

Storage temperature |

|

–40~+125 |

° C |

|

Viso |

Isolation voltage |

60Hz, Sinusoidal, 1 minute, |

2500 |

Vrms |

|

All connected pins to heat-sink plate |

|||||

|

|

|

|

Note 2 : Tf measurement point

Al Board Specification : |

|

|

|

|

|

|

|

|

|

|

|

||||||

Dimensions : 100 100 10mm, Finishing : 12s, Warp : –50~100 m |

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

Control Terminals |

|

|

|

|

|

|

|

|||

18mm |

|

|

|

|

|

|

|

|

|

FWDi Chip |

|

IGBT/FWDi Chip |

|||||

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

16mm |

Groove |

Al Board |

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IGBT Chip |

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||

N W V U P |

|

Temperature measurement |

|||||||||||||||

|

|

|

|

|

|

|

|

||||||||||

Temperature |

|

point (inside the AI board) |

|||||||||||||||

measurement point |

|

|

|

|

|

|

|

|

|

|

|

||||||

(inside the AI board) |

|

Power Terminals |

|

|

|

|

|

|

|

||||||||

Silicon-grease should be applied evenly with a thickness of 100~200 m

Sep. 2005

Loading...

Loading...