Mitsubishi M37905M8C-XXXSP, M37905M8C-XXXFP, M37905M6C-XXXSP, M37905M6C-XXXFP, M37905M4C-XXXSP Datasheet

...

|

|

|

|

|

|

Y |

|

PRELIMINAR |

|

||||||

|

|

|

|

|

|

. . |

|

|

|

|

|

|

specification |

change |

|

|

|

|

|

|

|

to |

|

|

|

|

a |

final |

|

subject |

|

|

is |

not |

are |

|

|

||

|

limits |

|

|

|

|||

This |

|

|

|

|

|||

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

Notice:parametric |

|

|

|

|

|

||

Some |

|

|

|

|

|

|

|

MITSUBISHI MICROCOMPUTERS

M37905M4C-XXXFP, M37905M4C-XXXSP M37905M6C-XXXFP, M37905M6C-XXXSP M37905M8C-XXXFP, M37905M8C-XXXSP

16-BIT CMOS MICROCOMPUTER

DESCRIPTION

These are single-chip 16-bit microcomputers designed with high-per- formance CMOS silicon gate technology, being packaged in 64-pin plastic molded QFP or shrink plastic molded SDIP. These microcomputers support the 7900 Series instruction set, which are enhanced and expanded instruction set and are upper-compatible with the

7700/7751 Series instruction set.

The CPU of these microcomputers is a 16-bit parallel processor that can also be switched to perform 8-bit parallel processing. Also, the bus interface unit of these microcomputers enhances the memory access efficiency to execute instructions fast. Therefore, these microcomputers are suitable for office, business, and industrial equipment controller that require high-speed processing of large data.

Also, they are suitable for motor-control equipment since each of them includes the motor control circuit.

[M37905M8C-XXXFP, M37905M8C-XXXSP] |

|

|

ROM .............................................................................. |

|

60 Kbytes |

RAM ............................................................................. |

|

3072 bytes |

• Instruction execution time |

|

|

The fastest instruction at 20 MHz frequency ........................ |

50 ns |

|

• Single power supply .................................................... |

5 V ± 0.5 V |

|

• Interrupts ........... |

8 external sources, 23 internal sources, 7 levels |

|

• Multi-functional 16-bit timer ................................................. |

10 + 3 |

|

(Three-phase motor drive waveform and Pulse motor drive waveform output are available.)

• Serial I/O (UART or Clock synchronous) |

..................................... 3 |

• 10-bit A-D converter .......................................... |

12-channel inputs |

• 8-bit D-A converter ............................................ |

2-channel outputs |

• 12-bit watchdog timer |

|

• Programmable input/output (ports P1, P2, P4, P5, P6, P7, P8) .. 50

DISTINCTIVE FEATURES |

|

APPLICATION |

• Number of basic machine instructions .................................... |

203 |

Control devices for office equipment such as copiers and facsimiles |

• Memory |

|

Control devices for industrial equipment such as communication |

[M37905M4C-XXXFP, M37905M4C-XXXSP] |

|

and measuring instruments |

ROM .............................................................................. |

32 Kbytes |

Control devices for equipment, requiring motor control, such as |

RAM ............................................................................. |

1024 bytes |

inverter air conditioners and general-purpose inverters |

[M37905M6C-XXXFP, M37905M6C-XXXSP] |

|

|

ROM .............................................................................. |

48 Kbytes |

|

RAM ............................................................................. |

3072 bytes |

|

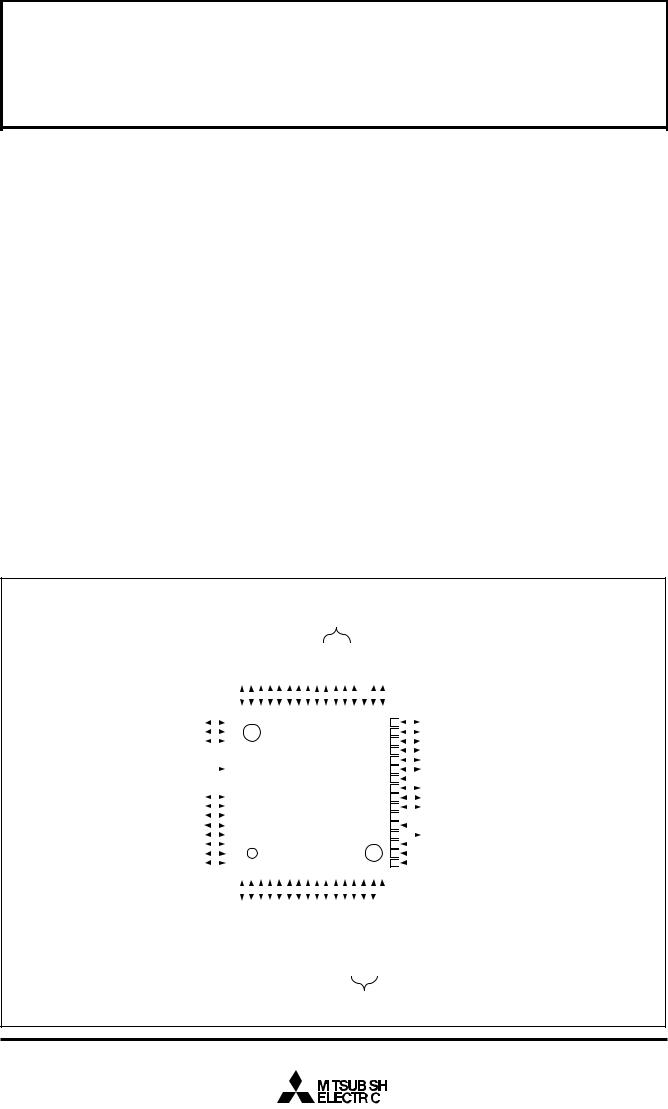

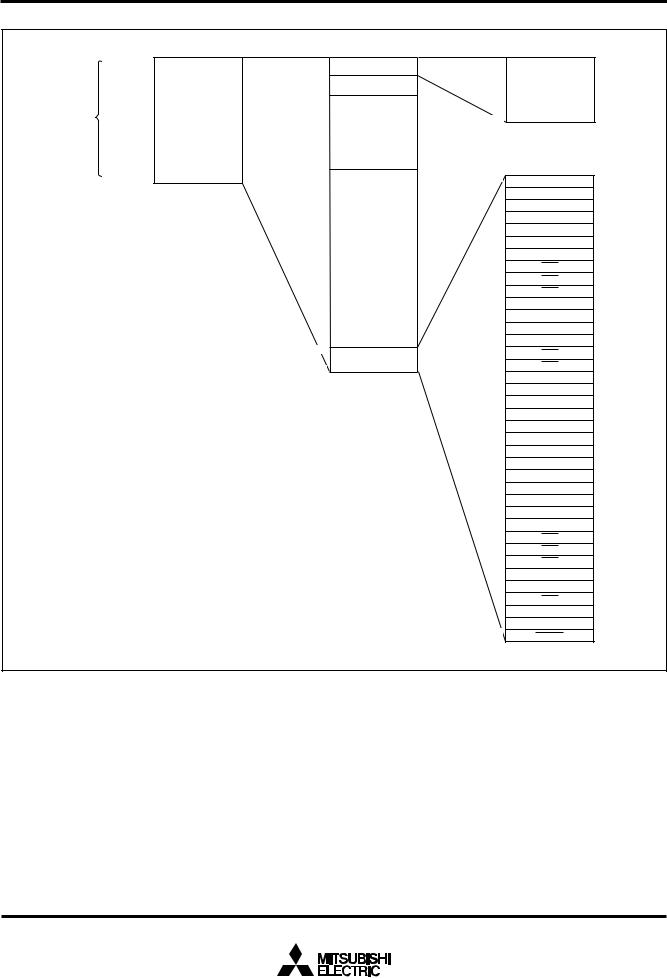

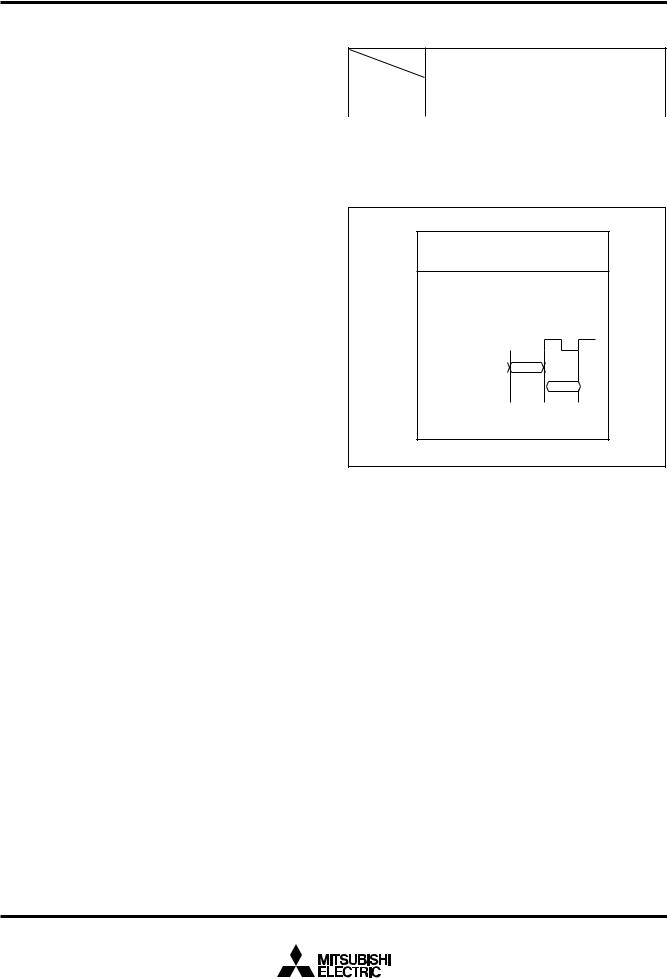

M37905MxC-XXXFP PIN CONFIGURATION (TOP VIEW)

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P13/TxD0 |

|

P14/CTS1/RTS1 |

|

P15/CTS1/CLK1 |

P16/RxD1 |

P17/TxD1 |

P20/TA4OUT |

P21/TA4IN |

P22/TA9OUT |

P23/TA9IN |

|

P24(/TB0IN) |

|

P25(/TB1IN) Note |

|

P26(/TB2IN) |

|

P27 |

|

MD1 |

|

P40/TA5OUT/RTP20 |

|

P41/TA5IN/RTP21 |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

48 |

47 |

46 |

45 |

44 |

43 |

42 |

41 |

40 |

39 |

38 |

37 |

36 |

35 |

|

34 |

|

33 |

|||||||||||||||||||

|

|

|

|

|

|

P12/RXD0 |

|

|

|

49 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

P11 |

|

|

|

|

/CLK0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

/CTS0 |

|

|

|

50 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

P10 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

/CTS0 |

|

/RTS0 |

|

|

|

|

51 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

VCC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

52 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

AVCC |

|

|

|

53 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

VREF |

|

|

|

54 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

AVSS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

55 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

M37905MXC-XXXFP |

|

|

|

|

|

|

|||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

VSS |

|

|

|

56 |

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||

|

P83/AN11/TXD2 |

|

|

|

57 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

P82/AN10/RXD2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

58 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

P81/AN9 |

/CTS2 |

/CLK2 |

|

|

|

59 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

P80/AN8 |

/CTS2 |

|

/RTS2 |

/DA1 |

|

|

|

60 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

P77/AN7/DA0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

61 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

P76/AN6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

62 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

P75/AN5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

63 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

P74/AN4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

64 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

11 |

12 |

13 |

14 |

|

15 |

|

16 |

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P73/AN3 |

|

P72/AN2 |

|

P71/AN1 |

P70/AN0 |

P67/TA3IN/RTP13 |

P66/TA3OUT/RTP12 |

P65/TA2IN/U/RTP11 |

P64/TA2OUT/V/RTP10 |

P63/TA1IN/W/RTP03 |

|

P62/TA1OUT/U/RTP02 |

|

P61/TA0IN/V/RTP01 |

|

P60/TA0OUT/W/RTP00 |

|

P57/INT7/TB2IN/IDU |

|

P56/INT6/TB1IN/IDV |

|

P55/INT5/TB0IN/IDW |

|

P6OUTCUT/INT4 |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

Outline 64P6N-A |

|

|

|

|

|

|

|

|

|

|

Note |

|

|

|

|

|

|

|||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

32 |

|

|

|

|

|

|

P42/TA6OUT/RTP22 |

|||||||||||||

|

|

|

||||||||||||||||||

31 |

|

|

|

|

|

|

P43/TA6IN/RTP23 |

|||||||||||||

|

|

|

||||||||||||||||||

30 |

|

|

|

|

|

|

P44/TA7OUT/RTP30 |

|||||||||||||

|

|

|

||||||||||||||||||

29 |

|

|

|

|

|

|

P45/TA7IN/RTP31 |

|||||||||||||

|

|

|

||||||||||||||||||

28 |

|

|

|

|

|

|

P46/TA8OUT/RTP32 |

|||||||||||||

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|||||||||||||||||

27 |

|

|

|

|

|

|

P47/TA8IN/RTP33 |

|||||||||||||

|

|

|

|

|||||||||||||||||

26 |

|

|

|

|

|

|

|

P4OUTCUT |

|

/INT0 |

|

|||||||||

|

|

|

|

|

|

|||||||||||||||

25 |

|

|

|

|

|

|

P51 |

/INT1 |

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

||||||||||||

24 |

|

|

|

|

|

|

P52 |

|

/INT2 |

/RTPTRG1 |

||||||||||

|

|

|

|

|

||||||||||||||||

23 |

|

|

|

|

|

|

P53 |

|

|

|

|

|

||||||||

/INT3/RTPTRG0 |

||||||||||||||||||||

|

|

|

|

|

||||||||||||||||

22 |

|

|

|

|

|

|

VSS |

|||||||||||||

|

|

|

|

|

|

|||||||||||||||

21 |

|

|

|

|

|

|

VCONT |

|||||||||||||

|

|

|

|

|

|

|||||||||||||||

20 |

|

|

|

|

|

|

XOUT |

|||||||||||||

|

|

|

|

|

|

|||||||||||||||

19 |

|

|

|

|

|

|

XIN |

|||||||||||||

|

|

|

|

|

|

|||||||||||||||

18 |

|

|

|

|

|

|

|

|

RESET |

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

17 |

|

|

|

|

|

|

MD0 |

|||||||||||||

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Note : Allocation of pins TB0IN to TB2IN can be switched by software.

|

|

|

|

|

|

Y |

|

PRELIMINAR |

|

||||||

|

|

|

|

|

|

. . |

|

|

|

|

|

|

specification |

change |

|

|

|

|

|

|

|

to |

|

|

|

|

a |

final |

|

subject |

|

|

is |

not |

are |

|

|

||

|

limits |

|

|

|

|||

This |

|

|

|

|

|||

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

Notice:parametric |

|

|

|

|

|

||

Some |

|

|

|

|

|

|

|

MITSUBISHI MICROCOMPUTERS

M37905M4C-XXXFP, M37905M4C-XXXSP M37905M6C-XXXFP, M37905M6C-XXXSP M37905M8C-XXXFP, M37905M8C-XXXSP

16-BIT CMOS MICROCOMPUTER

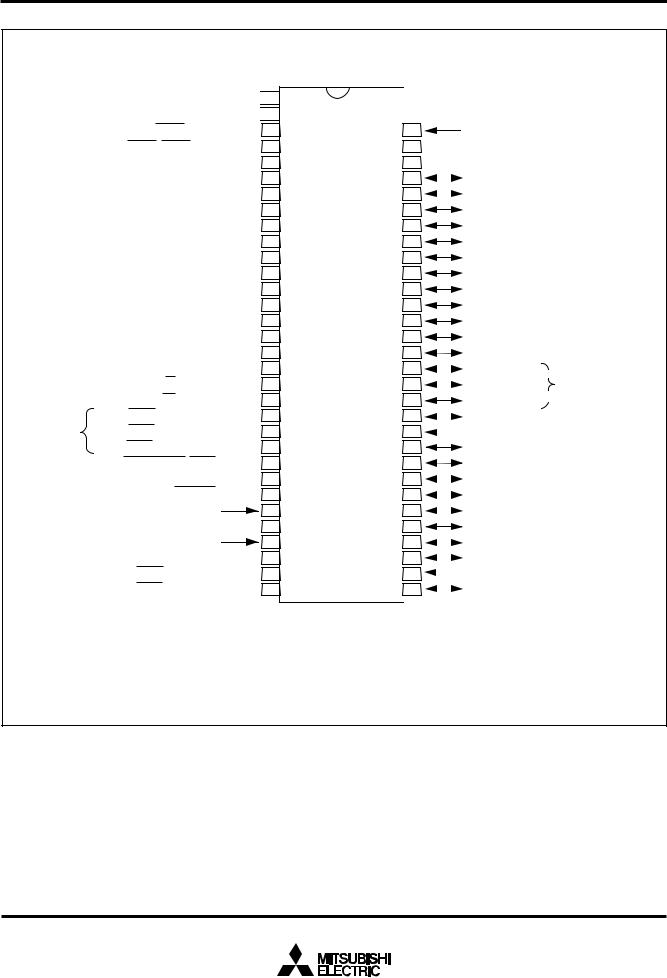

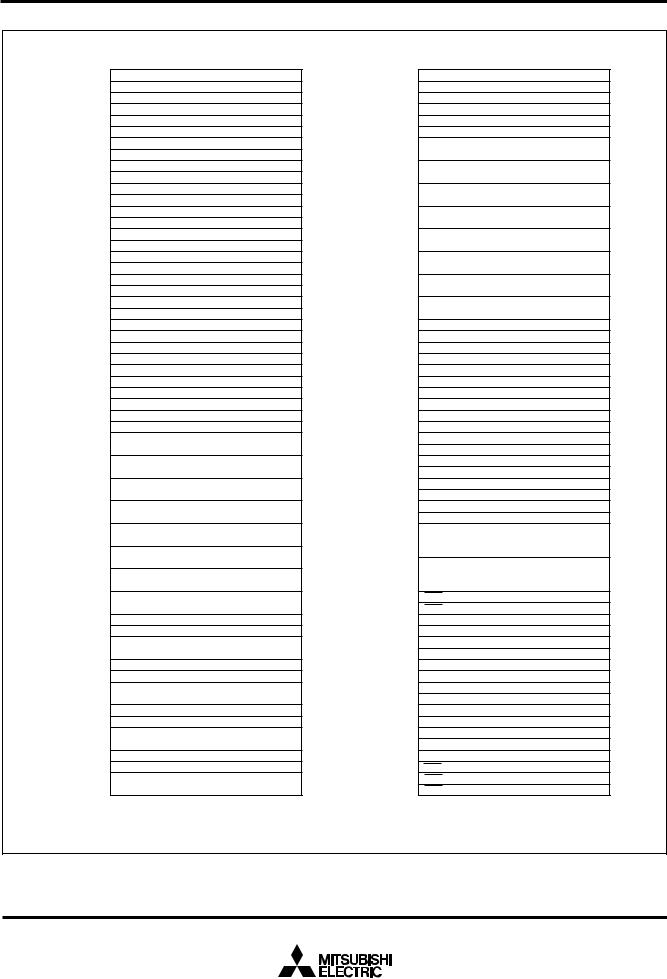

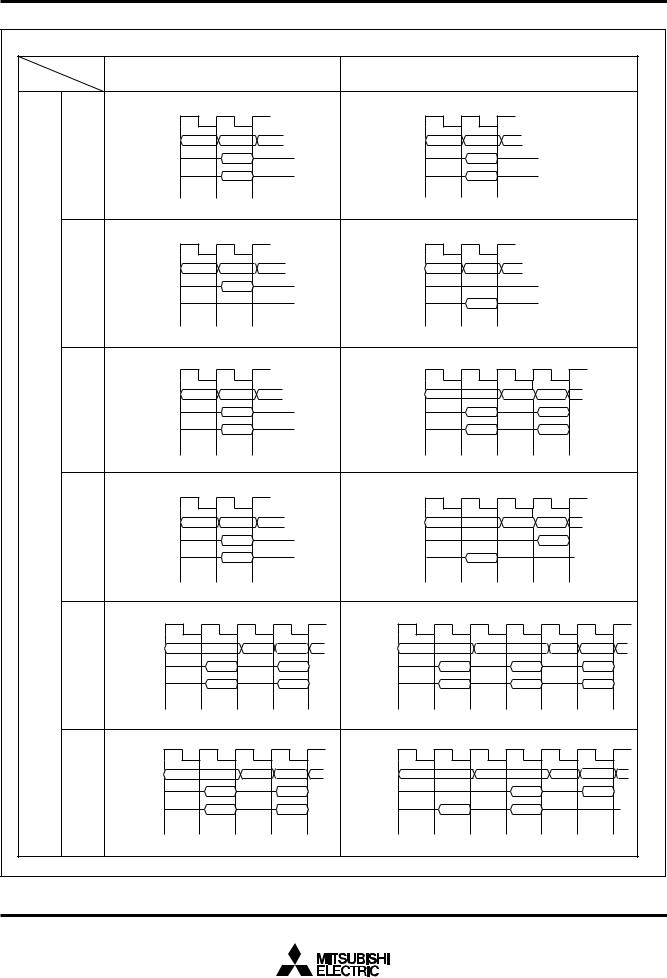

M37905MxC-XXXSP PIN CONFIGURATION (TOP VIEW)

P83/AN11/TxD2

P82/AN10/RxD2

P81/AN9/CTS2/CLK2

P80/AN8/CTS2/RTS2/DA1

P77/AN7/DA0

P76/AN6

P75/AN5

P74/AN4

P73/AN3

P72/AN2

P71/AN1

P70/AN0

P67/TA3IN/RTP13

P66/TA3OUT/RTP12

P65/TA2IN/U/RTP11

P64/TA2OUT/V/RTP10

P63/TA1IN/W/RTP03

P62/TA1OUT/U/RTP02

P61/TA0IN/V/RTP01

P60/TA0OUT/W/RTP00

P57/INT7/TB2IN/IDU

Note P56/INT6/TB1IN/IDV

P55/INT5/TB0IN/IDW

P6OUTCUT/INT4

MD0

RESET

XIN

XOUT

VCONT

VSS

P53/INT3/RTPTRG0

P52/INT2/RTPTRG1

1 |

|

2 |

|

3 |

|

4 |

|

5 |

|

6 |

|

7 |

|

8 |

|

9 |

|

10 |

|

11 |

|

12 |

X-CM37905M |

19 |

|

13 |

|

14 |

|

15 |

|

16 |

|

17 |

|

18 |

XXXSP |

23 |

|

20 |

|

21 |

|

22 |

|

24 |

|

25 |

|

26 |

|

27 |

Outline 64P4B |

28 |

|

29 |

|

30 |

|

31 |

|

32 |

|

|

|

|

|

|

|

VSS |

|

|

|||||||||||||||||

64 |

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

AVSS |

|

|

|||||||||||||||||

63 |

|

|

|

|

|

|

|

||||||||||||||||||

62 |

|

|

|

|

|

VREF |

|

|

|||||||||||||||||

61 |

|

|

|

|

|

AVCC |

|

|

|||||||||||||||||

60 |

|

|

|

|

|

VCC |

|

|

|||||||||||||||||

59 |

|

|

|

|

|

P10 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

/CTS0 |

/RTS0 |

||||||||||||||||||||||

|

|

||||||||||||||||||||||||

58 |

|

|

|

|

|

P11 |

/CTS0 |

/CLK0 |

|

|

|||||||||||||||

|

|

|

|

||||||||||||||||||||||

57 |

|

|

|

|

|

P12/RxD0 |

|

|

|||||||||||||||||

56 |

|

|

|

|

|

P13/TxD0 |

|

|

|||||||||||||||||

55 |

|

|

|

|

|

P14 |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

/CTS1 |

/RTS1 |

|

|

||||||||||||||||||||

54 |

|

|

|

|

|

P15 |

/CTS1 |

/CLK1 |

|

|

|||||||||||||||

53 |

|

|

|

|

|

P16/RxD1 |

|

|

|||||||||||||||||

52 |

|

|

|

|

|

P17/TxD1 |

|

|

|||||||||||||||||

51 |

|

|

|

|

|

P20/TA4OUT |

|

|

|||||||||||||||||

50 |

|

|

|

|

|

P21/TA4IN |

|

|

|||||||||||||||||

49 |

|

|

|

|

|

P22/TA9OUT |

|

|

|||||||||||||||||

48 |

|

|

|

|

|

P23/TA9IN |

|

|

|||||||||||||||||

47 |

|

|

|

|

|

P24(/TB0IN) |

|

|

Note |

||||||||||||||||

|

|

|

|

|

|

||||||||||||||||||||

46 |

|

|

|

|

|

P25(/TB1IN) |

|

|

|||||||||||||||||

|

|

||||||||||||||||||||||||

45 |

|

|

|

|

|

P26(/TB2IN) |

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

||||||||||||||||||

44 |

|

|

|

|

|

P27 |

|

|

|||||||||||||||||

|

|

|

|

||||||||||||||||||||||

43 |

|

|

|

|

|

MD1 |

|

|

|||||||||||||||||

|

|

|

|

||||||||||||||||||||||

42 |

|

|

|

|

|

P40/TA5OUT/RTP20 |

|||||||||||||||||||

41 |

|

|

|

|

|

P41/TA5IN/RTP21 |

|||||||||||||||||||

40 |

|

|

|

|

|

P42/TA6OUT/RTP22 |

|||||||||||||||||||

39 |

|

|

|

|

|

P43/TA6IN/RTP23 |

|||||||||||||||||||

|

|

|

|||||||||||||||||||||||

38 |

|

|

|

|

|

P44/TA7OUT/RTP30 |

|||||||||||||||||||

|

|

|

|||||||||||||||||||||||

37 |

|

|

|

|

|

P45/TA7IN/RTP31 |

|||||||||||||||||||

36 |

|

|

|

|

|

P46/TA8OUT/RTP32 |

|||||||||||||||||||

|

|

|

|||||||||||||||||||||||

35 |

|

|

|

|

|

P47/TA8IN/RTP33 |

|||||||||||||||||||

|

|

|

|||||||||||||||||||||||

34 |

|

|

|

|

|

P4OUTCUT |

|

/INT0 |

|

||||||||||||||||

|

|

|

|||||||||||||||||||||||

33 |

|

|

|

|

|

P51 |

/INT1 |

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Note : Allocation of pins TB0IN to TB2IN can be switched by software.

Outline 64P4B

2

|

|

|

|

|

|

Y |

|

PRELIMINAR |

|

||||||

|

|

|

|

|

|

. . |

|

|

|

|

|

|

specification |

change |

|

|

|

|

|

|

|

to |

|

|

|

|

a |

final |

|

subject |

|

|

is |

not |

are |

|

|

||

|

|

|

|

||||

|

limits |

|

|

|

|||

This |

|

|

|

|

|||

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

Notice:parametric |

|

|

|

|

|

||

Some |

|

|

|

|

|

|

|

MITSUBISHI MICROCOMPUTERS

M37905M4C-XXXFP, M37905M4C-XXXSP M37905M6C-XXXFP, M37905M6C-XXXSP M37905M8C-XXXFP, M37905M8C-XXXSP

16-BIT CMOS MICROCOMPUTER

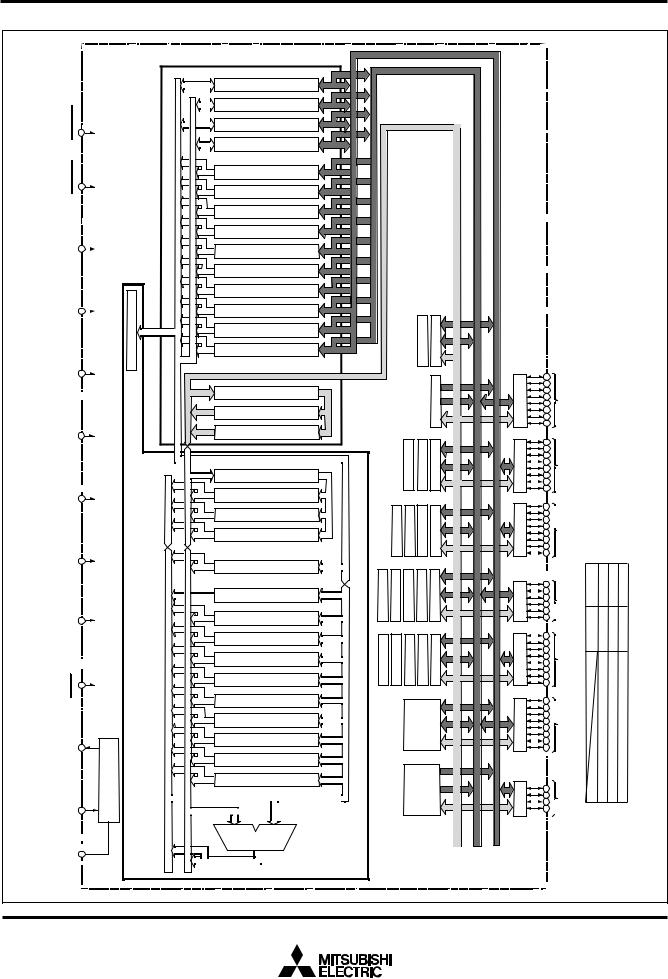

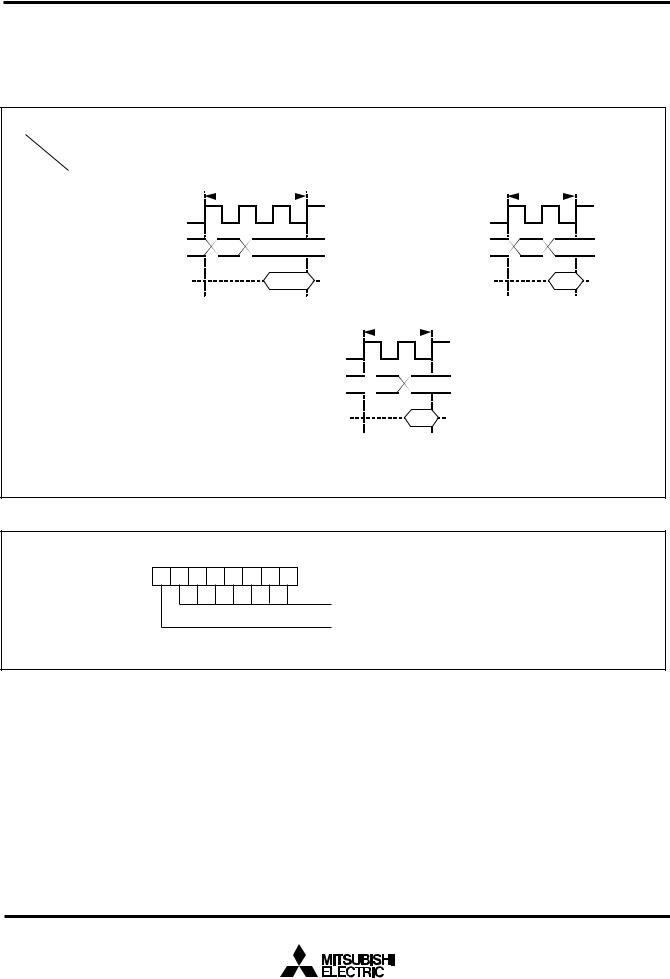

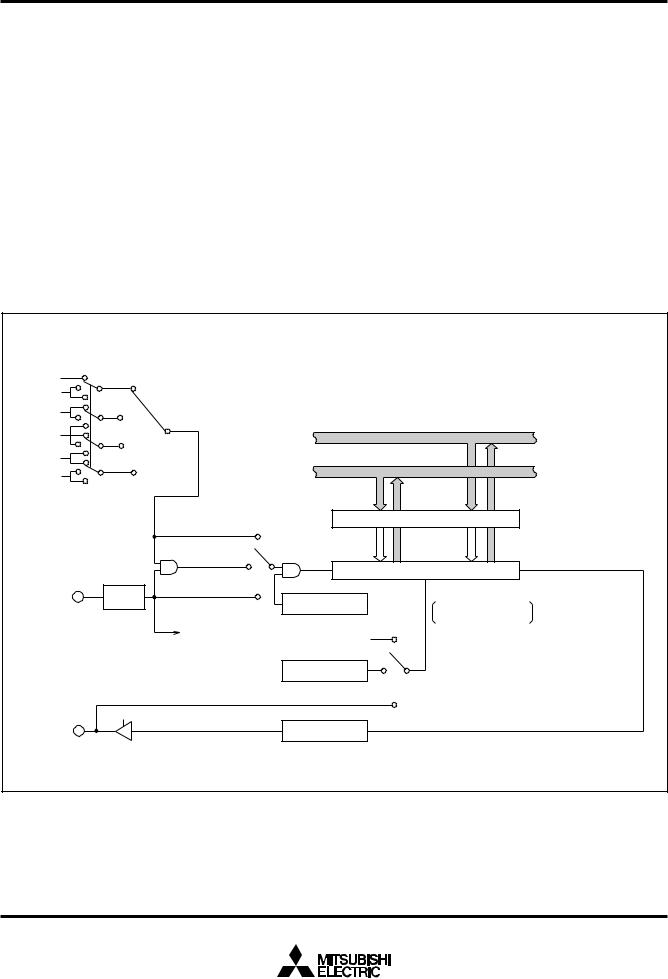

|

|

|

|

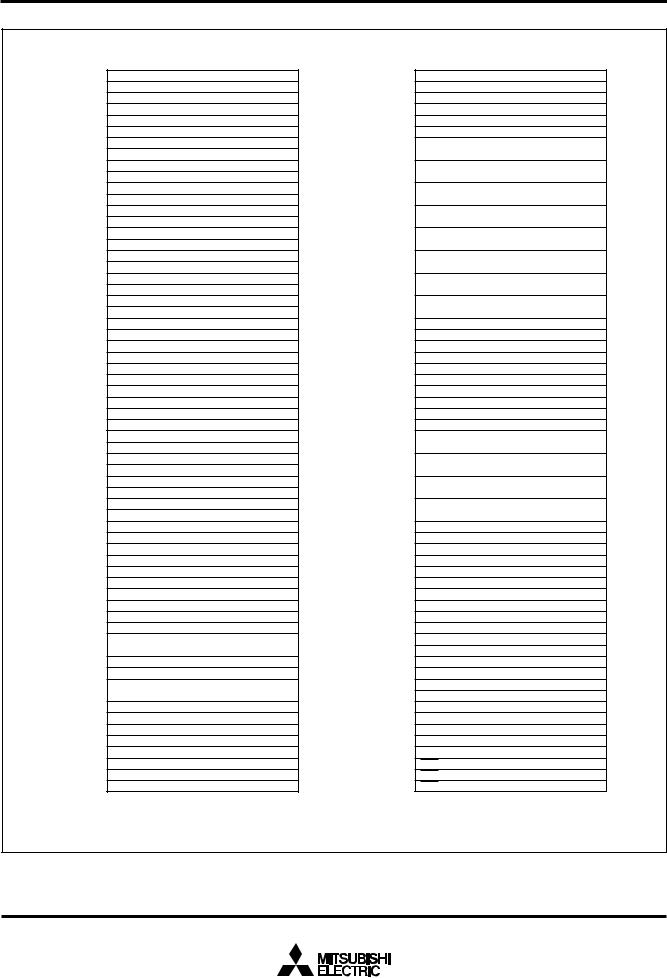

Data Buffer DQ0 |

(8) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CUT |

|

Data Buffer DQ1 |

(8) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P6OUT |

|

Data Buffer DQ2 |

(8) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Data Buffer DQ3 |

(8) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CUT |

|

Instruction Queue Buffer Q0 |

(8) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P4OUT |

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

Instruction Queue Buffer Q1 |

(8) |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

Instruction Queue Buffer Q2 |

(8) |

|

|

|

|

|

|

|

|

|

|

|

|

Reference |

VoltageInput |

|

|

Instruction Queue Buffer Q3 |

(8) |

|

|

|

|

|

|

|

|

|

|

|

|

VREF |

|

Instruction Queue Buffer Q4 |

(8) |

|

|

|

|

|

|

|

|

|

|

|

|||

|

Instruction Queue Buffer Q5 |

(8) |

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

Instruction Queue Buffer Q6 |

(8) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AVCC |

Register(8) |

Instruction Queue Buffer Q7 |

(8) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Instruction Queue Buffer Q8 |

(8) |

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

Instruction |

Instruction Queue Buffer Q9 |

(8) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(0V) |

AVSS |

|

|

|

|

|

|

|

|

|

|

P1 |

|

|

|

|

|

|

|

|

Incrementer (24) |

|

|

|

|

|

|

P1(8) |

Input/Output |

|

|

|

|

|

|

|

|

|

Program Address Register PA (24) |

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

MD1 |

|

Data Address Register DA (24) |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

Incrementer/Decrementer (24) |

|

|

UART2(9) |

|

|

P2(8) |

Input/OutputP2 |

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

MD0 |

|

Program Counter PC (16) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P4 |

|

|

|

|

|

|

|

|

|

Program Bank Register PG |

(8) |

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

Input/Output |

|

|

|

|

|||

|

|

|

|

Data Bank Register DT (8) |

|

|

|

|

|

|

P4(8) |

|

|

|

|

||

|

(0V) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

VSS |

|

Input Buffer Register IB (16) |

|

|

|

|

|

|

|

|

|

Kbytes 3Kbytes |

Kbytes 3Kbytes |

|||

|

|

|

|

Processor Status Register PS (11) |

TimerTA9(16) |

TimerTA8(16) |

TimerTA7(16) |

TimerTA6(16) |

TimerTA5(16) |

P5(6) |

Input/OutputP5 |

ROM RAM |

Kbytes 1Kbyte |

||||

|

|

VCC |

|

Direct Page Register DPR0 (16) |

|||||||||||||

|

|

|

Direct Page Register DPR1 (16) |

||||||||||||||

|

|

|

|

|

|

|

|

|

|

P6 |

|

32 |

48 |

60 |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

Direct Page Register DPR2 (16) |

|

|

|

|

|

P8(4) P7(8) P6(8) |

Input/OutputP8 Input/OutputP7 Input/Output |

|

M37905M4C-XXXFP,M37905M4C-XXXSP |

M37905M6C-XXXFP,M37905M6C-XXXSP |

M37905M8C-XXXFP,M37905M8C-XXXSP |

||

|

Clockinput Clockoutput Resetinput |

XXRESETINOUT |

|

Direct Page Register DPR3 (16) |

|

|

|

|

|

|

|||||||

|

|

Stack Pointer S (16) |

|

|

|

|

|

|

|

||||||||

|

|

Index Register Y (16) |

|

|

|

|

|

|

|

||||||||

|

ClockGeneratingCircuit |

Index Register X (16) |

|

|

|

|

|

|

|

||||||||

DIAGRAM |

Accumulator B (16) |

|

|

|

|

|

|

|

|||||||||

Accumulator A (16) |

|

|

|

ROM |

(Note) |

|

|

||||||||||

Arithmetic Logic |

|

|

Central |

|

|

Note: |

|||||||||||

BLOCK |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

VCONT |

|

Unit (16) |

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3 |

|

|

|

|

|

Y |

|

PRELIMINAR |

|

|||||

|

|

|

|

|

. . |

|

|

|

|

|

specification |

change |

|

|

|

|

|

|

to |

|

|

a |

final |

|

subject |

|

|

isnot |

its |

are |

|

|

||

|

|

|

||||

This |

lim |

|

|

|

|

|

etric |

|

|

|

|

|

|

Notice:param |

|

|

|

|

|

|

e |

|

|

|

|

|

|

Som |

|

|

|

|

|

|

MITSUBISHI MICROCOMPUTERS

M37905M4C-XXXFP, M37905M4C-XXXSP M37905M6C-XXXFP, M37905M6C-XXXSP M37905M8C-XXXFP, M37905M8C-XXXSP

16-BIT CMOS MICROCOMPUTER

FUNCTIONS

|

|

|

|

Parameter |

|

|

Functions |

||

|

|

|

|

|

|

|

|

|

|

Number of basic machine instructions |

203 |

|

|

||||||

|

|

|

|

|

|

|

|

|

|

Instruction execution time |

|

|

|

50 ns (the fastest instruction at f(fsys) = 20 MHz) |

|||||

External clock input frequency f(XIN) |

20 MHz (Max.) |

|

|

||||||

System clock frequency f(fsys) |

20 MHz (Max.) |

|

|

||||||

Memory size |

|

ROM |

(Note 1) |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

RAM |

(Note 1) |

|

|

|

|

|

|

|

|

|

|

|

|

|

Programmable input/output |

|

P1, P2, P4, P6, P7 |

8-bit 5 |

|

|

||||

ports |

|

|

|

|

|

|

|||

|

P5 |

6-bit 1 |

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P8 |

4-bit 1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

Multi-functional timers |

|

TA0–TA9 |

16-bit 10 |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TB0–TB2 |

16-bit 3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

Serial I/O |

|

UART0, UART1, and UART2 |

(UART or Clock synchronous serial I/O) 3 |

||||||

|

|

|

|

|

|

|

|

|

|

A-D converter |

|

|

|

10-bit successive approximation method 1 (12 channels) |

|||||

|

|

|

|

|

|

|

|

|

|

D-A converter |

|

|

|

8-bit 2 |

|

|

|||

|

|

|

|

|

|

|

|

|

|

Dead-time timer |

|

|

|

8-bit 3 |

|

|

|||

|

|

|

|

|

|

|

|

|

|

Watchdog timer |

|

|

|

12-bit 1 |

|

|

|||

|

|

|

|

|

|

|

|

|

|

Interrupts |

|

Maskable interrups |

8 external sources, 20 internal sources. Each interrupt can be set |

||||||

|

|

|

|

|

|

|

to a priority level within the range of 0–7 by software. |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Non-maskable interrups |

3 internal sources |

|

|

|

|

|

|

|

|

|

|

|

|

|

Clock generating circuit |

|

|

|

Incorporated (externally connected to a ceramic resonator or |

|||||

|

|

|

|

|

|

|

quartz-crystal resonator). |

||

|

|

|

|

|

|

|

|

|

|

PLL frequency multiplier |

|

|

|

The following multiplication ratios are available: 2, 3, 4. |

|||||

|

|

|

|

|

|

|

|

|

|

Power supply voltage |

|

|

|

5 V±0.5 V |

|

|

|||

|

|

|

|

|

|

|

|

|

|

Power dissipation |

|

|

|

125 mW (at f(fsys) = 20 MHz, Typ, ; the PLL frequency multiplier is inactive.) |

|||||

Ports’ input/output |

|

nput/Output withstand voltage |

5 V |

|

|

||||

characteristics |

|

utput current |

5 mA |

|

|

||||

Memory expansion |

|

|

|

Not available (single-chip mode only). |

|||||

Operating ambient temperature range |

–20 to 85 °C |

|

|

||||||

Device structure |

|

|

|

CMOS high-performance silicon gate process |

|||||

Package |

|

|

|

(Note 2) |

|

|

|||

|

|

|

|

|

|

|

|||

Notes 1: |

ROM |

|

|

M37905M4C-XXXFP, M37905M4C-XXXSP |

|

32 Kbytes |

|||

|

|

|

|

||||||

|

|

|

|

|

|

M37905M6C-XXXFP, M37905M6C-XXXSP |

|

48 Kbytes |

|

|

|

|

|

|

|

M37905M8C-XXXFP, M37905M8C-XXXSP |

|

60 Kbytes |

|

|

RAM |

|

|

M37905M4C-XXXFP, M37905M4C-XXXSP |

|

1024 bytes |

|||

|

|

|

|

|

|

M37905M6C-XXXFP, M37905M6C-XXXSP |

|

3072 bytes |

|

|

|

|

|

|

|

M37905M8C-XXXFP, M37905M8C-XXXSP |

|

3072 bytes |

|

2: |

|

|

|

|

|

|

|

|

|

Packages |

|

M37905M4C-XXXFP, M37905M6C-XXXFP, M37905M8C-XXXFP |

64-pin plastic molded QFP (64P6N-A) |

||||||

|

|

|

|

|

|

|

|

||

|

|

|

|

M37905M4C-XXXSP, M37905M6C-XXXSP, M37905M8C-XXXSP |

64-pin shrink plastic moldeds DIP (64P4B) |

||||

|

|

|

|

|

|

|

|

|

|

4

|

|

|

|

|

Y |

|

PRELIMINAR |

|

|||||

|

|

|

|

|

. . |

|

|

|

|

|

specification |

change |

|

|

|

|

|

|

to |

|

|

a |

final |

|

subject |

|

|

isnot |

its |

are |

|

|

||

|

|

|

||||

This |

lim |

|

|

|

|

|

etric |

|

|

|

|

|

|

Notice:param |

|

|

|

|

|

|

e |

|

|

|

|

|

|

Som |

|

|

|

|

|

|

MITSUBISHI MICROCOMPUTERS

M37905M4C-XXXFP, M37905M4C-XXXSP M37905M6C-XXXFP, M37905M6C-XXXSP M37905M8C-XXXFP, M37905M8C-XXXSP

16-BIT CMOS MICROCOMPUTER

PIN DESCRIPTION

|

Pin |

|

|

Name |

Input/ |

Functions |

||

|

|

|

Output |

|||||

|

|

|

|

|

|

|

|

|

|

Vcc, Vss |

|

Power supply input |

— |

Apply 5 V±0.5 V to Vcc, and 0 V to Vss. |

|||

|

|

|

|

|

|

|

|

|

|

MD0 |

|

MD0 |

Input |

Connect this pin to VSS. |

|||

|

|

|

|

|

|

|

|

|

|

MD1 |

|

MD1 |

Input |

Connect this pin to Vss. |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

Reset input |

Input |

The microcomputer is reset when “L” level is applies to this pin. |

||

|

RESET |

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

XIN |

|

Clock input |

Input |

These are input and output pins of the internal clock generating circuit. Connect a |

|||

|

|

|

|

|

|

|

|

ceramic resonator or quartz-crystal oscillator between pins XIN and XOUT. When an |

|

XOUT |

|

Clock output |

Output |

||||

|

|

external clock is used, the clock source should be connected to pin XIN, and pin |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

XOUT should be left open. |

|

|

|

|

|

|

|

|

|

|

VCONT |

|

Filter circuit connection |

— |

When using the PLL frequency multiplier, connect this pin to the filter circuit. When |

|||

|

|

|

|

|

|

|

|

not using the PLL frequency multiplier, this pin should be left open. |

|

|

|

|

|

|

|

|

|

|

AVcc, |

|

Analog power supply input |

— |

Power supply input pins for the A-D and D-A converters. Connect AVcc to Vcc, and |

|||

|

AVss |

|

|

|

|

AVss to Vss externally. |

||

|

|

|

|

|

|

|

|

|

|

VREF |

|

Reference voltage input |

Input |

This is the reference voltage input pin for the A-D and D-A converters. |

|||

|

|

|

|

|

|

|

|

|

|

P10–P17 |

|

I/O port P1 |

I/O |

Port P1 is an 8-bit I/O port. This port has an I/O direction register, and each pin can |

|||

|

|

|

|

|

|

|

|

be programmed for input or output. These pins enter the input mode ar reset. These |

|

|

|

|

|

|

|

|

pins also function as I/O pins of UART0, 1. |

|

|

|

|

|

|

|

|

|

|

P20–P27 |

|

I/O port P2 |

I/O |

In addition to having the same functions as port P1, these pins function as I/O pins |

|||

|

|

|

|

|

|

|

|

for timers A4 and A9. Also, they can be programmed to function as input pins for tim- |

|

|

|

|

|

|

|

|

ers B0 to B2. |

|

|

|

|

|

|

|

|

|

|

P40–P47 |

|

I/O port P4 |

I/O |

In addition to having the same functions as port P1, these pins function as I/O pins |

|||

|

|

|

|

|

|

|

|

for timers A5 to A8. Also, they function as output pins for motor drive waveform. |

|

|

|

|

|

|

|||

|

P51–P53, |

|

I/O port P5 |

I/O |

In addition to having the same functions as port P1, these pins function as input pins |

|||

|

P55–P57 |

|

|

|

|

for INT1 to INT3 and INT5 to INT7. Also, pins P55 to P57 function as input pins for |

||

|

|

|

|

|

|

|

|

timers B0 to B2 and as input pins for position data in the three-phase waveform |

|

|

|

|

|

|

|

|

mode; and pins P52 and P53 function as trigger-input pins in the pulse output port |

|

|

|

|

|

|

|

|

mode. |

|

|

|

|

|

|

|

|

|

|

P60–P67 |

|

I/O port P6 |

I/O |

In addition to having the same functions as port P1, these pins function as I/O pins |

|||

|

|

|

|

|

|

|

|

for timers A0 to A3. Also, they function as motor drive waveform output pins. |

|

|

|

|

|

|

|||

|

P70–P77 |

|

I/O port P7 |

I/O |

In addition to having the same functions as port P1, these pins function as input pins |

|||

|

|

|

|

|

|

|

|

for the A-D converter. Also, P77 functions as an output pin for the D-A converter. |

|

|

|

|

|

|

|

|

|

|

P80–P83 |

|

I/O port P8 |

I/O |

In addition to having the same functions as port P1, these pins function as input pins |

|||

|

|

|

|

|

|

|

|

for the A-D converter. Also, these pins function as I/O pins for UART2,and pin P80 |

|

|

|

|

|

|

|

|

functions as an output pin for the D-A converter. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

input |

Input |

This pin has the function to forcibly place port P4 pins in the input mode. Also, this |

|

|

P4OUTCUT |

|

P4OUTCUT |

|||||

|

|

|

|

|

|

|

|

pin functions as an input pin for INT0; and this pin is used to input a signal, which |

|

|

|

|

|

|

|

|

forcibly cuts off a motor drive waveform output. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

input |

Input |

This pin has the function to forcibly place port P6 pins in the input mode. Also, this |

|

P6OUTCUT |

P6OUTCUT |

||||||

|

|

|

|

|

|

|

|

pin functions as an input pin for INT4; and this pin is used to input a signal, which |

|

|

|

|

|

|

|

|

forcibly cuts off a motor drive waveform output. |

|

|

|

|

|

|

|

|

|

5

|

|

|

|

|

|

Y |

|

PRELIMINAR |

|

||||||

|

|

|

|

|

|

. . |

|

|

|

|

|

|

specification |

change |

|

|

|

|

|

|

|

to |

|

|

|

|

a |

final |

|

subject |

|

|

is |

not |

are |

|

|

||

|

limits |

|

|

|

|||

This |

|

|

|

|

|||

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

Notice:parametric |

|

|

|

|

|

||

Some |

|

|

|

|

|

|

|

MITSUBISHI MICROCOMPUTERS

M37905M4C-XXXFP, M37905M4C-XXXSP M37905M6C-XXXFP, M37905M6C-XXXSP M37905M8C-XXXFP, M37905M8C-XXXSP

16-BIT CMOS MICROCOMPUTER

BASIC FUNCTION BLOCKS

These microcomputers contain the following devices in the single chip: ROM, RAM, CPU, bus interface unit, and peripheral devices such as the interrupt control circuit, timers, serial I/O, A-D converter, D-A converter, I/O ports, clock generating circuit, etc.

MEMORY

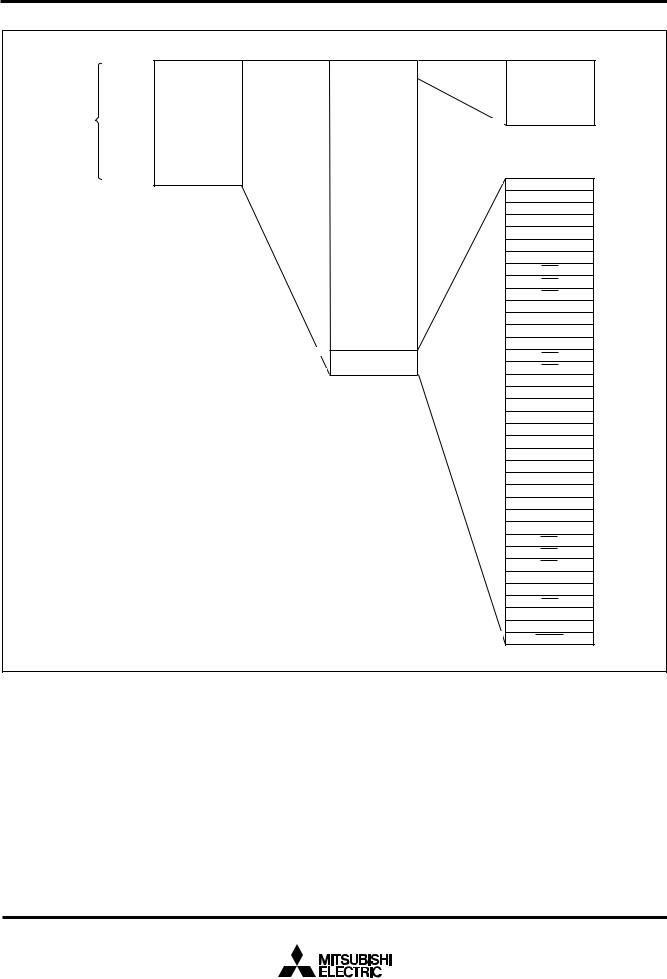

Figures 1 (1) through (3) show the memory maps. The address space is 64 Kbytes from addresses 016 through FFFF16. This ad-

dress space is called “bank 016”.

The internal ROM and RAM are allocated as shown in Figures 1 (1) through (3).

Addresses FFB416 through FFFF16 contain the RESET and the interrupt vector addresses, and the interrupt vectors are stored there. For details, refer to the section on interrupts.

Allocated to addresses 016 through FF16 are peripheral devices such as I/O ports, A-D converter, D-A converter, serial I/O, timers, interrupt control registers, etc. Figures 2 and 3 show the location of SFRs.

00000016

Bank 016

00FFFF16

00000016 |

Peripheral devices' |

0000FF16 |

control registers |

00010016 |

Unused area |

|

000BFF16 |

||

|

||

000C0016 |

|

|

|

Internal RAM |

|

|

1024 bytes |

|

000FFF16 |

|

|

00100016 |

Unused area |

|

007FFF16 |

||

|

||

00800016 |

|

Internal ROM

32 Kbytes

00FFB416

00FFFF16

00000016

0000FF16

00FFB416

00FFFE16

Peripheral devices' control registers (See Figures 2 and 3.)

Interrupt vector table UART2 transmit

UART2 receive

Timer A9

Timer A8

Timer A7

Timer A6

Timer A5

INT7

INT6

INT5

Reserved area

Address matching detect

Reserved area

Reserved area

INT4

INT3

A-D conversion

UART1 transmit

UART1 receive

UART0 transmit

UART0 receive

Timer B2

Timer B1

Timer B0

Timer A4

Timer A3

Timer A2

Timer A1

Timer A0

INT2

INT1

INT0

Received area

Watchdog timer

DBC

BRK instruction

Zero divide

RESET

Fig. 1 (1) Memory map of M37905M4C-XXXFP/SP (Single-chip mode)

6

|

|

|

|

|

|

Y |

|

PRELIMINAR |

|

||||||

|

|

|

|

|

|

. . |

|

|

|

|

|

|

specification |

change |

|

|

|

|

|

|

|

to |

|

|

|

|

a |

final |

|

subject |

|

|

is |

not |

are |

|

|

||

|

|

|

|

||||

|

limits |

|

|

|

|||

This |

|

|

|

|

|||

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

Notice:parametric |

|

|

|

|

|

||

Some |

|

|

|

|

|

|

|

00000016

Bank 016

00FFFF16

MITSUBISHI MICROCOMPUTERS

M37905M4C-XXXFP, M37905M4C-XXXSP M37905M6C-XXXFP, M37905M6C-XXXSP M37905M8C-XXXFP, M37905M8C-XXXSP

16-BIT CMOS MICROCOMPUTER

00000016 |

Peripheral devices' |

0000FF16 |

control registers |

00010016 |

Unused area |

|

0003FF16 |

||

|

||

00040016 |

|

|

|

Internal RAM |

|

|

3072 bytes |

|

000FFF16 |

|

|

00100016 |

Unused area |

|

003FFF16 |

||

|

||

00400016 |

|

Internal ROM

48 Kbytes

00FFB416

00FFFF16

00000016

0000FF16

00FFB416

00FFFE16

Peripheral devices' control registers (See Figures 2 and 3.)

Interrupt vector table UART2 transmit

UART2 receive

Timer A9

Timer A8

Timer A7

Timer A6

Timer A5

INT7

INT6

INT5

Reserved area

Address matching detect

Reserved area

Reserved area

INT4

INT3

A-D conversion

UART1 transmit

UART1 receive

UART0 transmit

UART0 receive

Timer B2

Timer B1

Timer B0

Timer A4

Timer A3

Timer A2

Timer A1

Timer A0

INT2

INT1

INT0

Reserved area

Watchdog timer

DBC

BRK instruction

Zero divide

RESET

Fig. 1 (2) Memory map of M37905M6C-XXXFP/SP (Single-chip mode)

7

|

|

|

|

|

|

Y |

|

PRELIMINAR |

|

||||||

|

|

|

|

|

|

. . |

|

|

|

|

|

|

specification |

change |

|

|

|

|

|

|

|

to |

|

|

|

|

a |

final |

|

subject |

|

|

is |

not |

are |

|

|

||

|

limits |

|

|

|

|||

This |

|

|

|

|

|||

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

Notice:parametric |

|

|

|

|

|

||

Some |

|

|

|

|

|

|

|

00000016

Bank 016

00FFFF16

MITSUBISHI MICROCOMPUTERS

M37905M4C-XXXFP, M37905M4C-XXXSP M37905M6C-XXXFP, M37905M6C-XXXSP M37905M8C-XXXFP, M37905M8C-XXXSP

16-BIT CMOS MICROCOMPUTER

00000016 Peripheral devices' 0000FF16 control registers

00010016

Unused area

0003FF16 00040016

Internal RAM

3072 bytes

000FFF16 00100016

Internal ROM

60 Kbytes

00FFB416

00FFFF16

00000016

0000FF16

00FFB416

00FFFE16

Peripheral devices' control registers (See Figures 2 and 3.)

Interrupt vector table UART2 transmit

UART2 receive

Timer A9

Timer A8

Timer A7

Timer A6

Timer A5

INT7

INT6

INT5

Reserved area

Address matching detect

Reserved area

Reserved area

INT4

INT3

A-D conversion

UART1 transmit

UART1 receive

UART0 transmit

UART0 receive

Timer B2

Timer B1

Timer B0

Timer A4

Timer A3

Timer A2

Timer A1

Timer A0

INT2

INT1

INT0

Reserved area

Watchdog timer

DBC

BRK instruction

Zero divide

RESET

Fig. 1 (3) Memory map of M37905M8C-XXXFP/SP (Single-chip mode)

8

|

|

|

|

|

|

Y |

|

PRELIMINAR |

|

||||||

|

|

|

|

|

|

. . |

|

|

|

|

|

|

specification |

change |

|

|

|

|

|

|

|

to |

|

|

|

|

a |

final |

|

subject |

|

|

is |

not |

are |

|

|

||

|

|

|

|

||||

|

limits |

|

|

|

|||

This |

|

|

|

|

|||

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

Notice:parametric |

|

|

|

|

|

||

Some |

|

|

|

|

|

|

|

MITSUBISHI MICROCOMPUTERS

M37905M4C-XXXFP, M37905M4C-XXXSP M37905M6C-XXXFP, M37905M6C-XXXSP M37905M8C-XXXFP, M37905M8C-XXXSP

16-BIT CMOS MICROCOMPUTER

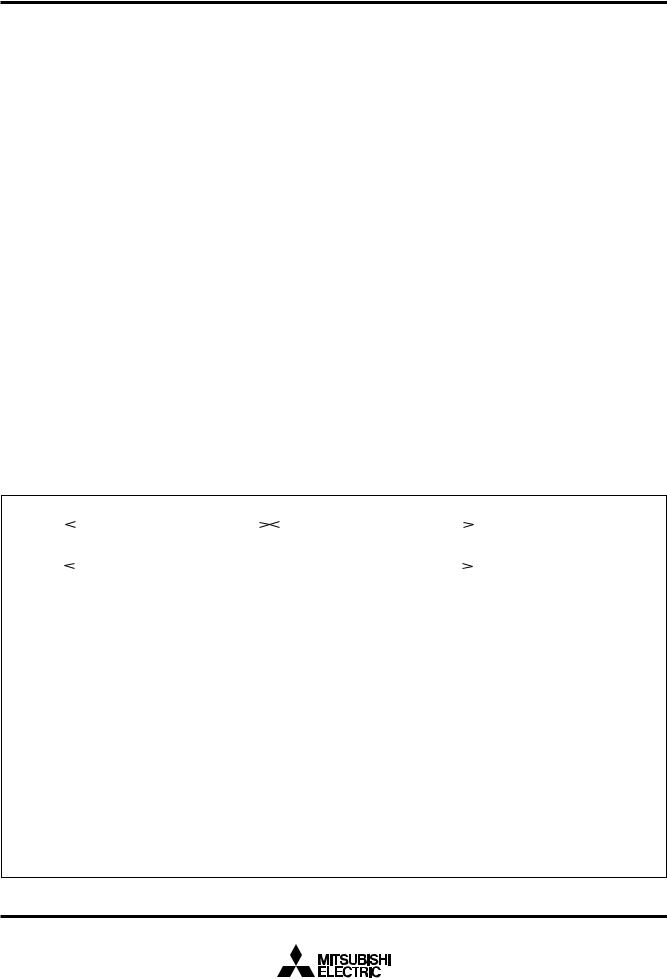

Address (Hexadecimel notation)

00000016

00000116

00000216

00000316

00000416

00000516

00000616

00000716

00000816

00000916

00000A16

00000B16

00000C16

00000D16

00000E16

00000F16

00001016

00001116

00001216

00001316

00001416

00001516

00001616

00001716

00001816

00001916

00001A16

00001B16

00001C16

00001D16

00001E16

00001F16

00002016

00002116

00002216

00002316

00002416

00002516

00002616

00002716

00002816

00002916

00002A16

00002B16

00002C16

00002D16

00002E16

00002F16

00003016

00003116

00003216

00003316

00003416

00003516

00003616

00003716

00003816

00003916

00003A16

00003B16

00003C16

00003D16

00003E16

00003F16

Reserved area (Note)

Reserved area (Note)

Reserved area (Note)

Port P1 register

Reserved area (Note)

Port P1 direction register

Port P2 register

Reserved area (Note)

Port P2 direction register

Reserved area (Note)

Port P4 register

Port P5 register

Port P4 direction register

Port P5 direction register

Port P6 register

Port P7 register

Port P6 direction register

Port P7 direction register

Port P8 register

Port P8 direction register

Reserved area (Note)

Reserved area (Note)

Reserved area (Note)

Reserved area (Note)

A-D control register 0

A-D control register 1

A-D register 0

A-D register 1

A-D register 2

A-D register 3

A-D register 4

A-D register 5

A-D register 6

A-D register 7

UART0 transmit/receive mode register

UART0 band rate register (BRG0)

UART0 transmit buffer register

UART0 transmit/receive control register 0

UART0 transmit/receive control register 1

UART0 receive buffer register

UART1 transmit/receive mode register

UART1 baud rate register (BRG1)

UART1 transmit buffer register

UART1 transmit/receive control register 0

UART1 transmit/receive control register 1

UART1 receive buffer register

Address (Hexadecimel notation)

00004016

00004116

00004216

00004316

00004416

00004516

00004616

00004716

00004816

00004916

00004A16

00004B16

00004C16

00004D16

00004E16

00004F16

00005016

00005116

00005216

00005316

00005416

00005516

00005616

00005716

00005816

00005916

00005A16

00005B16

00005C16

00005D16

00005E16

00005F16

00006016

00006116

00006216

00006316

00006416

00006516

00006616

00006716

00006816

00006916

00006A16

00006B16

00006C16

00006D16

00006E16

00006F16

00007016

00007116

00007216

00007316

00007416

00007516

00007616

00007716

00007816

00007916

00007A16

00007B16

00007C16

00007D16

00007E16

00007F16

Count start register 0

Count start register 1

One-shot start register 0

One-shot start register 1

Up-down register 0

Timer A clock division select register

Timer A0 register

Timer A1 register

Timer A2 register

Timer A3 register

Timer A4 register

Timer B0 register

Timer B1 register

Timer B2 register

Timer A0 mode register

Timer A1 mode register

Timer A2 mode register

Timer A3 mode register

Timer A4 mode register

Timer B0 mode register

Timer B1 mode register

Timer B2 mode register

Processor mode register 0

Processor mode register 1

Watchdog timer register

Watchdog timer frequency select register

Particular function select register 0

Particular function select register 1

Particular function select register 2

Reserved area (Note)

Debug control register 0

Debug control register 1

Address comparison register 0

Address comparison register 1

INT3 interrupt control register

INT4 interrupt control register

A-D conversion interrupt control register

UART0 transmit interrupt control register

UART0 receive interrupt control register

UART1 transmit interrupt control register

UART1 receive interrupt control register

Timer A0 interrupt control register

Timer A1 interrupt control register

Timer A2 interrupt control register

Timer A3 interrupt control register

Timer A4 interrupt control register

Timer B0 interrupt control register

Timer B1 interrupt control register

Timer B2 interrupt control register

INT0 interrupt control register

INT1 interrupt control register

INT2 interrupt control register

Note: Do not write to this address.

Fig. 2 Location of SFRs (1)

9

|

|

|

|

|

|

Y |

|

PRELIMINAR |

|

||||||

|

|

|

|

|

|

. . |

|

|

|

|

|

|

specification |

change |

|

|