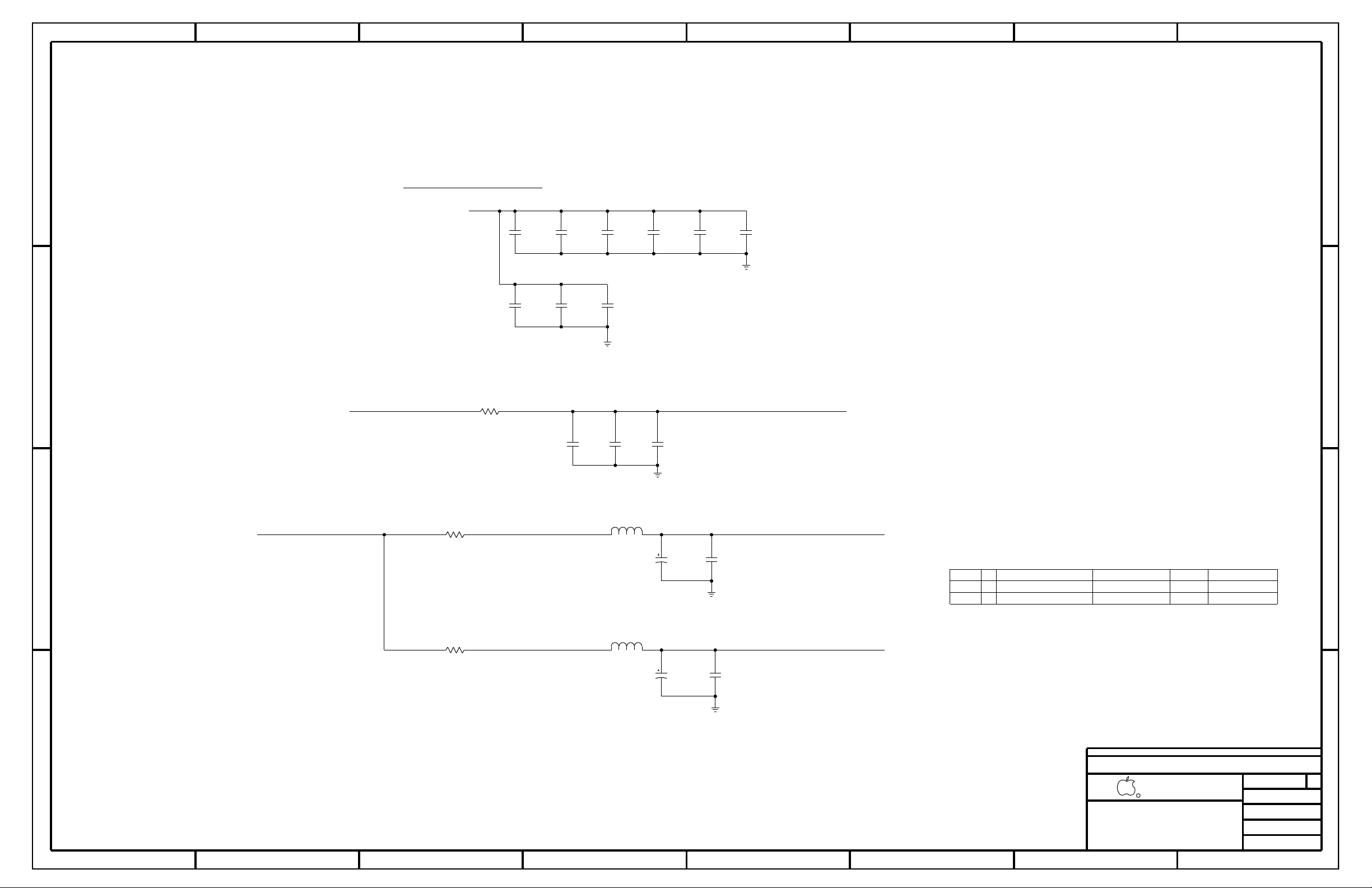

2. ALL CAPACITANCE VALUES ARE IN MICROFARADS.

PROPRIETARY PROPERTY OF APPLE INC.

3. ALL CRYSTALS & OSCILLATOR VALUES ARE IN HERTZ.

DESCRIPTION OF REVISION

CK

APPD

2 1

1245678

B

D

6 5 4 3

C

A

NOTICE OF PROPRIETARY PROPERTY:

PAGE

THE INFORMATION CONTAINED HEREIN IS THE

C

A

D

DATE

R

SHEET

Apple Inc.

THE POSESSOR AGREES TO THE FOLLOWING:

DRAWING TITLE

D

SIZE

REVISION

DRAWING NUMBER

BRANCH

REV ECN

7

B

3

II NOT TO REPRODUCE OR COPY IT

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

IV ALL RIGHTS RESERVED

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

1. ALL RESISTANCE VALUES ARE IN OHMS, 0.1 WATT +/- 5%.

8

TABLE_TABLEOFCONTENTS_ITEM

CRITICAL BOM OPTION

TABLE_5_HEAD

PART#

DESCRIPTION

QTY

REFERENCE DESIGNATOR(S)

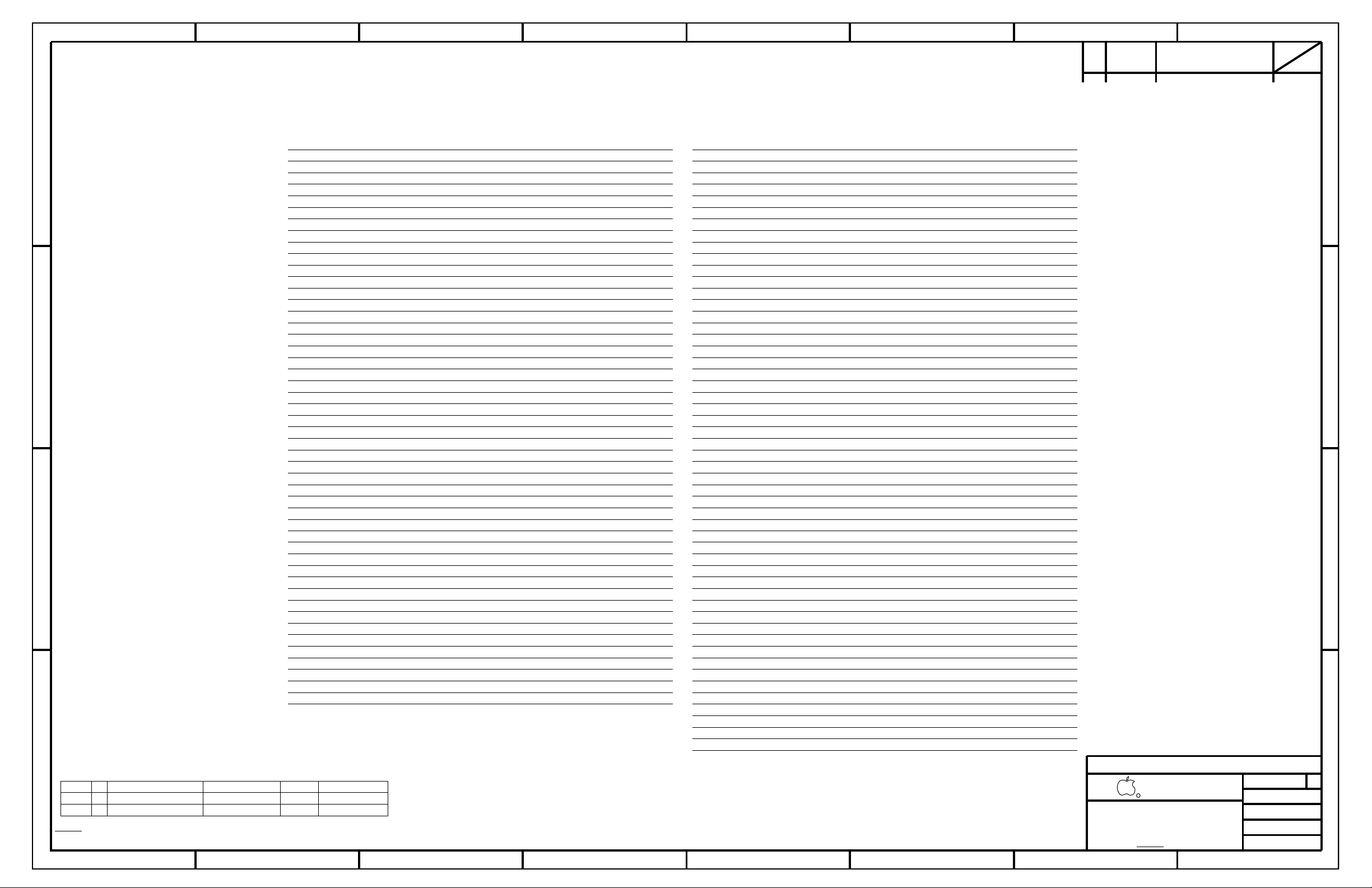

TABLE_TABLEOFCONTENTS_HEAD

TABLE_5_ITEM

TABLE_5_ITEM

DRAWING

DRAWING

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_HEAD

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

D7 MLB

Schematic / PCB #’s

1 OF 100

2012-01-12

1 OF 113

4.2.0

051-9509

LAST_MODIFIED=Thu Jan 12 10:24:09 2012

LAST_MODIFIED=Thu Jan 12 10:24:09 2012

SCH,D7,MLB

49

11/30/2011

K70_MLB

54

I and V Sense(Development)

Contents

Page Sync

Date

(.csa)

CRITICAL

SCH

1

051-9509 SCH,MLB,D7

CRITICAL

PCB

1

820-3302

PCBF,MLB,D7

ABBREV=DRAWING

TITLE=D7

1

K70_MLB

11/30/2011

1

Table of Contents

(.csa)

Date

SyncPage

Contents

50

12/13/2011

D7_DOUG

55

Temperature Sensors

51

11/30/2011

K70_MLB

56

System Fan

52

01/03/2012

D7_BREECE

61

AUDIO: CODEC/REGULATORS

53

01/03/2012

D7_BREECE

62

AUDIO: HEADPHONE AMP

54

01/03/2012

D7_BREECE

63

AUDIO: LEFT SPKR AMP

55

01/03/2012

D7_BREECE

64

AUDIO: RIGHT SPKR AMP

56

01/03/2012

D7_BREECE

65

AUDIO: Jack, Mikey, CHS Switch

57

01/03/2012

D7_BREECE

66

Audio: Spkr/Mic Conn.

58

01/03/2012

D7_BREECE

67

AUDIO: Detects/Grounding

59

01/03/2012

D7_BREECE

68

AUDIO: Speaker ID

60

12/13/2011

D7_NICK

69

PM Regulator Enables

61

12/13/2011

D7_NICK

70

PM Power Good

62

01/04/2012

D7_NICK

71

VReg CPU Core/AXG Cntl

63

01/04/2012

D7_NICK

72

VReg CPU Core Phases

64

01/04/2012

D7_NICK

73

VReg CPU AXG Phases

65

01/04/2012

D7_NICK

74

VReg CPU/PCH 1.05V S0

66

01/04/2012

D7_NICK

75

VReg CPU VccSA S0

67

01/04/2012

D7_NICK

76

VReg 3.3V S5/5V S4

68

01/04/2012

D7_NICK

77

VReg VDDQ and 1.8V S0

69

01/04/2012

D7_NICK

78

VReg G3Hot

70

01/04/2012

D7_NICK

79

FET-Controlled S0 and S4

71

01/10/2012

D7_TONY

80

KEPLER PCI-E

72

01/10/2012

D7_TONY

81

KEPLER CORE/FB POWER

73

01/10/2012

D7_TONY

82

KEPLER FRAME BUFFER I/F

74

01/03/2012

D7_NICK

83

1V05 GPU POWER SUPPLY

75

12/13/2011

D7_TONY

84

GDDR5 Frame Buffer A

76

12/13/2011

D7_TONY

85

GDDR5 Frame Buffer B

77

12/13/2011

D7_TONY

86

KEPLER EDP/DP/GPIO

78

01/10/2012

D7_TONY

87

KEPLER GPIOS,CLK & STRAPS

79

01/10/2012

D7_TONY

88

KEPLER PEX PWR/GNDS

80

01/03/2012

D7_NICK

89

VReg GPU Core

81

11/30/2011

K70_MLB

91

Internal DP Support

82

12/14/2011

D7_NICK

92

Internal DP MUXing

83

12/15/2011

D7_DOUG

93

TBT DDC Crossbar

84

12/15/2011

D7_DOUG

94

Thunderbolt Connector A

85

12/15/2011

D7_DOUG

96

Thunderbolt Connector B

86

01/03/2012

D7_NICK

97

LCD Backlight Driver (LP8545)

87

12/12/2011

D7_DAVE

100

K70 Rule Definitions

88

12/12/2011

D7_DAVE

101

DDR3 Constraints

89

12/12/2011

D7_DAVE

102

CPU PCIe Constraints

90

12/12/2011

D7_DAVE

103

PCH PCIe/DMI Constaints

91

12/12/2011

D7_DAVE

104

SATA/FDI/XDP Constraints

92

12/12/2011

D7_DAVE

105

PCH and BR Constraints

93

12/12/2011

D7_DAVE

106

USB/Ethernet/SD Constraints

94

01/03/2012

D7_DOUG

107

SMBus/Sensor Constraints

95

12/12/2011

D7_DAVE

108

VReg Constraints

96

12/12/2011

D7_DAVE

109

CPU VReg Constraints

97

12/12/2011

D7_DAVE

110

Platform VReg Constraints

98

12/13/2011

D7_NICK

111

TBT/DP Constraints

99

12/12/2011

D7_DAVE

112

GDDR5/GPU Constraints

100

12/12/2011

D7_DAVE

113

BLC Constraints

2

K70_MLB

11/30/2011

2

System Block Diagram

3

D7_NICK

01/03/2012

3

Power Block Diagram

4

D7_NICK

12/13/2011

4

BOM Configuration

5

K70_MLB

11/30/2011

5

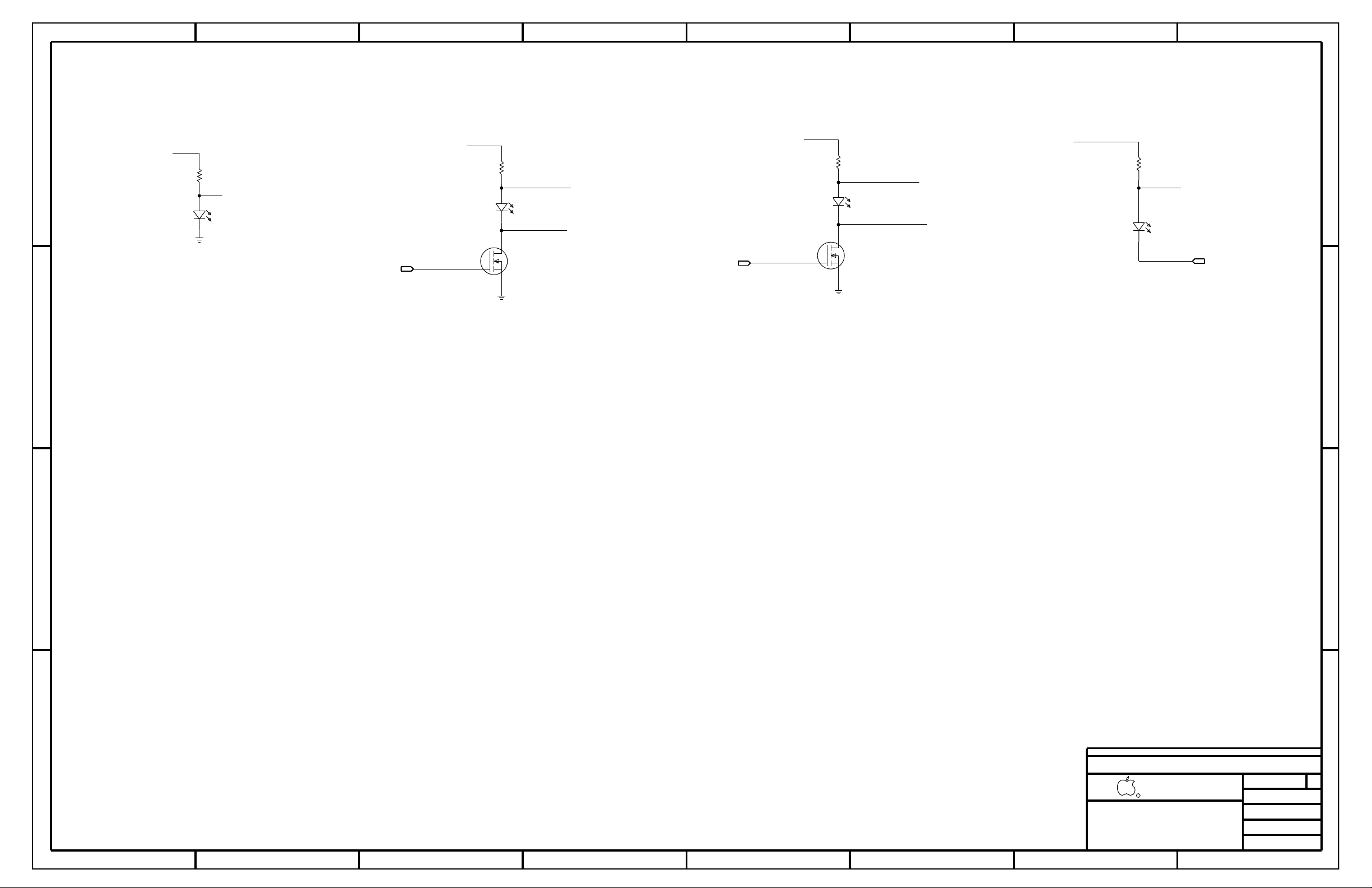

DEBUG LEDS

6

D7_NICK

01/11/2012

6

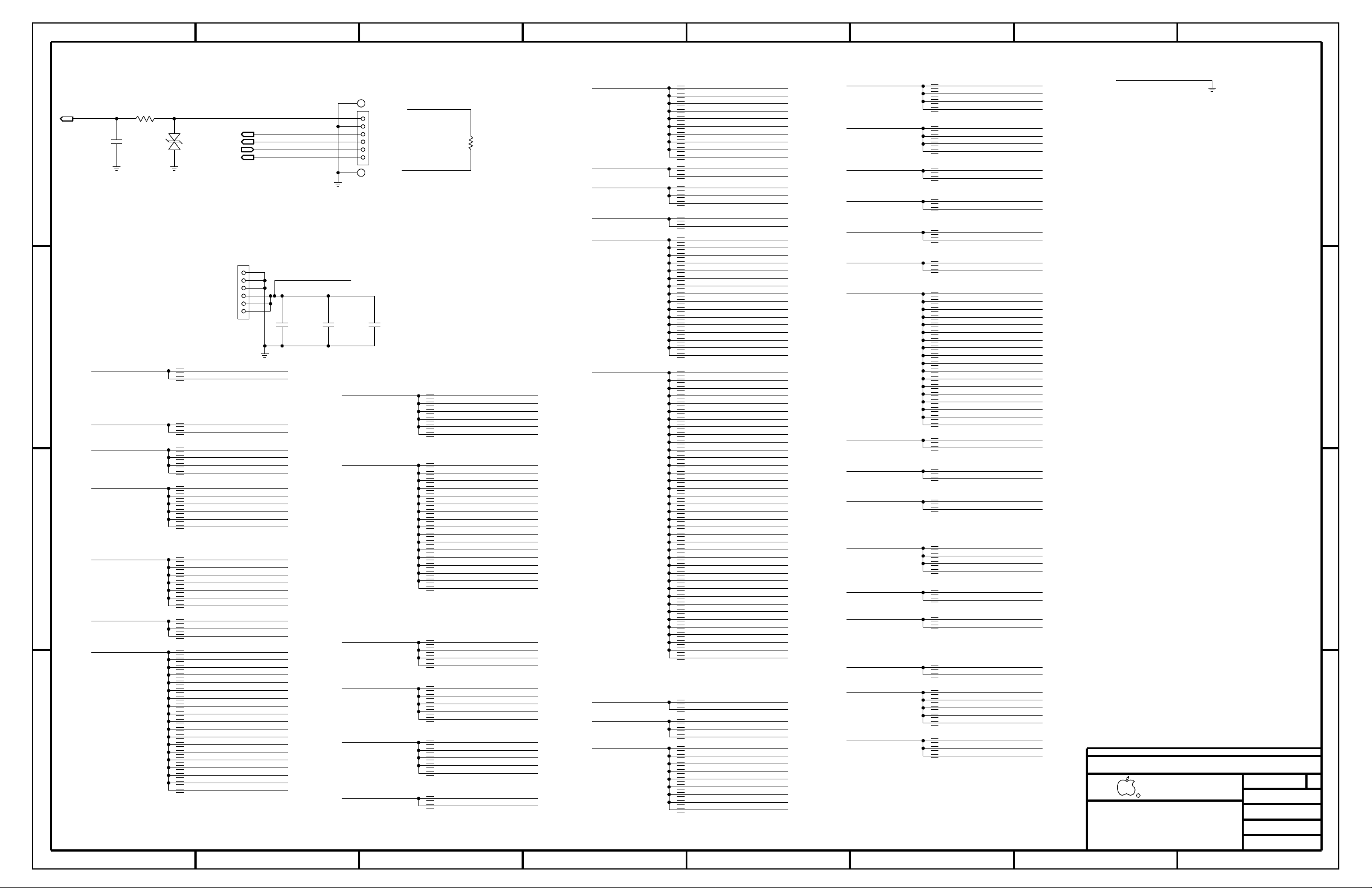

Power Connectors/Aliases

7

K70_MLB

11/30/2011

7

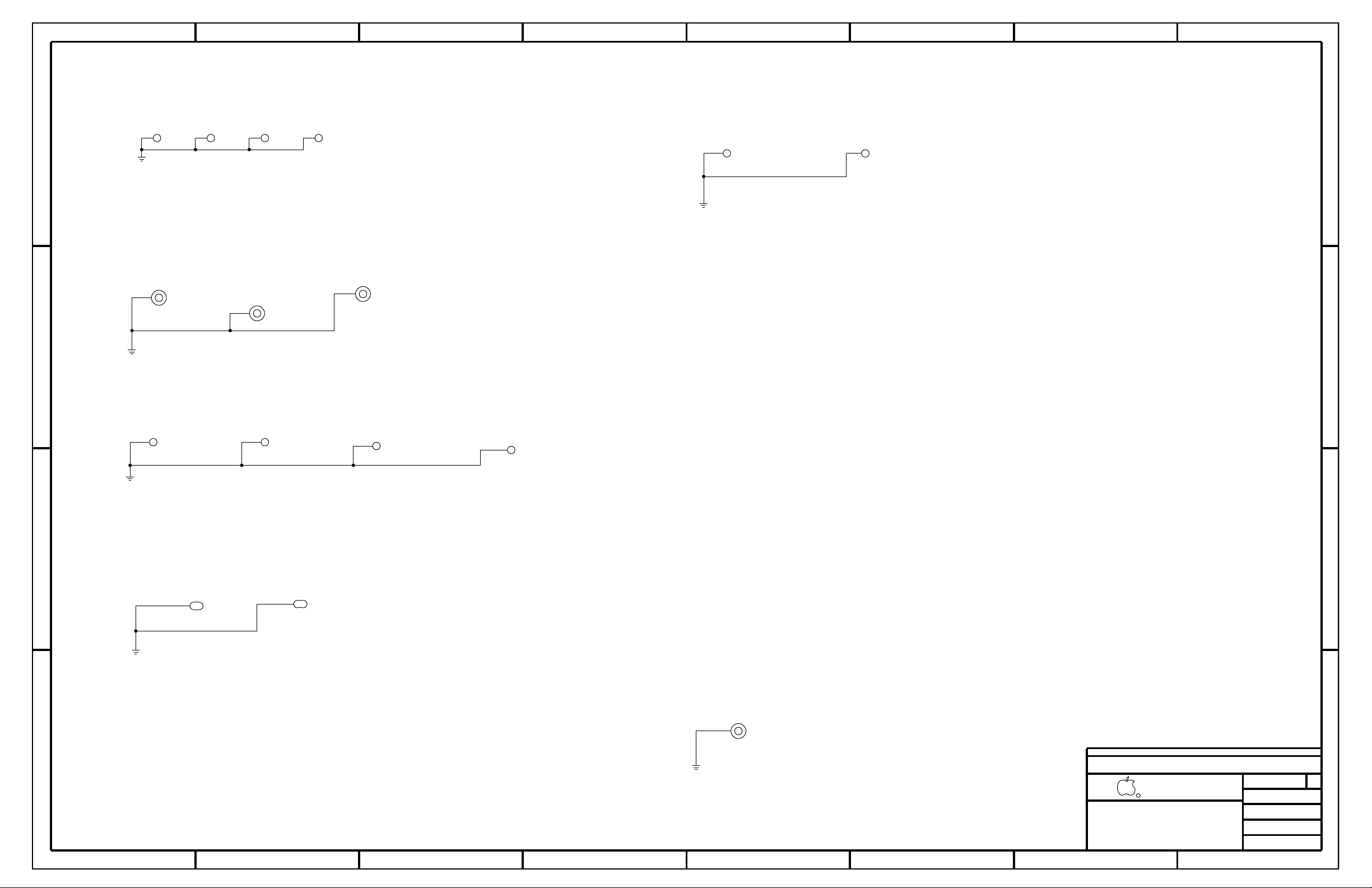

Holes/PD parts

8

K70_MLB

11/30/2011

8

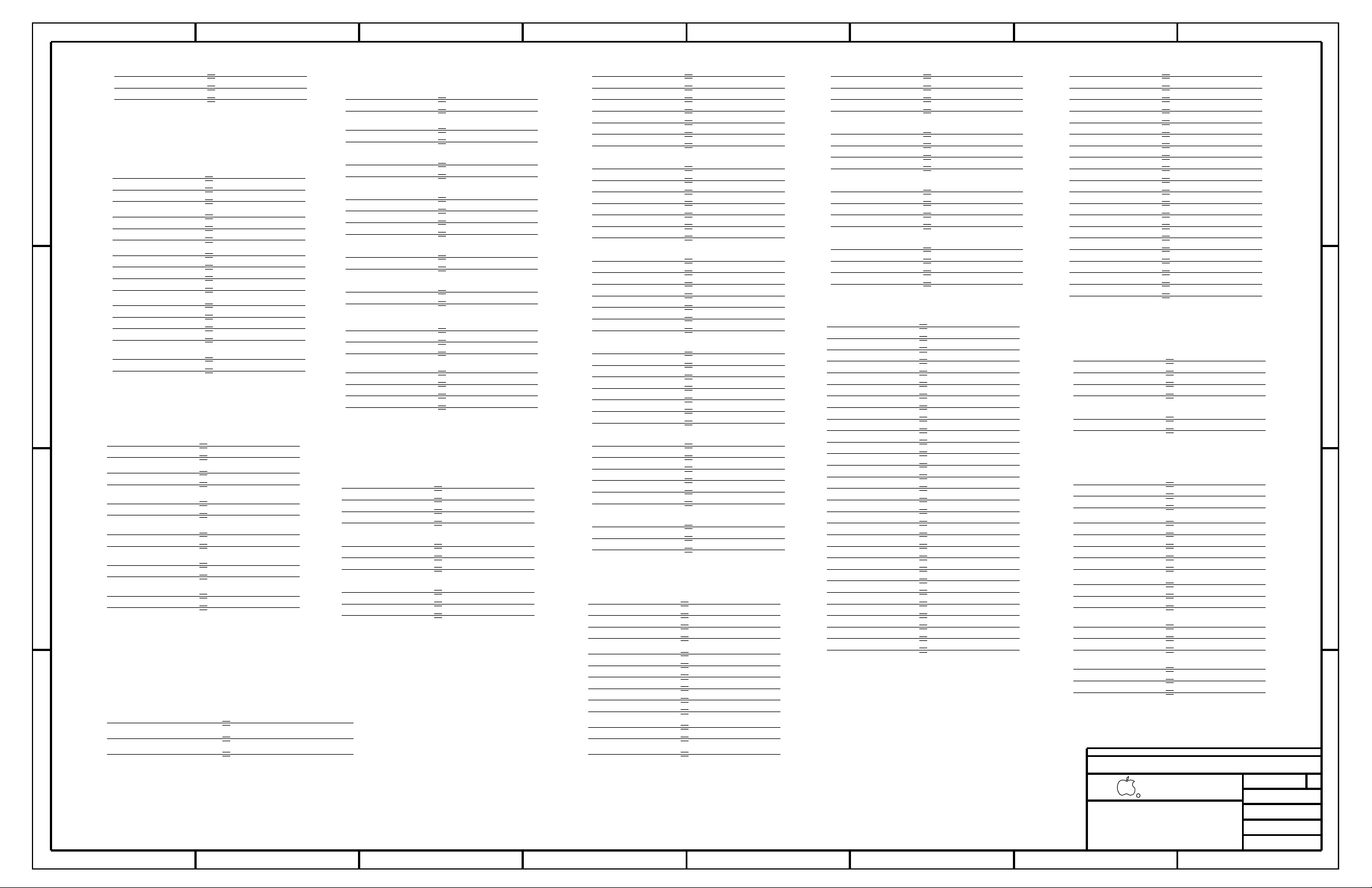

Unused Signal Aliases

9

K70_MLB

11/30/2011

9

Signal Aliases

10

K70_MLB

11/30/2011

10

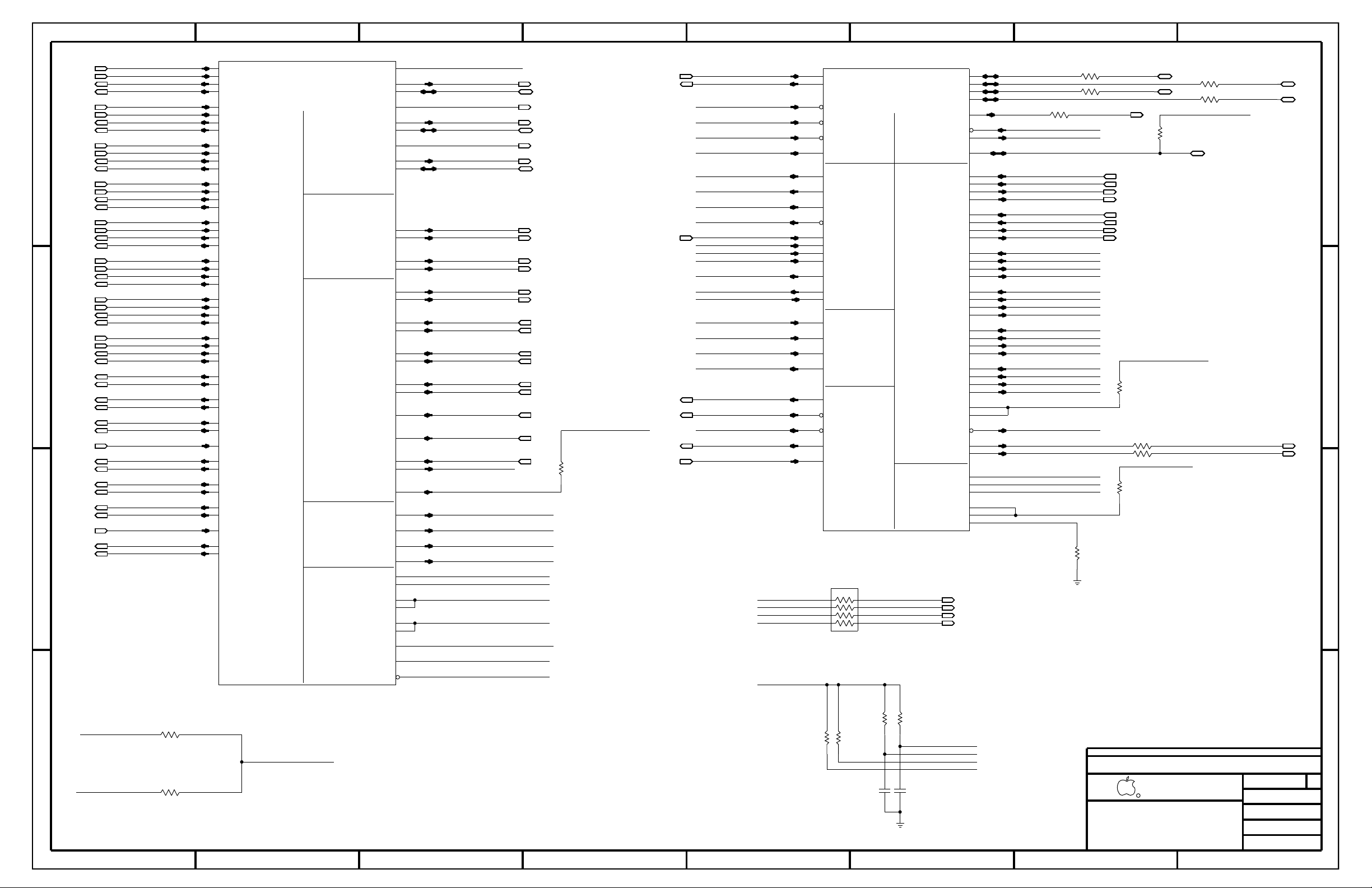

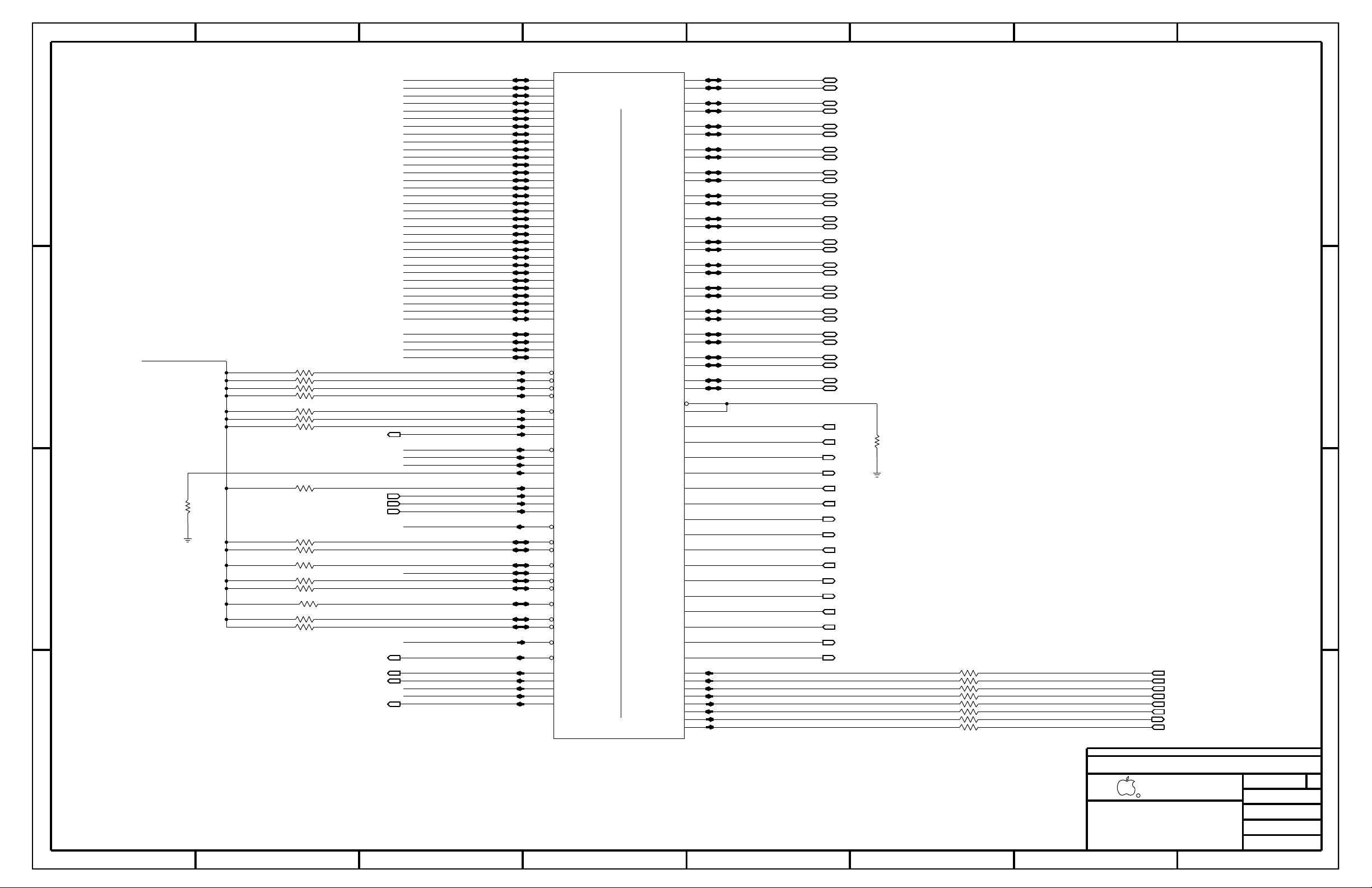

CPU DMI/PEG/FDI/RSVD

11

K70_MLB

11/30/2011

11

CPU CLOCK/MISC/JTAG

12

K70_MLB

11/30/2011

12

CPU DDR3 INTERFACES

13

K70_MLB

11/30/2011

13

CPU POWER

14

K70_MLB

11/30/2011

14

CPU GROUNDS

15

D7_TONY

01/11/2012

15

STRAPS,PULL UPS,PULL DOWNS FOR PCH AND CPU

16

K70_MLB

11/30/2011

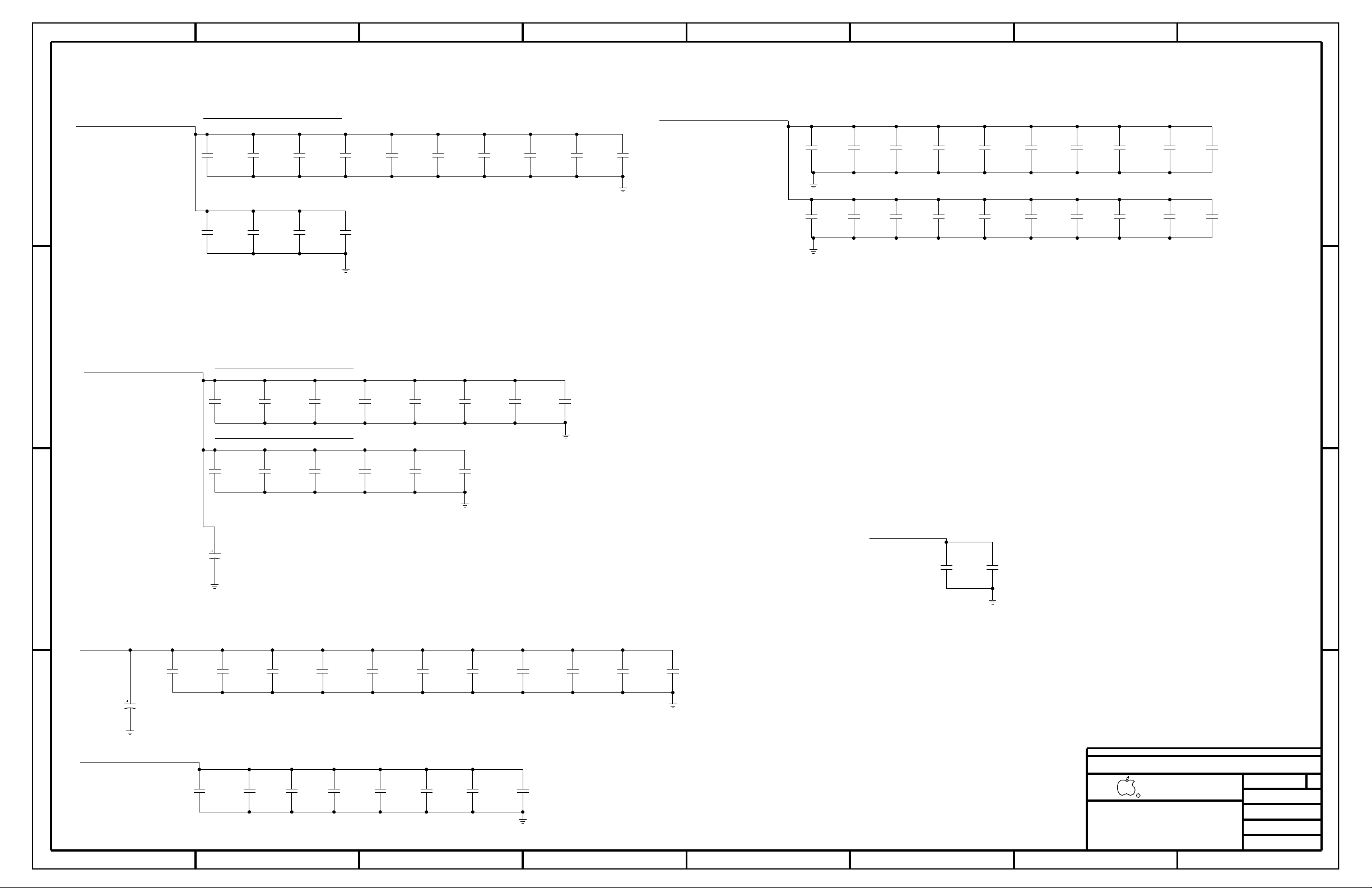

16

CPU NON-GFX DECOUPLING

17

K70_MLB

11/30/2011

17

GFX DECOUPLING & PCH PWR ALIAS

18

K70_MLB

11/30/2011

18

PCH SATA/PCIE/CLK/LPC/SPI

19

K70_MLB

11/30/2011

19

PCH DMI/FDI/GRAPHICS

20

K70_MLB

11/30/2011

20

PCH PCI/USB

21

D7_TONY

01/11/2012

21 PCH MISC

22

K70_MLB

11/30/2011

22

PCH POWER

23

K70_MLB

11/30/2011

23

PCH GROUNDS

24

K70_MLB

11/30/2011

24

PCH DECOUPLING

25

K70_MLB

11/30/2011

25

CPU and PCH XDP

26

K70_MLB

11/30/2011

26

CHIPSET SUPPORT

27

D7_NICK

12/13/2011

27 USB HUB

28

K70_MLB

11/30/2011

28

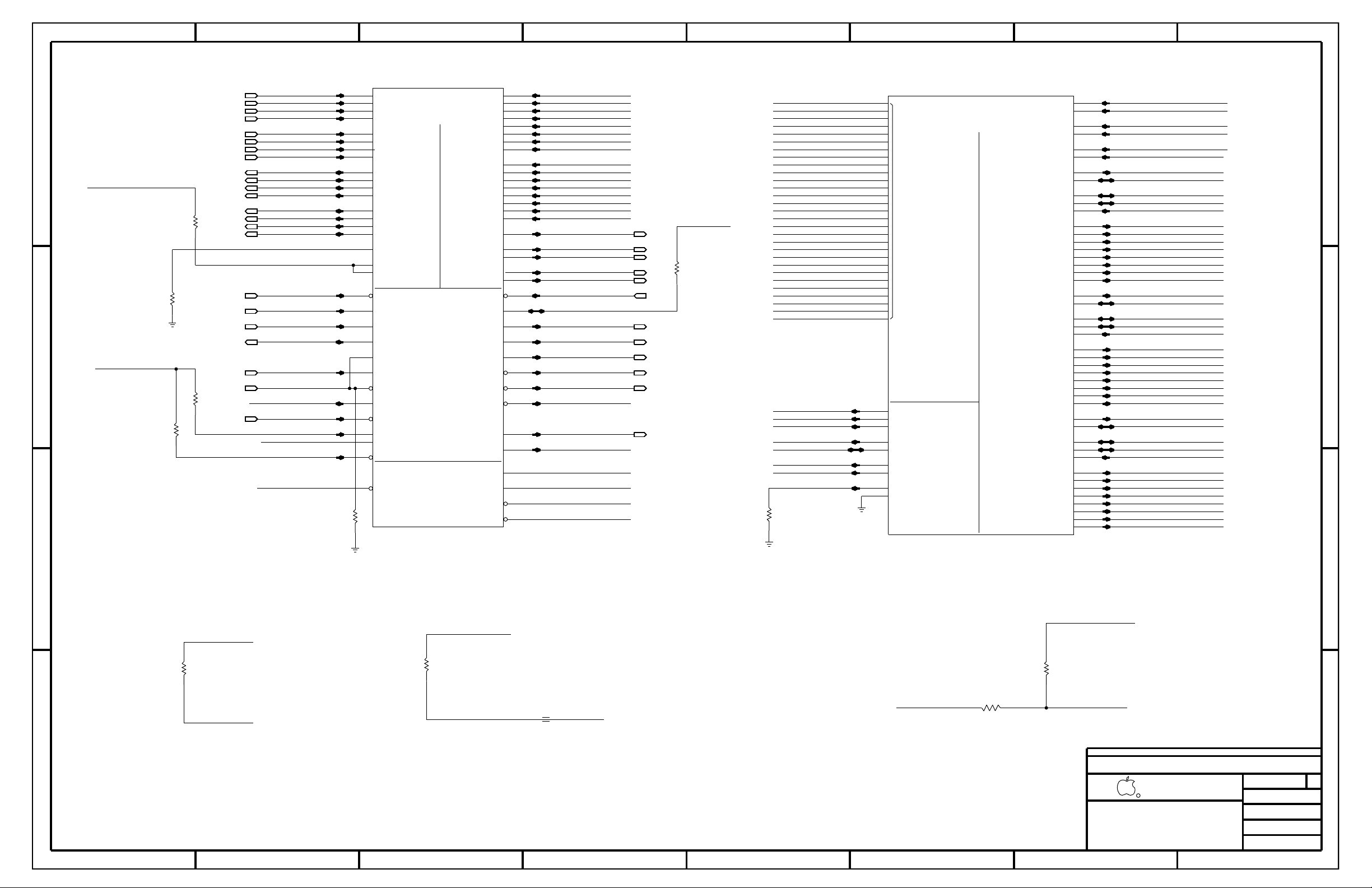

CPU Memory S3 Support

29

K70_MLB

11/30/2011

29

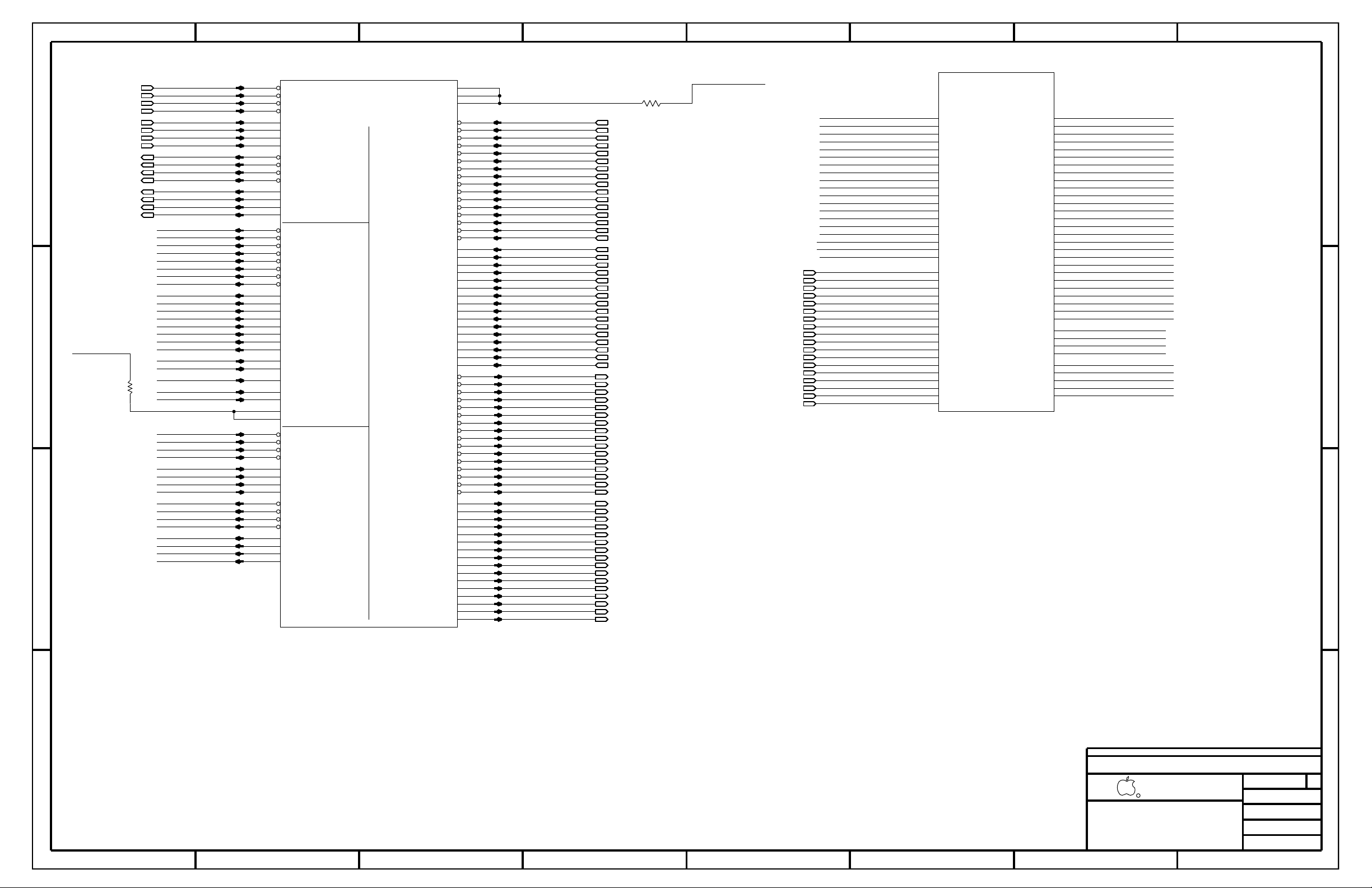

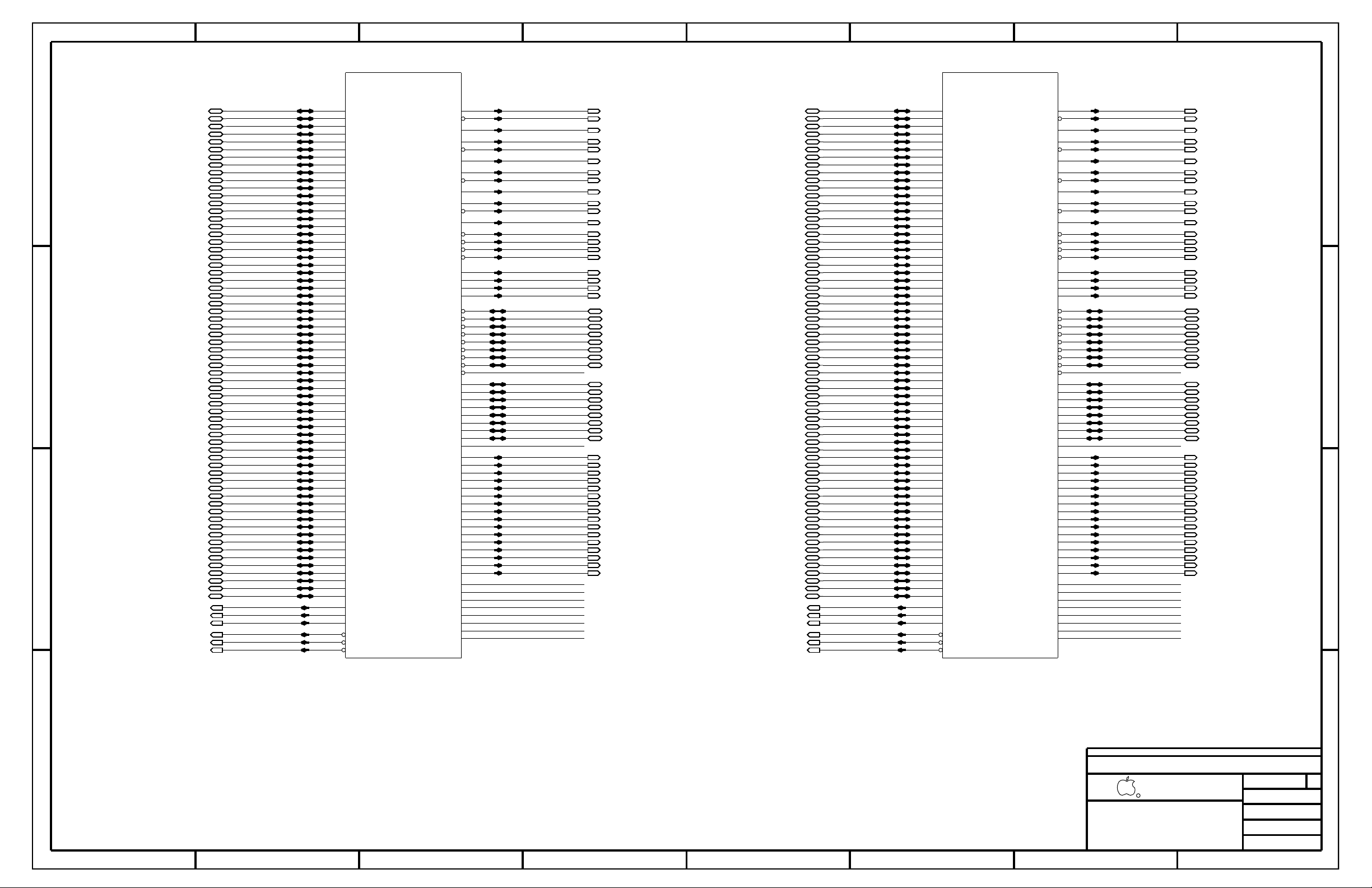

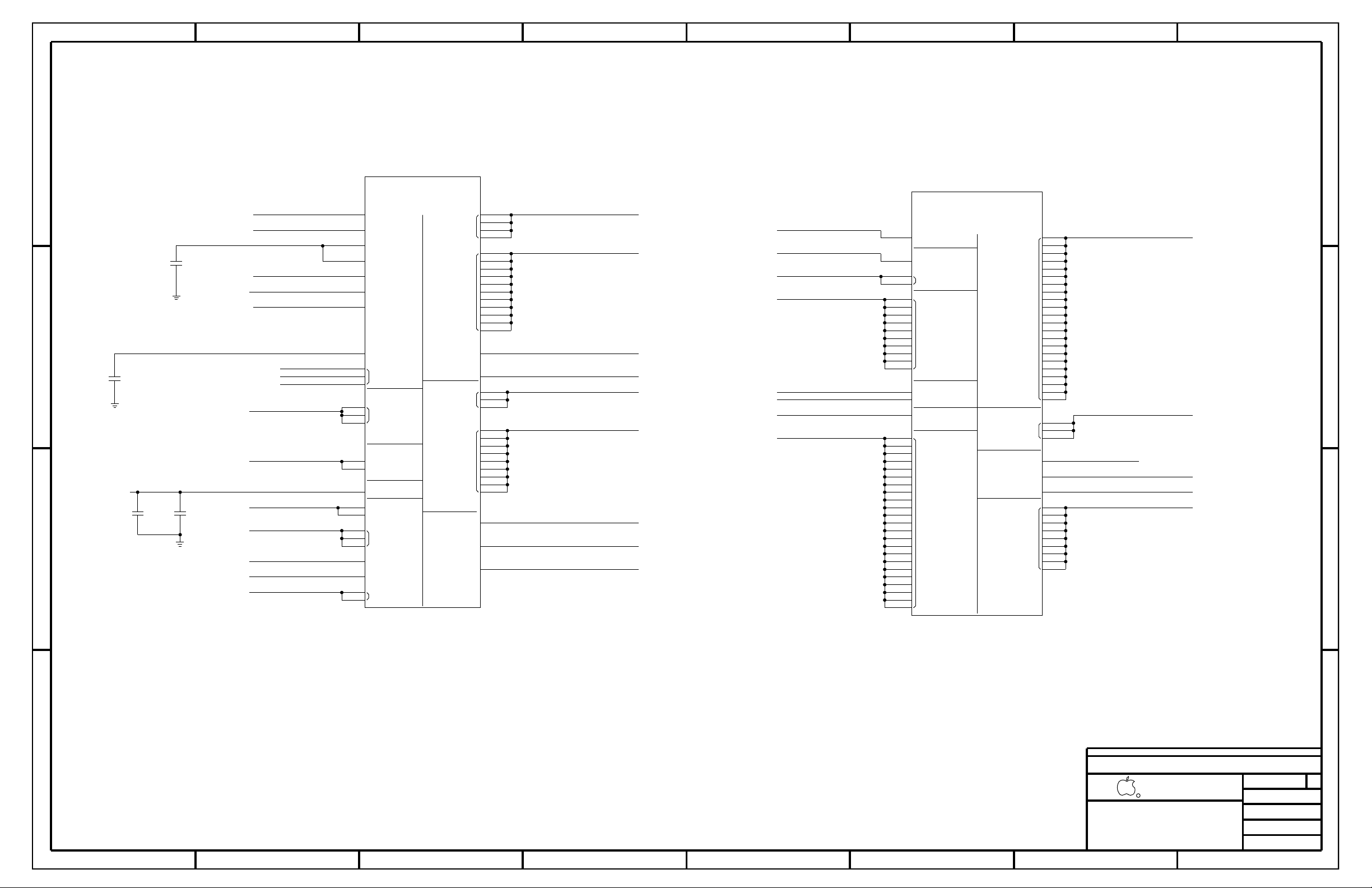

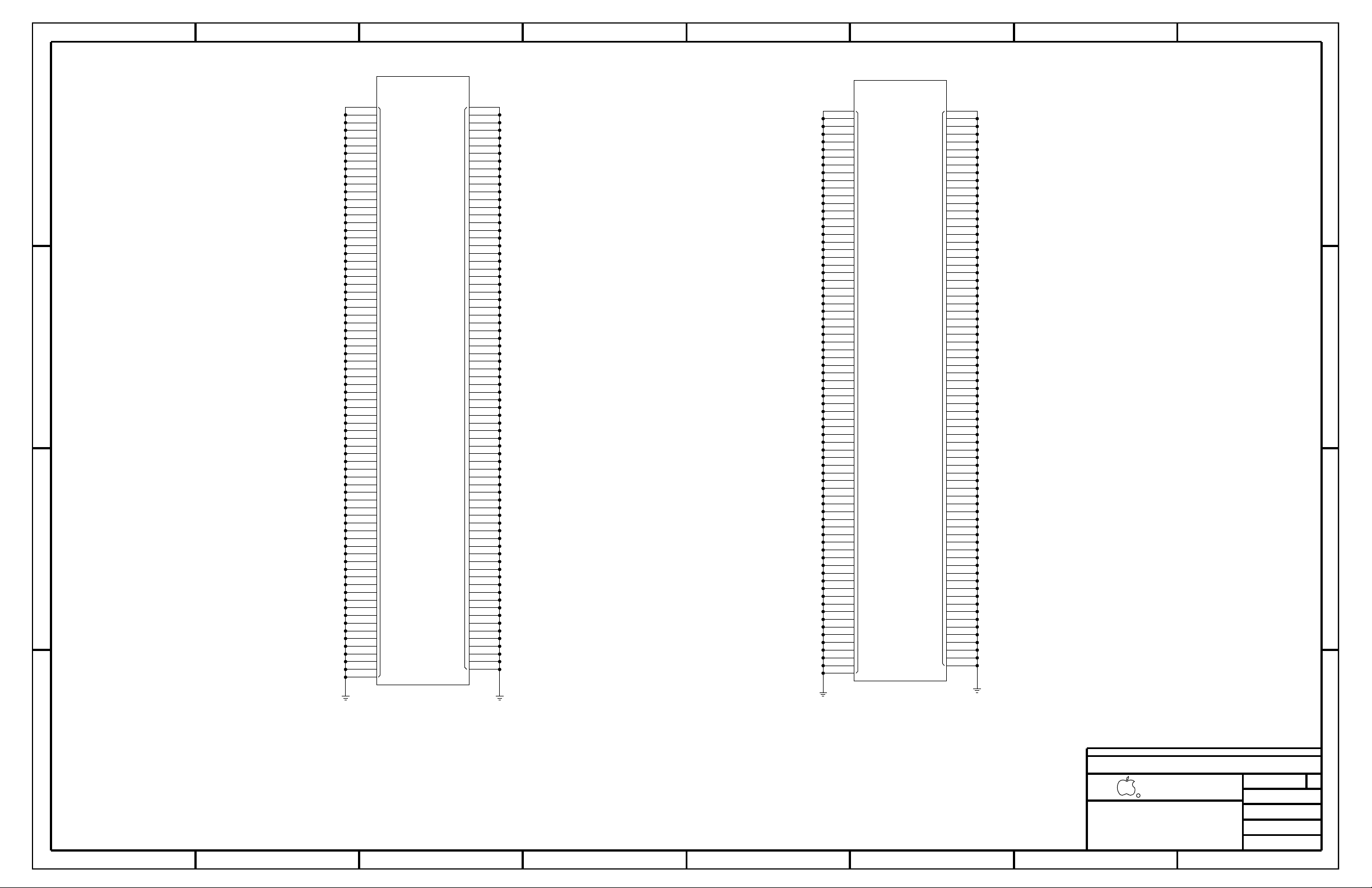

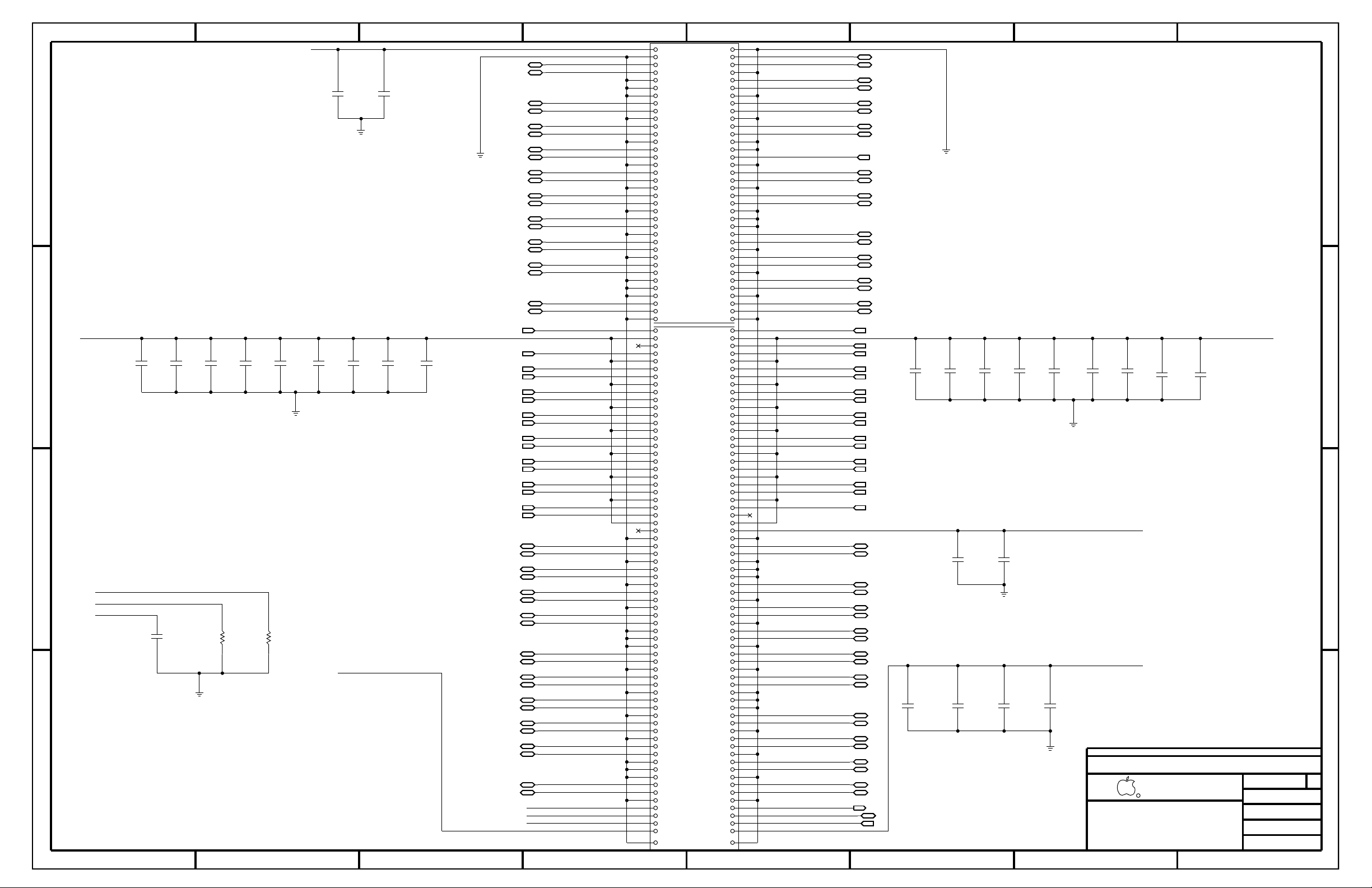

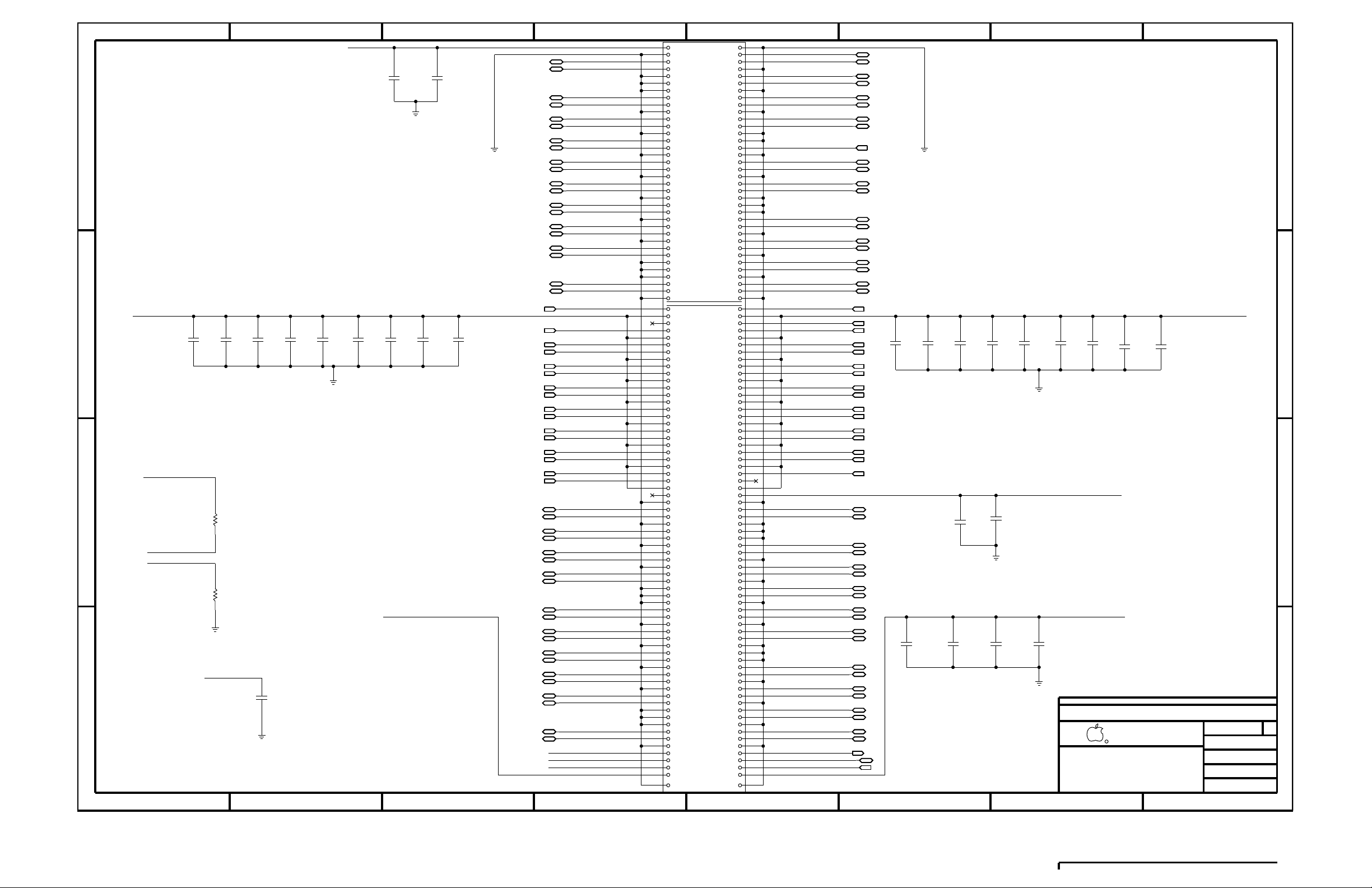

DDR3 SO-DIMM Connector A

31

K70_MLB

11/30/2011

30

DDR3 SO-DIMM CONNECTOR B

33

K70_MLB

11/30/2011

31

DDR3 ALIASES AND BITSWAPS

34

K70_MLB

11/30/2011

32

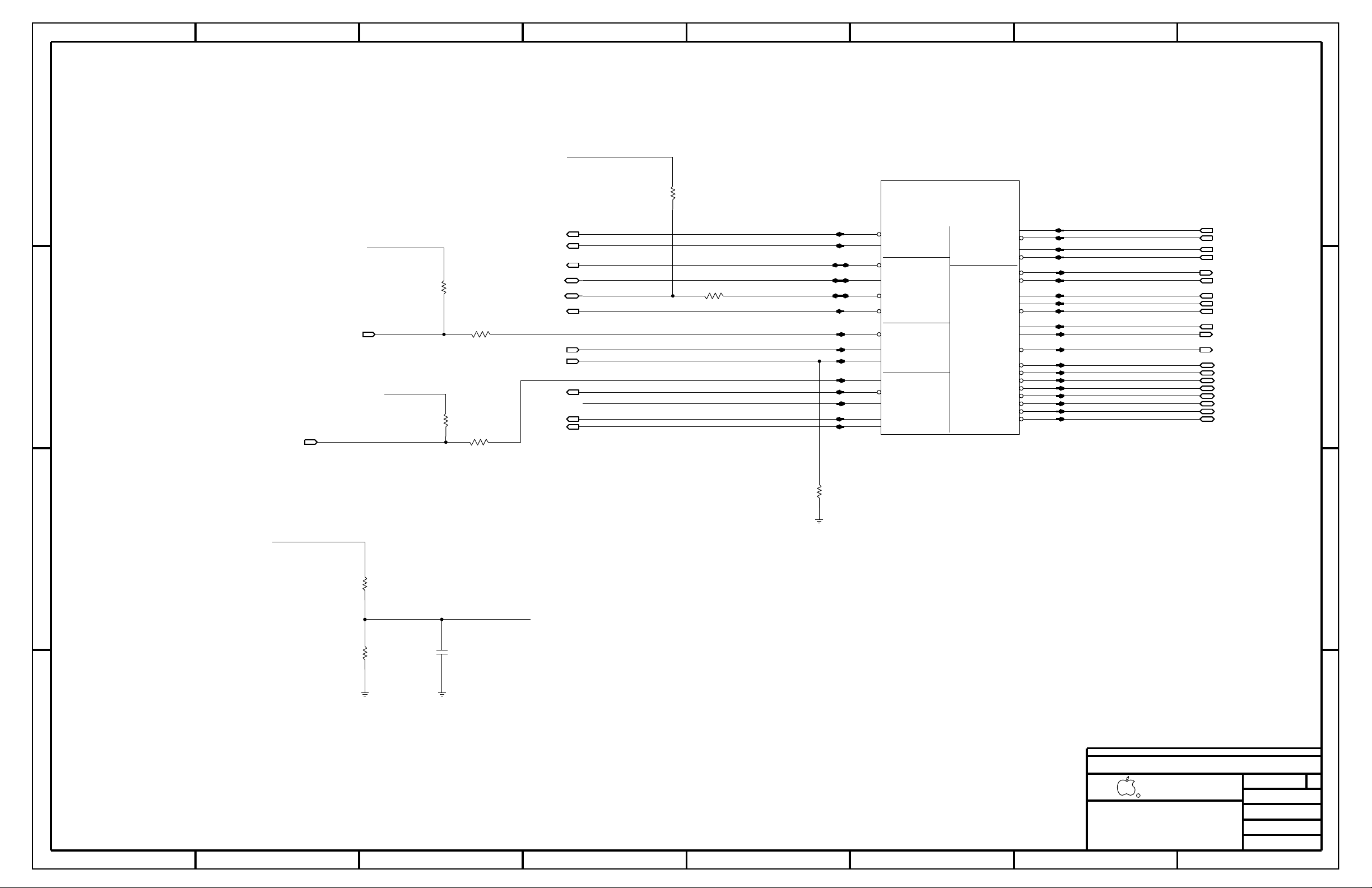

DDR3/FRAMEBUF VREF MARGINING

35

D7_NICK

12/13/2011

33

AIRPORT/BT

36

D7_DOUG

01/11/2012

34

Thunderbolt Host (1 of 2)

37

D7_DOUG

01/11/2012

35

Thunderbolt Host (2 of 2)

38

D7_DOUG

01/11/2012

36

Thunderbolt Power Support

39

D7_NICK

01/12/2012

37

ETHERNET PHY (CAESAR IV)

40

D7_NICK

01/12/2012

38

Ethernet Support & Connector

41

D7_NICK

01/12/2012

39

SD READER CONNECTOR

42

D7_TONY

01/11/2012

40

Camera Controller

45

D7_NICK

12/16/2011

41

SATA Connectors

46

D7_NICK

01/04/2012

42

EXTERNAL USB PORTS A & B

47

D7_NICK

01/04/2012

43

EXTERNAL USB PORTS C & D

49

D7_DOUG

01/11/2012

44 SMC

50

D7_DOUG

01/11/2012

45

SMC Support

51

D7_NICK

12/13/2011

46

SPI and Debug Connector

52

D7_DOUG

01/03/2012

47

SMBus Connections

53

D7_DOUG

01/06/2012

48

I and V Sense(Production)

Apple Inc.

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

124578

B

D

8 7 6 5 4 3

C

B

A

NOTICE OF PROPRIETARY PROPERTY:

PAGE

12

D

A

C

PAGE TITLE

SHEET

IV ALL RIGHTS RESERVED

R

D

SIZE

DRAWING NUMBER

REVISION

BRANCH

6 3

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

PATH: Kismet > K70/72 > Block Diagrams > K70 Block Diagram

System Block diagram can be found on Kismet

SYNC_DATE=11/30/2011

SYNC_MASTER=K70_MLB

System Block Diagram

051-9509

4.2.0

2 OF 113

2 OF 100

Apple Inc.

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

124578

B

D

8 7 6 5 4 3

C

B

A

NOTICE OF PROPRIETARY PROPERTY:

PAGE

12

D

A

C

PAGE TITLE

SHEET

IV ALL RIGHTS RESERVED

R

D

SIZE

DRAWING NUMBER

REVISION

BRANCH

6 3

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

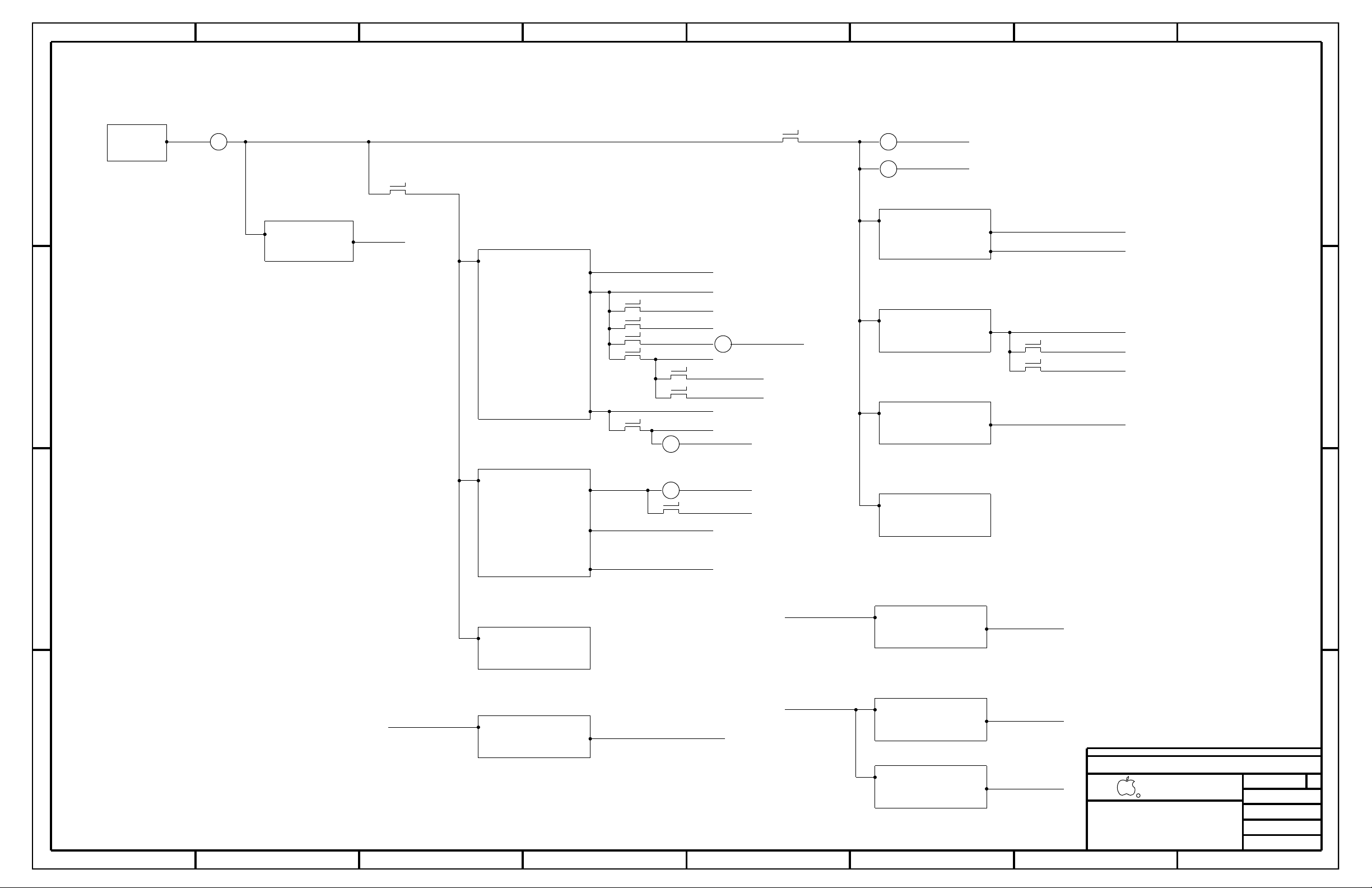

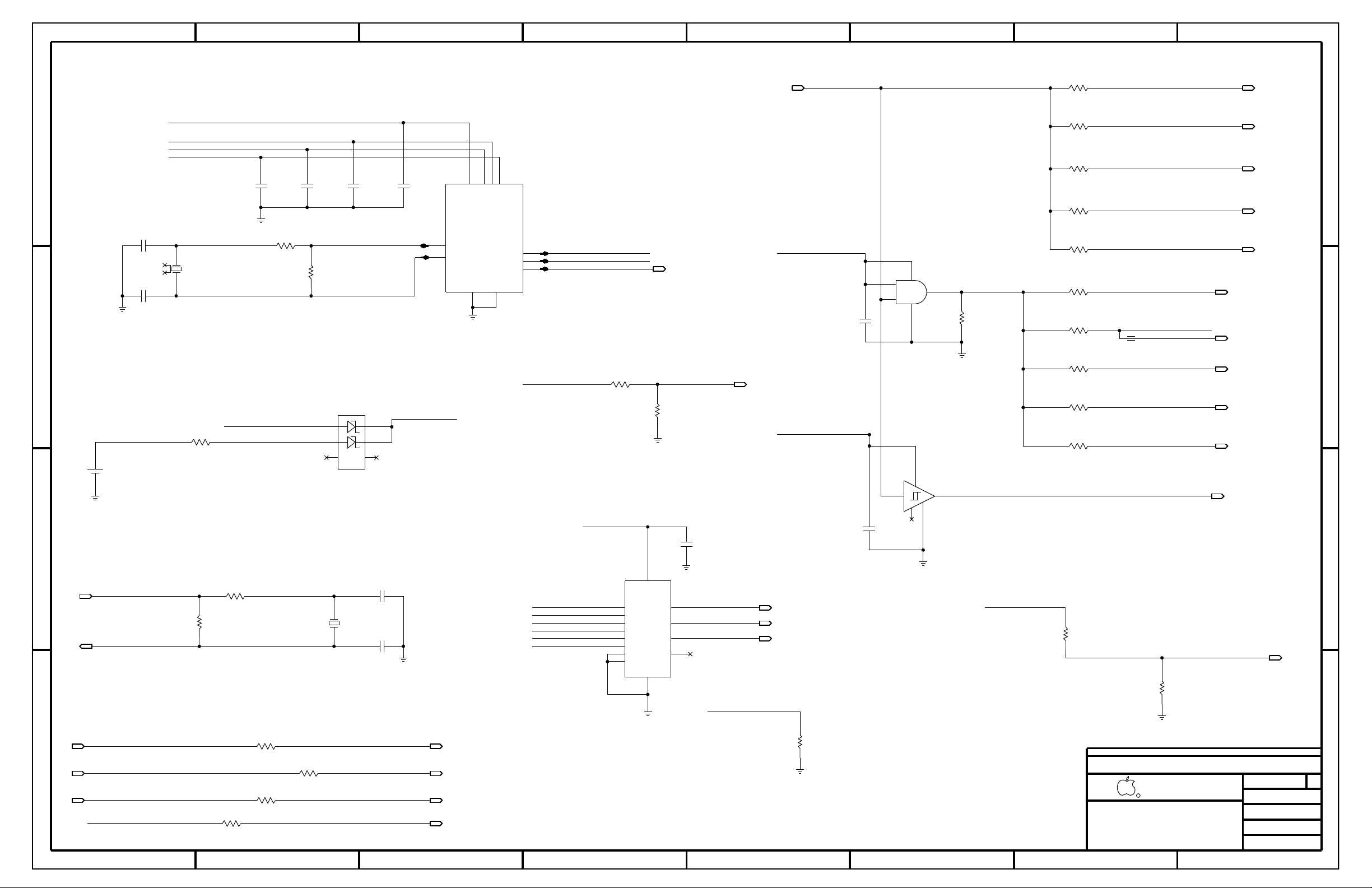

AC/DC

Supply Module

12V

G3HReg

PP3V42_G3H

G3HRegG3H

Vin

en

Regulator

U7800

3.3V

S5

LDO5VS5

U7600

Regulator

Vin

en

PP5V_S5_LDO

S5

SMC, RTC, BT

Audio, LCD, PCH, Camera, GPU

Thunderbolt

SD Card

PP3V3_S0

Reg

PP3V3_S0_SSD

AirPort

PP3V3_TBTLC

PP3V3_S4_AP_FET

Ethernet

PP3V3_ENET

PP3V3_S5

USB ports

SO-DIMMs

PP5V_S4

5V

Reg S4

Reg S3

VDDQ

VTT

VTT

LDO S3

S0LDO

Regulator

en

S4

en

S3

Vin

U7700

en

S0

Loads

I

PPHDD_S0

PP5V_S0

I

SO-DIMMs

PPVDDQ_S3_DDR

PP1V5_S0

S0-DIMMs

PPDDRVTT_S0

PPDDRVTT_S3

PPVDDQ_S3

Thunderbolt

PP12V_S0_FET

CPU

CPU

CPU, PCH

PPVCCSA_S0_REG

S0Reg

Reg S0

AXG

Reg

Reg S0

VccIO

S0S0

S0

Regulator

S0

Regulator

Regulator

U7100

Vin

en

Vin

en

U7500

en

Vin

Internal display

Loads

Fan

PP12V_G3H

I

PP12V_ACDC

PP12V_S5

PPCPUCORE_S0

PPCPUAXG_S0

Core

U7400

PP1V05_S0_REG

VccSA

Speaker amps

GPU

S0

Regulator

U8900

Vin

CPU PLL, GPU PLL

PP1V8_S0_REG

S0Reg

1.8V

S0

Regulator

PP5V_S0_FET

U7750

Vin

en

Thunderbolt

CPU

PP1V05_TBTCIO

PP1V05_TBTLC

Thunderbolt

Audio, CPU

Audio, PCH, Camera

PP3V3_S0_SW_SD_PWR

Bootrom, PCH

SMC AVref

I

PPSSD_S0

SSD

I

I

PP12V_S0_GPUUNCORE

Core

RegS0

en

HDD

PP12V_S0_GPUCORE

PP12V_S0_GPUCORE

PP12V_S0_GPUUNCORE

PPVCORE_S0_GPU

en

Regulator

Reg S0

GPU

PP1V05_S0_GPU

S0Reg

Regulator

S0

en

Vin

Vin

S0

GPU FB

U8350

U8300

IOVDD

GPUVDDQ

PPVDDQ_S0_GPU

SYNC_DATE=01/03/2012

SYNC_MASTER=D7_NICK

Power Block Diagram

051-9509

4.2.0

3 OF 113

3 OF 100

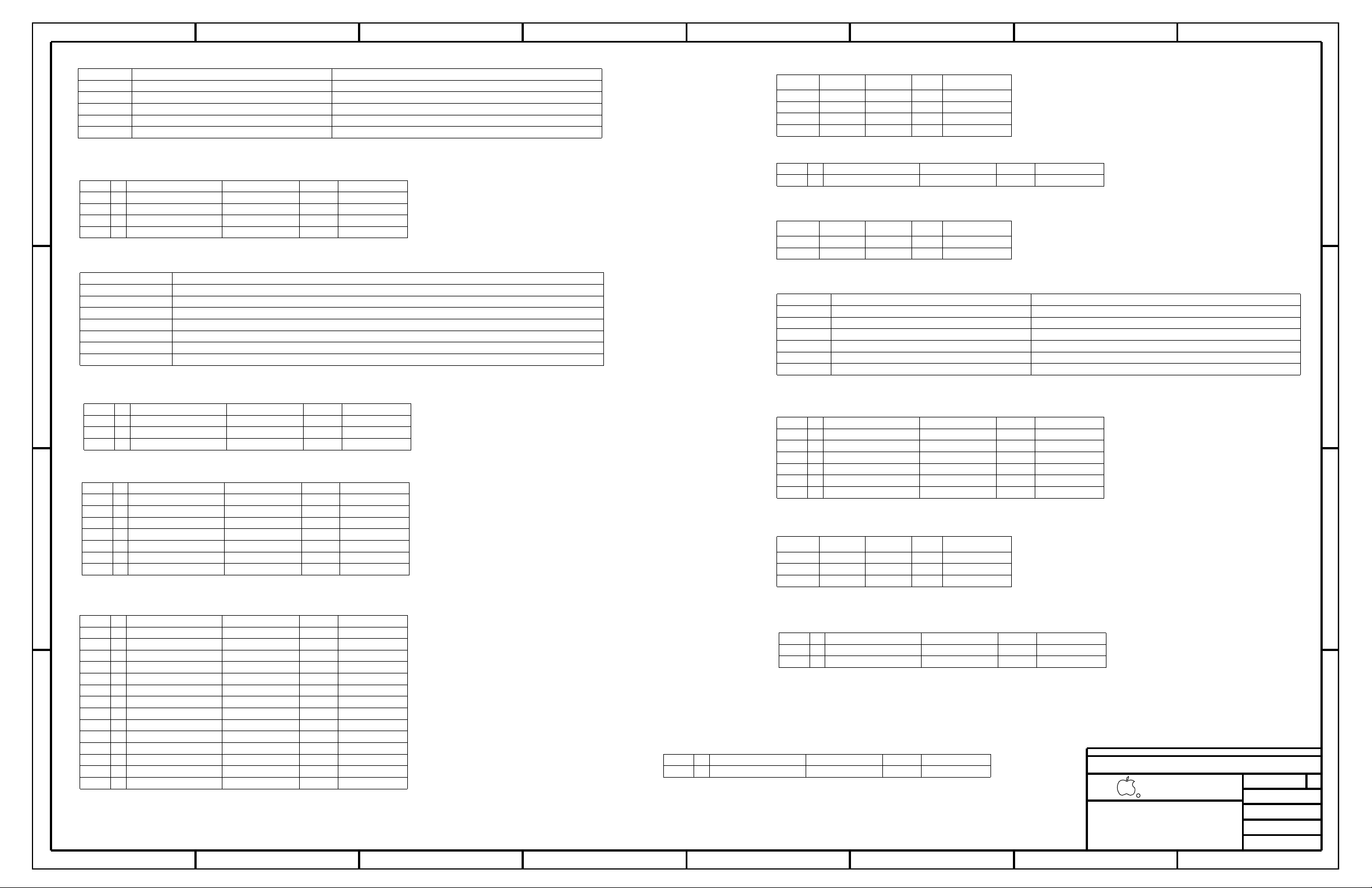

BOM OPTIONS

BOM GROUP

TABLE_BOMGROUP_HEAD

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_5_ITEM

CRITICAL BOM OPTION

TABLE_5_HEAD

PART#

DESCRIPTION

QTY

REFERENCE DESIGNATOR(S)

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

CRITICAL BOM OPTION

TABLE_5_HEAD

PART#

DESCRIPTION

QTY

REFERENCE DESIGNATOR(S)

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

CRITICAL BOM OPTION

TABLE_5_HEAD

PART#

DESCRIPTION

QTY

REFERENCE DESIGNATOR(S)

TABLE_5_ITEM

TABLE_5_ITEM

CRITICAL BOM OPTION

TABLE_5_HEAD

PART#

DESCRIPTION

QTY

REFERENCE DESIGNATOR(S)

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

CRITICAL BOM OPTION

TABLE_5_HEAD

PART#

DESCRIPTION

QTY

REFERENCE DESIGNATOR(S)

TABLE_5_ITEM

TABLE_BOMGROUP_ITEM

TABLE_5_ITEM

PART NUMBER

ALTERNATE FOR

PART NUMBER

BOM OPTION

REF DES

COMMENTS:

TABLE_ALT_HEAD

TABLE_ALT_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

CRITICAL BOM OPTION

TABLE_5_HEAD

PART#

DESCRIPTION

QTY

REFERENCE DESIGNATOR(S)

TABLE_5_ITEM

BOM OPTIONS

BOM NAME

BOM NUMBER

TABLE_BOMGROUP_HEAD

TABLE_BOMGROUP_ITEM

TABLE_ALT_ITEM

CRITICAL BOM OPTION

TABLE_5_HEAD

PART#

DESCRIPTION

QTY

REFERENCE DESIGNATOR(S)

PART NUMBER

ALTERNATE FOR

PART NUMBER

BOM OPTION

REF DES

COMMENTS:

TABLE_ALT_HEAD

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_5_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

PART NUMBER

ALTERNATE FOR

PART NUMBER

BOM OPTION

REF DES

COMMENTS:

TABLE_ALT_HEAD

TABLE_ALT_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

CRITICAL BOM OPTION

TABLE_5_HEAD

PART#

DESCRIPTION

QTY

REFERENCE DESIGNATOR(S)

TABLE_5_ITEM

TABLE_BOMGROUP_ITEM

BOM OPTIONS

BOM NAME

BOM NUMBER

TABLE_BOMGROUP_HEAD

Apple Inc.

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

124578

B

D

8 7 6 5 4 3

C

B

A

NOTICE OF PROPRIETARY PROPERTY:

PAGE

12

D

A

C

PAGE TITLE

SHEET

IV ALL RIGHTS RESERVED

R

D

SIZE

DRAWING NUMBER

REVISION

BRANCH

6 3

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

BOM Groups

Programmable Parts

Alternate: 335S0854

GPU Module Parts

VRAM Alternates

Alternate: 335S0812

Alternates

CPUs

Programmable Parts (unused)

CPU Socket Alternates

VRAM Module Parts

VRAM BOM Variants

CPU Socket

Add ’K70_PRODUCTION’ at RevA release

Replace with 65W part

Main BOM Variants

Module Parts

Bar Code Labels / EEEE #’s

BOM Configuration

SYNC_DATE=12/13/2011

SYNC_MASTER=D7_NICK

PCBA,MLB,DEV,D7

085-4441

PCBA,MLB,D7,GSA,GOOD

639-3566

PCBA,MLB,D7,GTX,CTO

639-3665

639-3668

PCBA,MLB,D7,GSB,GOOD

639-3567

PCBA,MLB,D7,GTX,BETTER

MLB LABEL,48.0X4.8

825-7122

1

EEEE:DT42

CRITICAL

IVB,QC13,QS,E0,2.8G,65W,4+1,1.10,6M,LGA

337S4240

1

CRITICAL

CPU

CPU:GOOD

1

337S4246 CRITICAL

CPU

IVB,SR0PN,PRQ,E1,3.1G,65W,4+2,1.15,8M,LG

CPU:CTO

341S3390

U4900

CRITICAL

1

IC,SMC,PROGRMD,PVT,D7

SMC:PVT

CRITICAL

U1000

511S0073

1

SOCKET,MOLEX,LGA1155,CPU-LF

607-9432

FB:BOTH_SAMSUNG

K70,GDDR5,SAMSUNG

607-9435

FB:BOTH_HYNIX

K70,GDDR5,HYNIX

607-9433

FB:CH1_SAMSUNG

K70,GDDR5,SAMSUNG_CH1

607-9436

FB:CH1_HYNIX

K70,GDDR5,HYNIX_CH1

607-9437

FB:CH2_HYNIX

K70,GDDR5,HYNIX_CH2

FB:CH2_HYNIX

CRITICAL

IC,GDDR5,2GB,M-DIE,170B FBGA

2

U8500,U8550

333S0630

FB:CH2_SAMSUNG

U8500,U8550

IC,SGRAM,GDDR5,64MX32,4.2GBPS,D-DIE,HF

2

CRITICAL333S0631

IC,GDDR5,32MX32,1.5GHZ,VEGA 44NM,B-DIE

FB:BOTH_HYNIX

CRITICAL

U8400,U8450,U8500,U8550

4

333S0620

607-9432607-9435

GDDR5_BOTH

VRAM

607-9433607-9436

GDDR5_CH1

VRAM

GPU:GSA

607-9437 607-9434

GDDR5_CH2

VRAM

GPU:GSB

607-9434

VRAM

CRITICAL

1

GPU:GSB

K70,GDDR5,SAMSUNG_CH2

511S0073511S0072

ALL

FOXCONN SOCKET

511S0071 511S0073

TYCO SOCKET

ALL

Enet magnetics

157S0058157S0055

ALL

607-9434

FB:CH2_SAMSUNG

K70,GDDR5,SAMSUNG_CH2

CRITICAL

U8701

GPUROM:BLANK

335S0724

1

IC,1 MBIT SERIAL FLASH

341S3388

U4900

CRITICAL

1

IC,SMC,PROGRMD,EVT,D7

SMC:EVT

341S3389

U4900

CRITICAL

1

IC,SMC,PROGRMD,DVT,D7

SMC:DVT

377S0126377S0107

USB diodes

ALL

1

EEEE_DF98

825-7122

EEEE:DF98

CRITICAL

XDP_CONN,LPCPLUS,VREFMRGN:EXT,BKLT_PWM,DEVEL_SENSORS,DEVEL_AUDIO

D7_DEVEL

1

U4202

CRITICAL

335S0852

IC,FLASH,SPI,1MBIT,3V3

CAMROM:BLANK

IC,PCH,PPT-DT,Z77,QS,C1

337S4234

U1800

1

CRITICAL

CRITICAL

CAMROM:PROG

U4202

1

IC,CAMERA FLASH,K70/K72

341S3453

1

CRITICAL

U4900

IC,SMC,PROGRMD,PROD,D7

SMC:PROD

341S3409

BOOTROM:BLANK

1

U5110

IC,64 MBIT SPI SERIAL FLASH

CRITICAL

335S0807

337S4220

GPU:GSB

U8000

CRITICAL

IC,GPU,NV,GK107-GS-2/1-QS-A

1

IC,SGRAM,GDDR5,64MX32,4.2GBPS,D-DIE,HF

FB:CH1_SAMSUNG

2

U8400,U8450

CRITICAL333S0631

IC,SGRAM,GDDR5,32MX32,1.5GHz,G-DIE,HF

FB:BOTH_SAMSUNG

U8400,U8450,U8500,U8550

CRITICAL

4

333S0619

IC,GDDR5,2GB,M-DIE,170B FBGA

FB:CH1_HYNIX

2

U8400,U8450

CRITICAL333S0630

K70,GDDR5,SAMSUNG_CH1

607-9433

VRAM

CRITICAL

GPU:GSA

1

U3990

CRITICAL

335S0862

IC,SERIAL FLASH,2MBIT,2.7V,REV F

1

CIVROM:BLANK

337S4239

IC,GPU,NV,GK107-GTX-QS-A2

1

GPU:107GTX

U8000

CRITICAL

IC,GPU,NV,GK107-GS-2/1-QS-A

337S4221 CRITICAL

GPU:GSA

U8000

1

338S1047

U3600

CRITICAL

1

IC,TBT,CR-4C,ES1,288 FCBGA,12X12MM

337S4258

IVB,QC48,QS,E1,2.9G,65W,4+2,1.10,6M,LGA

1

CPU:BETTER

CPU

CRITICAL

K70,GDDR5,SAMSUNG

GPU:107GTX

607-9432 CRITICAL

1

VRAM

1

BOOTROM:PROG

CRITICAL

U5110

IC,PROGRMD,EFI ROM,K70

341S3480

341S3487

U3990

1

IC,ENET 1MBITFLASH,CIV,PVT,J40

CRITICAL

CIVROM:PROG

IC,SMC12-A3,BLANK,D7

338S1098

U4900

1

SMC:BLANK

CRITICAL

IC,SMC,PROGRMD,PROTO1,D7

341S3484

U4900

CRITICAL

1

SMC:PROTO1

CRITICAL

335S0865

IC,EEPROM,SERIAL,256KB,MLP8

U3690

T29ROM:BLANK

1

341S3493

U3690

CRITICAL

IC,CR,V24.2,D7/D7I

1

T29ROM:PROG

IC,BCM57766,CIV+,A0,8X8

343S0592

U3900

CRITICAL

1

P/NCh dual FET

ALL

376S0975376S1081

341S3487341S3486

ALL

P/NCh dual FET

D7_COMMON1

XDP,RSMRST:SMC,SPEAKERID,TBTHV:P12V

SNS_CPUCORE:3PHASE,CPUCOREDRV:ISL6612,IG:N,GPU_ROM:YES,SNS_GPUS0:K70,SNS_VDDQS3_DDR:Y

D7_COMMON2

SMC:PROTO1,BOOTROM:PROG,T29ROM:PROG,CIVROM:PROG,CAMROM:PROG

D7_PROGPARTS

D7_PRODUCTION

SNS_VDDQS0_GPU:N,SNS_VDDQS3:N,VREFMRGN:N

825-7122

MLB LABEL,48.0X4.8

CRITICAL

1

EEEE:F117EEEE_F117

1

825-7122

MLB LABEL,48.0X4.8

CRITICAL

EEEE:F116

SNS_VDDQS0_GPU:Y,SNS_VDDQS3:Y,TEMPSNSDEV

DEVEL_SENSORS

COMMON,ALTERNATE,D7_COMMON1,D7_COMMON2,D7_PROGPARTS

D7_COMMON

MLB LABEL,48.0X4.8

EEEE_F116

EEEE_DT42

D7_COMMON,CPU:BETTER,GPU:107GTX,FBA,FBB,SSD:Y,EEEE:DT42

D7_COMMON,CPU:CTO,GPU:107GTX,FBA,FBB,SSD:Y,EEEE:F116

D7_COMMON,CPU:GOOD,GPU:GSB,GS,FBB,SSD:N,EEEE:F117

DEVELOPMENT,D7_DEVEL

D7_COMMON,CPU:GOOD,GPU:GSA,GS,FBA,SSD:N,EEEE:DF98

051-9509

4.2.0

4 OF 113

4 OF 100

IN

G

D

S

IN

G

D

S

IN

Apple Inc.

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

124578

B

D

8 7 6 5 4 3

C

B

A

NOTICE OF PROPRIETARY PROPERTY:

PAGE

12

D

A

C

PAGE TITLE

SHEET

IV ALL RIGHTS RESERVED

R

D

SIZE

DRAWING NUMBER

REVISION

BRANCH

6 3

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

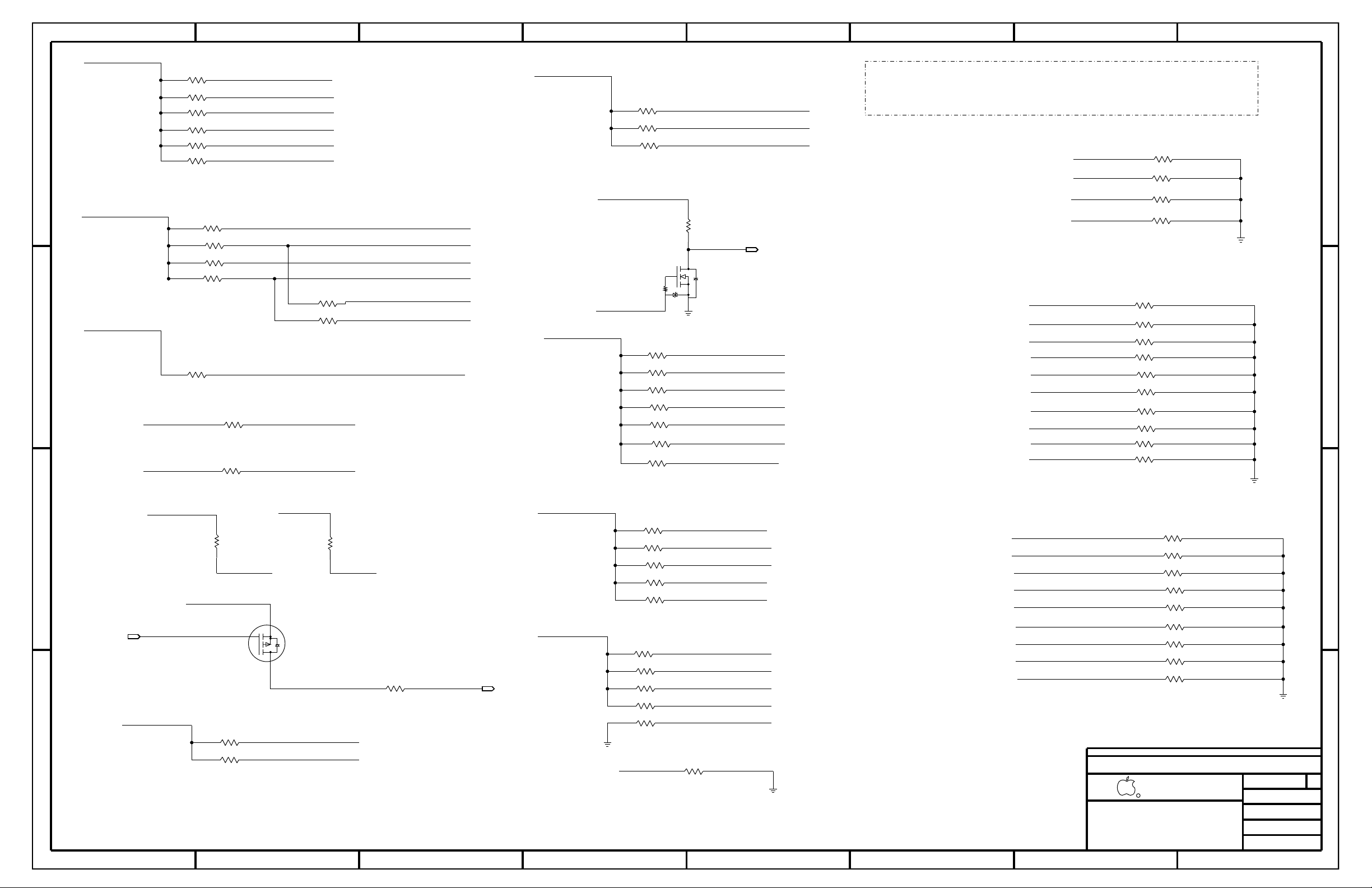

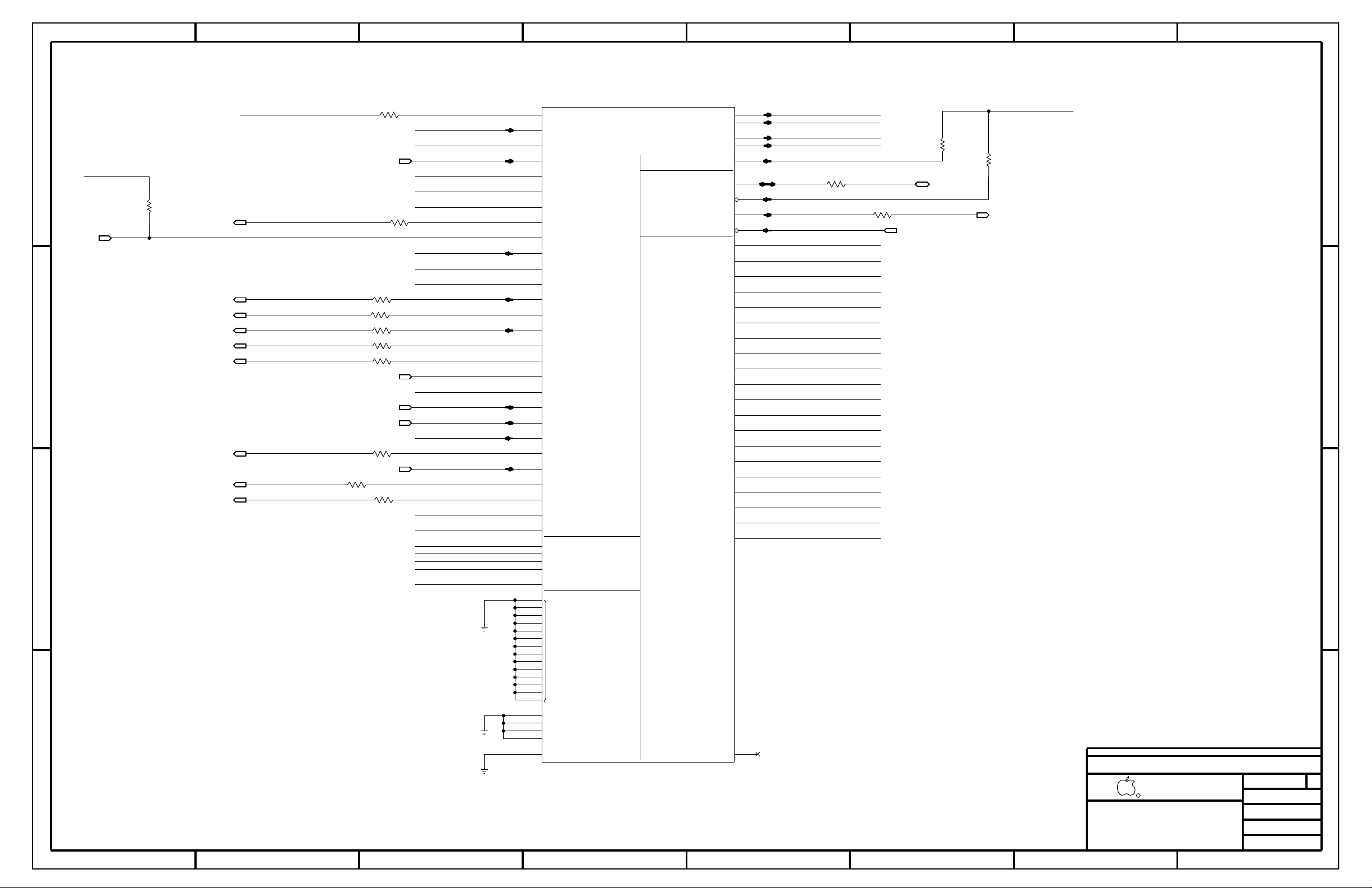

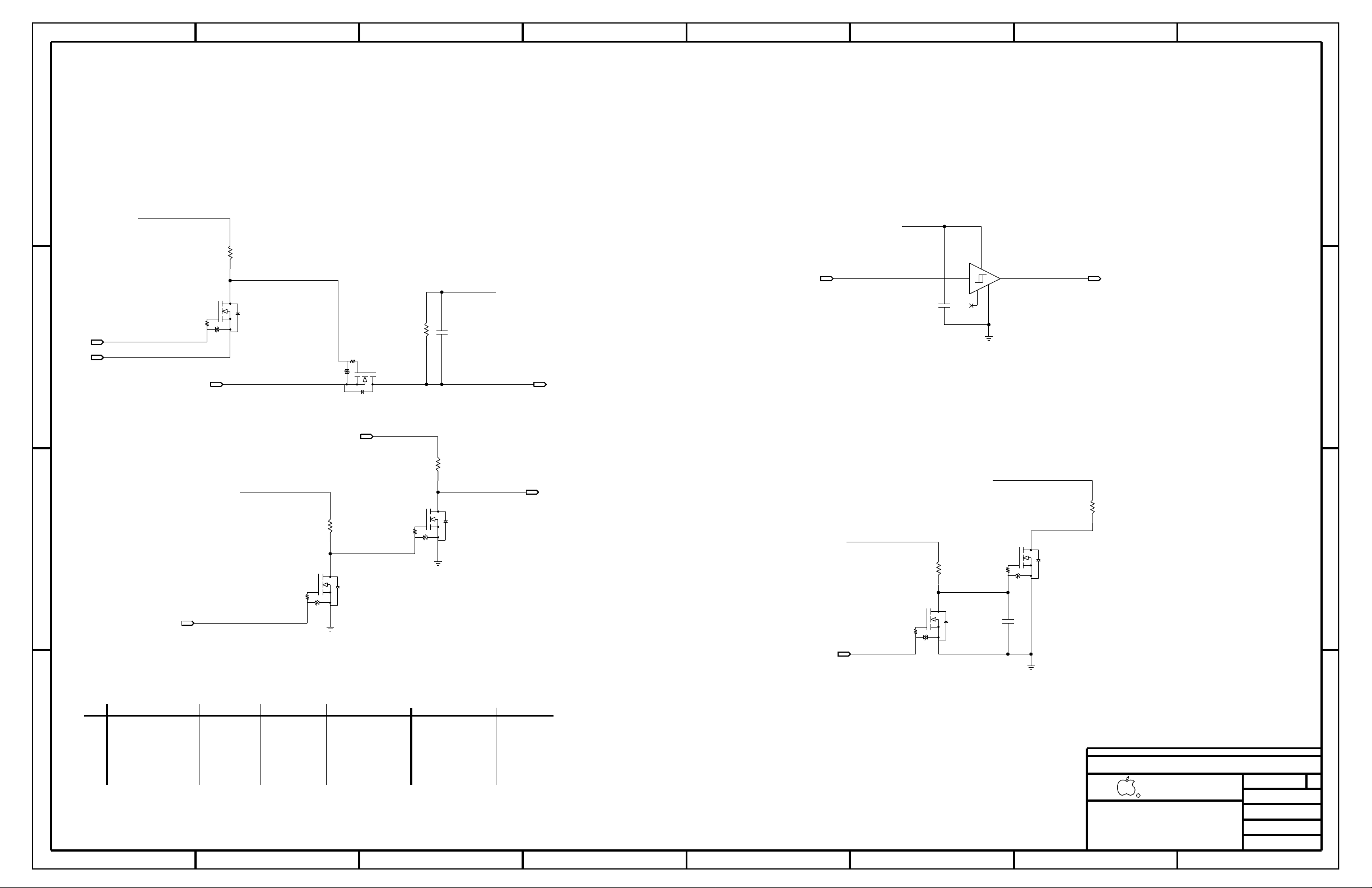

ALL_SYS_PWRGD Led

This LED is a GPIO driven from

that chipset has enumerated graphics

VIDEO ON Led

S5 Led

GPU GOOD Led

the southbridge that indicates

1/16W

5%

MF-LF

1K

402

81

SILK_PART=2

2.0X1.25MM-SM

GREEN-3.6MCD

SOT-363

2N7002DW-X-G

5%

MF-LF

1/16W

402

1K

44 61

SILK_PART=4

2.0X1.25MM-SM

GREEN-3.6MCD

1K

1/16W

402

MF-LF

5%

2.0X1.25MM-SM

SILK_PART=1

GREEN-3.6MCD

1K

5%

1/16W

MF-LF

402

SILK_PART=3

2.0X1.25MM-SM

GREEN-3.6MCD

SOT-363

2N7002DW-X-G

21

SYNC_MASTER=K70_MLB

DEBUG LEDS

SYNC_DATE=11/30/2011

ITS_PLUGGED_IN

=PP3V3_S5_LED

GPU_PRESENT_DRAIN

GPU_PRESENT_R

=PP3V3_S0_LED

VIDEO_ON_L

LCD_SHOULD_ON_R

=PP3V3_S0_LED

CORE_VOLTAGES_ON

CORE_VOLTAGES_ON_R

=PP3V3_S4_LED

ALL_SYS_PWRGD

GPU_GOOD

R502

1

2

LED502

A

K

Q502

3

5

4

R504

1

2

LED504

A

K

R501

1

2

LED501

A

K

R503

1

2

LED503

A

K

Q502

6

2

1

051-9509

4.2.0

5 OF 113

5 OF 100

6

5 6

5 6

6

OUT

OUT

IN

OUT

OUT

Apple Inc.

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

124578

B

D

8 7 6 5 4 3

C

B

A

NOTICE OF PROPRIETARY PROPERTY:

PAGE

12

D

A

C

PAGE TITLE

SHEET

IV ALL RIGHTS RESERVED

R

D

SIZE

DRAWING NUMBER

REVISION

BRANCH

6 3

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

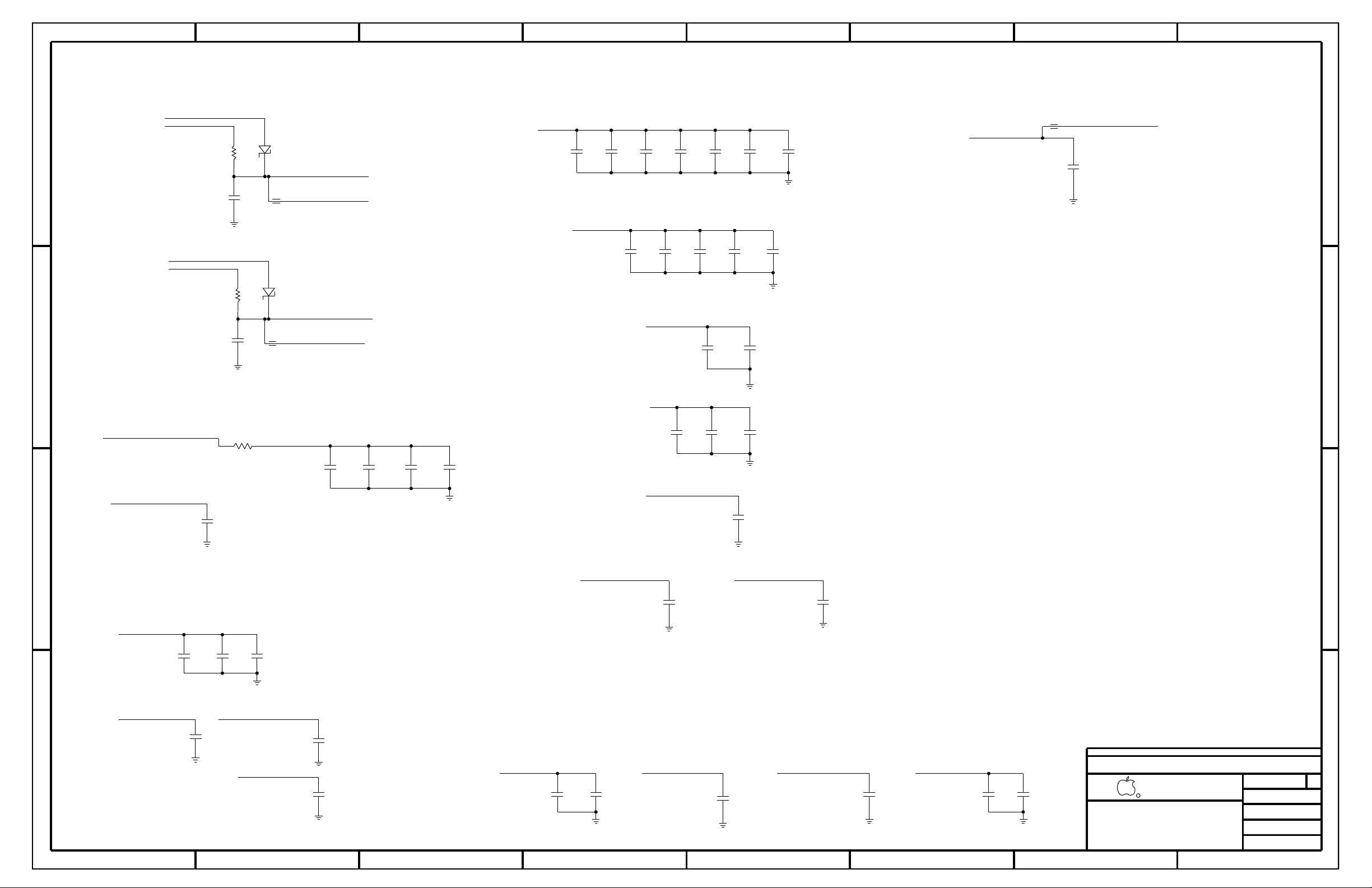

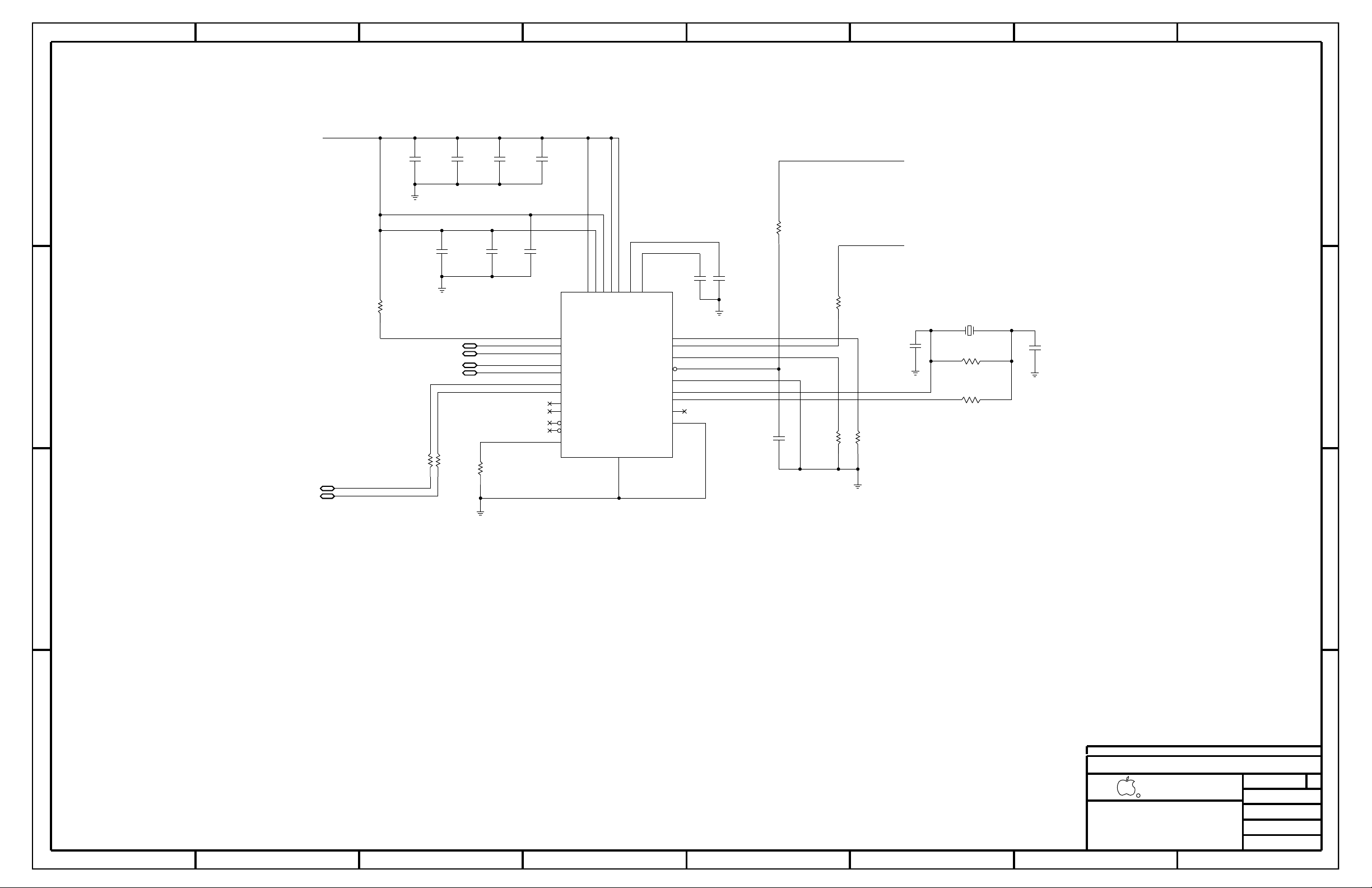

Enabled when system has AC and is in S5

Enabled when Thunderbolt cable is plugged in

Enabled when system is in run

S5 Rails

S3 Rails

Enabled when system is in run or sleep

Thunderbolt Rails (S0)

Enabled when system is in run

Ground/Common

S4 Rails

S0 Rails

Always on: Keeps the PCH RTC alive

G3 Rails

G3H Rails

Enabled when system has AC and is in run or sleep

GPU Rails (S0)

MLB to AC-DC Supplemental Signal Connector

MLB to AC-DC Connector

J600.7:3mm

EMC

5%

402

NP0-C0G

25V

1000PF

805

X5R

25V

10%

10UF

J600.6:3mm

EMC

1000PF

J600.8:3mm

25V

5%

402

NP0-C0G

50 94

50 94

45 67

6

45

10%

NOSTUFF

6.3V

1UF

CERM

402

402

6.8V-100PF

0

402

MF-LF

1/16W

5%

45

SILK_PART=PwrSig

CRITICAL

M-RT-SM

53780-8606

402

10K

5%

MF-LF

1/16W

CRITICAL

F-RT-TH

43650-0603

SYNC_DATE=01/11/2012

Power Connectors/Aliases

SYNC_MASTER=D7_NICK

GND

MAKE_BASE=TRUE

MAKE_BASE=TRUE

PP3V3_S4

MAKE_BASE=TRUE

PP5V_S4

PP3V3_S5

MAKE_BASE=TRUE

PP5V_S5

MAKE_BASE=TRUE

PP12V_S5

MAKE_BASE=TRUE

PPVDDQ_S0_GPU

MAKE_BASE=TRUE

PP1V05_S0_GPU

MAKE_BASE=TRUE

MAKE_BASE=TRUE

PP1V05_TBTCIO

MAKE_BASE=TRUE

PP1V05_TBTLC

PP3V3_TBTLC

MAKE_BASE=TRUE

PPVCCSA_S0

MAKE_BASE=TRUE

MAKE_BASE=TRUE

PPVAXG_S0

PPDDRVREF_CA_MEM_B_S3

MAKE_BASE=TRUE

PPDDRVREF_DQ_MEM_B_S3

MAKE_BASE=TRUE

MAKE_BASE=TRUE

PPDDRVREF_CA_MEM_A_S3

PPDDRVREF_DQ_MEM_A_S3

MAKE_BASE=TRUE

MAKE_BASE=TRUE

PPDDRVTT_S0

PP12V_S0_GPUUNCORE

MAKE_BASE=TRUE

PP12V_S0_GPUCORE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

PP12V_S0

MAKE_BASE=TRUE

PP5V_S0

MAKE_BASE=TRUE

PPHDD_S0

MAKE_BASE=TRUE

PP3V42_G3H

PPDDRVTT_S3

MAKE_BASE=TRUE

MAKE_BASE=TRUE

PPVDDQ_S3_DDR

PP3V3_S0_SSD

MAKE_BASE=TRUE

MAKE_BASE=TRUE

PPSSD_S0

MAKE_BASE=TRUE

PPVDDQ_S3

MAKE_BASE=TRUE

PP12V_ACDC

VOLTAGE=3.3V

MAKE_BASE=TRUE

NET_SPACING_TYPE=POWER

MIN_LINE_WIDTH=0.6MM

PP3V3_G3

MIN_NECK_WIDTH=0.2MM

MAX_NECK_LENGTH=3MM

MAKE_BASE=TRUE

PP12V_G3H

MAKE_BASE=TRUE

PPVCORE_S0_CPU

MAKE_BASE=TRUE

PPVCORE_S0_GPU

PP3V3_ENET

MAKE_BASE=TRUE

PP1V5_S0

MAKE_BASE=TRUE

MAKE_BASE=TRUE

PP1V05_S0

=PP1V05_S0_DP

=PP1V05_S0_P1V05TBTFET

=PPVCCIO_S0_CPU

=PP1V05_S0_PCH_V_PROC_IO

=PP1V05_S0_PCH_VCCIO_USB

=PP1V05_S0_PCH_VCCIO_SATA

=PP1V05_S0_PCH_VCCIO_PCIE

=PP1V05_S0_PCH_VCCIO_DMI

=PP1V05_S0_PCH_VCC_SSC

=PP1V05_S0_PCH_VCC_DIFFCLK

=PP1V05_S0_PCH_VCC_DMI

=PP1V05_S0_PCH_VCC_ASW

=PP1V05_S0_PCH_VCC_CORE

=PP1V05_S0_PCH_VCC_ADPLL

=PP1V05_S0_PCH

=PPVCCIO_S0_XDP

=PPVCCIO_S0_SMC

PPHDD_S0_SNS

SNS_ACDC_N

SNS_ACDC_P

SMC_ACDC_ID

PWR_BTN_R

BURSTMODE_EN_L

=PP1V8_S0_CAMERA

=PP1V5_S0_SENSE

=PPSPD_S0_MEM_A

=PP3V3_GPU_VDD33

=PP3V3_GPU_MISC

=PP3V3_GPU_IFPX_PLLVDD

=PP3V3_S0_BKLT_VDDIO

=PP3V3_S0_TBTPWRCTL

=PP3V3_S4_MEMRESET

=PP3V3_S4_PM

PP3V3_S4_FET

=PP5V_S4_FET_P5V_S0

=PP3V3_S4_ALS

PP12V_G3H_ACDC

=PPVDDQ_S3_LDO_DDRVTT

=PP3V3_ENET_PHY

PPDDRVTT_S3_LDO

=PPVDDQ_S3_MEMRESET

=PP3V3_S0_BT

=PP3V3_S0_AUDIO_DIG

=PP3V3_S0_VRD

=PP3V3_S0_AUDIO

=PP3V3_S0_CAMERA

PPCPUCORE_S0_REG

=PP5V_S4_REG_VDDQ_S3

=PP12V_S0_SNS_GPUUNCORE_R

=PP12V_S0_AUDIO_SPKRAMP

=PP12V_S0_BKLT

=PP12V_S0_SNS_GPUCORE_R

=PP3V3_G3H_BT

=PP12V_G3H_SNS_R

=PP12V_G3H_REG_3V42_G3H

PP5V_S5_LDO

=PP5V_S5_PWRCTL

PP3V3_S5_REG

=PP3V3_G3_PCH

=PP5V_S4_MEMRESET

=PP5V_S0_ISENSE

=PP1V8_S0_PCH_VCC_VRM

=PP1V8_S0_PCH_VCC_DFTERM

=PP1V8_S0_PCH

PP1V8_S0_REG

=PP3V3_S0_SSD

=PP3V3_S0_SMBUS_SMC_3

=PP3V3_S0_SMBUS_SMC_1

=PP3V3_S0_SMBUS_SMC_0

=PP3V3_S0_SENSE

=PP3V3_S0_SMBUS

=PP3V3_S0_SDCARD

=PP3V3_S0_RSTBUF

=PP3V3_S0_PCH_VCC_PCI

=PP3V3_S0_PCH_VCC_HVCMOS

=PP3V3_S0_PCH_VCC

=PP3V3_S0_PCH_PM

=PP3V3_S0_PCH_STRAPS

=PP3V3_S0_PCH_GPIO

=PP3V3_S0_LED_SATA

=PP3V3_S0_LED

=PP3V3_S0_ENET

=PP3V3_S0_PWRCTL

PP3V3_S0_FET

=PPHDD_S0_SNS_R

=PP5V_S0_PCH

=PP5V_S0_BKLT

=PP5V_S0_LPCPLUS

=PP5V_S0_AUDIO

=PP5V_S0_CAMERA

=PP5V_S0_VRD

=PP5V_S0_REG_GPU_VDDQ_S0

=PP5V_S0_REG_GPUCORE_S0

=PP5V_S0_REG_GPU_P1V05_S0

=PP5V_S0_REG_P1V05_S0

=PP5V_S0_REG_VCCSA_S0

=PP12V_S0_REG_CPUCORE_S0

=PP12V_S0_REG_VCCSA_S0

PPVDDQ_S3_SNS_DDR

=PP12V_G3H_FET_P12V_S0

=PPVIN_G3H_SMCVREF

=PP12V_G3H_FET_P12V_S5

=PP12V_S0_REG_P1V05_S0

=PPVDDQ_S3_SNS_DDR_R

=PPVDDQ_S3_FET_VDDQ_S0

=PP3V3_ENET_SYSCLK

PPVDDQ_S3_REG

=PPVDDQ_S3_VSNS

PP3V3_ENET_FET

=PPVDDQ_S3_MEM_B

=PPVDDQ_S3_MEM_A

=PPVDDQ_S3_DDR_VREF

PWR_BTN

SMC_ACDC_ID

=PP3V3_S0_VRD

PP12V_S0_FET

=PP5V_S4_USB

=PP5V_S4_PWRCTL

=PP12V_S5_REG_VDDQ_S3

PP3V42_G3H_REG

=PP3V3_G3H_SMC

=PP3V3_RTC_D

=PP5V_S0_REG_P1V8_S0

PP5V_S0_FET

=PP5V_S0_REG_CPUCORE_S0

PP5V_S4_REG

=PP5V_S0_SATA

=PP12V_S0_FAN

=PP12V_S0_LCD

PP12V_S0_SNS_GPUCORE

PP12V_S0_SNS_GPUUNCORE

=PP12V_S0_REG_GPUCORE_S0

=PP12V_S0_REG_GPU_P1V05_S0

=PP12V_S0_REG_GPU_VDDQ_S0

=PP3V3_S0_PCH

PP1V5_S0_FET

=PP1V5_S0_CPU_MEM

=PP1V5_S0_AUD_DIG

PPDDRVTT_S0_LDO

=PPDDRVTT_S0_CLAMP

=PPDDRVTT_S0_MEM_A

=PPDDRVTT_S0_MEM_B

PPDDRVREF_DQ_MEM_A

=PPDDRVREF_DQ_MEM_A

PPDDRVREF_CA_MEM_A

=PPDDRVREF_CA_MEM_A

PPDDRVREF_DQ_MEM_B

=PPDDRVREF_DQ_MEM_B

PPDDRVREF_CA_MEM_B

=PPDDRVREF_CA_MEM_B

PP1V05_S0_REG

=PPVCORE_S0_CPU

=PPVAXG_S0_CPU

PPCPUAXG_S0_REG

=PP3V3_TBTLC_FET

=PP3V3_TBT_PCH_GPIO

=PP3V3_TBTLC_RTR

=PP1V05_TBTLC_FET

=PP1V05_TBTCIO_FET

=PP1V05_GPU_IFPCD_IOVDD

=PP1V05_GPU_IFPEF_IOVDD

=PP1V05_GPU_PEX_IOVDD

=PP1V05_GPU_PEX_PLLVDD

PP1V5R1V35_S0_GPU_REG

=PP1V35_GPU_FBVDDQ

=PP1V35_GPU_S0_FB

=PP3V3_S0_P3V3TBTFET

=PP1V05_TBTLC_RTR

=PPVDDIO_ENET_CLK

=PP12V_S5_REG_P3V3P5V_S5

=PP12V_S5_PWRCTL

=PPHV_SW_TBTAPWRSW

=PPHV_SW_TBTBPWRSW

=PP12V_S5_SNS

=PP3V3_S5_FET_P3V3_S0

=PP3V3_S5_FET_P3V3_S4

=PP3V3_S5_PWRCTL

=PP3V3_S5_LPCPLUS

=PP3V3_S5_PCH_VCC_SPI

=PP3V3_S5_PCH_VCCSUS_HDA

=PP3V3_S5_PCH_VCCSUS_USB

=PP3V3_S5_ROM

=PP3V3_S0_PCH_VCC_GPIO

=PP3V3_S4_SDCARD

=PP3V3_S4_FET_ENET

=PP3V3_S4_PCH

=PP3V3_S4_LED

=PP3V3_S4_TBT

=PP3V3_S4_SMBUS_SMC_2

=PP3V3_S4_USB_HUB

=PP3V3_S4_TBTBPWRSW

=PP3V3_S4_TBTAPWRSW

=PP3V3_S4_VREFMRGN

PP12V_S5_FET

PP3V3_G3H_RTC

PP12V_G3H_SNS

=PP3V3_S0_DP

PPVCCSA_S0_REG

=PPVCCSA_S0_CPU

PP1V05_S0_GPU_REG

=PPVCORE_GPU

PPGPUCORE_S0_REG

=PP1V05_TBTCIO_RTR

=PPVDDIO_TBT_CLK

=PP3V3_S0_PCH_VCC_ADAC

=PPSPD_S0_MEM_B

PP12V_G3H_ACDC

=PP3V3_S4_PWRCTL

=PP3V3_S4_AP

=PP3V3_S4_SMC

=PP3V3_S5_XDP

=PP3V3_S5_SENSE

=PP3V3_S5_SMC

=PP3V3_S5_USBMUX

=PP3V3_S5_VRD

=PP5V_S5_PCH

=PP3V3_S5_LDO_P1V05_S5

=PP3V3_S5_LED

=PP3V3_S5_PCH

=PP3V3_S5_PCH_STRAPS

=PP3V3_S5_PCH_VCC_DSW

=PP3V3_G3H_SMC_USBMUX

PP3V3_S0

MAKE_BASE=TRUE

=PP3V3_S0_INTDPMUX

=PP3V3_S0_FAN

=PPDDRVTT_S3_VREFCA

=PPSSD_S0_SNS_R

PP3V3_S0_SSD_FET

=PP3V3_S0_SATAMUX

=PP1V8_S0_GPUVID

=PP1V8_S0_CPU_PLL

=PP3V3_S0_SMC

PPSSD_S0_SNS

=PPVDDIO_S0_SBCLK

=PP1V8_S0_ENET

MAKE_BASE=TRUE

PP1V8_S0

C602

1

2

C601

1

2

C603

1

2

C600

1

2

D600

1

2

R606

1 2

J601

7

8

1

2

3

4

5

6

R601

1

2

J600

1

2

3

4

5

6

051-9509

4.2.0

6 OF 113

6 OF 100

97

97

97

97

97

97

97

95

95

97

95

96

97

97

97

97

95

97

97

97

97

97

97

95

95

97

97

95

97

97

96

97

97

95

95

36

10 11 13 16 62

22 24

22

18 22 24

18 19 22

22

22

22

22 24

22 24

22 24

17

18 24

25

45

48

40

41

29

71 77 78 79

77 80

77

86

36

28

28

70

70

40

6

68

37 38

68

28

33

56

6

62 65 66 68 74

40 52 54 55 58

40

63

68

48

54 55

86

48

33

48

69

67

67 70

67

18 19

28

48

24

22 24

19

68

41

47

47

47

41 48 49 50

47

39

26

22 24

22 24

22 24

26

15

15 19 20 36

15 41

5

37

70 80

70

48

24

86

46

52 59

40

68

74

80

74

65

66

63

66

49

70

45

69

65

49

70

26

68

38

30

29

32

6

45

6

62 65 66 68 74

70

42 43

70

68

69

44 45

26

68

70

62

67

41

51

81

48

48

80

74

74

18 21 24

70

11 13 16

52

68

28

29

30

32

29

32

29

32

30

32

30

65

13 16 48 62

13 17 48 62

64

36

15

34 35 36

36

36

77

77

73 79

77 79

74

72 75 76

73

36

35 36

26

67

60 61 70

84

85

48

70

70

60 61 70 78

46

22 24

22 24

22 24

46

22 24

15 39

38

15

5

34 35 36 84 85

47

27

45 85

45 84

32

69

22 26

48

47 81 83

66

13 16

74

72 79

80

35

26

17

30

6

70

33

45

25

48

45

42 43

67 68

24

5

19 24 26

15

22 24

42

97

82

51

32

49

70

41

80

13 16

45

49

26

38

97

Apple Inc.

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

124578

B

D

8 7 6 5 4 3

C

B

A

NOTICE OF PROPRIETARY PROPERTY:

PAGE

12

D

A

C

PAGE TITLE

SHEET

IV ALL RIGHTS RESERVED

R

D

SIZE

DRAWING NUMBER

REVISION

BRANCH

6 3

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

998-4560 (Plated holes, 2.3mm inner diameter, 4.3mm pad)

APN: 870-1939

CPU Heatsink

WIRELESS CARD MTG HOLES

SSD STANDOFF

APN: 860-1461

4mm Plated Holes (998-0850)

POGO PINS

GPU HEATSINK MOUNTING FEATURES

(860-0988)

Rear Cover

998-4559 (Plated holes, 4mm inner diameter, 8mm pad)

USB Can holes

998-3975 (Plated slot holes, 1.10mm x 0.45mm)

8P5R5-NSP

OMIT

8P5R5-NSP

OMIT

8P5R5-NSP

OMIT OMIT

8P5R5-NSP

CRITICAL

STDOFF-4.5OD2.2ID-5.6H-SM

CRITICAL

STDOFF-4.5OD.98H-1.1-3.48-TH

STDOFF-4.5OD.98H-1.1-3.48-TH

CRITICAL

CRITICAL

STDOFF-4.5OD.98H-1.1-3.48-TH

CRITICAL

7P0R4P0-8P0B-NSP

CRITICAL

7P0R4P0-8P0B-NSP

7P0R4P0-8P0B-NSP

CRITICAL

CRITICAL

7P0R4P0-8P0B-NSP

5P5R2P3-4P3B-NSP

CRITICAL

5P5R2P3-4P3B-NSP

CRITICAL

TH-NSP

SL-1.1X0.45-1.4X0.75

TH-NSP

SL-1.1X0.45-1.4X0.75

SYNC_DATE=11/30/2011

SYNC_MASTER=K70_MLB

Holes/PD parts

ZH07001ZH07011ZH07021ZH0703

1

NUT0713

1

SH0777

1

SH0778

1

SH0779

1

ZH0713

1

ZH0714

1

ZH0715

1

ZH0716

1

ZH0721

1

ZH0722

1

ZH0730

1

ZH0731

1

051-9509

4.2.0

7 OF 113

7 OF 100

Apple Inc.

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

124578

B

D

8 7 6 5 4 3

C

B

A

NOTICE OF PROPRIETARY PROPERTY:

PAGE

12

D

A

C

PAGE TITLE

SHEET

IV ALL RIGHTS RESERVED

R

D

SIZE

DRAWING NUMBER

REVISION

BRANCH

6 3

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

CPU Memory

CPU Reserved

PCH PLL

UNUSED GRAPHICS ALIASES

PCH Reserved

PCH SATA

PCH Test Points

PCH Unused Display

PCH PCI

PCH Miscellaneous

PCH Clocks

PCH USB

PCH and CPU FDI

SYNC_MASTER=K70_MLB

SYNC_DATE=11/30/2011

Unused Signal Aliases

TP_PCH_RESERVE_5

TP_PCI_PAR

TP_PCI_C_BE_L<3..0>

MEM_B_CLK_P<2..3>

MEM_B_CLK_N<2..3>

CPU_CFG<15..12>

TP_MEM_B_DQ_CB<7..0>

TP_MEM_A_DQS_N<8>

TP_MEM_A_DQ_CB<7..0>

TP_CPU_RSVD<46..19>

TP_SDVO_STALLN

TP_SDVO_STALLP

TP_SDVO_INTN

TP_PCH_RESERVE_23

TP_PCH_RESERVE_21

DP_IG_D_AUXP

DMI_MIDBUS_CLK100M_N

MEM_B_CS_L<2..3>

MEM_A_CKE<2..3>

MEM_A_CS_L<2..3>

TP_MEM_B_DQS_N<8>

TP_MEM_A_DQS_P<8>

TP_CPU_RSVD<16..1>

TP_CLKOUT_PEG_A_P

PP1V05_S0_PCH_VCCAPLL_SATA

PP1V05_S0_PCH_VCCAPLL_EXP

PP1V05_S0_PCH_VCCAPLLDMI2

CPU_FDI_TX_P<7..0>

TP_DVPCNTL_M<0..1>

TP_PCH_RESERVE_28

HDMI_EG_DATA_C_P<0..2>

TP_PCH_RESERVE_12

TP_PCH_RESERVE_20

USB_PCH_5_N

DP_IG_B_AUX_N

DP_IG_B_AUX_P

DP_IG_B_HPD

TP_PCH_GPIO65_CLKOUTFLEX1

TP_PCH_GPIO64_CLKOUTFLEX0

TP_CRT_IG_VSYNC

TP_CRT_IG_DDC_CLK

TP_CRT_IG_DDC_DATA

DP_IG_B_MLN<3..0>

DP_IG_C_MLP<3..0>

TP_PCH_GPIO67_CLKOUTFLEX3

HDMI_EG_DDC_DATA

PP1V05_S0_PCH_VCC_A_CLK

TP_PPVOUT_PCH_DCPSUSBYP

PP1V05_S0_PCH_FDIPLL

TP_PCH_GPIO8

TP_PCI_CLK33M_OUT3

TP_PCI_CLK33M_OUT2

TP_PCH_CL_RST1

TP_PCH_CL_CLK1

TP_PCH_CL_DATA1

TP_PCH_SST

TP_PCH_PWM3

TP_PCH_PWM2

TP_PCH_PWM1

TP_PCH_PWM0

TP_PCH_RESERVE_8

TP_PCH_RESERVE_7

TP_PCH_RESERVE_0

TP_DVPDATA<4..23>

TP_PCH_RESERVE_19

TP_PCH_RESERVE_22

TP_PCH_RESERVE_27

TP_PCH_RESERVE_26

TP_PCH_RESERVE_24

TP_PCH_RESERVE_17

TP_PCH_RESERVE_18

TP_PCH_RESERVE_15

TP_PCH_RESERVE_16

TP_PCH_RESERVE_14

TP_PCH_RESERVE_13

TP_PCH_RESERVE_10

TP_PCH_RESERVE_11

TP_PCH_RESERVE_9

TP_PCH_RESERVE_6

TP_PCH_RESERVE_3

TP_PCH_RESERVE_4

TP_PCH_RESERVE_2

TP_PCH_RESERVE_1

TP_PCH_L_BKLTEN

TP_SDVO_TVCLKINP

DP_IG_C_AUX_N

DP_IG_C_AUX_P

DP_IG_C_CTRL_CLK

TP_SATA_F_R2D_CP

TP_SATA_F_R2D_CN

TP_PCH_L_BKLTCTL

DP_IG_D_MLP<3..0>

DP_IG_B_DDC_CLK

DP_IG_D_CTRL_DATA

TP_SDVO_INTP

TP_SDVO_TVCLKINN

DP_IG_D_HPD

DP_IG_C_MLN<3..0>

DP_IG_B_DDC_DATA

TP_SATA_F_D2RP

TP_SATA_F_D2RN

DP_IG_B_MLP<3..0>

TP_CRT_IG_BLUE

TP_CRT_IG_RED

TP_CRT_IG_GREEN

TP_SATA_E_R2D_CP

TP_SATA_E_R2D_CN

TP_SATA_D_R2D_CP

TP_SATA_D_R2D_CN

TP_SATA_C_D2RN

TP_SATA_C_D2RP

TP_SATA_C_R2D_CN

TP_PCH_TP20

TP_PCH_TP19

TP_PCH_TP18

TP_PCH_TP17

TP_PCH_TP16

TP_PCH_TP15

TP_PCH_TP13

TP_PCH_TP14

TP_PCH_TP12

TP_PCH_TP11

TP_PCH_TP10

TP_PCH_TP9

TP_PCH_TP8

TP_PCH_TP7

TP_PCH_TP6

TP_PCH_TP5

TP_PCH_TP4

TP_PCH_TP3

TP_PCH_TP1

TP_SATA_D_D2RP

TP_PCH_TP2

TP_SATA_C_R2D_CP

TP_SATA_E_D2RP

TP_SATA_E_D2RN

TP_SATA_D_D2RN

DP_IG_C_HPD

DP_IG_C_CTRL_DATA

TP_PCI_AD<31..0>

TP_PCI_RESET_L

TP_LPC_DREQ0_L

TP_PCH_INIT3V3_L

TP_HDA_SDIN1

TP_HDA_SDIN3

TP_HDA_SDIN2

HDMI_EG_DDC_CLK

HDMI_EG_DATA_C_N<0..2>

GPU_TDIODE_P

HDMI_EG_CLK_C_N

HDMI_EG_CLK_C_P

EG_LCD_PWR_EN

GPU_TDIODE_N

TP_DVPCLK

TP_DVPCNTL<0..2>

TP_PCH_L_VDD_EN

TP_PCH_RESERVE_25

TP_CRT_IG_HSYNC

USB_PCH_4_N

USB_PCH_4_P

USB_PCH_5_P

USB_PCH_6_N

USB_PCH_6_P

USB_PCH_11_P

USB_PCH_11_N

USB_PCH_12_P

USB_PCH_12_N

USB_PCH_13_P

USB_PCH_13_N

TP_PCIE_CLK100M_PE6N

TP_PCIE_CLK100M_PE7N

TP_PCIE_CLK100M_PE6P

TP_PCIE_CLK100M_PE7P

TP_PE_TX_P<3..0>

TP_PE_TX_N<3..0>

TP_PE_RX_N<3..0>

TP_PE_RX_P<3..0>

TP_PCH_CLKOUT_DPN

TP_PCH_CLKOUT_DPP

PCH_CLK25M_XTALOUT

TP_PCH_GPIO66_CLKOUTFLEX2

TP_PCIE_CLK100M_PE4N

TP_PCIE_CLK100M_PE4P

CPU_FDI_TX_N<7..0>

PCH_FDI_RX_P<7..0>

PCH_FDI_RX_N<7..0>

CPU_FDI_INT

CPU_FDI_FSYNC<1..0>

CPU_FDI_LSYNC<1..0>

PCH_FDI_INT

PCH_FDI_LSYNC<1..0>

PCH_FDI_FSYNC<1..0>

DP_IG_D_MLN<3..0>

DP_IG_D_AUXN

DP_IG_D_CTRL_CLK

TP_CLKOUT_PEG_A_N

TP_MEM_B_DQS_P<8>

MEM_A_CLK_N<2..3>

DMI_MIDBUS_CLK100M_P

MEM_A_CLK_P<2..3>

MEM_B_CKE<2..3>

MEM_A_ODT<2..3>

MEM_B_ODT<2..3>

NC_MEM_A_DQSN<8>

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_PCIE_CLK100M_PE6N

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_PCIE_CLK100M_PE6P

MAKE_BASE=TRUE

NO_TEST=TRUE

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_MEM_A_CKE<2..3>

NC_MEM_A_CS_L<2..3>

NO_TEST=TRUE

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_MEM_A_CLKP<2..3>

MAKE_BASE=TRUE

NC_CLKOUT_PEG_AN

NO_TEST=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

TP_CPU_CFG<15..12>

MAKE_BASE=TRUE

NC_MEM_A_DQSP<8>

NO_TEST=TRUE

NC_MEM_B_DQ_CB<7..0>

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_PCH_CLKOUT_DPN

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PE_RXN<3..0>

NO_TEST=TRUE

MAKE_BASE=TRUE

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PE_TXP<3..0>

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_CPU_RSVD<46..19>

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_MEM_B_ODT<2..3>

MAKE_BASE=TRUE

NC_MEM_B_CKE<2..3>

NO_TEST=TRUE

NC_MEM_B_CS_L<2..3>

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_MEM_A_ODT<2..3>

MAKE_BASE=TRUE

NO_TEST=TRUE

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_MEM_B_CLKP<2..3>

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_MEM_B_CLKN<2..3>

MAKE_BASE=TRUE

NC_MEM_A_CLKN<2..3>

NO_TEST=TRUE

NC_MEM_B_DQSP<8>

NO_TEST=TRUE

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_MEM_B_DQSN<8>

MAKE_BASE=TRUE

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_MEM_A_DQ_CB<7..0>

MAKE_BASE=TRUE

NC_PP1V05_S0_PCH_VCCAPLL_SATA

NO_TEST=TRUE

NC_PP1V05_S0_PCH_VCCAPLL_EXP

NO_TEST=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_PP1V05_S0_PCH_VCCAPLLDMI2

NC_PCH_RESERVE_20

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_PCH_RESERVE_21

MAKE_BASE=TRUE

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCH_RESERVE_1

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCH_RESERVE_2

NO_TEST=TRUE

NC_PCH_RESERVE_3

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_DMI_MIDBUS_CLK100P

MAKE_BASE=TRUE

NO_TEST=TRUE

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_CPU_FDI_TXP<7..0>

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_DP_IG_B_HPD

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_DP_IG_B_MLN<3..0>

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_DP_IG_B_MLP<3..0>

NC_CLKOUT_PEG_AP

NO_TEST=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

NC_PCH_CLK25M_XTALOUT

NO_TEST=TRUE

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_GPU_TDIODE_P

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_EG_LCD_PWR_EN

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_GPU_TDIODE_N

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PP1V05_S0_PCH_VCC_A_CLK

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PPVOUT_PCH_DCPSUSBYP

NC_PP1V05_S0_PCH_FDIPLL

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCH_GPIO8

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_PCI_CLK33M_OUT3

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_PCI_CLK33M_OUT2

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCH_CL_RST1

NO_TEST=TRUE

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_PCH_CL_CLK1

MAKE_BASE=TRUE

MAKE_BASE=TRUE

NC_PCH_CL_DATA1

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCH_SST

NO_TEST=TRUE

NO_TEST=TRUE

NC_PCH_PWM3

MAKE_BASE=TRUE

MAKE_BASE=TRUE

NC_PCH_PWM2

NO_TEST=TRUE

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_PCH_PWM1

NO_TEST=TRUE

NC_PCH_PWM0

MAKE_BASE=TRUE

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_DP_IG_D_AUXN

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_DVPCLK

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_DVPDATA<4..23>

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_DVPCNTL_M<0..1>

MAKE_BASE=TRUE

NC_DVPCNTL<0..2>

NO_TEST=TRUE

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_PCH_RESERVE_28

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCH_RESERVE_26

NC_PCH_RESERVE_24

NO_TEST=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_PCH_RESERVE_25

NO_TEST=TRUE

NC_PCH_RESERVE_23

MAKE_BASE=TRUE

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_PCH_RESERVE_22

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCH_RESERVE_19

NC_PCH_RESERVE_17

MAKE_BASE=TRUE

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCH_RESERVE_18

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCH_RESERVE_14

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCH_RESERVE_13

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCH_RESERVE_12

NO_TEST=TRUE

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_PCH_RESERVE_10

NO_TEST=TRUE

NC_PCH_RESERVE_11

MAKE_BASE=TRUE

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_PCH_RESERVE_9

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_PCH_RESERVE_8

MAKE_BASE=TRUE

NC_PCH_RESERVE_7

NO_TEST=TRUE

NC_PCH_RESERVE_5

MAKE_BASE=TRUE

NO_TEST=TRUE

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_PCH_RESERVE_6

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_PCH_RESERVE_4

NC_SDVO_STALLN

MAKE_BASE=TRUE

NO_TEST=TRUE

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_SDVO_TVCLKINN

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_DP_IG_C_HPD

NC_SATA_E_R2D_CN

NO_TEST=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_DP_IG_D_CTRL_CLK

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCH_L_BKLTCTL

NC_PCH_L_BKLTEN

NO_TEST=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_DP_IG_D_HPD

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_DP_IG_D_MLN<3..0>

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_DP_IG_C_CTRL_CLK

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_DP_IG_C_CTRL_DATA

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_DP_IG_C_MLP<3..0>

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_DP_IG_C_MLN<3..0>

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_DP_IG_B_CTRL_DATA

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_SATA_F_D2RP

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_SATA_F_D2RN

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_SATA_F_R2D_CP

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_DP_IG_B_CTRL_CLK

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_CRT_IG_DDC_CLK

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_CRT_IG_VSYNC

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_CRT_IG_BLUE

NC_CRT_IG_HSYNC

MAKE_BASE=TRUE

NO_TEST=TRUE

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_CRT_IG_RED

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_CRT_IG_GREEN

NC_SATA_E_R2D_CP

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_SATA_D_D2RP

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_SATA_D_D2RN

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_SATA_D_R2D_CP

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_SATA_D_R2D_CN

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_SATA_C_D2RN

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_SATA_C_D2RP

MAKE_BASE=TRUE

NO_TEST=TRUE

NO_TEST=TRUE

NC_SATA_C_R2D_CN

MAKE_BASE=TRUE

NC_SATA_C_R2D_CP

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_PCH_TP20

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCH_TP19

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCH_TP18

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCH_TP17

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCH_TP16

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCH_TP15

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCH_TP13

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCH_TP14

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCH_TP12

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCH_TP11

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCH_TP10

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCH_TP9

NO_TEST=TRUE

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_PCH_TP8

MAKE_BASE=TRUE

NC_PCH_TP7

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCH_TP6

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCH_TP5

NO_TEST=TRUE

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_PCH_TP4

MAKE_BASE=TRUE

NC_PCH_TP1

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCH_TP2

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCH_TP3

NO_TEST=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_CRT_IG_DDC_DATA

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_DP_IG_D_AUXP

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_DP_IG_C_AUXP

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_DP_IG_C_AUXN

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_DP_IG_B_AUXP

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_PCI_AD<31..0>

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCI_PAR

MAKE_BASE=TRUE

NC_PCI_C_BE_L<3..0>

NO_TEST=TRUE

NO_TEST=TRUE

NC_PCI_RESET_L

MAKE_BASE=TRUE

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_LPC_DREQ0_L

NC_PCH_INIT3V3_L

MAKE_BASE=TRUE

NO_TEST=TRUE

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_HDA_SDIN1

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_HDA_SDIN3

MAKE_BASE=TRUE

NC_HDA_SDIN2

NO_TEST=TRUE

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCH_L_VDD_EN

NC_CPU_RSVD<16..1>

NO_TEST=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_DP_IG_D_CTRL_DATA

NO_TEST=TRUE

NC_SDVO_STALLP

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_SDVO_INTN

MAKE_BASE=TRUE

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_HDMI_EG_DDC_CLK

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_HDMI_EG_DDC_DATA

MAKE_BASE=TRUE

NC_HDMI_EG_DATA_C_P<0..2>

NO_TEST=TRUE

NC_HDMI_EG_DATA_C_N<0..2>

NO_TEST=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_HDMI_EG_CLK_C_P

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_HDMI_EG_CLK_C_N

NC_SDVO_TVCLKINP

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_SDVO_INTP

MAKE_BASE=TRUE

NO_TEST=TRUE

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCH_RESERVE_27

NC_PCH_RESERVE_16

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_PCH_RESERVE_15

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_USB_PCH_4_N

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_USB_PCH_4_P

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_USB_PCH_5_P

MAKE_BASE=TRUE

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_USB_PCH_5_N

NO_TEST=TRUE

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_USB_PCH_6_N

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_USB_PCH_6_P

NC_USB_PCH_11_P

NO_TEST=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_USB_PCH_11_N

NC_USB_PCH_12_P

MAKE_BASE=TRUE

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_USB_PCH_12_N

NO_TEST=TRUE

NO_TEST=TRUE

NC_USB_PCH_13_P

MAKE_BASE=TRUE

NC_USB_PCH_13_N

MAKE_BASE=TRUE

NO_TEST=TRUE

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCIE_CLK100M_PE7N

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_PCIE_CLK100M_PE7P

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PE_TXN<3..0>

MAKE_BASE=TRUE

NC_PE_RXP<3..0>

NO_TEST=TRUE

NC_DMI_MIDBUS_CLK100N

NO_TEST=TRUE

MAKE_BASE=TRUE

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCH_CLKOUT_DPP

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_PCH_GPIO64_CLKOUTFLEX0

NC_PCH_GPIO66_CLKOUTFLEX2

MAKE_BASE=TRUE

NO_TEST=TRUE

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_PCH_GPIO65_CLKOUTFLEX1

NC_PCH_GPIO67_CLKOUTFLEX3

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCIE_CLK100M_PE4N

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_PCIE_CLK100M_PE4P

MAKE_BASE=TRUE

NO_TEST=TRUE

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_DP_IG_B_AUXN

NC_CPU_FDI_TXN<7..0>

NO_TEST=TRUE

MAKE_BASE=TRUE

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCH_FDI_RXP<7..0>

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCH_FDI_RXN<7..0>

NO_TEST=TRUE

NC_CPU_FDI_INT

MAKE_BASE=TRUE

NC_CPU_FDI_FSYNC<1..0>

MAKE_BASE=TRUE

NO_TEST=TRUE

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_CPU_FDI_LSYNC<1..0>

NC_PCH_FDI_INT

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCH_FDI_LSYNC<1..0>

NO_TEST=TRUE

MAKE_BASE=TRUE

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_PCH_FDI_FSYNC<1..0>

MAKE_BASE=TRUE

NO_TEST=TRUE

NC_DP_IG_D_MLP<3..0>

MAKE_BASE=TRUE

NC_PCH_RESERVE_0

NO_TEST=TRUE

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_SATA_F_R2D_CN

NC_SATA_E_D2RP

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_SATA_E_D2RN

NO_TEST=TRUE

MAKE_BASE=TRUE

051-9509

4.2.0

8 OF 113

8 OF 100

19 20

20

12 88

12 88

10 91

12

12

12

10

19

19

19

19

19

19

18

12 88

12 88

12 88

12

12

10

18

22

22

22

10 91

19

19

19

20

19

19

19

18

18

19

19

19

19

19

18

22

22

22

21

20

20

18

18

18

21

21

21

21

21

19

19

19

19

19

19

19

19

19

19

19

19

19

19

19

19

19

19

19

19

19

19

18

19

19

19

19

18

18

18

19

19

19

19

19

19

19

19

18

18

19

19

19

19

18

18

18

18

18

18

18

21

21

21

21

21

21

21

21

21

21

21

21

21

21

21

21

21

21

21

18

21 18

18

18

18

19

19

20

20

18

19

18

18

18

77

78

77

18

19

19

20

20

20

20

20

20

20

20

20

20

20

21

21

21

21

10

10

10

10

18

18

18

18

18

18

10 91

19

19

10 91

10 91

10 91

19

19

19

19

19

19

18

12

12 88

18

12 88

12 88

12 88

12 88

Apple Inc.

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

124578

B

D

8 7 6 5 4 3

C

B

A

NOTICE OF PROPRIETARY PROPERTY:

PAGE

12

D

A

C

PAGE TITLE

SHEET

IV ALL RIGHTS RESERVED

R

D

SIZE

DRAWING NUMBER

REVISION

BRANCH

6 3

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

Whistler aliases

Signal Aliases

SYNC_DATE=11/30/2011

SYNC_MASTER=K70_MLB

=PEG_R2D_C_P<15..0>

=PEG_D2R_P<15..0>

=PEG_R2D_C_N<15..0>

=PEG_D2R_N<15..0>

MAKE_BASE=TRUE

PEG_D2R_N<0..15>

MAKE_BASE=TRUE

PEG_R2D_C_N<0..15>

MAKE_BASE=TRUE

PEG_R2D_C_P<0..15>

MAKE_BASE=TRUE

PEG_D2R_P<0..15>

051-9509

4.2.0

9 OF 113

9 OF 100

10

10

10

10 71 89

71 89

71 89

71 89

IN

IN

IN

IN

IN

IN

IN

IN

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

DMI_TX_1*

PE_TX_3*

PE_TX_3

PE_TX_2*

PE_TX_2

PE_TX_1*

PE_TX_1

PE_TX_0*

PE_TX_0

PE_RX_3*

PE_RX_3

PE_RX_2*

PE_RX_2

PE_RX_1*

PE_RX_1

PE_RX_0*

PE_RX_0

PEG_TX_15*

PEG_TX_15

PEG_TX_14*

PEG_TX_14

PEG_TX_13*

PEG_TX_13

PEG_TX_12*

PEG_TX_12

PEG_TX_11*

PEG_TX_11

PEG_TX_10*

PEG_TX_10

PEG_TX_9*

PEG_TX_9

PEG_TX_8*

PEG_TX_8

PEG_TX_7*

PEG_TX_7

PEG_TX_6

PEG_TX_5*

PEG_TX_5

PEG_TX_4*

PEG_TX_4

PEG_TX_3*

PEG_TX_3

PEG_TX_2*

PEG_TX_2

PEG_TX_1*

PEG_TX_1

PEG_TX_0*

PEG_TX_0

PEG_RX_15*

PEG_RX_15

PEG_RX_13*

PEG_RX_12

PEG_RX_11*

PEG_RX_11

PEG_RX_10

PEG_RX_9

PEG_RX_8

PEG_RX_7

PEG_RX_6

PEG_RX_5

PEG_RX_4*

PEG_RX_4

PEG_RX_3*

PEG_RX_3

PEG_RX_2

PEG_RX_1*

PEG_RX_0

FDI_TX_7*

FDI_TX_7

FDI_TX_6*

FDI_TX_6

FDI_TX_5*

FDI_TX_5

FDI_TX_4*

FDI_TX_4

FDI_TX_3*

FDI_TX_3

FDI_TX_2*

FDI_TX_2

FDI_TX_1*

FDI_TX_1

FDI_TX_0*

FDI_TX_0

FDI_LSYNC_1

FDI_LSYNC_0

FDI_FSYNC_1

FDI_FSYNC_0

DMI_TX_3*

DMI_TX_3

DMI_TX_2*

DMI_TX_2

DMI_TX_1

DMI_TX_0*

DMI_TX_0

DMI_RX_3*

DMI_RX_3

DMI_RX_2*

DMI_RX_2

DMI_RX_1

DMI_RX_0*

FDI_COMPIO

FDI_ICOMPO

FDI_INT

PEG_COMPI

PEG_ICOMPO

PEG_RX_1

PEG_RX_14*

PEG_RX_12*

PEG_RX_6*

PEG_RX_13

PEG_RX_14

PEG_RCOMPO

PEG_RX_10*

PEG_RX_9*

PEG_RX_8*

PEG_RX_7*

PEG_RX_2*

PEG_RX_0*

PEG_RX_5*

PEG_TX_6*

DMI_RX_0

DMI_RX_1*

SYM 1 OF 10

FLEXIBLE DISPLAY INTERFACE

PCI EXPRESS -- GRAPHICS

DMI

PCI EXPRESS

RSVD_NCTF_AV1

RSVD_NCTF_AW2

RSVD_NCTF_AY3

RSVD_NCTF_B39

NCTF_AW38

NCTF_AU40

NCTF_D1

NCTF_C2

NCTF_A38

CFG_8

RSVD_J34

RSVD_J33

RSVD_J31

CFG_0

CFG_1

CFG_2

CFG_3

CFG_4

CFG_5

CFG_6

CFG_7

CFG_9

CFG_10

CFG_11

CFG_12

CFG_13

CFG_14

CFG_15

CFG_16

CFG_17

RSVD_K9

RSVD_K31

RSVD_K34

RSVD_L9

RSVD_L31

RSVD_L33

RSVD_L34

RSVD_M34

RSVD_N33

RSVD_N34

RSVD_P35

RSVD_P37

RSVD_P39

RSVD_R34

RSVD_R36

RSVD_R38

RSVD_R40

RSVD_AB6

RSVD_AB7

RSVD_AD34

RSVD_AD35

RSVD_AD37

RSVD_AE6

RSVD_AF4

RSVD_AG4

RSVD_AJ11

RSVD_AJ29

RSVD_AJ30

RSVD_AJ31

RSVD_AN20

RSVD_AP20

RSVD_AT11

RSVD_AT14

RSVD_AU10

RSVD_AV34

RSVD_AW34

RSVD_AY10

RSVD_J9

RSVD_H8

RSVD_H7

RSVD_C38

RSVD_D38

RSVD_C39

SYM 5 OF 10

RESERVED

Apple Inc.

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

124578

B

D

8 7 6 5 4 3

C

B

A

NOTICE OF PROPRIETARY PROPERTY:

PAGE

12

D

A

C

PAGE TITLE

SHEET

IV ALL RIGHTS RESERVED

R

D

SIZE

DRAWING NUMBER

REVISION

BRANCH

6 3

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

ThermDA

ThermDC

CFG[17:7] Reserved config lanes

CFG[6:5] PCIe bifurcation; Refer to page 15 for more info

CFG[4] Reserved config lane

CFG[3] PCIe Static x4 lane reversal; Refer to page 15 for more info

CFG[2] PCIe Static x16 lane reversal; Refer to page 15 for more info

CFG[1:0] Reserved config lane

(Available for Workstation only)

INTEL SUGGESTS TO KEEP THESE TPS

(Unused)

SHORT B4 & C4 TOGETHER, ROUTE AS A SINGLE 4 MIL TRACE TO R1010.1

ROUTE B5 TO R1010.1 AS A SEPERATE 10 MIL TRACE.

19 90

19 90

19 90

19 90

19 90

19 90

19 90

19 90

19 90

19 90

19 90

19 90

19 90

19 90

19 90

19 90

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

MF-LF

402

1/16W

1%

24.9

PLACE_NEAR=U1000.B4:12.7mm

25 91

25 91

8

91

8

91

8

91

8

91

25 91

25 91

25 91

25 91

25 91

15 25 91

15 25 91

25 91

15 25 91

15 25 91

25 91

25 91

IVY-BRIDGE

OMIT_TABLE

BGA-SKT-K70

IVY-BRIDGE

OMIT_TABLE

BGA-SKT-K70

24.9

1%

1/16W

MF-LF

402

CPU DMI/PEG/FDI/RSVD

SYNC_MASTER=K70_MLB

SYNC_DATE=11/30/2011

NO_TEST=TRUE

NC_SNS_CPU_THERMDN

NO_TEST=TRUE

NC_SNS_CPU_THERMDP

CPU_FDI_TX_P<2>

CPU_FDI_TX_P<3>

CPU_FDI_TX_P<0>

CPU_FDI_TX_P<4>

CPU_FDI_TX_N<1>

CPU_FDI_TX_N<0>

DMI_N2S_P<1>

DMI_N2S_P<0>

DMI_N2S_N<3>

DMI_N2S_N<2>

CPU_FDI_TX_N<4>

CPU_FDI_TX_N<5>

=PEG_D2R_P<3>

=PEG_D2R_P<0>

=PEG_D2R_N<10>

=PEG_D2R_N<5>

=PEG_D2R_N<15>

=PEG_D2R_P<2>

=PEG_D2R_P<1>

=PEG_D2R_P<7>

TP_PE_RX_N<0>

TP_PE_RX_N<2>

TP_PE_TX_N<2>

TP_PE_TX_N<3>

TP_PE_TX_P<0>

CPU_FDI_TX_N<7>

DMI_N2S_P<3>

DMI_N2S_P<2>

CPU_FDI_TX_P<6>

=PEG_D2R_N<6>

=PEG_D2R_N<4>

=PEG_D2R_N<3>

=PEG_D2R_N<2>

=PEG_D2R_N<12>

=PEG_D2R_N<14>

=PEG_D2R_N<13>

=PEG_D2R_N<11>

DMI_S2N_N<3>

CPU_FDI_FSYNC<1>

=PEG_D2R_P<15>

=PEG_R2D_C_P<3>

CPU_CFG<16>

CPU_CFG<12>

CPU_CFG<9>

CPU_CFG<6>

CPU_CFG<3>

CPU_CFG<1>

CPU_CFG<0>

TP_CPU_RSVD<19>

TP_CPU_RSVD<8>

=PEG_D2R_P<10>

=PPVCCIO_S0_CPU

DMI_S2N_N<1>

=PEG_D2R_N<7>

=PEG_D2R_N<9>

=PEG_D2R_P<13>

CPU_FDI_INT

DMI_S2N_N<2>

CPU_FDI_FSYNC<0>

CPU_FDI_LSYNC<0>

CPU_FDI_LSYNC<1>

CPU_FDI_TX_P<1>

CPU_FDI_TX_N<2>

=PEG_D2R_P<4>

=PEG_D2R_P<5>

=PEG_D2R_P<6>

=PEG_D2R_P<8>

=PEG_D2R_P<9>

=PEG_D2R_P<11>

=PEG_R2D_C_P<0>

=PEG_R2D_C_N<0>

=PEG_R2D_C_P<1>

=PEG_R2D_C_N<1>

=PEG_R2D_C_P<2>

=PEG_R2D_C_N<4>

=PEG_R2D_C_P<5>

=PEG_R2D_C_N<5>

=PEG_R2D_C_P<6>

=PEG_R2D_C_P<7>

=PEG_R2D_C_N<7>

=PEG_R2D_C_P<8>

=PEG_R2D_C_N<8>

=PEG_R2D_C_N<9>

=PEG_R2D_C_P<10>

=PEG_R2D_C_N<10>

=PEG_R2D_C_P<11>

=PEG_R2D_C_N<11>

=PEG_R2D_C_P<12>

=PEG_R2D_C_P<13>

=PEG_R2D_C_N<13>

=PEG_R2D_C_P<14>

=PEG_R2D_C_N<14>

=PEG_R2D_C_N<15>

TP_PE_RX_P<0>

TP_PE_RX_P<1>

TP_PE_RX_N<1>

TP_PE_RX_P<2>

TP_PE_RX_P<3>

TP_PE_RX_N<3>

TP_PE_TX_N<0>

TP_PE_TX_P<1>

TP_PE_TX_N<1>

TP_PE_TX_P<2>

TP_PE_TX_P<3>

DMI_S2N_N<0>

DMI_S2N_P<3>

DMI_S2N_P<2>

TP_CPU_RSVD<2>

TP_CPU_RSVD<3>

TP_CPU_RSVD<1>

TP_CPU_RSVD<4>

TP_CPU_RSVD<5>

TP_CPU_RSVD<6>

TP_CPU_RSVD<46>

TP_CPU_RSVD<45>

TP_CPU_RSVD<44>

TP_CPU_RSVD<43>

TP_CPU_RSVD<42>

TP_CPU_RSVD<41>

TP_CPU_RSVD<40>

TP_CPU_RSVD<39>

TP_CPU_RSVD<38>

TP_CPU_RSVD<37>

TP_CPU_RSVD<36>

TP_CPU_RSVD<35>

TP_CPU_RSVD<34>

TP_CPU_RSVD<33>

TP_CPU_RSVD<32>

TP_CPU_RSVD<31>

TP_CPU_RSVD<30>

TP_CPU_RSVD<29>

TP_CPU_RSVD<28>

TP_CPU_RSVD<27>

TP_CPU_RSVD<26>

TP_CPU_RSVD<25>

TP_CPU_RSVD<24>

TP_CPU_RSVD<23>

TP_CPU_RSVD<22>

TP_CPU_RSVD<21>

TP_CPU_RSVD<20>

TP_CPU_RSVD<16>

TP_CPU_RSVD<11>

CPU_CFG<15>

CPU_CFG<11>

CPU_CFG<10>

CPU_CFG<5>

CPU_CFG<4>

CPU_CFG<2>

TP_CPU_RSVD<7>

TP_CPU_RSVD<9>

TP_CPU_NCTF<1>

TP_CPU_NCTF<2>

TP_CPU_NCTF<3>

TP_CPU_NCTF<4>

TP_CPU_NCTF<5>

TP_CPU_RSVD_NCTF<4>

TP_CPU_RSVD_NCTF<3>

TP_CPU_RSVD_NCTF<2>

TP_CPU_RSVD_NCTF<1>

DMI_S2N_P<0>

DMI_S2N_P<1>

=PEG_D2R_N<8>

=PEG_D2R_P<14>

=PEG_R2D_C_N<3>

=PEG_R2D_C_P<4>

=PEG_R2D_C_P<9>

=PEG_R2D_C_P<15>

=PEG_R2D_C_N<12>

=PEG_D2R_P<12>

CPU_CFG<17>

CPU_CFG<14>

CPU_CFG<13>

CPU_CFG<7>

CPU_CFG<8>

=PEG_R2D_C_N<2>

=PEG_D2R_N<0>

=PEG_D2R_N<1>

=PEG_R2D_C_N<6>

CPU_PEG_COMP

DMI_N2S_N<1>

DMI_N2S_N<0>

CPU_FDI_TX_P<7>

CPU_FDI_TX_P<5>

TP_CPU_RSVD<15>

TP_CPU_RSVD<14>

TP_CPU_RSVD<13>

TP_CPU_RSVD<12>

TP_CPU_RSVD<10>

CPU_FDI_TX_N<6>

CPU_FDI_TX_N<3>

CPU_FDI_COMPIO

=PPVCCIO_S0_CPU

R1010

1 2

U1000

W5

W4

V3

V4

Y3

Y4

AA4

AA5

V7

V6

W7

W8

Y6

Y7

AA7

AA8

AE2

AC5

AE5

AE1

AG3

AC4

AE4

AC8

AC7

AC2

AC3

AD2

AD1

AD4

AD3

AD7

AD6

AE7

AE8

AF3

AF2

AG2

AG1

P3

P4

R2

R1

T4

T3

U2

U1

P8

P7

T7

T8

R6

R5

U5

U6

B4

B5

C4

B11

B12

D12

D11

H3

H4

J1

J2

K3

K4

L1

L2

M3

M4

N1

N2

C10

C9

E10

E9

B8

B7

C6

C5

A5

A6

E2

E1

F4

F3

G2

G1

C13

C14

E14

E13

G5

G6

K7

K8

J5

J6

M8

M7

L6

L5

N5

N6

G14

G13

F12

F11

J14

J13

D8

D7

D3

C3

E6

E5

F8

F7

G10

G9

U1000

H36

J36

M38

N36

N38

N39

N37

N40

G37

G36

J37

K36

L36

N35

L37

M36

J38

L35

A38

AU40

AW38

C2

D1

AB6

AB7

AD34

AD35

AD37

AE6

AF4

AG4

AJ11

AJ29

AJ30

AJ31

AN20

AP20

AT11

AT14

AU10

AV34

AW34

AY10

C38

C39

D38

H7

H8

J31

J33

J34

J9

K31

K34

K9

L31

L33

L34

L9

M34

N33

N34

AV1

AW2

AY3

B39

P35

P37

P39

R34

R36

R38

R40

R1011

1

2

051-9509

4.2.0

10 OF 113

10 OF 100

8

91

8

91

8

91

8

91

8

91

8

91

8

91

8

91

8

8

8

8

8

8

91

8

91

8

91

8

8

6

10 11 13 16 62

8

91

8

91

8

91

8

91

8

91

8

91

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8