ON Semiconductor NCP51820 User manual

High Speed Half-Bridge Driver for GaN Power Switches

NCP51820

The NCP51820 high−speed, gate driver is designed to meet the stringent requirements of driving enhancement mode (e−mode), high electron mobility transistor (HEMT) and gate injection transistor (GIT), gallium nitrade (GaN) power switches in off−line, half−bridge power topologies. The NCP51820 offers short and matched propagation delays with advanced level shift technology providing −3.5 V to +650 V (typical) common mode voltage range for the high−side drive and −3.5 V to +3.5 V common mode voltage range for the low−side drive. In addition, the device provides stable dV/dt operation rated up to 200 V/ns for both driver output stages in high speed switching applications.

To fully protect the gate of the GaN power transistor against excessive voltage stress, both drive stages employ a dedicated voltage regulator to accurately maintain the gate−source drive signal amplitude. The circuit actively regulates the driver’s bias rails and thus protects against potential gate−source over−voltage under various operating conditions.

The NCP51820 offers important protection functions such as independent under−voltage lockout (UVLO), monitoring VDD bias voltage and VDDH and VDDL driver bias and thermal shutdown based on die junction temperature of the device. Programmable dead−time control can be configured to prevent cross−conduction.

Features

•650 V, Integrated High−Side and Low−Side Gate Drivers

•UVLO Protections for VDD High and Low−Side Drivers

•Dual TTL Compatible Schmitt Trigger Inputs

•Split Output Allows Independent Turn−ON/Turn−OFF Adjustment

•Source Capability: 1 A; Sink Capability: 2 A

•Separated HO and LO Driver Output Stages

•1 ns Rise and Fall Times Optimized for GaN Devices

•SW and PGND: Negative Voltage Transient up to 3.5 V

•200 V/ns dV/dt Rating for all SW and PGND Referenced Circuitry

•Maximum Propagation Delay of Less Than 50 ns

•Matched Propagation Delays to Less Than 5 ns

•User Programmable Dead−Time Control

•Thermal Shutdown (TSD)

Typical Applications

•Driving GaN Power Transistors used in Full or Half−Bridge, LLC, Active Clamp Flyback or Forward, Totem Pole PFC and Synchronous Rectifier Topologies

•Industrial Inverters and Motor Drives

•AC to DC Converters

♥ Semiconductor Components Industries, LLC, 2019 |

1 |

February, 2021 − Rev. 3 |

|

www.onsemi.com

QFN15 4x4, 0.5P

CASE 485FN

MARKING DIAGRAM

|

|

51820A |

|

|

|

ALYW G |

|

|

|

G |

|

|

|

|

|

51820A |

= Specific Device Code |

||

A |

= Assembly Site |

||

L |

= Wafer Lot Number |

||

YW |

= Assembly Start Week |

||

G= Pb−Free Package

(Note: Microdot may be in either location)

PIN ASSIGNMENT

|

|

<![if ! IE]> <![endif]>VBST |

|

|

|

|

<![if ! IE]> <![endif]>VDD |

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

<![if ! IE]> <![endif]>15 |

|

|

|

|

|

|

|

<![if ! IE]> <![endif]>14 |

|

|

|

VDDH |

|

|

|

|

|

|

|

|

|

|

|

|

|

EN |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

1 |

|

|

|

|

|

|

|

|

|

13 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

HIN |

HOSRC |

2 |

|

|

|

|

|

|

|

|

|

12 |

|||

|

|

|

|

|

NCP51820 |

|

|

|

|

LIN |

||||

HOSNK |

3 |

|

|

|

11 |

|||||||||

|

|

|

(Top View) |

|

||||||||||

SW |

|

|

|

|

|

|

|

|

SGND |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||

4 |

|

|

|

|

|

|

|

|

|

10 |

||||

|

|

|

|

|

|

|

|

|

|

|

DT |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

<![if ! IE]> <![endif]>5 |

|

<![if ! IE]> <![endif]>6 |

|

<![if ! IE]> <![endif]>7 |

|

<![if ! IE]> <![endif]>8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

<![if ! IE]> <![endif]>VDDL |

<![if ! IE]> <![endif]>LOSRC |

<![if ! IE]> <![endif]>LOSNK |

<![if ! IE]> <![endif]>PGND |

|

||||||

ORDERING INFORMATION

Device |

Package |

Shipping† |

NCP51820AMNTWG |

QFN15 |

4000 / Tape |

|

(Pb−Free) |

& Reel |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

Publication Order Number:

NCP51820/D

NCP51820

VIN |

VDD |

| <![if ! IE]> <![endif]>VBST |

<![if ! IE]> <![endif]>VDD |

|

<![if ! IE]> <![endif]>15 |

|

|

<![if ! IE]> <![endif]>14 |

|

|

VDDH |

1 |

|

|

13 |

EN |

PWM |

HOSRC |

|

|

|

|

HIN |

|

2 |

|

|

12 |

mC |

||

|

|

|

|

|||

|

|

|

|

or |

||

HOSNK |

|

|

|

|

LIN |

|

3 |

NCP51820 |

11 |

DSP |

|||

|

|

(Top View) |

|

|

|

|

SW |

4 |

|

|

10 |

SGND |

|

POWER |

|

|

|

|

DT |

|

STAGE |

|

|

|

9 |

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

<![if ! IE]> <![endif]>5 |

<![if ! IE]> <![endif]>6 |

<![if ! IE]> <![endif]>7 |

<![if ! IE]> <![endif]>8 |

|

|

| <![if ! IE]> <![endif]>VDDL |

<![if ! IE]> <![endif]>LOSRC |

<![if ! IE]> <![endif]>LOSNK |

<![if ! IE]> <![endif]>PGND |

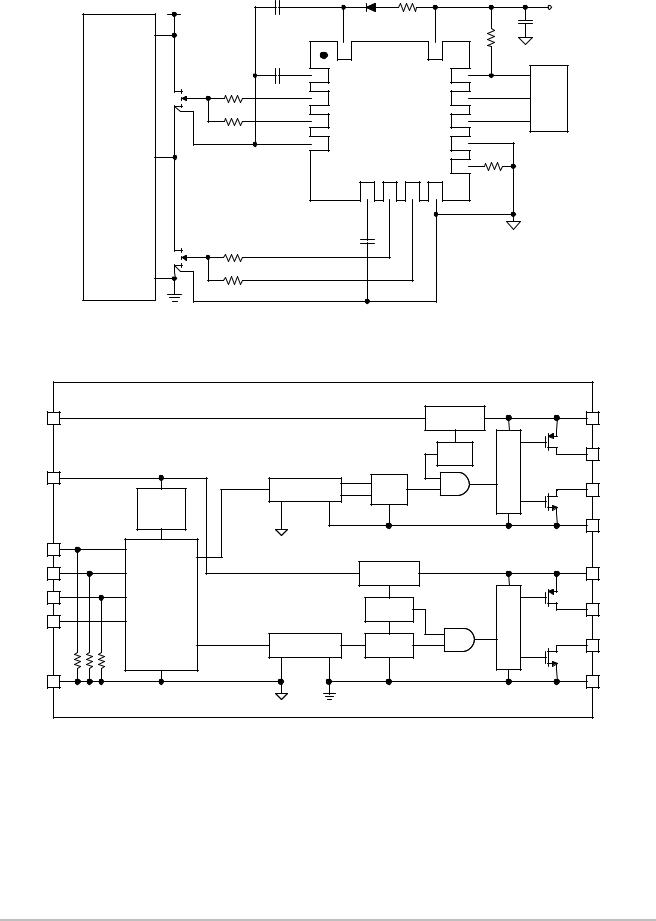

Figure 1. Typical Application Schematic

VBST |

|

|

|

|

|

VDDH |

|

|

|

|

|

|

REGULATOR |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VDDH |

|

|

|

|

|

|

|

UVLO |

<![if ! IE]> <![endif]>DRIVER |

VDD |

|

HO |

S |

|

|

|

|

|

|

|

|

|

|

|

|

|

VDD |

LEVEL SHIFTER |

R |

Q |

|

|

|

|

|

|

|

||||

|

UVLO |

|

|

|

|

|

|

|

8.5V/8V |

|

|

|

|

|

|

|

(ON/OFF) |

|

|

|

|

|

|

EN |

SCHMITT |

|

|

|

|

|

|

|

TRIGGER INPUT |

|

|

|

|

|

|

HIN |

SHOOT THOUGH |

|

|

VDDL |

|

|

|

|

REGULATOR |

|

|

||||

|

|

|

|

||||

|

PREVENTION |

|

|

|

|

|

|

LIN |

CYCLE−By− |

|

|

VDDL |

|

|

|

|

|

|

|

|

|||

DT |

CYCLE EDGE |

LO |

|

UVLO |

|

<![if ! IE]> <![endif]>DRIVER |

|

TRIGGERED |

|

|

|

|

|||

|

SHUTDOWN |

|

|

|

|

|

|

|

DEAD−TIME |

LEVEL SHIFTER |

DELAY |

|

|

||

|

|

|

|

|

|

||

|

MODE CONTROL |

|

|

|

|

|

|

SGND

Figure 2. Internal Block Diagram

www.onsemi.com

VDDH

HOSRC

HOSNK

SW

VDDL

LOSRC

LOSNK

PGND

2

NCP51820

PIN CONNECTIONS

|

|

|

<![if ! IE]> <![endif]>VBST |

|

|

|

|

|

<![if ! IE]> <![endif]>VDD |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

<![if ! IE]> <![endif]>15 |

|

|

|

|

|

|

|

<![if ! IE]> <![endif]>14 |

|

|

|

|

VDDH |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

13 |

EN |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

HOSRC |

2 |

|

|

|

|

|

|

|

|

|

12 |

HIN |

||

|

|

|

|

|

|

NCP51820 |

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

||||

HOSNK |

3 |

|

|

|

|

|

|

|

11 |

LIN |

||||

|

|

|

|

(Top View) |

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SW |

4 |

|

|

|

|

|

|

|

|

|

10 |

SGND |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

9 |

DT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

<![if ! IE]> <![endif]>5 |

|

<![if ! IE]> <![endif]>6 |

|

<![if ! IE]> <![endif]>7 |

|

<![if ! IE]> <![endif]>8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

<![if ! IE]> <![endif]>VDDL |

|

<![if ! IE]> <![endif]>LOSRC |

|

<![if ! IE]> <![endif]>LOSNK |

|

<![if ! IE]> <![endif]>PGND |

|

||

|

|

Figure 3. Pin Assignments – 15 Lead QFN (Top View) |

PIN DESCRIPTION |

|

|

|

|

|

Pin No. |

Name |

Description |

|

|

|

1 |

VDDH |

High−side driver positive bias voltage output |

|

|

|

2 |

HOSRC |

High−side driver sourcing output |

|

|

|

3 |

HOSNK |

High−side driver sinking output |

|

|

|

4 |

SW |

Switch−node / high−side driver return |

|

|

|

5 |

VDDL |

Low−side driver positive bias voltage output |

|

|

|

6 |

LOSRC |

Low−side driver sourcing output |

|

|

|

7 |

LOSNK |

Low−side driver sinking output |

|

|

|

8 |

PGND |

Power ground / low−side driver return |

|

|

|

9 |

DT |

Dead time adjustment / mode select |

|

|

|

10 |

SGND |

Logic / signal ground |

|

|

|

11 |

LIN |

Logic input for low−side gate driver output |

|

|

|

12 |

HIN |

Logic input for high−side gate driver output |

|

|

|

13 |

EN |

Logic input for disabling the driver (low power mode) |

|

|

|

14 |

VDD |

Bias voltage for high current driver |

|

|

|

15 |

VBST |

Bootstrap positive bias voltage |

|

|

|

www.onsemi.com

3

NCP51820

ABSOLUTE MAXIMUM RATINGS (All voltages are referenced to SGND pin unless otherwise noted)

Symbol |

Rating |

Min |

Max |

Unit |

|

|

|

|

|

|

|

VDD |

Low−side and logic−fixed supply voltage (PGND = SGND) |

−0.3 |

20 |

V |

|

VDDL |

Low−side supply voltage VDDL (internally regulated; output only, do not |

−0.3 |

5.5 |

V |

|

|

connect to external voltage source, referenced to PGND) |

|

|

|

|

|

|

|

|

|

|

VSW |

High−side common mode voltage range (SW) |

−3.5 |

650 |

V |

|

VDDH |

High−side floating supply voltage VDDH (internally regulated; output only, |

−0.3 |

5.5 |

V |

|

|

do not connect to external voltage source; referenced to SW) |

|

|

|

|

|

|

|

|

|

|

VBST_SGND |

High−side floating supply voltage VBST |

|

−0.3 |

670 |

V |

VBST_SW |

High−side floating supply voltage VBST (referenced to SW) |

−0.3 |

20 |

V |

|

VHOSRC, |

High−side floating driver sourcing/sinking output voltage (referenced to SW) |

−0.3 |

VDDH+0.3 |

V |

|

VHOSNK |

|

|

|

|

|

VPGND |

PGND voltage |

|

−3.5 |

3.5 |

V |

VLOSRC, |

Low−side driver sourcing/sinking output voltage (referenced to PGND) |

−0.3 |

VDDL+0.3 |

V |

|

VLOSNK |

|

|

|

|

|

VIN |

Logic input voltage (HIN, LIN, and EN) |

|

−0.3 |

VDD+0.3 |

V |

VDT |

Dead−time control voltage (DT) |

|

−0.3 |

VDD+0.3 |

V |

dVSW/dt |

Allowable offset voltage slew rate |

|

− |

200 |

V/ns |

TJ |

Operating Junction Temperature |

|

− |

150 |

°C |

TSTG |

Storage Temperature Range |

|

−55 |

150 |

°C |

|

Electrostatic Discharge Capability |

Human Body Model (Note 3) |

− |

1 |

kV |

|

|

|

|

|

|

|

|

Charged Device Model (Note 3) |

− |

1 |

kV |

|

|

|

|

|

|

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1.Refer to ELECTRICAL CHARACTERISTICS, RECOMMENDED OPERATING RANGES and/or APPLICATION INFORMATION for Safe Operating parameters.

2.VDD – PGND voltage must not exceed 20 V

3.This device series incorporates ESD protection and is tested by the following methods:

ESD Human Body Model tested per ANSI/ESDA/JEDEC JS−001−2012 ESD Charged Device Model tested per JESD22−C101.

4.This device contains latch−up protection and exceeds 100 mA per JEDEC Standard JESD78 Class I.

THERMAL CHARACTERISTICS

Symbol |

Rating |

|

Value |

Unit |

|

|

|

|

|

qJA |

Thermal Characteristics, |

IS0P |

245 |

°C/W |

|

QFN15 4x4 (Note 5) |

|

|

|

|

IS2P |

188 |

|

|

|

Thermal Resistance Junction−Ambient (Note 6) |

|

||

|

|

|

|

|

PD |

Power Dissipation (Note 6) |

IS0P |

0.51 |

W |

|

QFN15 4x4 (Note 5) |

|

|

|

|

IS2P |

0.665 |

|

|

|

|

|

||

|

|

|

|

|

5.Refer to ELECTRICAL CHARACTERISTICS, RECOMMENDED OPERATING RANGES and/or APPLICATION INFORMATION for Safe Operating parameters.

6.JEDEC standard: JESD51−2, JESD51−3. Mounted on 76.2×114.3×1.6 mm PCB (FR−4 glass epoxy material). IS0P: one single layer with zero power planes

IS2P: one single layer with two power planes

www.onsemi.com

4

NCP51820

RECOMMENDED OPERATING CONDITIONS (All voltages are referenced to SGND pin unless otherwise noted)

Symbol |

Rating |

Min |

Max |

Unit |

|

|

|

|

|

VDD |

Low−side and logic−fixed supply voltage |

9 |

17 |

V |

VSW−SGND |

SW−SGND maximum dc offset voltage (High−Side driver) |

− |

580 |

V |

VBST |

High−side floating supply voltage VBST |

− |

VSW+17 |

V |

VHOSRC, VHOSNK |

High−side floating driver sourcing/sinking output voltage |

− |

VDDH |

V |

VLOSRC, VLOSNK |

Low−side driver sourcing/sinking output voltage |

− |

VDDL |

V |

VIN |

Logic input voltage (HIN, LIN, and EN) |

− |

17 |

V |

PGND−SGND |

PGND−SGND maximum dc offset voltage (Low−Side driver) |

−3.0 |

3.0 |

V |

|

|

|

|

|

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

ELECTRICAL CHARACTERISTICS (VBIAS (VDD, VBST) = 15 V, DT = SGND = PGND and CLOAD = 330 pF for typical values

TA = 25°C, for min/max values TA = −40°C to +125°C, unless otherwise specified.) The VIN and IIN parameters are referenced to SGND. The VO and IO parameters are referenced to VSW and PGND and are applicable to the respective outputs HOSRC, HOSNK, LOSRC, and LOSNK.

Symbol |

Parameter |

Test Conditions and Description |

Min |

Typ |

Max |

Unit |

|

|

|

|

|

|

|

POWER SUPPLY SECTION (VDD) |

|

|

|

|

|

|

|

|

|

|

|

|

|

IQDD |

Quiescent VDD supply current |

VLIN = VHIN = 0 V, EN = 0 V |

− |

100 |

150 |

mA |

IPDD |

Operating VDD supply current |

fLIN = 500 kHz, average value |

− |

1.5 |

2.5 |

mA |

VDDUV+ |

VDD UVLO positive going threshold |

VDD = Sweep |

8.0 |

8.5 |

9.0 |

V |

VDDUV− |

VDD UVLO negative going threshold |

VDD = Sweep |

7.5 |

8.0 |

8.5 |

V |

VDDHYS |

VDD UVLO Hysteresis |

VDD = Sweep |

− |

0.5 |

− |

V |

tUVDDFLT |

VDD UVLO Filter Delay Time (Note 7) |

|

− |

5.3 |

− |

ms |

BOOTSTRAPPED POWER SUPPLY SECTION |

|

|

|

|

|

|

|

|

|

|

|

|

|

ILK |

Offset supply leakage current |

VBST = VSW = 600 V |

− |

− |

10 |

mA |

IQBST |

Quiescent VBST supply current |

VLIN = VHIN = 0 V, EN = 5 V |

− |

35 |

100 |

mA |

IPBST |

Operating VBST supply current |

fHIN = 500 kHz, average value |

− |

1.5 |

2.5 |

mA |

VBSTUV+ |

VBST UVLO positive going threshold |

VDD = 12 V |

− |

6.5 |

− |

V |

VBSTUV− |

VBST UVLO negative going threshold |

VDD = 12 V |

− |

6.0 |

− |

V |

VHYST |

VBST UVLO Hysteresis |

VDD = 12 V |

− |

0.5 |

− |

V |

GATE DRIVER POWER SUPPLY SECTION |

|

|

|

|

|

|

|

|

|

|

|

|

|

VDDH |

VDDH−VSW regulated voltage |

0 mA < IO < 10 mA |

4.94 |

5.20 |

5.46 |

V |

VDDL |

VDDL−PGND regulated voltage |

|

4.94 |

5.20 |

5.46 |

V |

INPUT LOGIC SECTION (HIN, LIN and EN) |

|

|

|

|

|

|

|

|

|

|

|

|

|

VINH |

High Level Input Voltage Threshold |

|

− |

− |

2.5 |

V |

VINL |

Low Level Input Voltage Threshold |

|

1.2 |

− |

− |

V |

VIN_HYS |

Input Logic Voltage Hysteresis |

|

− |

0.5 |

− |

V |

IIN+ |

High Level Logic Input Bias Current |

VHIN = VLIN = 5 V |

9 |

15 |

21 |

mA |

IIN− |

Low Level Logic Input Bias Current |

VHIN = VLIN = 0 V |

− |

− |

2.2 |

mA |

RIN |

Input Pull−down Resistance |

VHIN = VLIN = 5 V |

− |

333 |

− |

kW |

DEAD−TIME SECTION |

|

|

|

|

|

|

|

|

|

|

|

|

|

VDT,MIN |

Minimum Dead−Time Control Voltage |

RDT = 30 kW |

0.45 |

0.60 |

0.75 |

V |

tDT,MIN |

|

|

22 |

30 |

38 |

ns |

www.onsemi.com

5

NCP51820

ELECTRICAL CHARACTERISTICS (VBIAS (VDD, VBST) = 15 V, DT = SGND = PGND and CLOAD = 330 pF for typical values

TA = 25°C, for min/max values TA = −40°C to +125°C, unless otherwise specified.) The VIN and IIN parameters are referenced to SGND. The VO and IO parameters are referenced to VSW and PGND and are applicable to the respective outputs HOSRC, HOSNK, LOSRC, and LOSNK. (continued)

Symbol |

Parameter |

Test Conditions and Description |

Min |

Typ |

Max |

Unit |

|

|

|

|

|

|

|

DEAD−TIME SECTION |

|

|

|

|

|

|

|

|

|

|

|

|

|

VDT,MAX |

Maximum Dead−Time Control Voltage |

RDT = 200 kW |

3.1 |

4.0 |

4.8 |

V |

tDT,MAX |

|

|

160 |

200 |

240 |

ns |

DtDT |

Dead−Time mismatch between |

RDT = 30 kW |

− |

− |

5 |

ns |

|

LO → HO and HO → LO |

|

|

|

|

|

|

RDT = 200 kW |

− |

− |

10 |

ns |

|

|

|

|||||

VDT,0 |

Dead−Time Disable Threshold |

Cross conduction prevention active |

0.35 |

0.40 |

0.45 |

V |

VDT,OLE |

High− & Low−Side Overlap Enable |

Cross conduction prevention |

5.5 |

6.0 |

6.5 |

V |

|

Threshold |

disabled |

|

|

|

|

|

|

|

|

|

|

|

PROTECTION SECTION |

|

|

|

|

|

|

|

|

|

|

|

|

|

VUVTH_VDDX+ |

UVLO Threshold on VDDH and VDDL |

|

4.15 |

4.40 |

4.70 |

V |

|

positive going threshold |

|

|

|

|

|

|

|

|

|

|

|

|

VUVTH_VDDX− |

UVLO Threshold on VDDH and VDDL |

|

4.0 |

4.2 |

4.5 |

V |

|

negative going threshold |

|

|

|

|

|

|

|

|

|

|

|

|

TSD |

Thermal Shutdown (Note 7) |

|

150 |

− |

− |

°C |

|

|

|

|

|

|

|

hys |

Hysteresis of Thermal Shutdown |

|

− |

50 |

− |

°C |

|

(Note 7) |

|

|

|

|

|

|

|

|

|

|

|

|

GATE DRIVE OUTPUT SECTION |

|

|

|

|

|

|

|

|

|

|

|

|

|

VOH |

High−level output voltage, |

IOSRC = 10 mA |

− |

10 |

40 |

mV |

|

VVDDH−VHOSRC or VVDDL−VLOSRC |

|

|

|

|

|

VOL |

Low−level output voltage, |

IOSNK = 10 mA |

− |

5 |

20 |

mV |

|

VHOSNK−VSW or VLOSNK –PGND |

|

|

|

|

|

IOSRC |

Peak source current (Note 7) |

CLOAD = 200 pF, Rgate = 1 W |

0.9 |

1.0 |

− |

A |

IOSNK |

Peak sink current (Note 7) |

CLOAD = 200 pF, Rgate = 1 W |

1.8 |

2.0 |

− |

A |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

7. Guaranteed by design, is not tested in production.

DYNAMIC ELECTRICAL CHARACTERISTICS (VBIAS (VDD, VBST)=15 V, DT=SGND=PGND and CLOAD=330 pF, for typical values TA=25°C, for min/max values TA=−40°C to +125°C, unless otherwise specified.) (Notes 9)

Symbol |

Parameter |

Test Conditions |

Min |

Typ |

Max |

Unit |

|

|

|

|

|

|

|

IQDD |

Quiescent VDD supply current |

VLIN = VHIN = 0 V, EN = 0 V |

− |

100 |

150 |

mA |

tPDLON |

LOSRC turn−on propagation delay |

LIN rising to LOSRC rising (50% to 10%) |

− |

25 |

50 |

ns |

|

time |

|

|

|

|

|

|

|

|

|

|

|

|

tPDLOFF |

LOSNK turn−off propagation delay |

LIN falling to LOSNK falling (50% to 90%) |

− |

25 |

50 |

ns |

|

time |

|

|

|

|

|

|

|

|

|

|

|

|

tPDHON |

HOSRC turn−on propagation delay |

HIN rising to HOSRC rising (50% to 10%) |

− |

25 |

50 |

ns |

|

time |

SW = PGND |

|

|

|

|

|

|

|

|

|

|

|

tPDHOFF |

HOSNK turn−off propagation delay |

HIN falling to HOSNK falling (50% to 90%) |

− |

25 |

50 |

ns |

|

time |

SW = PGND |

|

|

|

|

|

|

|

|

|

|

|

tRL |

LOSRC turn−on rising time |

|

− |

2 |

4 |

ns |

tFL |

LOSNK turn−off falling time |

|

− |

1.5 |

3.0 |

ns |

tRH |

HOSRC turn−on rising time |

SW = PGND |

− |

2 |

4 |

ns |

tFH |

HOSNK turn−off falling time |

|

− |

1.5 |

3.0 |

ns |

www.onsemi.com

6

NCP51820

DYNAMIC ELECTRICAL CHARACTERISTICS (VBIAS (VDD, VBST)=15 V, DT=SGND=PGND and CLOAD=330 pF, for typical values TA=25°C, for min/max values TA=−40°C to +125°C, unless otherwise specified.) (Notes 9) (continued)

Symbol |

Parameter |

Test Conditions |

Min |

Typ |

Max |

Unit |

|

|

|

|

|

|

|

DtDEL |

Propagation Delay match |

HIN to HO and LIN to LO, SW = PGND |

− |

− |

5 |

ns |

tPW |

Minimum input pulse width |

|

− |

− |

10 |

ns |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

8. This parameter, although guaranteed by design, is not tested in production.

9. Performance guaranteed over the indicated operating temperature range by design and/or characterization tested at TJ = TA = 25°C.

Timing Diagram

Shown in Figure 4 are the timing waveform definitions matching the specified dynamic electrical characteristics specified in the gate drive output section.

50%

HIN |

|

|

|

|

(LIN) |

|

|

|

|

|

90% |

|

|

|

|

10% |

|

|

|

HO |

|

|

|

|

(LO) |

tPDHON |

tRH |

tPDHOFF |

tFH |

|

||||

|

(tPDLON) |

(tRL) |

(tPDLOFF) |

(tFL) |

Figure 4. Input to Output Timing Diagram

www.onsemi.com

7

Loading...

Loading...