HITACHI H8-3437 User Manual

To all our customers

Regarding the change of names mentioned in the document, such as Hitachi Electric and Hitachi XX, to Renesas Technology Corp.

The semiconductor operations of Mitsubishi Electric and Hitachi were transferred to Renesas Technology Corporation on April 1st 2003.

These operations include microcomputer, logic, analog and discrete devices, and memory chips other than DRAMs (flash memory, SRAMs etc.)

Accordingly, although Hitachi, Hitachi, Ltd., Hitachi Semiconductors, and other Hitachi brand names are mentioned in the document, these names have in fact all been changed to Renesas Technology Corp.

Thank you for your understanding. Except for our corporate trademark, logo and corporate statement, no changes whatsoever have been made to the contents of the document, and these changes do not constitute any alteration to the contents of the document itself.

Renesas Technology Home Page: www.renesas.com

Renesas Technology Corp.

Customer Support Dept.

April 1, 2003

Renesas Technology Corp.

Hitachi Single-Chip Microcomputer

H8/3437 Series

H8/3437

HD6473437, HD6433437

H8/3436

HD6433436

H8/3434

HD6473434, HD6433434

H8/3437W

HD6433437W

H8/3436W

HD6433436W

H8/3434W

HD6433434W

H8/3437F-ZTAT™

HD64F3437

H8/3437SF-ZTAT™

HD64F3437S

H8/3434F-ZTAT™

HD64F3434

Hardware Manual

ADE-602-077F Rev. 7.0 3/14/02 Hitachi, Ltd.

Cautions

1.Hitachi neither warrants nor grants licenses of any rights of Hitachi’s or any third party’s patent, copyright, trademark, or other intellectual property rights for information contained in this document. Hitachi bears no responsibility for problems that may arise with third party’s rights, including intellectual property rights, in connection with use of the information contained in this document.

2.Products and product specifications may be subject to change without notice. Confirm that you have received the latest product standards or specifications before final design, purchase or use.

3.Hitachi makes every attempt to ensure that its products are of high quality and reliability. However, contact Hitachi’s sales office before using the product in an application that

demands especially high quality and reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation, traffic, safety equipment or medical equipment for life support.

4.Design your application so that the product is used within the ranges guaranteed by Hitachi particularly for maximum rating, operating supply voltage range, heat radiation characteristics, installation conditions and other characteristics. Hitachi bears no responsibility for failure or damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as fail-safes, so that the equipment incorporating Hitachi

product does not cause bodily injury, fire or other consequential damage due to operation of the Hitachi product.

5.This product is not designed to be radiation resistant.

6.No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without written approval from Hitachi.

7.Contact Hitachi’s sales office for any questions regarding this document or Hitachi semiconductor products.

General Precautions on Handling of Product

1. Treatment of NC Pins

Note: Do not connect anything to the NC pins.

The NC (not connected) pins are either not connected to any of the internal circuitry or are they are used as test pins or to reduce noise. If something is connected to the NC pins, the operation of the LSI is not guaranteed.

2. Treatment of Unused Input Pins

Note: Fix all unused input pins to high or low level.

Generally, the input pins of CMOS products are high-impedance input pins. If unused pins are in their open states, intermediate levels are induced by noise in the vicinity, a passthrough current flows internally, and a malfunction may occur.

3. Processing before Initialization

Note: When power is first supplied, the product’s state is undefined.

The states of internal circuits are undefined until full power is supplied throughout the chip and a low level is input on the reset pin. During the period where the states are undefined, the register settings and the output state of each pin are also undefined. Design your system so that it does not malfunction because of processing while it is in this

undefined state. For those products which have a reset function, reset the LSI immediately after the power supply has been turned on.

4. Prohibition of Access to Undefined or Reserved Addresses Note: Access to undefined or reserved addresses is prohibited.

The undefined or reserved addresses may be used to expand functions, or test registers

may have been be allocated to these addresses. Do not access these registers; the system’s operation is not guaranteed if they are accessed.

Preface

The H8/3437 Series is a high-performance single-chip microcomputer that integrates peripheral functions necessary for system configuration with an H8/300 CPU featuring a 32-bit internal architecture as its core.

On-chip peripheral functions include ROM, RAM, four kinds of timers, a serial communication

interface (SCI), host interface (HIF), keyboard controller, D/A converter, A/D converter, and I/O ports, enabling the H8/3437 Series to be used as a microcontroller for embedding in high-speed

control systems. Flash memory (F-ZTAT™ *), PROM (ZTAT® *), and mask ROM are available as on-chip ROM, enabling users to respond quickly and flexibly to changing application

specifications and the demands of the transition from initial to full-fledged volume production.

Note: * F-ZTAT is a trademark of Hitachi, Ltd.

ZTAT is a registered trademark of Hitachi, Ltd.

Intended Readership: This manual is intended for users undertaking the design of an application system using a H8/3437 Series microcomputer. Readers using this manual require a basic knowledge of electrical circuits, logic circuits, and microcomputers.

Purpose: |

The purpose of this manual is to give users an understanding of the |

|

hardware functions and electrical characteristics of the H8/3437 Series. |

|

Details of execution instructions can be found in the H8/300 Series |

|

Programming Manual, which should be read in conjunction with the present |

|

manual. |

Using this Manual: |

|

•For an overall understanding of the H8/3437 Series’ functions

Follow the Table of Contents. This manual is broadly divided into sections on the CPU, system control functions, peripheral functions, and electrical characteristics.

•For a detailed understanding of CPU functions

Refer to the separate publication H8/300 Series Programming Manual.

•For a detailed description of a register’s function when the register name is known. Information on addresses, bit contents, and initialization is summarized in Appendix B, Internal I/O Register.

Note on bit notation: Bits are shown in high-to-low order from left to right.

Related Material: The latest information is available at our Web Site. Please make sure that you have the most up-to-date information available. http://www.hitachisemiconductor.com/

User's Manuals on the H8/3437 Series:

Manual Title |

ADE No. |

H8/3437 Series Hardware Manual |

This manual |

|

|

H8/300 Series Programming Manual |

ADE-602-025 |

|

|

Users manuals for development tools:

Manual Title |

|

|

|

|

|

|

|

ADE No. |

|||||||||

C/C++ Compiler, Assembler, Optimized Linkage Editor User's Manual |

|

ADE-702-247 |

|||||||||||||||

|

|

|

|

|

|

|

|

|

|||||||||

Simulator Debugger Users Manual |

|

|

|

|

|

|

|

ADE-702-282 |

|||||||||

|

|

|

|

|

|

|

|

|

|||||||||

Hitachi Debugging Interface Users Manual |

|

|

|

|

|

|

|

ADE-702-161 |

|||||||||

|

|

|

|

|

|

|

|

|

|||||||||

Hitachi Embedded Workshop Users Manual |

|

|

|

|

|

|

|

ADE-702-201 |

|||||||||

|

|

|

|

|

|

|

|

|

|||||||||

H8S, H8/300 Series Hitachi Embedded Workshop, Hitachi Debugging |

|

|

|

|

|

|

|

ADE-702-231 |

|||||||||

Interface Users Manual |

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Notes on S-Mask Model (Single-Power-Supply Specification)

There are two versions of the H8/3437F with on-chip flash memory: a dual-power-supply version and a single-power-supply (S-mask) version. Points to be noted when using the H8/3437F single- power-supply S-mask model are given below.

1.Notes on Voltage Application

12 V must not be applied to the S-mask model (single-power-supply specification), as this may permanently damage the device.

The flash memory programming power supply for the S-mask model (single-power-supply |

|

|

||

specification) is V |

CC . The programming power supply for the dual-power-supply model is the FV |

|

PP |

|

pin (12 V), but the single-power-supply model (S-mask model) does not have an FV |

PP |

pin. |

||

Also, in boot mode, 12 V has to be applied to the MD |

1 pin in the dual-power-supply model, but 12 |

|

||

V application is not necessary in the single-power-supply model (S-mask model). |

|

|

||

The maximum rating of the MD |

1 pin is V |

CC +0.3 V. Applying a voltage in excess of the |

|

|

maximum rating will permanently damage the device. |

|

|

|

|

Do not select the HN28F101 programmer setting for the S-mask model (single-power-supply specification). If this setting is made by mistake, 12 V will be applied to the STBY pin, possibly causing permanent damage to the device.

When using a PROM programmer to program the on-chip flash memory in the S-mask model (single-power-supply specification), use a PROM programmer that supports Hitachi

microcomputer devices with 64-kbyte on-chip flash memory. Also, only use the specified socket adapter. Using the wrong PROM programmer or socket adapter may damage the device.

The following PROM programmers support the S-mask model (single-power-supply specification).

DATA I/O: UNISITE, 2900, 3900, etc.

Minato: 1892, 1891, 1890, etc.

2.Product Type Names and Markings

Table 1 shows examples of product type names and markings for the H8/3437F (dual-power- supply specification) and H8/3437SF (single-power-supply specification), and the differences in flash memory programming power supply.

Table 1 Differences in H8/3437F and H8/3437F S-Mask Model Markings

|

Dual-Power-Supply Model: |

Single-Power-Supply Model: |

|

H8/3437F |

H8/3437F S-Mask Model |

|

|

|

Product type name |

HD64F3437F16/TF16 |

HD64F3437SF16/TF16 |

|

|

|

Sample markings |

|

|

|

|

|

H8/3437 |

|

|

H8/3437 |

|

|

|

|

|||

|

|

|

8M3 |

|

|

8M3 |

|

HD |

HD S |

||||

|

64F3437F16 |

64F3437F16 |

||||

|

|

|

JAPAN |

|

|

JAPAN |

|

|

|

|

“S” is printed above the type name |

||

|

|

|

||||

Flash memory |

V PP power supply |

V CC power supply |

||||

programming power |

(12.0 V ±0.6 V) |

(5.0 V ±10%) |

||||

|

||||||

supply

3.Differences in S-Mask Model

Table 2 shows the differences between the H8/3437F (dual-power-supply specification) and

H8/3437SF (single-power-supply specification).

Table 2 Differences between H8/3437F and H8/3437F S-Mask Model

|

Dual-Power-Supply Model: |

|

Single-Power-Supply Model: |

||

Item |

H8/3437F |

|

H8/3437F S-Mask Model |

||

|

|

|

|||

Program/ |

12 V must be applied from off-chip |

12 V application not required |

|||

erase voltage |

V PP |

(12.0 V ±0.6 V) |

|

V CC |

single-power-supply programming |

|

|

||||

|

|

|

|

V CC |

(5.0 V ±10%) |

FV PP (FWE) |

Dual function as FV |

PP power supply |

No programming control pin |

||

pin function |

and STBY function |

|

|

|

|

|

|

|

|

|

|

Programming |

• |

Writer mode |

|

(See section 21 for the use of these |

|

modes |

• |

On-board |

|

modes) |

|

Boot mode

User programming mode

Operating |

• |

Writer mode |

|

|

(See section 21 for the use of these |

|

|

|

|

||||||

modes allowing |

• |

Boot mode |

|

|

modes) |

|

|

|

|

|

|

|

|

|

|

on-board |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

• |

User programming mode |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

programming |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

On-board |

1-byte-unit programming |

|

32-byte-unit programming |

|

|

|

|

|

|

|

|

|

|

||

programming |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

unit |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Programming |

Select Hitachi stand-alone flash |

|

|

Special programming mode setting |

|

|

|

|

|

|

|||||

with PROM |

memory HN28F101 setting |

|

|

required. Use of PROM programmer |

|

|

|

|

|

|

|||||

programmer |

|

|

|

|

that supports Hitachi microcomputer |

|

|

|

|

|

|

||||

|

|

|

|

|

device types with 64-kbyte on-chip flash |

|

|

||||||||

|

|

|

|

|

memory. (128-byte-unit fast page |

|

|

|

|

||||||

|

|

|

|

|

programming) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Boot mode |

Reset release after MD |

1 = FV PP |

/STBY = |

|

|

|

|

|

|

|

|

|

|

|

|

Pin |

MD 1 |

|

MD 0 |

|

P9 2 |

|

P9 1 |

P9 0 |

|

||||||

setting |

12 V application |

|

|

|

|

||||||||||

|

|

Setting level |

0 |

|

0 |

|

1 |

|

1 |

|

1 |

|

|||

method |

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Reset release after above pin settings |

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

User program |

FV |

PP = 12 V application |

|

Control bits set by software |

|

|

|

|

|

|

|

|

|||

mode setting |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

method

|

Dual-Power-Supply Model: |

Single-Power-Supply Model: |

Item |

H8/3437F |

H8/3437F S-Mask Model |

Programming |

|

tMDS |

|

|

tMDS |

mode timing |

RES |

|

RES |

||

|

MD |

0 |

|

MD |

1, |

|

|

|

|

MD |

1 |

|

MD |

|

12 V |

P9 |

2 , |

|

1 |

|

|||

|

|

Min 0 |

s |

P9 |

1, |

|

|

|

12 V |

P9 |

0 |

|

V PP |

|

|

|

|

|

|

tMDS: 4tcyc (min.) |

|

tMDS: 4tcyc (min.) |

|

|

|

|

|

||

Prewrite |

Required before erasing |

Not required |

processing |

|

|

|

|

|

Programming |

Block corresponding to programming |

Settings at left not required |

processing |

address must be set in EBR1/EBR2 |

|

|

registers before programming |

|

|

|

|

EBR register |

EBR1, EBR2 |

EBR2 |

configuration |

|

|

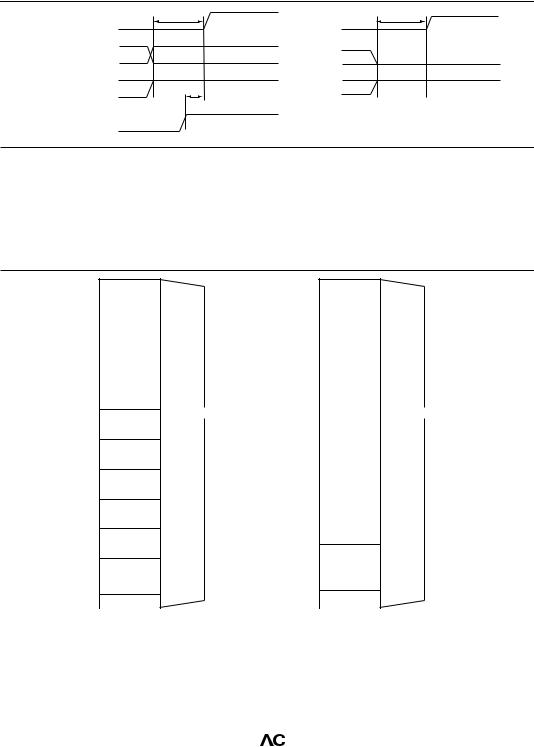

Memory map (block configuration)

SB0 (128 bytes) |

|

EB0 (1 kbyte) |

|

|

|

||

SB1 (128 bytes) |

|

|

|

|

|||

EB1 (1 kbyte) |

|

|

|

||||

|

|

|

|

|

|

|

|

SB2 (128 bytes) |

|

|

|

||||

|

|

|

|

||||

EB2 (1 kbyte) |

|

|

|

||||

|

|

|

|

|

|

|

|

SB3 (128 bytes) |

|

|

|

||||

|

|

|

|

||||

|

|

|

|

EB3 (1 kbyte) |

|

|

|

SB4 (512 bytes) |

|

|

|

||||

|

|

|

|

|

|

|

|

SB5 (1 kbyte) |

|

|

|

|

|||

|

|

|

|

|

|

|

|

SB6 (1 kbyte) |

|

|

|

|

|||

|

|

|

|

|

|

|

|

SB7 (1 kbyte) |

|

|

|

|

|||

|

|

|

|

|

|

|

|

LB0 (4 kbytes) |

|

|

|

|

|||

|

|

|

|

|

|

||

|

60 |

kbytes |

|

EB4 (24 kbytes) |

60 |

kbytes |

|

LB1(8 kbytes) |

|

|

|

||||

|

|

|

|

||||

LB2 (8 kbytes) |

|

|

|

|

|||

LB3 (8 kbytes) |

|

|

|

|

|||

EB5 (16 kbytes) |

|

|

|

||||

LB4 (8 kbytes) |

|

|

|

||||

LB5 (8 kbytes) |

|

|

|

|

|||

|

|

|

|

EB6 (12 kbytes) |

|

|

|

LB6 (12 kbytes) |

|

|

|

|

|||

|

LB7 (2 kbytes) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

EB7 (2 kbytes) |

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

Reset during |

Drive RES pin low for at least 10 |

RES pulse |

|

Drive RES pin low for at least 20 |

RES pulse |

|||||||||||||||||

operation |

system clock cycles (10ø). ( |

|

system clock cycles (20ø). ( |

|||||||||||||||||||

|

width t RESW = min. 10t cyc ) |

|

|

|

|

|

|

|

|

|

|

|

|

|

width t RESW = min. 20t cyc ) |

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Dual-Power-Supply Model: |

|

|

|

|

|

Single-Power-Supply Model: |

|

|

|

|

|

|||||||||

Item |

H8/3437F |

|

|

|

|

|

|

|

|

H8/3437F S-Mask Model |

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MDCR |

7 |

|

6 |

5 |

|

4 |

3 |

2 |

1 |

0 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

||

|

|

— |

|

— |

— |

|

— |

— |

— |

MDS1 |

MDS0 |

|

EXPE |

— |

— |

— |

— |

— |

MDS1 |

MDS0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

Bit 7: Expanded mode enable (EXPE) |

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

WSCR |

7 |

|

6 |

5 |

|

4 |

3 |

2 |

1 |

0 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

||

|

|

RAMS RAM0 |

|

|

CKDBL |

|

— |

WMS1WMS0 |

|

WC1 |

WC0 |

|

— |

— |

CKDBL |

FLSHE |

WMS1WMS0 |

|

WC1 |

WC0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

Bit 4: Flash memory control register |

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

enable (FLSHE) |

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

FLMCR1 |

7 |

|

6 |

5 |

|

4 |

3 |

2 |

1 |

0 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

||

|

|

V PP |

|

— |

— |

|

— |

EV |

PV |

E |

P |

|

FWE |

SWE |

— |

— |

EV |

PV |

E |

P |

|

Bit 7: Flash write enable (FWE)

Bit 6: Software write enable (SWE)

FLMCR2 —

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

FLER |

— |

— |

— |

— |

— |

ESU |

PSU |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Bit 7: Flash memory error (FLER) |

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Bit 1: Erase setup (ESU) |

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Bit 0: Program setup (PSU) |

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

EBR1 |

7 |

|

6 |

|

|

5 |

|

4 |

|

3 |

2 |

1 |

0 |

— |

|

|

|

|

|

|

|

|

|

|

|

|||||

|

LB7 |

LB6 |

|

LB5 |

LB4 |

LB3 |

|

LB2 |

|

LB1 |

|

LB0 |

|

This address is not used. |

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

EBR2 |

7 |

|

6 |

|

|

5 |

|

4 |

|

3 |

2 |

1 |

0 |

7 |

6 |

5 |

4 |

|

3 |

2 |

1 |

0 |

|

|||||||

|

SB7 |

SB6 |

SB5 |

SB4 |

|

SB3 |

|

SB2 |

|

SB1 |

SB0 |

|

|

|

EB7 |

|

EB6 |

EB5 |

EB4 |

EB3 |

|

EB2 |

EB1 |

EB0 |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Erase block register (EBR2) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

EB0 (1 kbyte): |

H'0000 to H'03FF |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

EB1 (1 kbyte): |

H'0400 to H'07FF |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

EB2 (1 kbyte): |

H'0800 to H'0BFF |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

EB3 (1 kbyte): |

H'0C00 to H'0FFF |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

EB4 (28 kbytes): H'1000 to H'7FFF |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

EB5 (16 kbytes): H'8000 to H'BFFF |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

EB6 (12 kbytes): H'C000 to H'EF7F |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

EB7 (2 kbytes): |

H'EF00 to H'F77F |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

Details |

See section 20, ROM (Dual-Power- |

|

|

|

|

|

|

|

|

|

|

|

|

See section 21, ROM (Single-Power- |

|||||

concerning |

Supply 60-Kbyte Flash Memory |

|

|

|

|

|

|

|

|

|

|

|

|

Supply 60-Kbyte Flash Memory |

|||||

flash memory |

Version) |

|

|

|

|

|

|

|

|

|

|

|

|

Version) |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

Electrical |

See section 23, Electrical |

|

|

|

|

|

|

|

|

|

|

|

|

See section 23, Electrical |

|||||

characteristics |

Characteristics |

|

|

|

|

|

|

|

|

|

|

|

|

Characteristics |

|

||||

|

|

|

|

|

|

|

|

|

|

||||||||||

Registers |

See Appendix B, Registers |

|

|

|

|

|

|

See Appendix B, Registers |

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Table 3 shows differences in the development environments of the H8/3437F (dual-power-supply specification) and H8/3437SF (single-power-supply specification).

Table 3 H8/3437F and H8/3437F S-Mask Model Development Environments

|

|

|

Dual-Power-Supply Model: |

Single-Power-Supply Model: |

Item |

|

H8/3437F |

H8/3437F S-Mask Model |

|

|

|

|

|

|

E6000 |

Emulator |

Hitachi |

Hitachi |

|

emulator |

unit |

HS3008EPI60H |

HS3008EPI60H |

|

|

|

|

|

|

|

|

User |

Hitachi |

Hitachi |

|

|

cable |

HS3437ECH61H |

HS3437ECH61H |

|

|

|

|

|

Programming |

|

Hitachi |

Minato |

|

socket adapter |

|

HS3434ESHF1H |

DATA I/O |

|

|

|

|

|

|

Adapter board |

|

Hitachi |

Hitachi |

|

|

|

|

HS0008EASF1H/2H |

HS0008EASF3H |

|

|

|

||

Windows interface |

Hitachi |

Hitachi |

||

software |

|

HS6400FWIW2SF |

HS6400FWIW2SF |

|

|

|

|

|

|

Table 4 shows differences in the pin settings of the H8/3437F (dual-power-supply specification) and H8/3437SF (single-power-supply specification).

Table 4 H8/3437F and H8/3437F S-Mask Model Pin Settings

|

Dual-Power-Supply Model: |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Single-Power-Supply Model: |

|

|

|

|||||||

Item |

H8/3437F |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

H8/3437F S-Mask Model |

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

Boot mode |

|

|

H8/3437F |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

H8/3437SF |

|

||||||||||

|

|

12 V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

V CC (5 V) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

23 |

P9 |

2 |

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

24 |

|

|||

|

|

8 |

FV |

|

/STBY |

|

|

P9 |

1 |

|

|||||||||||||||||||

|

|

PP |

|

|

|

|

|

|

|

|

|

|

|

|

25 |

|

|||||||||||||

|

|

5 |

|

|

P9 0 |

|

|||||||||||||||||||||||

|

|

MD |

|

|

|

|

|

|

|

|

|

5 |

|

||||||||||||||||

|

|

1 |

|

|

|

|

|

|

|

|

MD |

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

6 |

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MD |

0 |

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

V SS |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(GND) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

User programming |

|

|

H8/3437F |

|

|

|

|

|

|

|

|

There are no state transitions due to pin |

|

||||||||||||||||

mode |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

states. Transitions should be implemented |

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

12 V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

by means of register settings by software. |

|

|||||||

|

|

8 |

FV |

PP |

/STBY |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

List of Items Revised or Added for This Version

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Description |

Section |

|

|

|

Page |

Item |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(see Manual for details) |

|

|

|

|

|

|

|

||||||||||||||||||||

Notes on S-Mask Model |

|

|

|

Table 1 Differences in |

|

Single-Power-Supply |

||||||||||||||||||||

(Single-Power-Supply |

|

|

|

H8/3437F and H8/3437F S- |

|

Model: H8/3437F S- |

||||||||||||||||||||

Specification) |

|

|

|

Mask Model Markings |

|

mask model sample |

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

marking amended |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

1.1 Overview |

|

3 |

Table 1.1 |

|

Features |

|

|

|

|

|

|

“Other features” |

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

specifications amended. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

H8/3434F-ZTAT ROM |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

amended in “Series |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Lineup” specifications. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Notes 1 and 3 deleted |

|

|

|

|

|

|

|

||||||||||||||||||||

1.3.1 |

Pin Arrangement |

6 |

Figure 1.2 |

Pin Arrangement |

|

Rotated 90 degrees to |

||||||||||||||||||||

|

|

|

|

|

|

(FP-100B, TFP-100B, Top |

|

the left, so that pin 1 is at |

||||||||||||||||||

|

|

|

|

|

|

View) |

|

|

|

|

|

|

|

|

the bottom left. |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

6.2.2 |

Oscillator Circuit |

95 to 99 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Added |

||||

(H8/3437SF) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|||||||||||||||||||

12.3.2 |

Asynchronous |

|

264 |

Figure 12.5 |

Sample Flowchart |

|

Flowchart amended. |

|||||||||||||||||||

Mode |

|

|

|

|

|

for Transmitting Serial Data |

|

Procedure 1 description |

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

added. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

Section 13 |

I |

2C Bus |

283 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Descriptions 1 and 3 |

|||

Interface [Option] |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

deleted |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

13.4 |

Application Notes |

311 to 315 |

• Note on Issuance of |

|

|

|

|

|

|

|

|

Added |

||||||||||||||

|

|

|

|

|

|

|

|

Retransmission Start |

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

Condition |

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

• Note on Issuance of Stop |

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

Condition |

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

• |

|

Countermeasure |

|

|

||||||||||||||||

|

|

|

|

|

|

• |

|

Additional Note |

|

|

||||||||||||||||

|

|

|

|

|

|

• |

|

Precautions when Clearing |

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

the IRIC Flag when Using |

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

the Wait Function |

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

15.6 |

Application Notes |

354 |

Figure 15.10 |

|

Example of |

|

|

|

|

|

|

|

|

Figure amended |

||||||||||||

|

|

|

|

|

|

Analog Input Circuit |

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

18.3.2 |

Notes on |

|

|

373 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(1) description added. |

||

Programming |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

19.6.1 |

Writer Mode |

|

418 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Description amended |

|||

Setting |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Description |

Section |

|

Page |

Item |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(see Manual for details) |

||

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

21.1.7 |

Flash Memory |

504 |

|

|

Figure 21.2 |

Flash Memory |

|

“SWE” amended to |

|||||||||||||||||||

Operating Modes |

|

|

|

|

Related State Transitions |

|

“FLSHE”. |

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

505 |

|

Figure 21.3 |

Boot Mode |

|

Procedure 2 amended. |

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

506 |

|

|

Figure 21.4 |

User |

|

Procedure 2 amended. |

||||||||||||||||||

|

|

|

|

|

|

|

Programming Mode (Example) |

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

21.2.3 |

Erase Block |

511 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Bit 7 * and Note |

||

Register 2 (EBR2) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

description added. |

||

|

|

|

|

|

|

|

|

||||||||||||||||||||

21.3.1 |

Boot Mode |

516 |

|

RAM Area Allocation in Boot |

|

Description amended. |

|||||||||||||||||||||

|

|

|

|

|

|

|

Mode |

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

517 |

|

Figure 21.9 |

RAM Areas in |

|

Amended |

|||||||||||||||||||

|

|

|

|

|

|

|

Boot Mode |

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

Notes on Use of Boot Mode |

5 description amended. |

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

21.4 to 21.4.4 |

520 to 524 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Entire description |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

amended. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

21.5.1 |

Writer Mode |

528 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

* and Note description |

||

Setting |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

added. |

|

|

|

|

|

|

|

|

|

||||||||||||||||||||

21.5.3 |

Operation in |

538 |

|

Figure 21.22 |

Status Read |

|

Note amended |

||||||||||||||||||||

Writer Mode |

|

|

|

|

Mode Timing Waveforms |

|

|

||||||||||||||||||||

|

|

|

|

|

|

|

Table 21.19 |

Status Read |

|

|

|||||||||||||||||

|

|

|

|

|

|

|

Mode Return Codes |

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

||||||||||||||||||||

21.6 |

Flash Memory |

540 |

|

|

(1) Program with the specified |

|

Description amended. |

||||||||||||||||||||

Programming and Erasing |

|

|

|

|

voltage and timing |

|

|

||||||||||||||||||||

Precautions |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

541 |

|

Table 21.22 |

Area Accessed in |

|

FLSHE = 1 mode 2 |

||||||||||||||||||||||

|

|

|

|

|

|||||||||||||||||||||||

|

|

|

|

|

|

|

Each Mode with FLSHE = 0 |

|

amended |

||||||||||||||||||

|

|

|

|

|

|

|

and FLSHE = 1 |

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

22.3.5 |

Application Note |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 description deleted. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

23 |

Electrical |

|

553 to 604 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Heading number |

||

Characteristics |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

amended |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

23.3 |

Electrical |

579 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Entire description newly |

||

Characteristics |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

added. |

||

(H8/3437SF Low-Voltage |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Version) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||

B.2 |

Function |

665 |

I |

|

2C Bus Control Register |

|

Table amended and note |

||||||||||||||||||||

|

|

|

|

|

|

|

Bit 2 to 0: I2C Transfer Rate |

added |

|||||||||||||||||||

|

|

|

|

|

|

|

Select |

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Contents |

Section 1 |

Overview |

........................................................ |

|

1.1 |

Overview................................................................. |

1 |

|

1.2 |

Block Diagram ................................................................ |

5 |

|

1.3Pin Assignments and Functions

1.3.1Pin Arrangement .........................................................

1.3.2Pin Functions ..................................................................................................................

Section 2 |

CPU |

............................................................ |

2.1 Overview................................................................ |

19 |

|

2.1.1 Features ............................................................. |

19 |

|

2.1.2Address Space.........................................................

2.1.3Register Configuration......................................................

2.2 |

Register Descriptions ...................................................... |

......21 |

|

|

2.2.1 |

General Registers ........................................................ |

|

|

2.2.2 |

Control Registers ........................................................ |

|

|

2.2.3 |

Initial Register Values .................................................... |

|

2.3 |

Data Formats |

...................................................... ....... .... |

23 |

|

2.3.1 |

Data Formats in General Registers ................................................. |

|

|

2.3.2 ........................................................ |

Memory Data Formats |

|

2.4 |

Addressing ..............................................................Modes |

26 |

|

|

2.4.1 ........................................................ |

Addressing Mode |

|

|

2.4.2 ............................................... |

Calculation of Effective Address |

|

2.5 |

Instruction ..............................................................Set |

32 |

|

2.5.1Data Transfer Instructions ...................................................

2.5.2Arithmetic Operations .....................................................

2.5.3Logic Operations ........................................................

2.5.4Shift Operations ........................................................

2.5.5Bit Manipulations.......................................................

2.5.6Branching Instructions.....................................................

2.5.7System Control Instructions...................................................

2.5.8Block Data Transfer Instruction................................................

2.6 CPU States ............................................................. |

...49 |

2.6.1Overview..........................................................

2.6.2Program Execution State ....................................................

2.6.3Exception-Handling State ....................................................

2.6.4Power-Down State .......................................................

2.7Access Timing and Bus Cycle ........................................................

2.7.1Access to On-Chip Memory (RAM and ROM).............................................

2.7.2Access to On-Chip Register Field and External Devices .....................................

i

Section 3 |

MCU Operating Modes and Address Space |

............................ |

|

3.1 |

Overview................................................................. |

57 |

|

3.1.1Mode Selection ..........................................................

3.1.2Mode and System Control Registers .................................................

3.2System Control Register (SYSCR)........................................................

3.3Mode Control Register (MDCR) ..........................................................

3.4Address Space Map in Each Operating Mode ..................................................

Section 4 |

Exception Handling |

................................................ |

|

4.1 |

Overview................................................................. |

65 |

|

4.2Reset......................................................

4.2.1Overview...........................................................

4.2.2Reset Sequence ..........................................................

4.2.3Disabling of Interrupts after Reset...............................................................

4.3 |

Interrupts .................................................................. |

68 |

4.3.1Overview...........................................................

4.3.2Interrupt-Related Registers ....................................................

4.3.3External Interrupts .......................................................

4.3.4Internal Interrupts........................................................

4.3.5Interrupt Handling ........................................................

4.3.6Interrupt Response Time......................................................

4.3.7Precaution ............................................................

4.4 Note on Stack Handling ............................................................82

Section 5 |

Wait-State Controller |

............................................... |

||

5.1 |

Overview |

................................................................. |

83 |

|

|

5.1.1 |

Features ............................................................. |

83 |

|

5.1.2Block Diagram..........................................................

5.1.3Input/Output Pins........................................................

5.1.4Register Configuration.......................................................

5.2 |

|

Register Description....................................................... |

.......84 |

|

|

5.2.1 Wait-State Control Register (WSCR)................................................. |

|

5.3 |

|

Wait Modes.................................................................. |

86 |

Section 6 |

Clock Pulse Generator .............................................. |

|

|

6.1 |

Overview................................................................. |

89 |

|

6.1.1Block Diagram..........................................................

6.1.2Wait-State Control Register (WSCR)..................................................

6.2 |

Oscillator Circuit.......................................................... |

.....91 |

|

|

6.2.1 |

Oscillator (Generic Device) .................................................... |

|

|

6.2.2 |

Oscillator Circuit (H8/3437S).................................................... |

|

6.3 |

Duty Adjustment Circuit............................................................ |

99 |

|

6.4 |

Prescaler |

............................................................... |

....9 |

ii

Section 7 |

I/O Ports |

........................................................ |

||

7.1 |

Overview |

................................................................. |

101 |

|

7.2 |

Port 1................................................................... |

|

|

|

|

|

7.2.1 .......................................................... |

Overview |

4 |

7.2.2Register Configuration and Descriptions

7.2.3Pin Functions in Each Mode ...................................................

7.2.4Input Pull-Up Transistors....................................................

7.3Port 2.................................................................................................................

7.3.1 |

Overview |

...........................................................0 |

7.3.2Register Configuration and Descriptions

7.3.3Pin Functions in Each Mode ...................................................

7.3.4Input Pull-Up Transistors....................................................

7.4Port 3.................................................................................................................

7.4.1 |

Overview |

...........................................................6 |

7.4.2Register Configuration and Descriptions

7.4.3Pin Functions in Each Mode ...................................................

7.4.4Input Pull-Up Transistors....................................................

7.5Port 4.................................................................................................................

7.5.1 |

Overview |

..........................................................1 |

7.5.2Register Configuration and Descriptions

7.5.3Pin Functions ..........................................................

7.6Port 5.................................................................................................................

7.6.1 |

Overview |

...........................................................6 |

7.6.2Register Configuration and Descriptions

7.6.3Pin Functions ..........................................................

7.7Port 6.................................................................................................................

7.7.1 |

Overview |

...........................................................9 |

7.7.2Register Configuration and Descriptions

7.7.3Pin Functions ..........................................................

7.7.4Input Pull-Up Transistors....................................................

7.8Port 7.................................................................................................................

7.8.1 |

Overview |

...........................................................5 |

7.8.2Register Configuration and Descriptions

7.9Port 8................................................................................................................

7.9.1 Overview |

..........................................................6 |

7.9.2Register Configuration and Descriptions

7.9.3Pin Functions .........................................................

7.10Port 9.................................................................................................................

7.10.1 Overview |

...........................................................41 |

7.10.2Register Configuration and Descriptions

7.10.3Pin Functions ..........................................................

7.11Port A .................................................................................................................

7.11.1 Overview |

...........................................................46 |

iii

7.11.2Register Configuration and Descriptions................................................

7.11.3Pin Functions in Each Mode ....................................................

7.11.4Input Pull-Up Transistors.....................................................

7.12 Port B .................................................................. |

..15 |

7.12.1 Overview............................................................ |

50 |

7.12.2Register Configuration and Descriptions

7.12.3Pin Functions in Each Mode ....................................................

7.12.4Input Pull-Up Transistors.....................................................................................................

Section 8 |

16-Bit Free-Running Timer |

......................................... |

||

8.1 |

Overview |

................................................................. |

155 |

|

|

|

8.1.1 |

Features .............................................................. |

155 |

8.1.2Block Diagram..........................................................

8.1.3Input and Output Pins ......................................................

8.1.4Register Configuration.......................................................

8.2 |

Register Descriptions ............................................................. |

159 |

|

|

8.2.1 |

Free-Running Counter (FRC) ..................................................... |

|

|

8.2.2 |

Output Compare Registers A and B (OCRA and OCRB) .................................... |

159 |

8.2.3Input Capture Registers A to D (ICRA to ICRD)

8.2.4Timer Interrupt Enable Register (TIER)............................................

8.2.5Timer Control/Status Register (TCSR) ................................................

8.2.6Timer Control Register (TCR)....................................................

8.2.7Timer Output Compare Control Register (TOCR) ......................................................................................

8.3 |

CPU Interface........................................................... |

.....170 |

8.4 |

Operation................................................................... |

173 |

8.4.1FRC Increment Timing .......................................................

8.4.2Output Compare Timing .......................................................

8.4.3FRC Clear Timing ..........................................................

8.4.4Input Capture Timing........................................................

8.4.5Timing of Input Capture Flag (ICF) Setting .............................................

|

8.4.6 |

Setting of Output Compare Flags A and B (OCFA and OCFB) .......................... |

179 |

|

8.4.7 |

Setting of FRC Overflow Flag (OVF) ............................................... |

|

8.5 |

Interrupts |

.................................................... ........... |

...181 |

8.6 |

Sample Application........................................................ |

.......182 |

|

8.7 |

Application ........................................................ .......Notes |

183 |

|

Section 9 |

8-Bit Timers |

...................................................... |

9.1 Overview................................................................. |

189 |

|

9.1.1 Features ............................................................. |

189 |

|

9.1.2Block Diagram.........................................................

9.1.3Input and Output Pins .....................................................

9.1.4Register Configuration.......................................................

iv

9.2 Register Descriptions ............................................................ |

192 |

9.2.1 Timer Counter (TCNT)...................................................... |

|

9.2.2 Time Constant Registers A and B (TCORA and TCORB) .................................. |

19 |

9.2.3Timer Control Register (TCR)..................................................

9.2.4Timer Control/Status Register (TCSR) ..............................................

9.2.5Serial/Timer Control Register (STCR) ..............................................

9.3 Operation............................................................... |

..19 |

9.3.1TCNT Increment Timing .....................................................

9.3.2Compare-Match Timing.......................................................

9.3.3External Reset of TCNT ...................................................

9.3.4Setting of TCSR Overflow Flag (OVF).............................................