Hitachi H8S/2678 Series, H8S/2677, HD6432677, H8S/2676, HD64F2677 Reference Manual

...

Hitachi 16-Bit Single-Chip Microcomputer

H8S/2678 Series

H8S/2677

HD64F2677, HD6432677

H8S/2676

HD64F2676, HD6432676

H8S/2675

HD6432675

H8S/2673

HD6432673

H8S/2670

ADE-602-192A

Rev. 2.0

12/5/00

Hitachi, Ltd.

HD6412670

Reference Manual

H8S/2678 Series, H8S/2677 F-ZTAT™,

H8S/2676 F-ZTAT™ Reference Manual

Publication Date: 1st Edition, March 2000

2nd Edition, December 2000

Published by: Electronic Devices Sales & Marketing Group

Semiconductor & Integrated Circuits

Hitachi, Ltd.

Edited by: Technical Documentation Group

Hitachi Kodaira Semiconductor Co., Ltd.

Copyright © Hitachi, Ltd., 2000. All rights reserved. Printed in Japan.

Cautions

1. Hitachi neither warrants nor grants licenses of any rights of Hitachi’s or any third party’s

patent, copyright, trademark, or other intellectual property rights for information contained in

this document. Hitachi bears no responsibility for problems that may arise with third party’s

rights, including intellectual property rights, in connection with use of the information

contained in this document.

2. Products and product specifications may be subject to change without notice. Confirm that you

have received the latest product standards or specifications before final design, purchase or

use.

3. Hitachi makes every attempt to ensure that its products are of high quality and reliability.

However, contact Hitachi’s sales office before using the product in an application that

demands especially high quality and reliability or where its failure or malfunction may directly

threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear

power, combustion control, transportation, traffic, safety equipment or medical equipment for

life support.

4. Design your application so that the product is used within the ranges guaranteed by Hitachi

particularly for maximum rating, operating supply voltage range, heat radiation characteristics,

installation conditions and other characteristics. Hitachi bears no responsibility for failure or

damage when used beyond the guaranteed ranges. Even within the guaranteed ranges,

consider normally foreseeable failure rates or failure modes in semiconductor devices and

employ systemic measures such as fail-safes, so that the equipment incorporating Hitachi

product does not cause bodily injury, fire or other consequential damage due to operation of

the Hitachi product.

5. This product is not designed to be radiation resistant.

6. No one is permitted to reproduce or duplicate, in any form, the whole or part of this document

without written approval from Hitachi.

7. Contact Hitachi’s sales office for any questions regarding this document or Hitachi

semiconductor products.

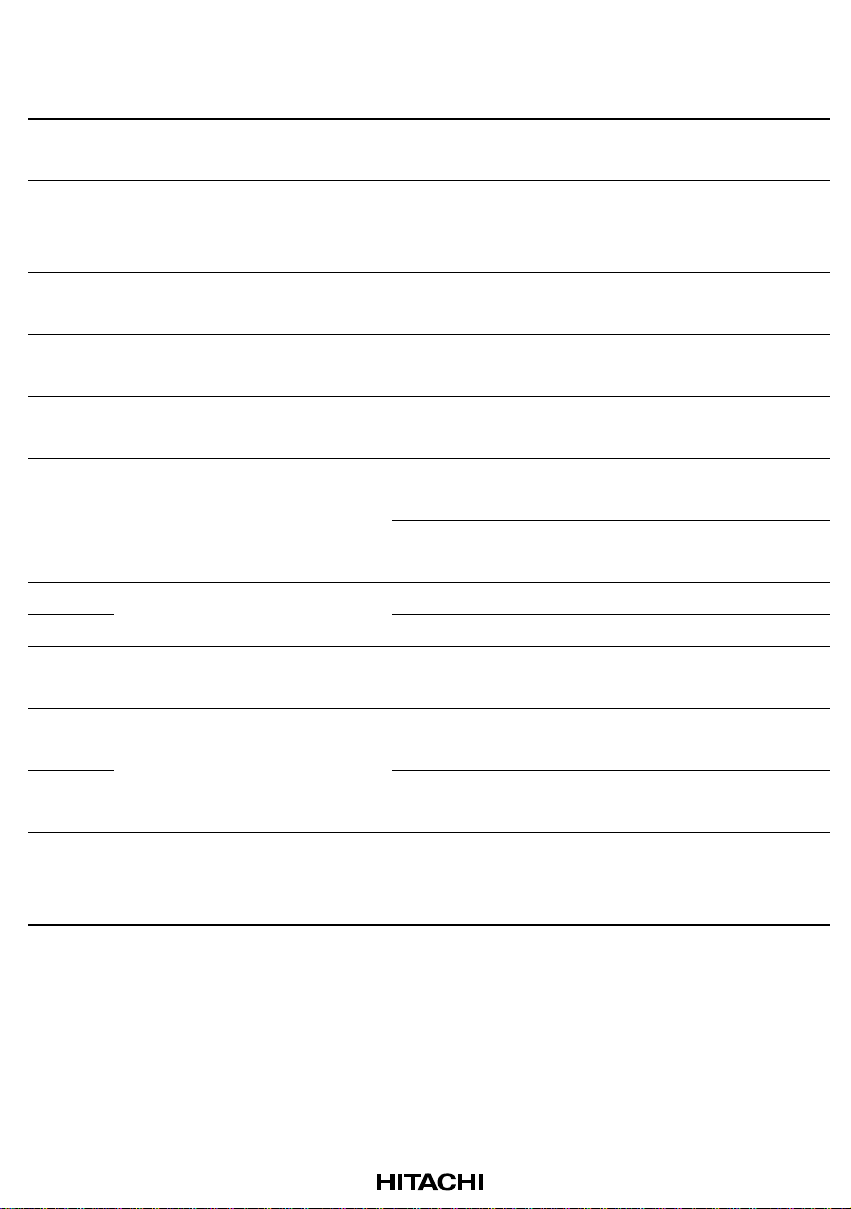

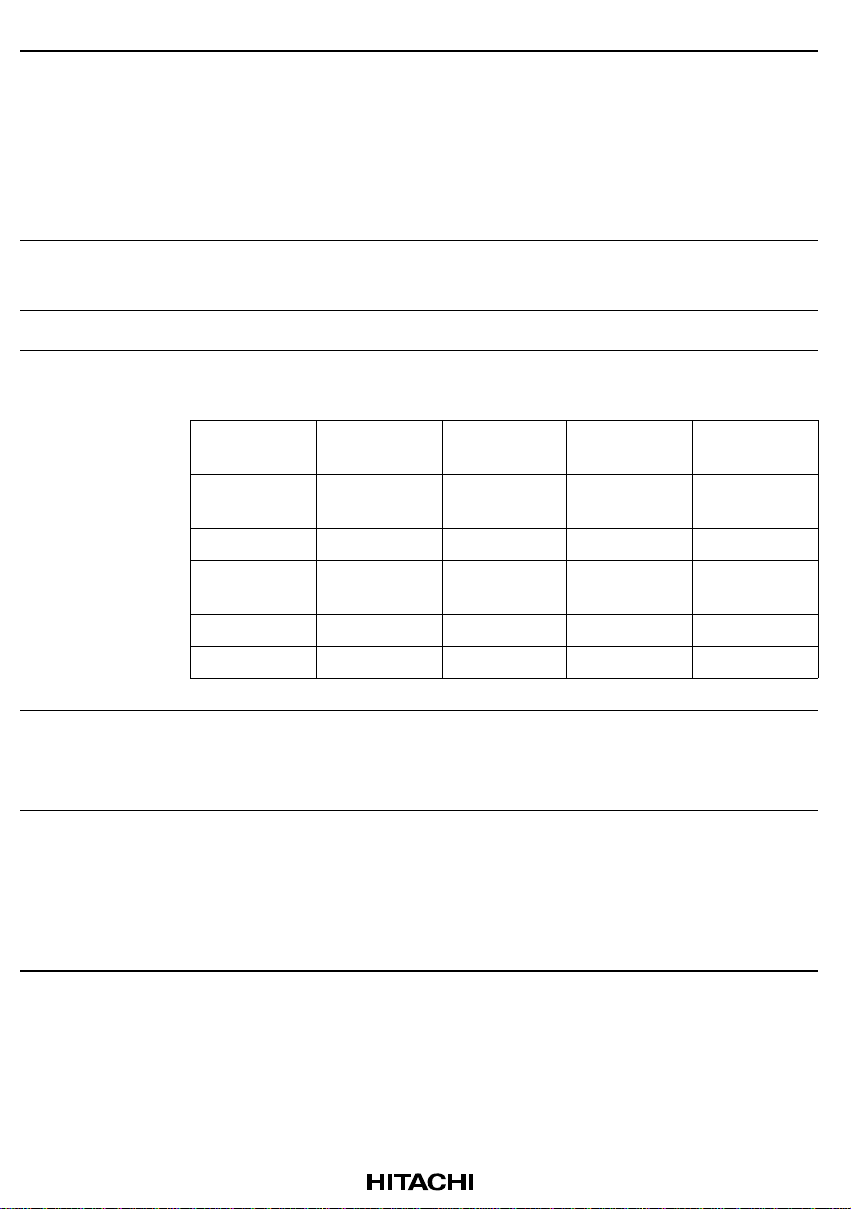

Main Revisions and Additions in this Edition

Page Item Revisions (See Manual for Details)

6 1.2 Block Diagram Figure 1.1 Internal Block Diagram

PLLVCC and PLLVSS pins added

151 4.5.12 Burst Operation Figure 4.29 Operation Timing in Fast Page Mode (1)

Title in parentheses amended

CAST = 1 → CAST = 0

286 5.16.3 Pin Functions Table 5.35 Port G Pin Functions

PG3 to PG0: Description amended

291 5.17.3 Pin Functions Table 5.37 Port H Pin Functions

PH1 and PH0: Description amended

295, 296 5.18.1 Port States in Each

Processing State

378 to

7.1.2 DC Characteristics Table 7.2 DC Characteristics

380

384 7.1.3 AC Characteristics Figure 7.3 (2) Oscillation Stabilization Timing added

414 Figure 7.36 WDT Output Timing amended

417 7.2.1 Absolute Maximum

Ratings

418, 419 7.2.2 DC Characteristics Table 7.12 DC Characteristics

420 Table 7.13 Permissible Output Currents

432, 433 7.2.6 Flash Memory

Characteristics

Table 5.38 I/O Port States in Each Processing State

PG5 and PG4 states amended

Entire table amended

Table 7.3 Permissible Output Currents

Max. values of ΣI

and Σ–IOH amended

OL

Table 7.11 Absolute Maximum Ratings

Note: Operating temperature ranges amended

Entire table amended

Max. values of ΣI

and Σ–IOH amended

OL

Conditions: Operating temperature range amended

Unit of t

amended

E

z and γ amended

Organization of H8S/2678 Series

Reference Manual

The following manuals are available for H8S/2678 Series products.

Table 1 H8S/2678 Series Manuals

Title Document Code

H8S/2600 Series, H8S/2000 Series Programming Manual ADE-602-083A

H8S/2678 Series Hardware Manual ADE-602-193A

H8S/2678 Series Reference Manual ADE-602-192A

The H8S/2600 Series, H8S/2000 Series Programming Manual gives a detailed description of the

architecture and instruction set of the H8S/2600 CPU incorporated into H8S/2678 Series products.

The H8S/2678 Series Hardware Manual describes the operation of on-chip functions common to

H8S/2678 Series products, and gives a detailed description of the related registers.

The H8S/2678 Series Reference Manual mainly covers information specific to H8S/2678 Series

products, including pin arrangement, I/O ports, MCU operating modes (memory maps), interrupt

vectors, bus control, and electrical characteristics, and also includes a brief description of all I/O

registers for the convenience of the user.

The contents of the H8S/2678 Series Hardware Manual and the H8S/2678 Series Reference

Manual are summarized in table 2.

Table 2 Contents of Hardware Manual and Reference Manual

Hardware

No. Item

1 Overview

2 MCU operating modes (including memory maps) —

3 Exception handling

4 Interrupt controller

5 Bus controller

6 DMA controller (DMAC) —

7 Data transfer controller (DTC) —

8 16-bit timer unit (TPU) —

9 Programmable pulse generator (PPG) —

10 8-bit timers —

11 Watchdog timer —

12 Serial communication interface (SCI) —

13 Smart card interface —

14 A/D converter —

15 D/A converter —

16 RAM —

17 ROM (flash memory) —

18 Clock pulse generator —

19 Power-down modes —

20 I/O ports (including port block diagrams) —

21 Electrical characteristics —

22 Register reference chart (in address order,

with function summary)

23 Instruction set —

24 Package dimension diagrams —

: Included

: Included (with detailed register descriptions)

—: Not included

Manual

—

Reference

Manual

(Including pin

arrangement)

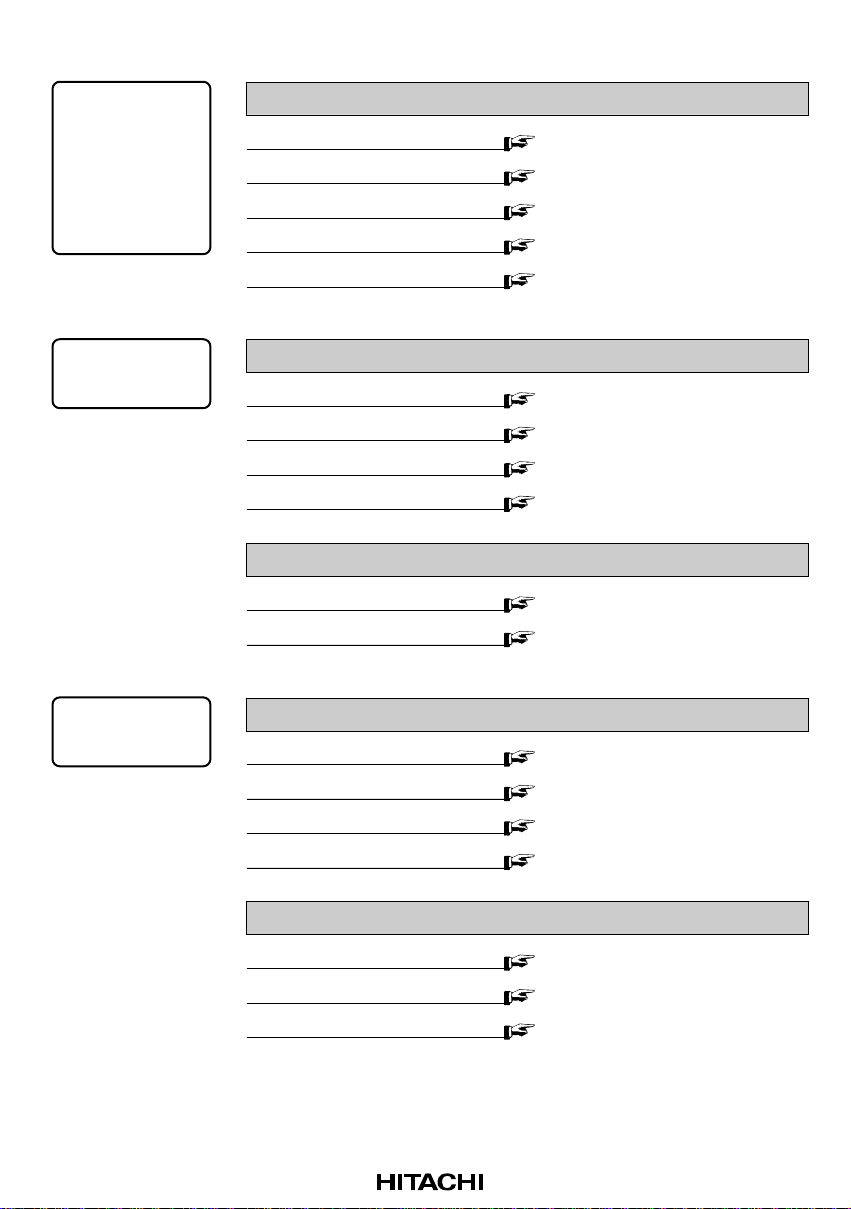

The following chart shows where to find various kinds of information for different purposes.

For product

evaluation

information, or

comparative

specification

information

for current

users of Hitachi

products

For detailed

information

on functions

For H8S/2678 Series specifications

Overview

Pin arrangement diagram

Block diagrams of function modules

Pin functions

Electrical characteristics

For details of operation of H8S/2678 Series modules

I/O port information

Interrupts and exception handling

Information on other modules

Pin functions

For information on H8S/2678 Series operating modes

List

Detailed descriptions

1.1 Overview

1.3 Pin Arrangement

Section 6 Peripheral Block Diagrams

1.5 Pin Functions

Section 7 Electrical Characteristics

Section 5 I/O Ports

Section 3 Exception Handling and

Interrupt Controller

H8S/2678 Series Hardware Manual

1.5 Pin Functions

1.4 Pin Functions in Each Operating

Mode

Section 2 MCU Operating Modes

For use as design

material

For information on H8S/2678 Series registers

List

To find a register from its address

To find register information by function

Setting procedure and notes

For information on H8S/2678 Series instructions

List

Operation description and notes

Program examples

Section 8 Registers

8.1 List of Registers (Address Order)

8.2 List of Registers (By Module)

H8S/2678 Series Hardware Manual

H8S/2600 Series, H8S/2000 Series

Programming Manual

Contents

Section 1 Overview........................................................................................................... 1

1.1 Overview............................................................................................................................ 1

1.2 Block Diagram................................................................................................................... 6

1.3 Pin Arrangement................................................................................................................ 7

1.4 Pin Functions in Each Operating Mode............................................................................. 8

1.5 Pin Functions..................................................................................................................... 20

1.6 Product Lineup................................................................................................................... 28

1.7 Package Dimensions..........................................................................................................28

Section 2 MCU Operating Modes................................................................................. 29

2.1 Overview............................................................................................................................ 29

2.1.1 Operating Mode Selection (F-ZTAT Version)..................................................... 29

2.1.2 Operating Mode Selection (ROMless and Mask ROM Versions)....................... 31

2.1.3 Register Configuration ......................................................................................... 33

2.2 Register Descriptions......................................................................................................... 33

2.2.1 Mode Control Register (MDCR).......................................................................... 33

2.2.2 System Control Register (SYSCR)....................................................................... 34

2.3 Operating Mode Descriptions............................................................................................ 35

2.3.1 Mode 1 (Expanded Mode with On-Chip ROM Disabled) ................................... 35

2.3.2 Mode 2 (Expanded Mode with On-Chip ROM Disabled) ................................... 35

2.3.3 Mode 3.................................................................................................................. 35

2.3.4 Mode 4 (Expanded Mode with On-Chip ROM Enabled)..................................... 36

2.3.5 Mode 5 (External ROM Activation Expanded Mode with On-Chip ROM

Enabled)................................................................................................................ 36

2.3.6 Mode 6 (External ROM Activation Expanded Mode with On-Chip ROM

Enabled)................................................................................................................ 36

2.3.7 Mode 7 (Single-Chip Activation Mode with On-Chip ROM Enabled) ............... 36

2.3.8 Modes 8 and 9 [F-ZTAT Version Only]............................................................... 37

2.3.9 Mode 10 [F-ZTAT Version Only]........................................................................ 37

2.3.10 Mode 11................................................................................................................ 37

2.3.11 Mode 12 ............................................................................................................... 37

2.3.12 Modes 13 and 14 [F-ZTAT Version Only]........................................................... 37

2.3.13 Mode 15 [F-ZTAT Version Only]........................................................................ 37

2.4 Pin Functions in Each Operating Mode............................................................................. 38

2.5 Memory Map in Each Operating Mode............................................................................. 39

Section 3 Exception Handling and Interrupt Controller......................................... 53

3.1 Overview............................................................................................................................ 53

3.1.1 Exception Handling Types and Priority ............................................................... 53

i

3.2 Interrupt Controller............................................................................................................ 54

3.2.1 Interrupt Controller Features ................................................................................ 54

3.2.2 Block Diagram...................................................................................................... 55

3.2.3 Pin Configuration ................................................................................................. 56

3.2.4 Register Configuration ......................................................................................... 57

3.3 Register Descriptions......................................................................................................... 58

3.3.1 Interrupt Control Register (INTCR)..................................................................... 58

3.3.2 Interrupt Priority Registers A to K (IPRA to IPRK) ............................................ 59

3.3.3 IRQ Enable Register (IER)................................................................................... 60

3.3.4 IRQ Sense Control Registers H and L (ISCRH, ISCRL)..................................... 61

3.3.5 IRQ Status Register (ISR) .................................................................................... 62

3.3.6 IRQ Pin Select Register (ITSR) ........................................................................... 64

3.3.7 Software Standby Release IRQ Enable Register (SSIER) ................................... 65

3.4 Interrupt Sources................................................................................................................ 66

3.4.1 External Interrupts................................................................................................ 66

3.4.2 Internal Interrupts................................................................................................. 67

3.4.3 Interrupt Vector Table .......................................................................................... 68

3.5 Interrupt Operation............................................................................................................. 74

3.5.1 Interrupt Control Modes and Interrupt Operation ................................................ 74

3.5.2 Interrupt Control Mode 0...................................................................................... 77

3.5.3 Interrupt Control Mode 2...................................................................................... 79

3.5.4 Interrupt Exception Handling Sequence............................................................... 81

3.5.5 Interrupt Response Times..................................................................................... 83

3.6 Usage Notes....................................................................................................................... 84

3.6.1 Contention between Interrupt Generation and Disabling..................................... 84

3.6.2 Instructions that Disable Interrupts....................................................................... 85

3.6.3 Periods when Interrupts are Disabled................................................................... 85

3.6.4 Interrupts during Execution of EEPMOV Instruction.......................................... 85

3.7 DTC and DMAC Activation by Interrupt.......................................................................... 85

3.7.1 Overview............................................................................................................... 85

3.7.2 Block Diagram...................................................................................................... 86

3.7.3 Operation .............................................................................................................. 87

Section 4 Bus Controller.................................................................................................. 91

4.1 Overview............................................................................................................................ 91

4.1.1 Features................................................................................................................. 91

4.1.2 Block Diagram ..................................................................................................... 93

4.1.3 Pin Configuration ................................................................................................. 94

4.1.4 Register Configuration ......................................................................................... 96

4.2 Register Descriptions......................................................................................................... 97

4.2.1 Bus Width Control Register (ABWCR)............................................................... 97

4.2.2 Access State Control Register (ASTCR).............................................................. 97

4.2.3 Wait Control Registers A and B (WTCRA, WTCRB)......................................... 98

ii

4.2.4 Read Strobe Timing Control Register (RDNCR)................................................. 99

4.2.5 CS Assertion Period Control Registers (CSACRH, CSACRL)........................... 101

4.2.6 Area 0 Burst ROM I/F Control Register (BROMCRH)

Area 1 Burst ROM I/F Control Register (BROMCRL) ....................................... 103

4.2.7 Bus Control Register (BCR)................................................................................. 105

4.2.8 DRAM Control Register (DRAMCR).................................................................. 107

4.2.9 DRAM Access Control Register (DRACCR) ...................................................... 112

4.2.10 Refresh Control Register (REFCR)...................................................................... 113

4.2.11 Refresh Timer Counter (RTCNT) ........................................................................ 117

4.2.12 Refresh Time Control Register (RTCOR)............................................................ 117

4.3 Overview of Bus Control................................................................................................... 118

4.3.1 Area Division........................................................................................................ 118

4.3.2 Bus Specifications ................................................................................................ 119

4.3.3 Memory Interfaces................................................................................................ 120

4.3.4 Chip Select Signals............................................................................................... 122

4.4 Basic Bus Interface............................................................................................................ 123

4.4.1 Overview............................................................................................................... 123

4.4.2 Data Size and Data Alignment ............................................................................. 123

4.4.3 Valid Strobes ........................................................................................................ 124

4.4.4 Basic Timing......................................................................................................... 126

4.4.5 Wait Control......................................................................................................... 134

4.4.6 Read Strobe (RD) Timing..................................................................................... 136

4.4.7 Extension of Chip Select (CS) Assertion Period.................................................. 137

4.5 DRAM Interface ................................................................................................................ 138

4.5.1 Overview............................................................................................................... 138

4.5.2 Setting DRAM Space ........................................................................................... 138

4.5.3 Address Multiplexing........................................................................................... 139

4.5.4 Data Bus ............................................................................................................... 139

4.5.5 Pins Used for DRAM Interface ............................................................................ 140

4.5.6 Basic Timing......................................................................................................... 141

4.5.7 Column Address Output Cycle Control ............................................................... 142

4.5.8 Row Address Output Cycle Control..................................................................... 143

4.5.9 Precharge State Control........................................................................................ 145

4.5.10 Wait Control......................................................................................................... 146

4.5.11 Byte Access Control............................................................................................. 149

4.5.12 Burst Operation..................................................................................................... 150

4.5.13 Refresh Control..................................................................................................... 154

4.5.14 DMAC and EXDMAC Single Address Transfer Mode and DRAM Interface.... 159

4.6 Burst ROM Interface ......................................................................................................... 162

4.6.1 Overview............................................................................................................... 162

4.6.2 Basic Timing......................................................................................................... 162

4.6.3 Wait Control......................................................................................................... 164

4.6.4 Write Access......................................................................................................... 164

iii

4.7 Idle Cycle........................................................................................................................... 165

4.7.1 Operation .............................................................................................................. 165

4.7.2 Pin States in Idle Cycle......................................................................................... 173

4.8 Write Data Buffer Function............................................................................................... 173

4.9 Bus Release........................................................................................................................ 174

4.9.1 Overview............................................................................................................... 174

4.9.2 Operation .............................................................................................................. 175

4.9.3 Pin States in External Bus Released State............................................................ 176

4.9.4 Transition Timing................................................................................................. 177

4.9.5 Usage Notes.......................................................................................................... 178

4.10 Bus Arbitration................................................................................................................... 179

4.10.1 Overview............................................................................................................... 179

4.10.2 Operation .............................................................................................................. 179

4.10.3 Bus Transfer Timing............................................................................................. 180

4.11 Bus Controller Operation in a Reset .................................................................................. 181

Section 5 I/O Ports............................................................................................................. 183

5.1 Overview............................................................................................................................ 183

5.2 Port 1.................................................................................................................................. 192

5.2.1 Overview............................................................................................................... 192

5.2.2 Register Configuration ......................................................................................... 193

5.2.3 Pin Functions........................................................................................................ 194

5.3 Port 2.................................................................................................................................. 203

5.3.1 Overview............................................................................................................... 203

5.3.2 Register Configuration ......................................................................................... 204

5.3.3 Pin Functions........................................................................................................ 205

5.4 Port 3.................................................................................................................................. 214

5.4.1 Overview............................................................................................................... 214

5.4.2 Register Configuration ......................................................................................... 215

5.4.3 Pin Functions........................................................................................................ 217

5.5 Port 4.................................................................................................................................. 220

5.5.1 Overview............................................................................................................... 220

5.5.2 Register Configuration ......................................................................................... 220

5.5.3 Pin Functions........................................................................................................ 221

5.6 Port 5.................................................................................................................................. 222

5.6.1 Overview............................................................................................................... 222

5.6.2 Register Configuration ......................................................................................... 222

5.6.3 Pin Functions........................................................................................................ 224

5.7 Port 6.................................................................................................................................. 227

5.7.1 Overview............................................................................................................... 227

5.7.2 Register Configuration ......................................................................................... 227

5.7.3 Pin Functions........................................................................................................ 229

5.8 Port 7.................................................................................................................................. 233

iv

5.8.1 Overview............................................................................................................... 233

5.8.2 Register Configuration ......................................................................................... 234

5.8.3 Pin Functions........................................................................................................ 236

5.9 Port 8.................................................................................................................................. 240

5.9.1 Overview............................................................................................................... 240

5.9.2 Register Configuration ......................................................................................... 241

5.9.3 Pin Functions........................................................................................................ 242

5.10 Port A................................................................................................................................. 246

5.10.1 Overview............................................................................................................... 246

5.10.2 Register Configuration ......................................................................................... 247

5.10.3 Pin Functions........................................................................................................ 252

5.10.4 MOS Input Pull-Up Function............................................................................... 253

5.11 Port B................................................................................................................................. 254

5.11.1 Overview............................................................................................................... 254

5.11.2 Register Configuration ......................................................................................... 255

5.11.3 Pin Functions........................................................................................................ 257

5.11.4 MOS Input Pull-Up Function............................................................................... 258

5.12 Port C................................................................................................................................. 259

5.12.1 Overview............................................................................................................... 259

5.12.2 Register Configuration ......................................................................................... 260

5.12.3 Pin Functions........................................................................................................ 262

5.12.4 MOS Input Pull-Up Function............................................................................... 263

5.13 Port D................................................................................................................................. 264

5.13.1 Overview............................................................................................................... 264

5.13.2 Register Configuration ......................................................................................... 265

5.13.3 Pin Functions........................................................................................................ 267

5.13.4 MOS Input Pull-Up Function............................................................................... 268

5.14 Port E................................................................................................................................. 269

5.14.1 Overview............................................................................................................... 269

5.14.2 Register Configuration ......................................................................................... 270

5.14.3 Pin Functions........................................................................................................ 272

5.14.4 MOS Input Pull-Up Function............................................................................... 273

5.15 Port F ................................................................................................................................. 274

5.15.1 Overview............................................................................................................... 274

5.15.2 Register Configuration ......................................................................................... 275

5.15.3 Pin Functions........................................................................................................ 278

5.16 Port G................................................................................................................................. 282

5.16.1 Overview............................................................................................................... 282

5.16.2 Register Configuration ......................................................................................... 282

5.16.3 Pin Functions........................................................................................................ 285

5.17 Port H................................................................................................................................. 287

5.17.1 Overview............................................................................................................... 287

5.17.2 Register Configuration ......................................................................................... 287

v

5.17.3 Pin Functions........................................................................................................ 290

5.18 Pin Functions..................................................................................................................... 292

5.18.1 Port States in Each Processing State..................................................................... 292

5.19 I/O Port Block Diagrams ................................................................................................... 297

5.19.1 Port 1..................................................................................................................... 297

5.19.2 Port 2..................................................................................................................... 301

5.19.3 Port 3..................................................................................................................... 303

5.19.4 Port 4..................................................................................................................... 307

5.19.5 Port 5..................................................................................................................... 308

5.19.6 Port 6..................................................................................................................... 313

5.19.7 Port 7..................................................................................................................... 316

5.19.8 Port 8..................................................................................................................... 319

5.19.9 Port A.................................................................................................................... 322

5.19.10 Port B.................................................................................................................... 324

5.19.11 Port C.................................................................................................................... 325

5.19.12 Port D.................................................................................................................... 326

5.19.13 Port E.................................................................................................................... 327

5.19.14 Port F.................................................................................................................... 328

5.19.15 Port G.................................................................................................................... 336

5.19.16 Port H.................................................................................................................... 341

Section 6 Supporting Module Block Diagrams........................................................ 345

6.1 Interrupt Controller............................................................................................................ 345

6.1.1 Features................................................................................................................. 345

6.1.2 Block Diagram...................................................................................................... 345

6.1.3 Pins....................................................................................................................... 346

6.2 DMA Controller................................................................................................................. 346

6.2.1 Features................................................................................................................. 346

6.2.2 Block Diagram...................................................................................................... 347

6.2.3 Pins....................................................................................................................... 348

6.3 Data Transfer Controller.................................................................................................... 348

6.3.1 Features................................................................................................................. 348

6.3.2 Block Diagram...................................................................................................... 349

6.4 EXDMA Controller (EXDMAC) ...................................................................................... 350

6.4.1 Features................................................................................................................. 350

6.4.2 Block Diagram...................................................................................................... 351

6.4.3 Pins....................................................................................................................... 352

6.5 16-bit Timer Pulse Unit..................................................................................................... 353

6.5.1 Features................................................................................................................. 353

6.5.2 Block Diagram...................................................................................................... 354

6.5.3 Pins....................................................................................................................... 355

6.6 Programmable Pulse Generator......................................................................................... 356

6.6.1 Features................................................................................................................. 356

vi

6.6.2 Block Diagram...................................................................................................... 357

6.6.3 Pins....................................................................................................................... 358

6.7 8-Bit Timer......................................................................................................................... 358

6.7.1 Features................................................................................................................. 358

6.7.2 Block Diagram...................................................................................................... 359

6.7.3 Pins....................................................................................................................... 360

6.8 Watchdog Timer ................................................................................................................ 360

6.8.1 Features................................................................................................................. 360

6.8.2 Block Diagram...................................................................................................... 361

6.8.3 Pins....................................................................................................................... 361

6.9 Serial Communication Interface........................................................................................ 362

6.9.1 Features................................................................................................................. 362

6.9.2 Block Diagram...................................................................................................... 362

6.9.3 Pins....................................................................................................................... 363

6.10 Smart Card Interface.......................................................................................................... 364

6.10.1 Features................................................................................................................. 364

6.10.2 Block Diagram...................................................................................................... 364

6.10.3 Pins....................................................................................................................... 365

6.11 IrDA................................................................................................................................... 365

6.11.1 Features................................................................................................................. 365

6.11.2 Block Diagram...................................................................................................... 366

6.11.3 Pins....................................................................................................................... 366

6.12 A/D Converter ................................................................................................................... 367

6.12.1 Features................................................................................................................. 367

6.12.2 Block Diagram...................................................................................................... 368

6.12.3 Pins....................................................................................................................... 369

6.13 D/A Converter ................................................................................................................... 370

6.13.1 Features................................................................................................................. 370

6.13.2 Block Diagram...................................................................................................... 370

6.13.3 Pins....................................................................................................................... 371

6.14 RAM .................................................................................................................................. 372

6.14.1 Features................................................................................................................. 372

6.14.2 Block Diagram...................................................................................................... 372

6.15 ROM .................................................................................................................................. 373

6.15.1 Features................................................................................................................. 373

6.15.2 Block Diagrams.................................................................................................... 373

6.16 Clock Pulse Generator ....................................................................................................... 375

6.16.1 Features................................................................................................................. 375

6.16.2 Block Diagram...................................................................................................... 375

Section 7 Electrical Characteristics.............................................................................. 377

7.1 Electrical Characteristics of Mask ROM Version (H8S/2677, H8S/2676, H8S/2675,

H8S/2673) and ROMless Version (H8S/2670) ................................................................. 377

vii

7.1.1 Absolute Maximum Ratings................................................................................. 377

7.1.2 DC Characteristics................................................................................................ 378

7.1.3 AC Characteristics................................................................................................ 381

7.1.4 Conversion Characteristics................................................................................... 415

7.1.5 D/A Conversion Characteristics........................................................................... 416

7.2 Electrical Characteristics of F-ZTAT Version (H8S/2677, H8S/2676)............................. 417

7.2.1 Absolute Maximum Ratings................................................................................. 417

7.2.2 DC Characteristics................................................................................................ 418

7.2.3 AC Characteristics................................................................................................ 421

7.2.4 A/D Conversion Characteristics........................................................................... 430

7.2.5 D/A Conversion Characteristics........................................................................... 431

7.2.6 Flash Memory Characteristics.............................................................................. 432

7.3 Usage Note......................................................................................................................... 434

Section 8 Registers ............................................................................................................ 435

8.1 List of Registers (Address Order)...................................................................................... 435

8.2 List of Registers (By Module)........................................................................................... 447

8.3 Register Descriptions......................................................................................................... 458

viii

Section 1 Overview

1.1 Overview

The H8S/2678 Series comprises microcomputers (MCUs), built around the H8S/2600 CPU,

employing Hitachi’s original architecture, and equipped with on-chip supporting functions

necessary for system configuration.

The H8S/2600 CPU has an internal 32-bit architecture, is provided with sixteen 16-bit general

registers and a concise, optimized instruction set designed for high-speed operation, and can

address a 16-Mbyte linear address space. The instruction set is upward-compatible with H8/300

and H8/300H CPU instructions at the object-code level, facilitating migration from the H8/300,

H8/300L, or H8/300H Series.

On-chip supporting functions required for system configuration include direct memory access

controller (DMAC), EXDMA controller (EXDMAC), and data transfer controller (DTC) bus

masters, ROM and RAM memory, a16-bit timer pulse unit (TPU), programmable pulse generator

(PPG), 8-bit timer module (TMR), watchdog timer module (WDT), serial communication

interfaces (SCI, IrDA), A/D converter, D/A converter, and I/O ports.

A high-functionality bus controller is also provided, enabling fast and easy connection of DRAM

and other kinds of memory.

The on-chip ROM is either single-power-supply flash memory (F-ZTAT™*) or mask ROM,

enabling users to respond quickly and flexibly to changing application specifications, growing

production volumes, and other conditions. The ROM is connected to the CPU via a 16-bit data

bus, enabling both byte and word data to be accessed in one state. Instruction fetching is thus

speeded up, and processing speed increased.

The features of the H8S/2678 Series are shown in table 1.1.

Note: * F-ZTAT is a trademark of Hitachi, Ltd.

1

Table 1.1 Overview

Item Specifications

CPU

• General-register architecture

Sixteen 16-bit general registers (also usable as sixteen 8-bit registers

or eight 32-bit registers)

• High-speed operation suitable for realtime control

Maximum operating frequency: 33 MHz

High-speed arithmetic operations

8/16/32-bit register-register add/subtract: 30 ns (33 MHz operation)

16 × 16-bit register-register multiply: 90 ns (33 MHz operation)

32 ÷ 16-bit register-register divide: 600 ns (33 MHz operation)

• Instruction set suitable for high-speed operation

Sixty-five basic instructions

8/16/32-bit transfer/arithmetic and logic instructions

Unsigned/signed multiply and divide instructions

Powerful bit-manipulation instructions

• CPU operating mode

Advanced mode: 16-Mbyte address space

Bus controller

DMA controller

(DMAC)

2

• Address space divided into 8 areas, with bus specifications settable

independently for each area

• Chip select output possible for each area

• Selection of 8-bit or 16-bit access space for each area

• 2-state or 3-state access space can be designated for each area

• Number of program wait states can be set for each area

• Maximum 8-Mbyte DRAM directly connectable

(or use of interval timer possible)

• External bus release function

• Selection of short address mode or full address mode

• Four channels in short address mode, two channels in full address mode

• Transfer possible in repeat mode, block transfer mode, etc.

• Single address mode transfer possible

• Can be activated by internal interrupt

Item Specifications

EXDMA controller

(EXDMAC)

• Four DMA channels exclusively for external bus use

• Selection of dual address mode or single address mode

• Transfer possible in burst transfer mode, block transfer mode, etc.

• Repeat area setting function

• Can operate in parallel with internal bus operations by internal bus master

Data transfer

controller (DTC)

16-bit timer-pulse

unit (TPU)

Programmable

pulse generator

(PPG)

8-bit timer,

2 channels

Watchdog timer

Serial communi-

cation interface

(SCI), 3 channels

• Activated by internal interrupt or software

• Multiple transfers or multiple types of transfer possible for one activation

source

• Transfer possible in repeat mode, block transfer mode, etc.

• Request can be sent to CPU for interrupt that activated DTC

• Six-channel 16-bit timer on-chip

• Pulse I/O processing capability for up to 16 pins

• Automatic 2-phase encoder count capability

• Maximum 16-bit pulse output possible with TPU as time base

• Output trigger selectable in 4-bit groups

• Non-overlap margin can be set

• Direct output or inverse output setting possible

• 8-bit up-counter (external event count capability)

• Two time constant registers

• Two-channel connection possible

• Watchdog timer or interval timer selectable

• Asynchronous mode or synchronous mode selectable

• Multiprocessor communication function

• Smart card interface function

• One channel (SCI0) functions as SCI with IrDA

Conforms to IrDA specification ver. 1.0

IrDA format encoding/decoding of TxD and RxD

3

Item Specifications

A/D converter

• Resolution: 10 bits

• Input: 12 channels

• 6.7 µs minimum conversion time (at 20 MHz operation)

• Single or scan mode selectable

• Sample-and-hold function

• A/D conversion can be activated by external trigger or timer trigger

D/A converter

I/O ports

Memory

Interrupt controller

Power-down state

• Resolution: 8 bits

• Output: 4 channels

• 103 input/output pins, 12 input pins

• Flash memory, mask ROM

• High-speed static RAM

Product

Name

H8S/2677 384 k/8 k In planning

H8S/2676 256 k/8 k HD64F2676 HD6432676 —

H8S/2675 128 k/8 k — In planning

H8S/2673 64 k/8 k — HD6432673 —

H8S/2670 —/8 k — — HD6412670

• 17 external interrupt pins (NMI, IRQ0 to IRQ15)

• 56 internal interrupt sources

• Eight interrupt priority levels settable

• Clock division mode

• Sleep mode

• Module stop mode

• Software standby mode

• Hardware standby mode

ROM/RAM

(Bytes)

F-ZTAT

Version

stage

Mask ROM

Version

In planning

stage

stage

ROMless

Version

—

—

4

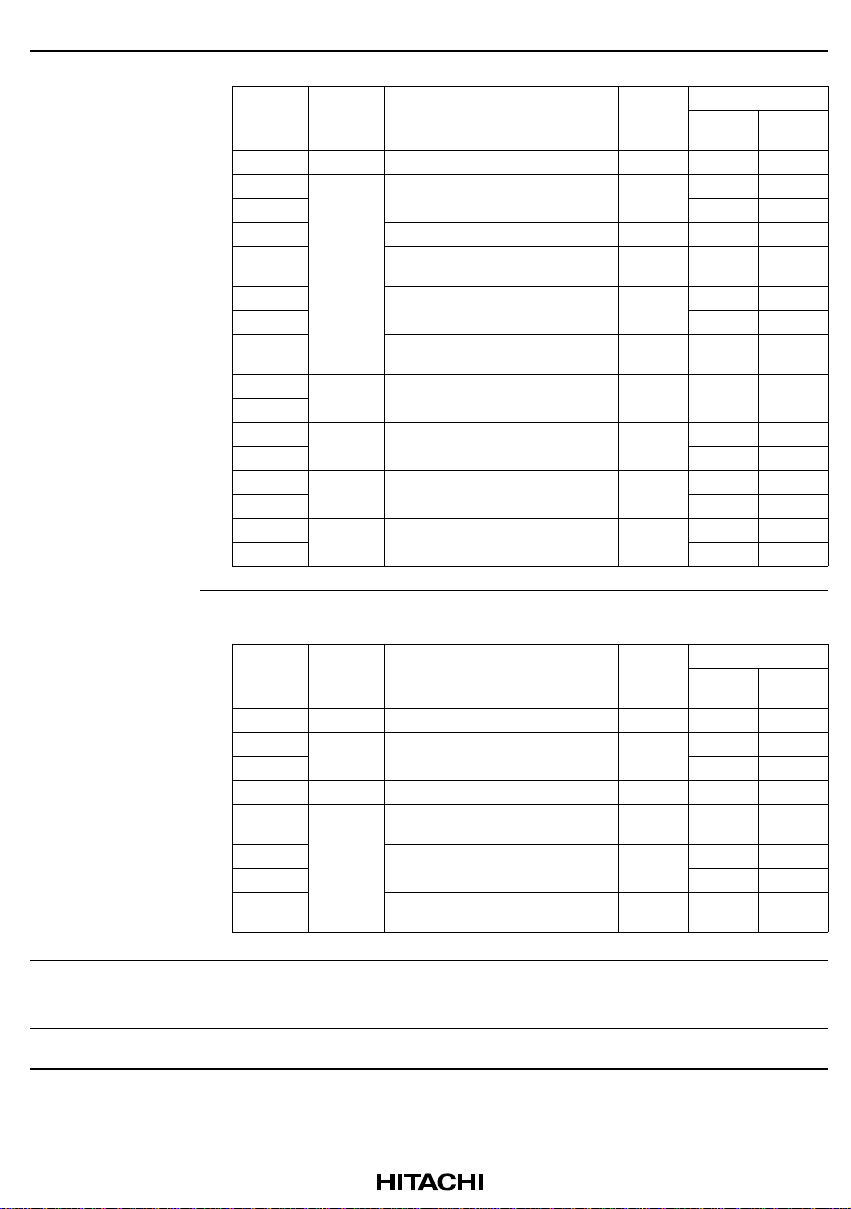

Item Specifications

Operating modes

• Selection of twelve MCU operating modes (F-ZTAT™ version)

MCU CPU

Operating

Mode

0 —— ———

1 Advanced Expanded mode with on-chip ROM Disabled 16 bits 16 bits

2

3 — ———

4 Expanded mode with on-chip ROM

5 External ROM activation expanded Enabled 16 bits 16 bits

6

7 Single-chip activation mode with

8 —— ———

9

10 Advanced Boot mode Enabled 8 bits 16 bits

11 — —

12 Advanced User program mode Enabled 8 bits 16 bits

13 16 bits 16 bits

14 Advanced User program mode Enabled 8 bits 16 bits

15 — 16 bits

• Selection of six MCU operating modes (mask ROM version, ROMless

version)

MCU CPU

Operating

Mode

0 —— ———

1* Advanced Expanded mode with on-chip ROM Disabled 16 bits 16 bits

2*

3 —— ———

4 Advanced Expanded mode with on-chip ROM

5 External ROM activation expanded Enabled 16 bits 16 bits

6

7 Single-chip activation mode with

Note: * Only modes 1 and 2 are available in the ROMless version.

Clock pulse

generator

• Built-in PLL circuits (×1, ×2, ×4)

Input clock frequency (2 to 33 MHz)

Operating

Mode

Operating

Mode

Description On-Chip

disabled

enabled

mode with on-chip ROM enabled

on-chip ROM enabled

Description On-Chip

disabled

enabled

mode with on-chip ROM enabled

on-chip ROM enabled

External Data Bus

Initial

ROM

Enabled 8 bits 16 bits

Enabled — 16 bits

External Data Bus

ROM

Enabled 8 bits 16 bits

Enabled — 16 bits

Maximum

Value

8 bits 16 bits

8 bits 16 bits

Initial

Value

8 bits 16 bits

8 bits 16 bits

Value

Maximum

Value

Packages

• 144-pin plastic QFP (FP-144)

5

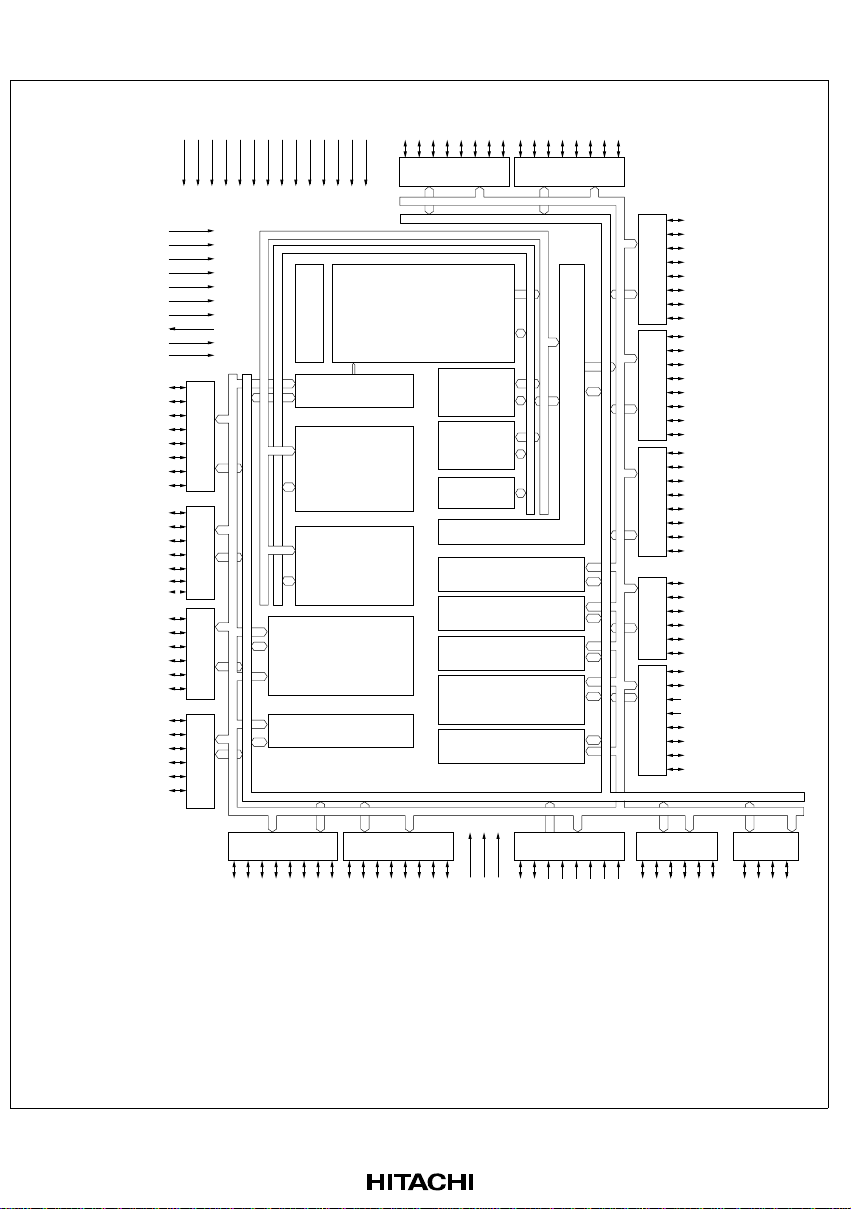

1.2 Block Diagram

PLLVCC

PLLVSS

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

PD7/D15

PD6/D14

PD5/D13

PD4/D12

PD3/D11

PD2/D10

PD1/D9

PD0/D8

PE7/D7

PE6/D6

PE5/D5

PE4/D4

PE3/D3

PE2/D2

PE1/D1

PE0/D0

MD2

MD1

MD0

EXTAL

XTAL

STBY

RES

WDTOVF

FWE

NMI

PF7/ø

PF6/AS

PF5/RD

PF4/HWR

PF3/LWR

PF2/LCAS/IRQ15

PF1/UCAS/IRQ14

PF0/WAIT

PG6/BREQ

PG5/BACK

PG4/BREQO

PG3/CS3

PG2/CS2

PG1/CS1

PG0/CS0

P65/TMO1/DACK1/IRQ13

P64/TMO0/DACK0/IRQ12

P63/TMCI1/TEND1/IRQ11

P62/TMCI0/TEND0/IRQ10

P61/TMRI1/DREQ1/IRQ9

P60/TMRI0/DREQ0/IRQ8

P85/EDACK3/(IRQ5)

P84/EDACK2/(IRQ4)

P83/ETEND3/(IRQ3)

P82/ETEND2/(IRQ2)

P81/EDREQ3/(IRQ1)

P80/EDREQ2/(IRQ0)

Port D

H8S/2600 CPU

generator

2

*

Port 6 Port G Port F

Port 8

Clock pulse

Interrupt controller

*

1

ROM

RAM

TPU

PPG

DTC

DMAC

EXDMAC

8-bit timer

D/A converter

A/D converter

WDT

SCI

Port E

Internal address bus

Internal data bus

Bus controller

Port APort BPort CPort 3Port 5

Peripheral address bus

Peripheral data bus

PA7/A23

PA6/A22

PA5/A21

PA4/A20

PA3/A19

PA2/A18

PA1/A17

PA0/A16

PB7/A15

PB6/A14

PB5/A13

PB4/A12

PB3/ A11

PB2/A10

PB1/A9

PB0/A8

PC7/A7

PC6/A6

PC5/A5

PC4/A4

PC3/A3

PC2/A2

PC1/A1

PC0/A0

P35/SCK1/(OE)

P34/SCK0

P33/RxD1

P32/RxD0/IrRxD

P31/TxD1

P30/TxD0/IrTxD

P57/AN15/DA3/IRQ7

P56/AN14/DA2/IRQ6

P55/AN13/IRQ5

P54/AN12/IRQ4

P53/ADTRG//IRQ3

P52/SCK2/IRQ2

P51/RxD2/IRQ1

P50/TxD2/IRQ0

6

P10/PO8/TIOCA0

P11/PO9/TIOCB0

P14/PO12/TIOCA1

P20/PO0/TIOCA3/(IRQ8)

P15/PO13/TIOCB1/TCLKC

P16/PO14/TIOCA2/EDRAK2

P21/PO1/TIOCB3/(IRQ9)

P17/PO15/TIOCB2/TCLKD/EDRAK3

P12/PO10/TIOCC0/TCLKA

P13/PO11/TIOCD0/TCLKB

1.

Notes:

ROM is not supported in the ROMless version.

2.

The FWE pin is used only in the F-ZTAT version. In other versions, this is an NC pin.

Figure 1.1 Internal Block Diagram

Port 4

Vref

AVCC

AVSS

P45/AN5

P44/AN4

P43/AN3

P42/AN2

P47/AN7/DA1

P46/AN6/DA0

P24/PO4/TIOCA4/(IRQ12)

P25/PO5/TIOCB4/(IRQ13)

P22/PO2/TIOCC3/(IRQ10)

P23/PO3/TIOCD3/(IRQ11)

P27/PO7/TIOCB5/EDRAK1/(IRQ15)

P26/PO6/TIOCA5/EDRAK0/(IRQ14)

P41/AN1

P40/AN0

Port 7

P73/ETEND1/(TEND1)

P72/ETEND0/(TEND0)

P75/EDACK1/(DACK1)

P74/EDACK0/(DACK0)

Port HPort 2Port 1

PH1/CS5

PH0/CS4

PH2/CS6/(IRQ6)

PH3/CS7/OE/(IRQ7)

P71/EDREQ1/(DREQ1)

P70/EDREQ0/(DREQ0)

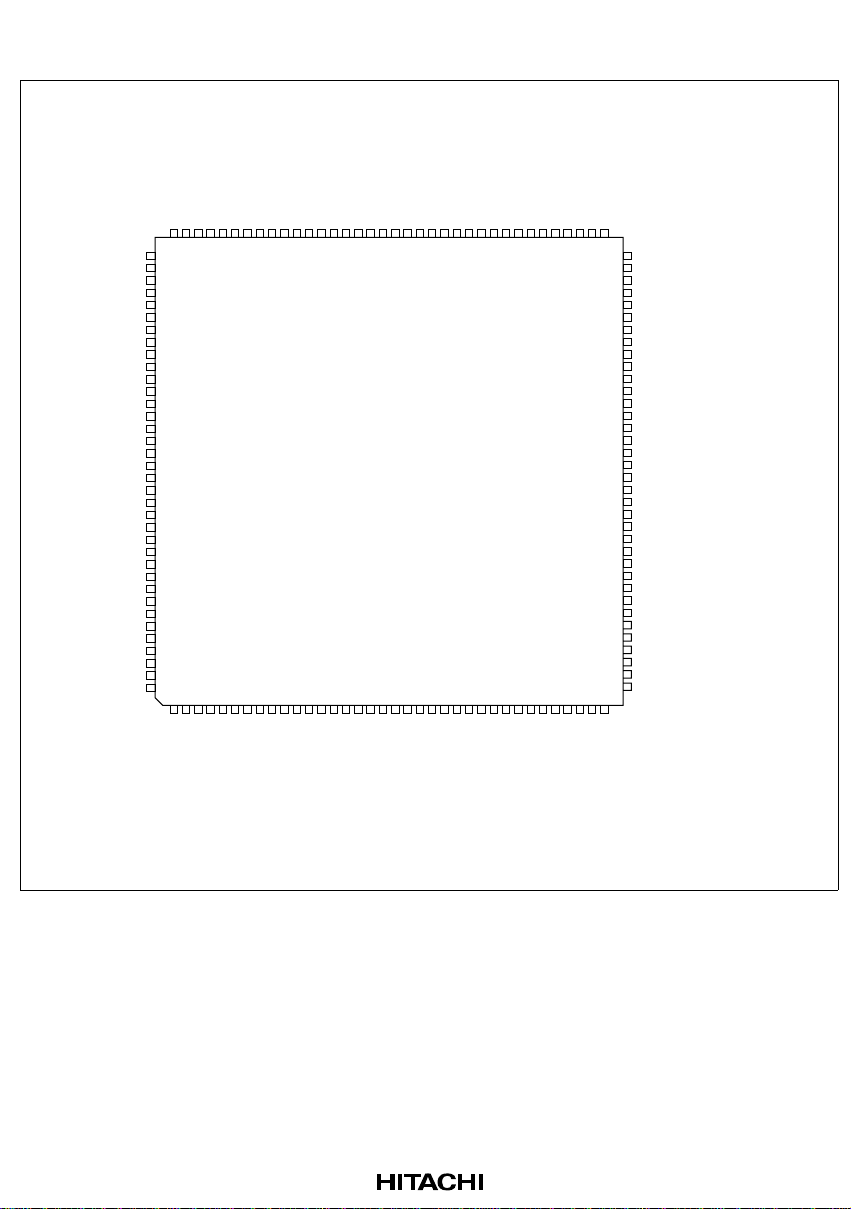

1.3 Pin Arrangement

P51/RxD2/IRQ1

P50/TxD2/IRQ0

PH1/CS5

PH0/CS4

PG3/CS3

PG2/CS2

PG1/CS1

PG0/CS0

STBY

108

107

106

105

104

103

102

101

VCC

PC0/A0

PC1/A1

100

PC2/A2

PC3/A3

P52/SCK2/IRQ2

P53/ADTRG/IRQ3

PH2/CS6/(IRQ6)

PH3/CS7/OE/(IRQ7)

PG4/BREQO

PG5/BACK

PG6/BREQ

VCC

P40/AN0

P41/AN1

P42/AN2

P43/AN3

Vref

AVCC

P44/AN4

P45/AN5

P46/AN6/DA0

P47/AN7/DA1

P54/AN12/IRQ4

P55/AN13/IRQ5

P56/AN14/DA2/IRQ6

P57/AN15/DA3/IRQ7

P80/EDREQ2/(IRQ0)

P81/EDREQ3/(IRQ1)

P82/ETEND2/(IRQ2)

AVSS

NC

P35/SCK1/(OE)

P34/SCK0

P33/RxD1

P32/RxD0/IrRxD

VSS

P31/TxD1

P30/TxD0/IrTxD

MD0

MD1

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

130

131

*2

132

133

134

135

136

137

138

139

140

141

142

143

144

1234567891011121314151617181920212223242526272829303132333435

MD2

VSS

XTAL

EXTAL

VCC

PF7/ø

PLLVCC

RES

PLLVSS

PF6/AS

PF5/RD

PF4/HWR

PF3/LWR

PF2/LCAS/IRQ15

PF1/UCAS/IRQ14

PF0/WAIT

P65/TMO1/DACK1/IRQ13

P64/TMO0/DACK0/IRQ12

P63/TMCI1/TEND1/IRQ11

P62/TMCI0/TEND0/IRQ10

PD0/D8

PD1/D9

PD2/D10

PD3/D11

VSS

PD4/D12

PD5/D13

999897969594939291908988878685848382818079787776757473

Pin Arrangement

(FP-144)

PC4/A4

PC5/A5

VSS

PC6/A6

PC7/A7

PB0/A8

PB1/A9

VSS

PB2/A10

PB3/A11

PB4/A12

PB5/A13

PB6/A14

PB7/A15

PA0/A16

PA1/A17

VSS

PA2/A18

PA3/A19

PA4/A20

PA5/A21

PA6/A22

NC

PA7/A23

PD6/D14

PD7/D15

72

PE0/D0

71

PE1/D1

70

PE2/D2

69

PE3/D3

68

VCC

67

PE4/D4

66

PE5/D5

65

PE6/D6

64

PE7/D7

63

*1

FWE

62

P61/TMRI1/DREQ1/IRQ9

61

P60/TMRI0/DREQ0/IRQ8

60

P27/PO7/TIOCB5/EDRAK1/(IRQ15)

59

P26/PO6/TIOCA5/EDRAK0/(IRQ14)

58

P25/PO5/TIOCB4/(IRQ13)

57

P24/PO4/TIOCA4/(IRQ12)

56

P23/PO3/TIOCD3/(IRQ11)

55

P22/PO2/TIOCC3/(IRQ10)

54

P21/PO1/TIOCB3/(IRQ9)

53

P20/PO0/TIOCA3/(IRQ8)

52

P17/PO15/TIOCB2/TCLKD/EDRAK3

51

P16/PO14/TIOCA2/EDRAK2

50

P15/PO13/TIOCB1/TCLKC

49

P14/PO12/TIOCA1

48

VSS

47

P13/PO11/TIOCD0/TCLKB

46

P12/PO10/TIOCC0/TCLKA

45

P11/PO9/TIOCB0

44

P10/PO8/TIOCA0

43

P75/EDACK1/(DACK1)

42

P74/EDACK0/(DACK0)

41

P73/ETEND1/(TEND1)

40

VCC

39

NMI

38

WDTOVF

37

36

P83/ETEND3/(IRQ3)

P84/EDACK2/(IRQ4)

P85/EDACK3/(IRQ5)

Notes: 1. The FWE pin is used only in the F-ZTAT version. In other versions, this is an NC pin.

2. An NC pin should be either fixed to VSS or opened.

Figure 1.2 Pin Arrangement (FP-144: Top View)

P72/ETEND0/(TEND0)

P70/EDREQ0/(DREQ0)

P71/EDREQ1/(DREQ1)

7

1.4 Pin Functions in Each Operating Mode

Table 1.2 Pin Functions in Each Operating Mode

Pin Name

Pin

No. Mode 1 Mode 2 Mode 4 Mode 5 Mode 6 Mode 7

1

MD2 MD2 MD2 MD2 MD2

2

P83/

ETEND3/

(IRQ3)

3

P84/

EDACK2/

(IRQ4)

4

P85/

EDACK3/

(IRQ5)

5

VCC VCC VCC VCC VCC

6

A0 A0 PC0/A0 A0 A0

7

A1 A1 PC1/A1 A1 A1

8

A2 A2 PC2/A2 A2 A2

9

A3 A3 PC3/A3 A3 A3

10

A4 A4 PC4/A4 A4 A4

P83/

ETEND3/

(IRQ3)

P84/

EDACK2/

(IRQ4)

P85/

EDACK3/

(IRQ5)

P83/

ETEND3/

(IRQ3)

P84/

EDACK2/

(IRQ4)

P85/

EDACK3/

(IRQ5)

P83/

ETEND3/

(IRQ3)

P84/

EDACK2/

(IRQ4)

P85/

EDACK3/

(IRQ5)

P83/

ETEND3/

(IRQ3)

P84/

EDACK2/

(IRQ4)

P85/

EDACK3/

(IRQ5)

MD2 VSS

When EXPE = 1:

P83/ETEND3/

(IRQ3)

When EXPE = 0:

P83/(IRQ3)

When EXPE = 1:

P84/EDACK2/

(IRQ4)

When EXPE = 0:

P84/(IRQ4)

When EXPE = 1:

P85/EDACK3/

(IRQ5)

When EXPE = 0:

P85/(IRQ5)

VCC VCC

When EXPE = 1:

PC0/A0

When EXPE = 0:

PC0

When EXPE = 1:

PC1/A1

When EXPE = 0:

PC1

When EXPE = 1:

PC2/A2

When EXPE = 0:

PC2

When EXPE = 1:

PC3/A3

When EXPE = 0:

PC3

When EXPE = 1:

PC4/A4

When EXPE = 0:

PC4

Flash

Memory

Programmer Mode

NC

NC

NC

A0

A1

A2

A3

A4

8

Pin Name

Pin

No. Mode 1 Mode 2 Mode 4 Mode 5 Mode 6 Mode 7

11 A5 A5 PC5/A5 A5 A5 When EXPE = 1:

PC5/A5

When EXPE = 0:

PC5

12 VSS VSS VSS VSS VSS VSS VSS

13 A6 A6 PC6/A6 A6 A6 When EXPE = 1:

PC6/A6

When EXPE = 0:

PC6

14 A7 A7 PC7/A7 A7 A7 When EXPE = 1:

PC7/A7

When EXPE = 0:

PC7

15 A8 A8 PB0/A8 A8 A8 When EXPE = 1:

PB0/A8

When EXPE = 0:

PB0

16 A9 A9 PB1/A9 A9 A9 When EXPE = 1:

PB1/A9

When EXPE = 0:

PB1

17 A10 A10 PB2/A10 A10 A10 When EXPE = 1:

PB2/A10

When EXPE = 0:

PB2

18 A11 A11 PB3/A11 A11 A11 When EXPE = 1:

PB3/A11

When EXPE = 0:

PB3

19 VSS VSS VSS VSS VSS VSS VSS

20 A12 A12 PB4/A12 A12 A12 When EXPE = 1:

PB4/A12

When EXPE = 0:

PB4

21 A13 A13 PB5/A13 A13 A13 When EXPE = 1:

PB5/A13

When EXPE = 0:

PB5

Flash

Memory

Programmer Mode

A5

A6

A7

A8

A9

A10

A11

A12

A13

9

Pin Name

Pin

No. Mode 1 Mode 2 Mode 4 Mode 5 Mode 6 Mode 7

22 A14 A14 PB6/A14 A14 A14 When EXPE = 1:

PB6/A14

When EXPE = 0:

PB6

23 A15 A15 PB7/A15 A15 A15 When EXPE = 1:

PB7/A15

When EXPE = 0:

PB7

24 A16 A16 PA0/A16 A16 A16 When EXPE = 1:

PA0/A16

When EXPE = 0:

PA0

25 A17 A17 PA1/A17 A17 A17 When EXPE = 1:

PA1/A17

When EXPE = 0:

PA1

26 VSS VSS VSS VSS VSS VSS VSS

27 A18 A18 PA2/A18 A18 A18 When EXPE = 1:

PA2/A18

When EXPE = 0:

PA2

28 A19 A19 PA3/A19 A19 A19 When EXPE = 1:

PA3/A19

When EXPE = 0:

PA3

29 A20 A20 PA4/A20 A20 A20 When EXPE = 1:

PA4/A20

When EXPE = 0:

PA4

30 PA5/A21 PA5/A21 PA5/A21 PA5/A21 PA5/A21 When EXPE = 1:

PA5/A21

When EXPE = 0:

PA5

31 PA6/A22 PA6/A22 PA6/A22 PA6/A22 PA6/A22 When EXPE = 1:

PA6/A22

When EXPE = 0:

PA6

Flash

Memory

Programmer Mode

A14

A15

A16

A17

A18

NC

NC

NC

NC

10

Pin Name

Pin

No. Mode 1 Mode 2 Mode 4 Mode 5 Mode 6 Mode 7

32 PA7/A23 PA7/A23 PA7/A23 PA7/A23 PA7/A23 When EXPE = 1:

PA7/A23

When EXPE = 0:

PA7

33 NC NC NC NC NC NC NC

34 P70/

EDREQ0/

(DREQ0)

35 P71/

EDREQ1/

(DREQ1)

36 P72/

ETEND0/

(TEND0)

37 WDTOVF WDTOVF WDTOVF WDTOVF WDTOVF WDTOVF NC

38 NMI NMI NMI NMI NMI NMI VCC

39 VCC VCC VCC VCC VCC VCC VCC

40 P73/

ETEND1/

(TEND1)

41 P74/

EDACK0/

(DACK0)

42 P75/

EDACK1/

(DACK1)

43 P10/PO8/

TIOCA0

P70/

EDREQ0/

(DREQ0)

P71/

EDREQ1/

(DREQ1)

P72/

ETEND0/

(TEND0)

P73/

ETEND1/

(TEND1)

P74/

EDACK0/

(DACK0)

P75/

EDACK1/

(DACK1)

P10/PO8/

TIOCA0

P70/

EDREQ0/

(DREQ0)

P71/

EDREQ1/

(DREQ1)

P72/

ETEND0/

(TEND0)

P73/

ETEND1/

(TEND1)

P74/

EDACK0/

(DACK0)

P75/

EDACK1/

(DACK1)

P10/PO8/

TIOCA0

P70/

EDREQ0/

(DREQ0)

P71/

EDREQ1/

(DREQ1)

P72/

ETEND0/

(TEND0)

P73/

ETEND1/

(TEND1)

P74/

EDACK0/

(DACK0)

P75/

EDACK1/

(DACK1)

P10/PO8/

TIOCA0

P70/

EDREQ0/

(DREQ0)

P71/

EDREQ1/

(DREQ1)

P72/

ETEND0/

(TEND0)

P73/

ETEND1/

(TEND1)

P74/

EDACK0/

(DACK0)

P75/

EDACK1/

(DACK1)

P10/PO8/

TIOCA0

When EXPE = 1:

P70/EDREQ0/

(DREQ0)

When EXPE = 0:

P70/(DREQ0)

When EXPE = 1:

P71/EDREQ1/

(DREQ1)

When EXPE = 0:

P71/(DREQ1)

When EXPE = 1:

P72/ETEND0/

(TEND0)

When EXPE = 0:

P72/(TEND0)

When EXPE = 1:

P73/ETEND1/

(TEND1)

When EXPE = 0:

P73/(TEND1)

When EXPE = 1:

P74/EDACK0/

(DACK0)

When EXPE = 0:

P74/(DACK0)

When EXPE = 1:

P75/EDACK1/

(DACK1)

When EXPE = 0:

P75/(DACK1)

P10/PO8/

TIOCA0

Flash

Memory

Programmer Mode

NC

NC

NC

NC

NC

NC

NC

NC

11

Pin Name

Pin

No. Mode 1 Mode 2 Mode 4 Mode 5 Mode 6 Mode 7

44 P11/PO9/

TIOCB0

45 P12/PO10/

TIOCC0/

TCLKA

46 P13/PO11/

TIOCD0/

TCLKB

47 VSS VSS VSS VSS VSS VSS VSS

48 P14/PO12/

TIOCA1

49 P15/PO13/

TIOCB1/

TCLKC

50 P16/PO14/

TIOCA2/

EDRAK2

51 P17/PO15/

TIOCB2/

TCLKD/

EDRAK3

52 P20/PO0/

TIOCA3/

(IRQ8)

53 P21/PO1/

TIOCB3/

(IRQ9)

54 P22/PO2/

TIOCC3/

(IRQ10)

55 P23/PO3/

TIOCD3/

(IRQ11)

P11/PO9/

TIOCB0

P12/PO10/

TIOCC0/

TCLKA

P13/PO11/

TIOCD0/

TCLKB

P14/PO12/

TIOCA1

P15/PO13/

TIOCB1/

TCLKC

P16/PO14/

TIOCA2/

EDRAK2

P17/PO15/

TIOCB2/

TCLKD/

EDRAK3

P20/PO0/

TIOCA3/

(IRQ8)

P21/PO1/

TIOCB3/

(IRQ9)

P22/PO2/

TIOCC3/

(IRQ10)

P23/PO3/

TIOCD3/

(IRQ11)

P11/PO9/

TIOCB0

P12/PO10/

TIOCC0/

TCLKA

P13/PO11/

TIOCD0/

TCLKB

P14/PO12/

TIOCA1

P15/PO13/

TIOCB1/

TCLKC

P16/PO14/

TIOCA2/

EDRAK2

P17/PO15/

TIOCB2/

TCLKD/

EDRAK3

P20/PO0/

TIOCA3/

(IRQ8)

P21/PO1/

TIOCB3/

(IRQ9)

P22/PO2/

TIOCC3/

(IRQ10)

P23/PO3/

TIOCD3/

(IRQ11)

P11/PO9/

TIOCB0

P12/PO10/

TIOCC0/

TCLKA

P13/PO11/

TIOCD0/

TCLKB

P14/PO12/

TIOCA1

P15/PO13/

TIOCB1/

TCLKC

P16/PO14/

TIOCA2/

EDRAK2

P17/PO15/

TIOCB2/

TCLKD/

EDRAK3

P20/PO0/

TIOCA3/

(IRQ8)

P21/PO1/

TIOCB3/

(IRQ9)

P22/PO2/

TIOCC3/

(IRQ10)

P23/PO3/

TIOCD3/

(IRQ11)

P11/PO9/

TIOCB0

P12/PO10/

TIOCC0/

TCLKA

P13/PO11/

TIOCD0/

TCLKB

P14/PO12/

TIOCA1

P15/PO13/

TIOCB1/

TCLKC

P16/PO14/

TIOCA2/

EDRAK2

P17/PO15/

TIOCB2/

TCLKD/

EDRAK3

P20/PO0/

TIOCA3/

(IRQ8)

P21/PO1/

TIOCB3/

(IRQ9)

P22/PO2/

TIOCC3/

(IRQ10)

P23/PO3/

TIOCD3/

(IRQ11)

P11/PO9/

TIOCB0

P12/PO10/

TIOCC0/

TCLKA

P13/PO11/

TIOCD0/

TCLKB

P14/PO12/

TIOCA1

P15/PO13/

TIOCB1/

TCLKC

When EXPE = 1:

P16/PO14/

TIOCA2/

EDRAK2

When EXPE = 0:

P16/PO14/

TIOCA2

When EXPE = 1:

P17/PO15/

TIOCB2/TCLKD/E

DRAK3

When EXPE = 0:

P17/PO15/

TIOCB2/TCLKD

P20/PO0/

TIOCA3/

(IRQ8)

P21/PO1/

TIOCB3/

(IRQ9)

P22/PO2/

TIOCC3/

(IRQ10)

P23/PO3/

TIOCD3/

(IRQ11)

Flash

Memory

Programmer Mode

NC

NC

NC

NC

NC

NC

NC

NC

NC

OE

CE

12

Pin Name

Pin

No. Mode 1 Mode 2 Mode 4 Mode 5 Mode 6 Mode 7

56 P24/PO4/

TIOCA4/

(IRQ12)

57 P25/PO5/

TIOCB4/

(IRQ13)

58 P26/PO6/

TIOCA5/

EDRAK0/

(IRQ14)

59 P27/PO7/

TIOCB5/

EDRAK1/

(IRQ15)

60 P60/TMRI0/

DREQ0/

IRQ8

61 P61/TMRI1/

DREQ1/

IRQ9

62 FWE* FWE* FWE* FWE* FWE* FWE* FWE*

63 D7 PE7/D7 PE7/D7 D7 PE7/D7 When EXPE = 1:

64 D6 PE6/D6 PE6/D6 D6 PE6/D6 When EXPE = 1:

65 D5 PE5/D5 PE5/D5 D5 PE5/D5 When EXPE = 1:

P24/PO4/

TIOCA4/

(IRQ12)

P25/PO5/

TIOCB4/

(IRQ13)

P26/PO6/

TIOCA5/

EDRAK0/

(IRQ14)

P27/PO7/

TIOCB5/

EDRAK1/

(IRQ15)

P60/TMRI0/

DREQ0/

IRQ8

P61/TMRI1/

DREQ1/

IRQ9

P24/PO4/

TIOCA4/

(IRQ12)

P25/PO5/

TIOCB4/

(IRQ13)

P26/PO6/

TIOCA5/

EDRAK0/

(IRQ14)

P27/PO7/

TIOCB5/

EDRAK1/

(IRQ15)

P60/TMRI0/

DREQ0/

IRQ8

P61/TMRI1/

DREQ1/

IRQ9

P24/PO4/

TIOCA4/

(IRQ12)

P25/PO5/

TIOCB4/

(IRQ13)

P26/PO6/

TIOCA5/

EDRAK0/

(IRQ14)

P27/PO7/

TIOCB5/

EDRAK1/

(IRQ15)

P60/TMRI0/

DREQ0/

IRQ8

P61/TMRI1/

DREQ1/

IRQ9

P24/PO4/

TIOCA4/

(IRQ12)

P25/PO5/

TIOCB4/

(IRQ13)

P26/PO6/

TIOCA5/

EDRAK0/

(IRQ14)

P27/PO7/

TIOCB5/

EDRAK1/

(IRQ15)

P60/TMRI0/

DREQ0/

IRQ8

P61/TMRI1/

DREQ1/

IRQ9

P24/PO4/

TIOCA4/

(IRQ12)

P25/PO5/

TIOCB4/

(IRQ13)

When EXPE = 1:

P26/PO6/

TIOCA5/

EDRAK0/

(IRQ14)

When EXPE = 0:

P26/PO6/

TIOCA5/(IRQ14)

When EXPE = 1:

P27/PO7/

TIOCB5/

EDRAK1/

(IRQ15)

When EXPE = 0:

P27/PO7/

TIOCB5/(IRQ15)

P60/TMRI0/

DREQ0/

IRQ8

P61/TMRI1/

DREQ1/

IRQ9

PE7/D7

When EXPE = 0:

PE7

PE6/D6

When EXPE = 0:

PE6

PE5/D5

When EXPE = 0:

PE5

Flash

Memory

Programmer Mode

WE

VSS

NC

NC

NC

NC

NC

NC

NC

13

Loading...

Loading...