AMD Am186, Am188 Service Manual

Am186ä and Am188ä Family

Instruction Set Manual

February, 1997

© 1997 Advanced Micro Devices, Inc.

Advanced Micro Devices reserves the right to make changes in its products without notice in order to improve design or performance characteristics.

This publication neither states nor implies any warranty of any kind, including but not limited to implied warrants of merchantability or fitness for a particular application. AMD assumes no responsibility for the use of any circuitry other than the circuitry in an AMD product.

The information in this publication is believed to be accurate in all respects at the time of publication, but is subject to change without notice. AMD assumes no responsibility for any errors or omissions, and disclaims responsibility for any consequences resulting from the use of the information included herein. Additionally, AMD assumes no responsibility for the functioning of undescribed features or parameters.

Trademarks

AMD, the AMD logo, and combinations thereof are trademarks of Advanced Micro Devices, Inc.

Am186, Am188, and E86 are trademarks of Advanced Micro Devices, Inc.

FusionE86 is a service mark of Advanced Micro Devices, Inc.

Product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

PREFACE

INTRODUCTION AND OVERVIEW

AMD has a strong history in x86 architecture and its E86™ family meets customer requirements of low system cost, high performance, quality vendor reputation, quick time to market, and an easy upgrade strategy.

The 16-bit Am186™ and Am188™ family of microcontrollers is based on the architecture of the original 8086 and 8088 microcontrollers, and currently includes the 80C186, 80C188, 80L186, 80L188, Am186EM, Am186EMLV, Am186ER, Am186ES, Am186ESLV, Am188EM, Am188EMLV, Am188ER, Am188ES, and Am188ESLV. Throughout this manual, the term Am186 and Am188 microcontrollers refers to any of these microcontrollers as well as future members based on the same core.

The Am186EM/ER/ES and Am188EM/ES/ER microcontrollers build on the 80C186/ 80C188 microcontroller cores and offer 386-class performance while lowering system cost. Designers can reduce the cost, size, and power consumption of embedded systems, while increasing performance and functionality. This is achieved by integrating key system peripherals onto the microcontroller. These low-cost, high-performance microcontrollers for embedded systems provide a natural migration path for 80C186/80C188 designs that need performance and cost enhancements.

PURPOSE OF THIS MANUAL

Each member of the Am186 and Am188 family of microcontrollers shares the standard 186 instruction set. This manual describes that instruction set. Details on technical features of family members can be found in the user’s manual for that specific device. Additional information is available in the form of data sheets, application notes, and other documentation provided with software products and hardware-development tools.

INTENDED AUDIENCE

This manual is intended for computer hardware and software engineers and system architects who are designing or are considering designing systems based on the Am186 and Am188 family of microcontrollers.

MANUAL OVERVIEW

The information in this manual is organized into 4 chapters and 1 appendix.

νChapter 1 provides a programming overview of the Am186 and Am188 microcontrollers, including the register set, instruction set, memory organization and address generation, I/O space, segments, data types, and addressing modes.

νChapter 2 offers an instruction set overview, detailing the format of the instructions.

νChapter 3 contains an instruction set listing, both by functional type and in alphabetical order.

νChapter 4 describes in detail each instruction in the Am186 and Am188 microcontrollers instruction set.

νAppendix A provides an instruction set summary table, as well as a guide to the instruction set by hex and binary opcode.

Introduction and Overview |

iii |

AMD DOCUMENTATION

E86 Family

ORDER NO. |

DOCUMENT TITLE |

19168 |

Am186EM and Am188EM Microcontrollers Data Sheet |

|

Hardware documentation for the Am186EM, Am186EMLV, Am188EM, and |

|

Am188EMLV microcontrollers: pin descriptions, functional descriptions, abso- |

|

lute maximum ratings, operating ranges, switching characteristics and wave- |

|

forms, connection diagrams and pinouts, and package physical dimensions. |

20732 |

Am186ER and Am188ER Microcontrollers Data Sheet |

|

Hardware documentation for the Am186ER and Am188ER microcontrollers: pin |

|

descriptions, functional descriptions, absolute maximum ratings, operating rang- |

|

es, switching characteristics and waveforms, connection diagrams and pinouts, |

|

and package physical dimensions. |

20002 |

Am186ES and Am188ES Microcontrollers Data Sheet |

|

Hardware documentation for the Am186ES, Am186ESLV, Am188ES, and |

|

Am188ESLV microcontrollers:pin descriptions,functionaldescriptions,absolute |

|

maximum ratings, operating ranges, switching characteristics and waveforms, |

|

connection diagrams and pinouts, and package physical dimensions. |

20071 |

E86 Family Support Tools Brief |

|

Lists available E86 family software and hardware development tools, as well as |

|

contact information for suppliers. |

19255 |

FusionE86SM Catalog |

|

Provides information on tools that speed an E86 family embedded product to |

|

market. Includes products from expert suppliers of embedded development so- |

|

lutions. |

21058 |

FusionE86 Development Tools Reference CD |

|

Provides a single-source multimedia tool for customer evaluation of AMD prod- |

|

ucts as well as Fusion partner tools and technologies that support the E86 family |

|

of microcontrollers and microprocessors. Technical documentation for the E86 |

|

family is included on the CD in PDF format. |

To order literature, contact the nearest AMD sales office or call 800-222-9323 (in the U.S. and Canada) or direct dial from any location 512-602-5651. Literature is also available in postscript and PDF formats on the AMD web site. To access the AMD home page, go to http:/ /www.amd.com.

iv |

Introduction and Overview |

TABLE OF CONTENTS

PREFACE |

INTRODUCTION AND OVERVIEW |

III |

|

PURPOSE OF THIS MANUAL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

III |

|

INTENDED AUDIENCE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

III |

|

MANUAL OVERVIEW . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

III |

|

AMD DOCUMENTATIONiv |

|

|

E86 Family . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

iv |

CHAPTER 1 PROGRAMMING

1.1 REGISTER SET . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1 1.1.1 Processor Status Flags Register . . . . . . . . . . . . . . . . . . . . . . . . . 1-2 1.2 INSTRUCTION SET . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-3

1.3 MEMORY ORGANIZATION AND ADDRESS GENERATION . . . . . . . . . . 1-3 1.4 I/O SPACE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5 1.5 SEGMENTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5 1.6 DATA TYPES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5 1.7 ADDRESSING MODES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-7

Register and Immediate Operands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-7

Memory Operands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

1-7 |

CHAPTER 2 INSTRUCTION SET OVERVIEW

2.1 OVERVIEW . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1 2.2 INSTRUCTION FORMAT. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1 2.2.1 Instruction Prefixes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1 2.2.2 Segment Override Prefix . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-2 2.2.3 Opcode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-2 2.2.4 Operand Address . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-2 2.2.5 Displacement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3 2.2.6 Immediate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3 2.3 NOTATION. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3

2.4 USING THIS manual . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-4 2.4.1 Mnemonics and Names . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-4 2.4.2 Forms of the Instruction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-4 2.4.3 What It Does . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-6 2.4.4 Syntax . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-6 2.4.5 Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-6 2.4.6 Operation It Performs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7 2.4.7 Flag Settings After Instruction . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7 2.4.8 Examples . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7 2.4.9 Tips . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-8 2.4.10 Related Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-8

CHAPTER 3 INSTRUCTION SET LISTING

3.1 INSTRUCTION SET BY TYPE. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

3.1.1 Address Calculation and Translation . . . . . . . . . . . . . . . . . . . . . . 3-1

3.1.2 Binary Arithmetic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-2

Table of Contents |

v |

3.1.4 Comparison . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-3 3.1.5 Control Transfer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-3 3.1.6 Data Movement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-5 3.1.7 Decimal Arithmetic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-6 3.1.8 Flag . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-7 3.1.9 Input/Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-8 3.1.10 Logical Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-8 3.1.11 Processor Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-9 3.1.12 String . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-9

3.2 INSTRUCTION SET in alphabetical order . . . . . . . . . . . . . . . . . . . . . . . . 3-11

CHAPTER 4 INSTRUCTION SET |

|

|

4.1 INSTRUCTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 4-1 |

|

AAA |

ASCII Adjust AL After Addition..................................................... |

4-2 |

AAD |

ASCII Adjust AX Before Division.................................................. |

4-4 |

AAM |

ASCII Adjust AL After Multiplication ............................................. |

4-6 |

AAS |

ASCII Adjust AL After Subtraction................................................ |

4-8 |

ADC |

Add Numbers with Carry ............................................................ |

4-10 |

ADD |

Add Numbers ............................................................................ |

4-14 |

AND |

Logical AND ............................................................................... |

4-17 |

BOUND |

Check Array Index Against Bounds ........................................... |

4-19 |

CALL |

Call Procedure ........................................................................... |

4-21 |

CBW |

Convert Byte Integer to Word..................................................... |

4-24 |

CLC |

Clear Carry Flag......................................................................... |

4-26 |

CLD |

Clear Direction Flag ................................................................... |

4-29 |

CLI |

Clear Interrupt-Enable Flag........................................................ |

4-31 |

CMC |

Complement Carry Flag ............................................................. |

4-33 |

CMP |

Compare Components ............................................................... |

4-34 |

CMPS |

Compare String Components..................................................... |

4-36 |

CWD |

Convert Word Integer to Doubleword......................................... |

4-40 |

DAA |

Decimal Adjust AL After Addition ............................................... |

4-42 |

DAS |

Decimal Adjust AL After Subtraction .......................................... |

4-45 |

DEC |

Decrement Number by One ....................................................... |

4-48 |

DIV |

Divide Unsigned Numbers ......................................................... |

4-50 |

ENTER |

Enter High-Level Procedure....................................................... |

4-53 |

ESC |

Escape ....................................................................................... |

4-56 |

HLT |

Halt............................................................................................. |

4-57 |

IDIV |

Divide Integers ........................................................................... |

4-60 |

IMUL |

Multiply Integers ......................................................................... |

4-63 |

IN |

Input Component from Port........................................................ |

4-67 |

INC |

Increment Number by One......................................................... |

4-69 |

INS |

Input String Component from Port ............................................. |

4-71 |

INT |

Generate Interrupt...................................................................... |

4-73 |

IRET |

Interrupt Return .......................................................................... |

4-76 |

JA |

Jump If Above ............................................................................ |

4-78 |

JAE |

Jump If Above or Equal.............................................................. |

4-80 |

JB |

Jump If Below............................................................................. |

4-82 |

JBE |

Jump If Below or Equal .............................................................. |

4-84 |

JC |

Jump If Carry.............................................................................. |

4-86 |

JCXZ |

Jump If CX Register Is Zero....................................................... |

4-87 |

JE |

Jump If Equal ............................................................................. |

4-89 |

vi |

Table of Contents |

JG |

Jump If Greater .......................................................................... |

4-91 |

JGE |

Jump If Greater or Equal............................................................ |

4-93 |

JL |

Jump If Less............................................................................... |

4-95 |

JLE |

Jump If Less or Equal ................................................................ |

4-97 |

JMP |

Jump Unconditionally ................................................................. |

4-99 |

JNA |

Jump If Not Above.................................................................... |

4-102 |

JNAE |

Jump If Not Above or Equal ..................................................... |

4-103 |

JNB |

Jump If Not Below .................................................................... |

4-104 |

JNBE |

Jump If Not Below or Equal...................................................... |

4-105 |

JNC |

Jump If Not Carry ..................................................................... |

4-106 |

JNE |

Jump If Not Equal..................................................................... |

4-107 |

JNG |

Jump If Not Greater.................................................................. |

4-109 |

JNGE |

Jump If Not Greater or Equal ................................................... |

4-110 |

JNL |

Jump If Not Less ...................................................................... |

4-111 |

JNLE |

Jump If Not Less or Equal........................................................ |

4-112 |

JNO |

Jump If Not Overflow................................................................ |

4-113 |

JNP |

Jump If Not Parity..................................................................... |

4-115 |

JNS |

Jump If Not Sign....................................................................... |

4-116 |

JNZ |

Jump If Not Zero ...................................................................... |

4-118 |

JO |

Jump If Overflow ...................................................................... |

4-119 |

JP |

Jump If Parity ........................................................................... |

4-121 |

JPE |

Jump If Parity Even .................................................................. |

4-122 |

JPO |

Jump If Parity Odd ................................................................... |

4-124 |

JS |

Jump If Sign ............................................................................. |

4-126 |

JZ |

Jump If Zero ............................................................................. |

4-128 |

LAHF |

Load AH with Flags .................................................................. |

4-129 |

LDS |

Load DS with Segment and Register with Offset ..................... |

4-131 |

LEA |

Load Effective Address ........................................................... |

4-133 |

LEAVE |

Leave High-Level Procedure.................................................... |

4-135 |

LES |

Load ES with Segment and Register with Offset .......................... |

4-138 |

LOCK |

Lock the Bus ............................................................................ |

4-140 |

LODS |

Load String Component ........................................................... |

4-141 |

LOOP |

Loop While CX Register Is Not Zero ........................................ |

4-146 |

LOOPE |

Loop If Equal ............................................................................ |

4-148 |

LOOPNE |

Loop If Not Equal ..................................................................... |

4-150 |

LOOPZ |

Loop If Zero.............................................................................. |

4-152 |

MOV |

Move Component..................................................................... |

4-153 |

MOVS |

Move String Component .......................................................... |

4-156 |

MUL |

Multiply Unsigned Numbers ..................................................... |

4-160 |

NEG |

Two’s Complement Negation ................................................... |

4-163 |

NOP |

No Operation............................................................................ |

4-165 |

NOT |

One’s Complement Negation ................................................... |

4-167 |

OR |

Logical Inclusive OR ................................................................ |

4-169 |

OUT |

Output Component to Port ....................................................... |

4-171 |

OUTS |

Output String Component to Port............................................. |

4-173 |

POP |

Pop Component from Stack ..................................................... |

4-175 |

POPA |

Pop All 16-Bit General Registers from Stack................................ |

4-178 |

POPF |

Pop Flags from Stack............................................................... |

4-180 |

PUSH |

Push Component onto Stack ................................................... |

4-181 |

|

|

|

|

Table of Contents |

vii |

PUSHA |

Push All 16-Bit General Registers onto Stack.......................... |

4-184 |

PUSHF |

Push Flags onto Stack ............................................................. |

4-186 |

RCL |

Rotate through Carry Left......................................................... |

4-187 |

RCR |

Rotate through Carry Right ...................................................... |

4-189 |

REP |

Repeat...................................................................................... |

4-191 |

REPE |

Repeat While Equal ................................................................. |

4-193 |

REPNE |

Repeat While Not Equal........................................................... |

4-197 |

REPZ |

Repeat While Zero ................................................................... |

4-201 |

RET |

Return from Procedure............................................................. |

4-202 |

ROL |

Rotate Left................................................................................ |

4-205 |

ROR |

Rotate Right ............................................................................. |

4-207 |

SAHF |

Store AH in Flags ..................................................................... |

4-209 |

SAL |

Shift Arithmetic Left .................................................................. |

4-211 |

SAR |

Shift Arithmetic Right................................................................ |

4-214 |

SBB |

Subtract Numbers with Borrow ................................................ |

4-216 |

SCAS |

Scan String for Component...................................................... |

4-219 |

SHL |

Shift Left ................................................................................... |

4-224 |

SHR |

Shift Right................................................................................. |

4-225 |

STC |

Set Carry Flag .......................................................................... |

4-228 |

STD |

Set Direction Flag..................................................................... |

4-231 |

STI |

Set Interrupt-Enable Flag ......................................................... |

4-235 |

STOS |

Store String Component........................................................... |

4-237 |

SUB |

Subtract Numbers .................................................................... |

4-240 |

TEST |

Logical Compare ...................................................................... |

4-243 |

WAIT |

Wait for Coprocessor ............................................................... |

4-245 |

XCHG |

Exchange Components............................................................ |

4-246 |

XLAT |

Translate Table Index to Component....................................... |

4-248 |

XOR |

Logical Exclusive OR ............................................................... |

4-251 |

APPENDIX A INSTRUCTION SET SUMMARY

INDEX

viii |

Table of Contents |

LIST OF FIGURES

Figure 1-1 |

Register Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

1-2 |

Figure 1-2 Processor Status Flags Register (FLAGS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

1-2 |

|

Figure 1-3 |

Physical-Address Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

1-4 |

Figure 1-4 Memory and i/O Space . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

1-4 |

|

Figure 1-5 Supported Data Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

1-6 |

|

Figure 2-1 |

Instruction Mnemonic and Name Sample . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2-4 |

Figure 2-2 |

Instruction Forms Table Sample . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2-4 |

LIST OF TABLES

Table 1-1 Segment Register Selection Rules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 1-5 |

|

Table 1-2 Memory Addressing Mode Examples . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 1-7 |

|

Table 2-1 |

mod field . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 2-2 |

Table 2-2 |

aux field . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 2-3 |

Table 2-3 |

r/m field . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 2-3 |

Table 3-4 |

Instruction Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

3-11 |

Table of Contents |

ix |

x |

Table of Contents |

CHAPTER

1 PROGRAMMING

All members of the Am186 and Am188 family of microcontrollers contain the same basic set of registers, instructions, and addressing modes, and are compatible with the original industry-standard 186/188 parts.

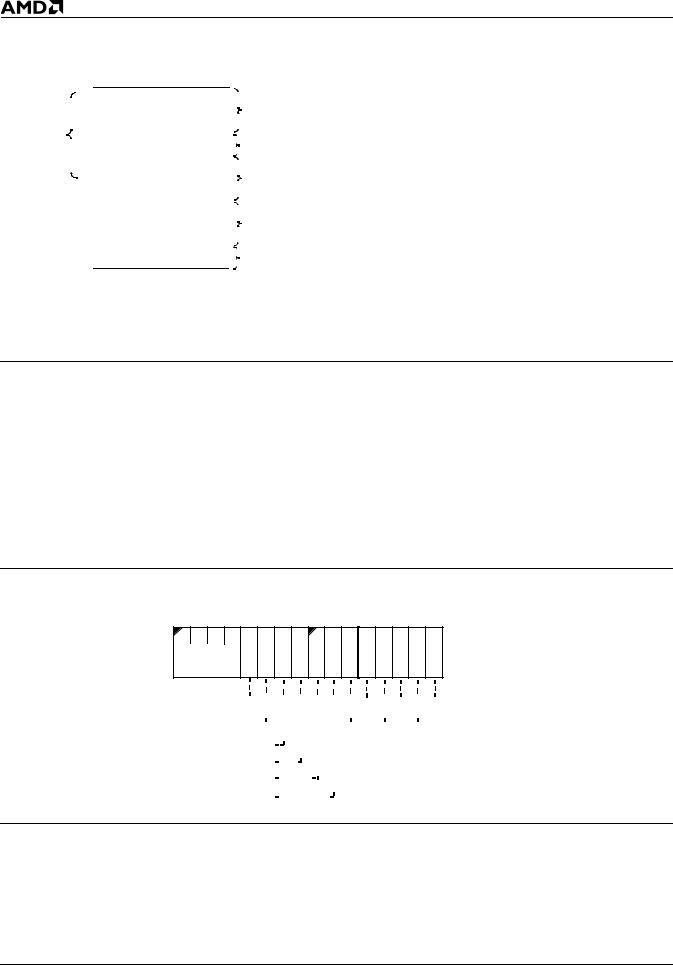

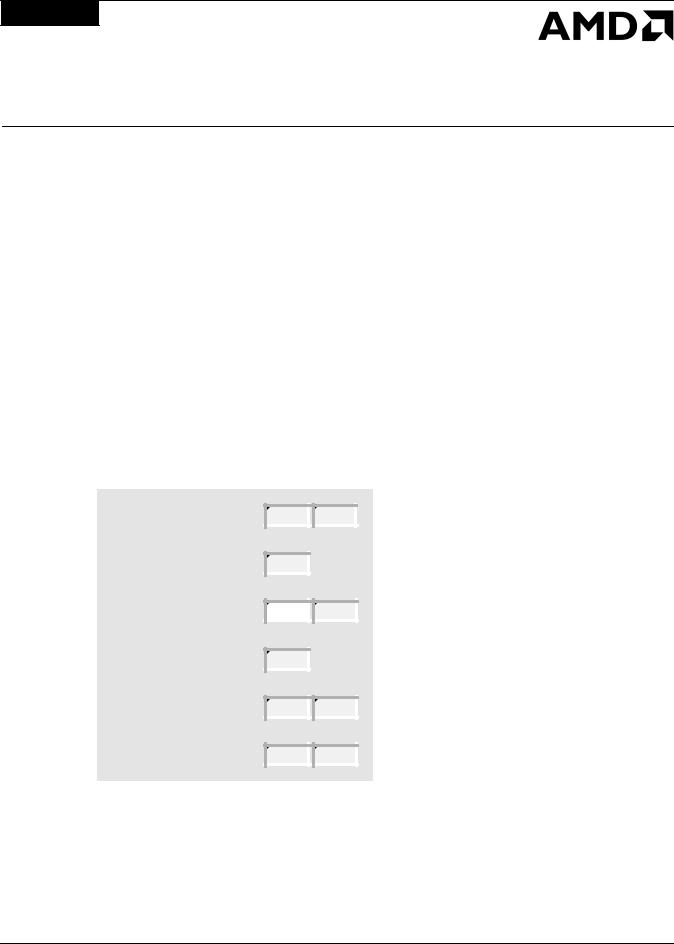

1.1REGISTER SET

The base architecture for Am186 and Am188 microcontrollers has 14 registers (see Figure 1-1), which are controlled by the instructions detailed in this manual. These registers are grouped into the following categories.

νGeneral Registers—Eight 16-bit general purpose registers can be used for arithmetic and logical operands. Four of these (AX, BX, CX, and DX) can be used as 16-bit registers or split into pairs of separate 8-bit registers (AH, AL, BH, BL, CH, CL, DH, and DL). The Destination Index (DI) and Source Index (SI) general-purpose registers are used for data movement and string instructions. The Base Pointer (BP) and Stack Pointer (SP) general-purpose registers are used for the stack segment and point to the bottom and top of the stack, respectively.

–Base and Index Registers—Four of the general-purpose registers (BP, BX, DI, and SI) can also be used to determine offset addresses of operands in memory. These registers can contain base addresses or indexes to particular locations within a segment. The addressing mode selects the specific registers for operand and address calculations.

–Stack Pointer Register—All stack operations (POP, POPA, POPF, PUSH, PUSHA, PUSHF) utilize the stack pointer. The Stack Pointer (SP) register is always offset from the Stack Segment (SS) register, and no segment override is allowed.

νSegment Registers—Four 16-bit special-purpose registers (CS, DS, ES, and SS) select, at any given time, the segments of memory that are immediately addressable for code (CS), data (DS and ES), and stack (SS) memory.

νStatus and Control Registers—Two 16-bit special-purpose registers record or alter certain aspects of the processor state—the Instruction Pointer (IP) register contains the offset address of the next sequential instruction to be executed and the Processor Status Flags (FLAGS) register contains status and control flag bits (see Figure 1-2).

Note that all members of the Am186 and Am188 family of microcontrollers have additional peripheral registers, which are external to the processor. These peripheral registers are not directly accessible by the instruction set. However, because the processor treats these peripheral registers like memory, instructions that have operands that access memory can also access peripheral registers. The above processor registers, as well as the additional peripheral registers, are described in the user’s manual for each specific part.

Programming |

1-1 |

Figure 1-1 |

|

Register Set |

|

|

|

|

|

|

|

||||

16-Bit |

|

|

|

|

|

|

Special |

16-Bit |

|

|

|||

Register |

|

7 |

0 7 |

0 |

|

Register |

Register |

|

|

||||

Name |

|

|

Functions |

Name 15 |

0 |

|

|||||||

Byte |

|

|

AX |

|

AH |

|

AL |

|

Multiply/Divide |

CS |

|

|

Code Segment |

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

||||||||

Addressable |

|

DX |

|

DH |

|

DL |

|

I/O Instructions |

DS |

|

|

||

|

|

|

|

|

|

|

|||||||

(8-Bit |

|

|

CX |

|

|

|

|

|

Loop/Shift/Repeat/Count SS |

|

|

Data Segment |

|

Register |

|

|

|

CH |

|

CL |

|

|

|

Stack Segment |

|||

|

|

|

|

||||||||||

Names |

|

|

BX |

|

BH |

|

BL |

|

Base Registers |

ES |

|

|

|

|

|

|

|

|

|

|

|

||||||

Shown) |

|

|

|

|

|

|

Extra Segment |

||||||

BP |

|

base pointer |

|

|

|

|

|||||||

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

Segment Registers |

||||||

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

SI |

|

source index |

|

Index Registers |

||||||

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|||||

|

|

|

DI |

|

destination index |

|

15 |

0 |

|

||||

|

|

|

|

|

|

|

|||||||

|

|

|

SP |

|

|

|

|

|

Stack Pointer |

FLAGS |

|

|

Processor Status Flags |

|

|

|

|

|

|

|

|

||||||

|

|

|

|

15 |

General |

0 |

|

|

IP |

|

|

Instruction Pointer |

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|||

Registers

Status and Control

Registers

1.1.1Processor Status Flags Register

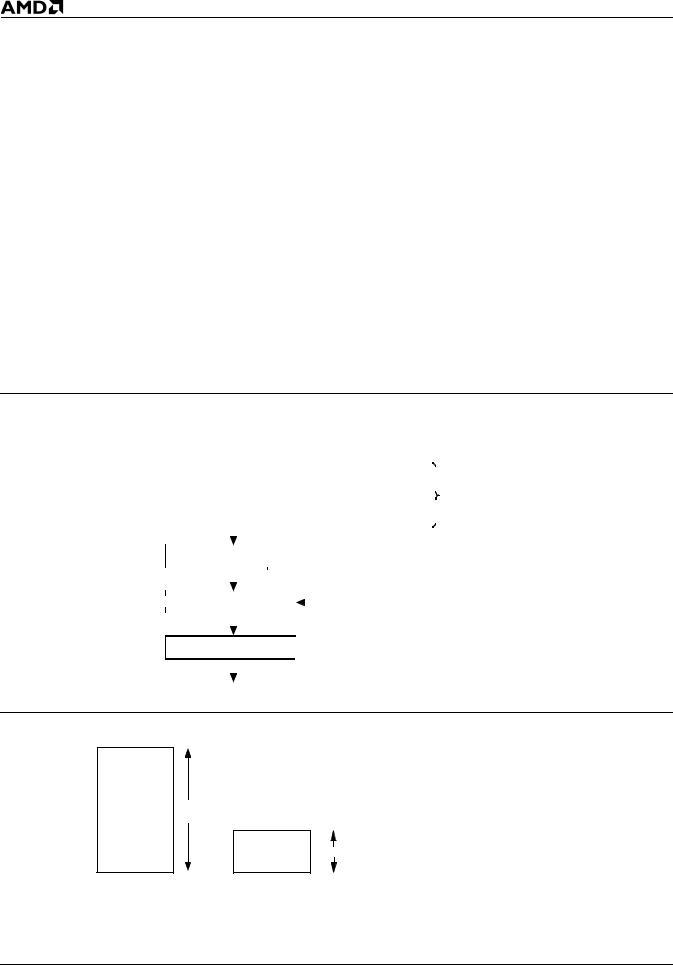

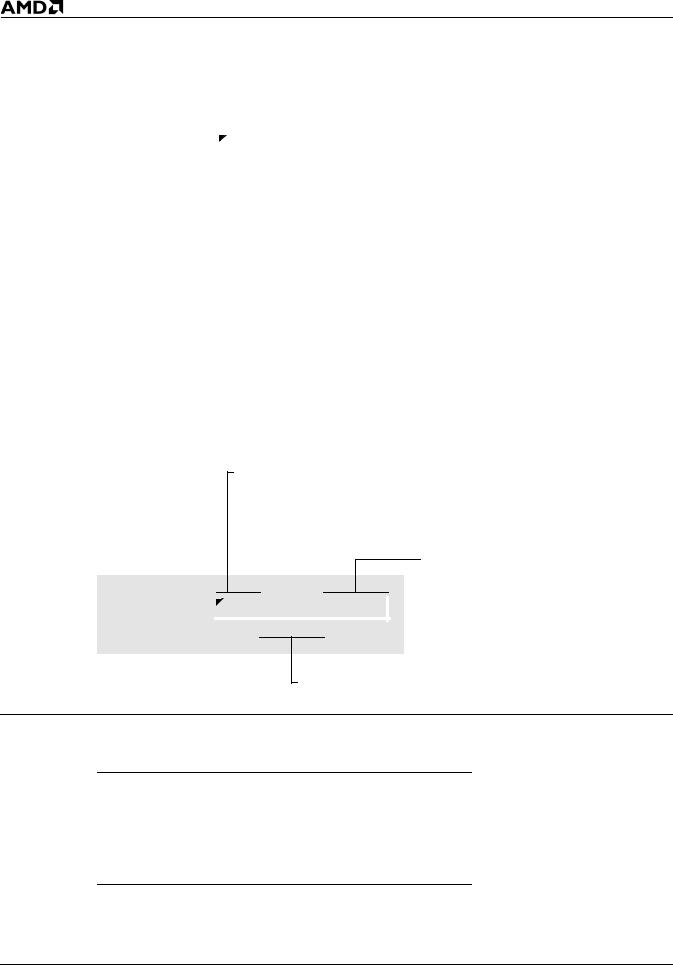

The 16-bit processor status flags register (see Figure 1-2) records specific characteristics of the result of logical and arithmetic instructions (bits 0, 2, 4, 6, 7, and 11) and controls the operation of the microcontroller within a given operating mode (bits 8, 9, and 10).

After an instruction is executed, the value of a flag may be set (to 1), cleared/reset (to 0), unchanged, or undefined. The term undefined means that the flag value prior to the execution of the instruction is not preserved, and the value of the flag after the instruction is executed cannot be predicted. The documentation for each instruction indicates how each flag bit is affected by that instruction.

Figure 1-2 Processor Status Flags Register (FLAGS)

15 |

7 |

0 |

Reserved

OF |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AF |

|

PF |

|

CF |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

||||||||||||||||||||||||

DF |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Res Res Res |

||||||||

IF |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

TF |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

SF |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

ZF |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

Bits 15–12 —Reserved.

Bit 11: Overflow Flag (OF)—Set if the signed result cannot be expressed within the number of bits in the destination operand, cleared otherwise.

1-2 |

Programming |

Bit 10: Direction Flag (DF)—Causes string instructions to auto decrement the appropriate index registers when set. Clearing DF causes auto-increment. See the CLD and STD instructions, respectively, for how to clear and set the Direction Flag.

Bit 9: Interrupt-Enable Flag (IF)—When set, enables maskable interrupts to cause the CPU to transfer control to a location specified by an interrupt vector. See the CLI and STI instructions, respectively, for how to clear and set the Interrupt-Enable Flag.

Bit 8: Trace Flag (TF)—When set, a trace interrupt occurs after instructions execute. TF is cleared by the trace interrupt after the processor status flags are pushed onto the stack. The trace service routine can continue tracing by popping the flags back with an IRET instruction.

Bit 7: Sign Flag (SF)—Set equal to high-order bit of result (set to 0 if 0 or positive, 1 if negative).

Bit 6: Zero Flag (ZF)—Set if result is 0; cleared otherwise.

Bit 5: Reserved

Bit 4: Auxiliary Carry (AF)—Set on carry from or borrow to the low-order 4 bits of the AL general-purpose register; cleared otherwise.

Bit 3: Reserved

Bit 2: Parity Flag (PF)—Set if low-order 8 bits of result contain an even number of 1 bits; cleared otherwise.

Bit 1: Reserved

Bit 0: Carry Flag (CF)—Set on high-order bit carry or borrow; cleared otherwise. See the CLC, CMC, and STC instructions, respectively, for how to clear, toggle, and set the Carry Flag. You can use CF to indicate the outcome of a procedure, such as when searching a string for a character. For instance, if the character is found, you can use STC to set CF to 1; if the character is not found, you can use CLC to clear CF to 0. Then, subsequent instructions that do not affect CF can use its value to determine the appropriate course of action.

1.2INSTRUCTION SET

Each member of the Am186 and Am188 family of microcontrollers shares the standard 186 instruction set. An instruction can reference from zero to several operands. An operand can reside in a register, in the instruction itself, or in memory. Specific operand addressing modes are discussed on page 1-7.

Chapter 2 provides an overview of the instruction set, describing the format of the instructions. Chapter 3 lists all the instructions for the Am186 and Am188 microcontrollers in both functional and alphabetical order. Chapter 4 details each instruction.

1.3MEMORY ORGANIZATION AND ADDRESS GENERATION

The Am186 and Am188 microcontrollers organize memory in sets of segments. Memory

is addressed using a two-component address that consists of a 16-bit segment value and a 16-bit offset. Each segment is a linear contiguous sequence of 64K (216) 8-bit bytes of memory in the processor’s address space. The offset is the number of bytes from the beginning of the segment (the segment address) to the data or instruction which is being accessed.

The processor forms the physical address of the target location by taking the segment address, shifting it to the left 4 bits (multiplying by 16), and adding this to the 16-bit offset.

Programming |

1-3 |

The result is a 20-bit address of the target data or instruction. Thisallowsfora 1-Mbyte physical address size.

For example, if the segment register is loaded with 12A4h and the offset is 0022h, the resultant address is 12A62h (see Figure 1-3). To find the result:

1.The segment register contains 12A4h.

2.The segment register is shifted 4 places and is now 12A40h.

3.The offset is 0022h.

4.The shifted segment address (12A40h) is added to the offset (00022h) to get 12A62h.

5.This address is placed on the address bus pins of the controller.

All instructions that address operands in memory must specify (implicitly or explicitly) a 16bit segment value and a 16-bit offset value. The 16-bit segment values are contained in one of four internal segment registers (CS, DS, ES, and SS). See "Addressing Modes” on page 1-7 for more information on calculating the segment and offset values. See "Segments" on page 1-5 for more information on the CS, DS, ES, and SS registers.

In addition to memory space, all Am186 and Am188 microcontrollers provide 64K of I/O space (see Figure 1-4). The I/O space is described on page 1-5.

Figure 1-3 Physical-Address Generation

Shift Left

4 Bits

|

|

|

|

|

|

|

|

1 |

|

|

2 |

A |

4 |

Segment |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

Base |

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

15 |

|

|

|

|

0 |

|

Logical Address |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

|

0 |

2 |

2 |

Offset |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

15 |

|

|

|

|

0 |

|

|

|

|

1 |

|

2 |

A |

4 |

|

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

19 |

|

|

|

|

0 |

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

0 |

0 |

2 |

|

2 |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

15 |

|

|

0 |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

2 |

A |

6 |

|

2 |

|

|

|

Physical Address |

|

|

|||||

19 |

|

|

|

|

0 |

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

To Memory |

|

|

|

|

|

|

|

|

|

|

|

||

Figure 1-4 Memory and i/O Space

Memory

Space 1M

I/O

Space 64K

1-4 |

Programming |

1.4I/O SPACE

The I/O space consists of 64K 8-bit or 32K 16-bit ports. The IN and OUT instructions address the I/O space with either an 8-bit port address specified in the instruction, or a 16-bit port address in the DX register. 8-bit port addresses are zero-extended so that A15–A8 are Low. I/O port addresses 00F8h through 00FFh are reserved. The Am186 and Am188 microcontrollers provide specific instructions for addressing I/O space.

1.5SEGMENTS

The Am186 and Am188 microcontrollers use four segment registers:

1.Data Segment (DS): The processor assumes that all accesses to the program’s variables are from the 64K space pointed to by the DS register. The data segment holds data, operands, etc.

2.Code Segment (CS): This 64K space is the default location for all instructions. All code must be executed from the code segment.

3.Stack Segment (SS): The processor uses the SS register to perform operations that involve the stack, such as pushes and pops. The stack segment is used for temporary space.

4.Extra Segment (ES): Usually this segment is used for large string operations and for large data structures. Certain string instructions assume the extra segment as the segment portion of the address. The extra segment is also used (by using segment override) as a spare data segment.

When a segment register is not specified for a data movement instruction, it’s assumed to be a data segment. An instruction prefix can be used to override the segment register (see "Segment Override Prefix" on page 2-2).For speed and compact instruction encoding, the segment register used for physical-address generation is implied by the addressing mode used (see Table 1-1).

Table 1-1 |

Segment Register Selection Rules |

||

Memory Reference Needed |

Segment Register Used |

Implicit Segment Selection Rule |

|

|

|

|

|

Local Data |

|

Data (DS) |

All data references |

|

|

|

|

Instructions |

|

Code (CS) |

Instructions (including immediate data) |

|

|

|

|

Stack |

|

Stack (SS) |

All stack pushes and pops |

|

|

|

Any memory references that use the BP register |

|

|

|

|

External Data (Global) |

Extra (ES) |

All string instruction references that use the DI register as an index |

|

|

|

|

|

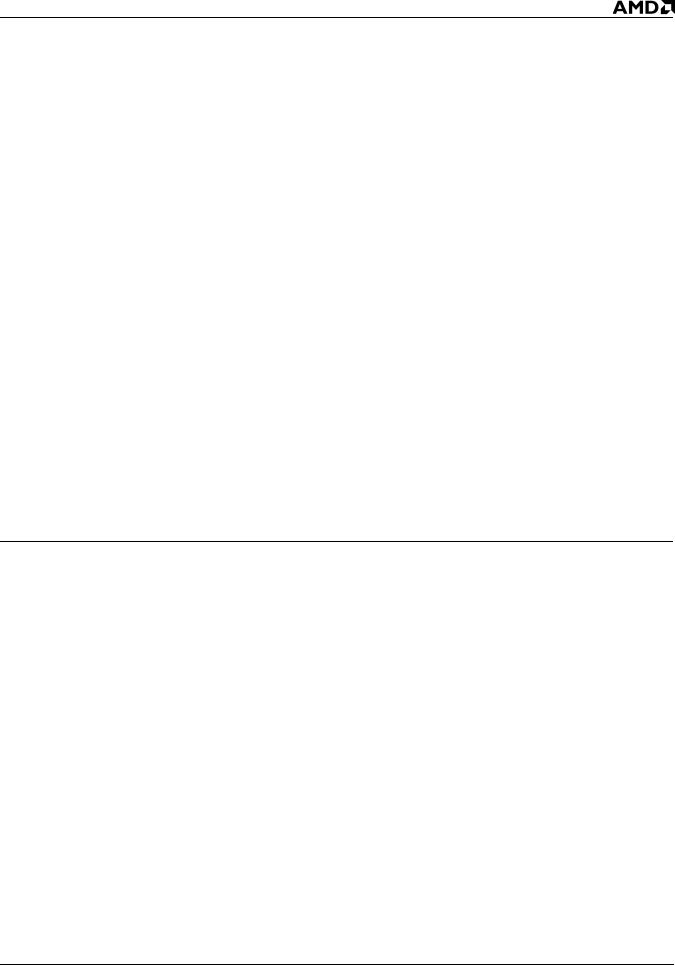

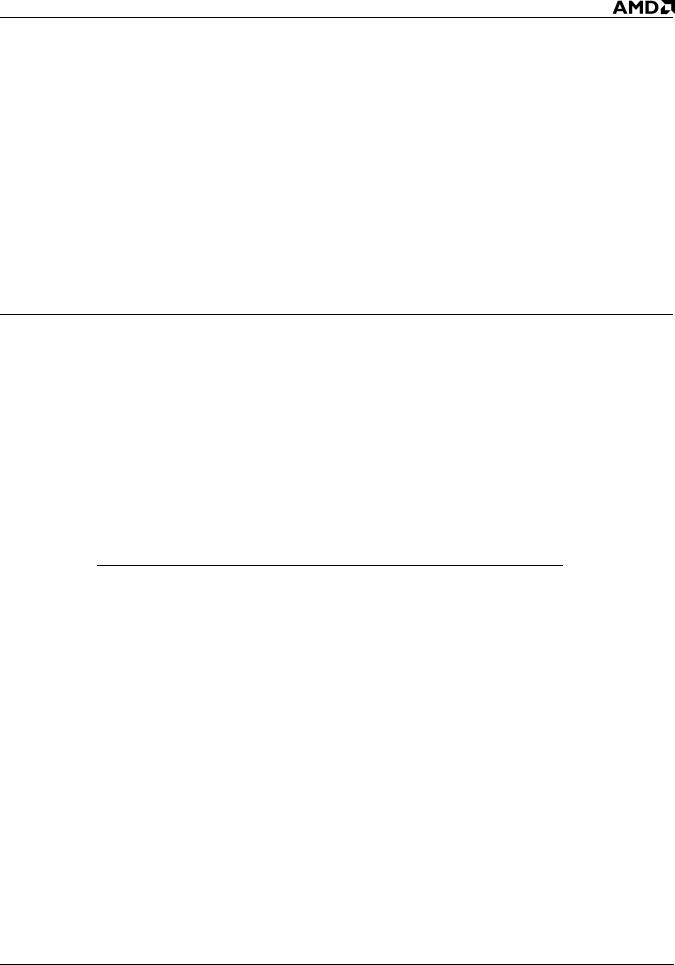

1.6DATA TYPES

The Am186 and Am188 microcontrollers directly support the following data types:

νInteger—A signed binary numeric value contained in an 8-bit byte or a 16-bit word. All operations assume a two’s complement representation.

νOrdinal—An unsigned binary numeric value contained in an 8-bit byte or a 16-bit word.

νDouble Word—A signed binary numeric value contained in two sequential 16-bit addresses, or in a DX::AX register pair.

νQuad Word—A signed binary numeric value contained in four sequential 16-bit addresses.

νBCD—An unpacked byte representation of the decimal digits 0–9.

Programming |

1-5 |

νASCII—A byte representation of alphanumeric and control characters using the ASCII standard of character representation.

νPacked BCD—A packed byte representation of two decimal digits (0–9). One digit is stored in each nibble (4 bits) of the byte.

νString—A contiguous sequence of bytes or words. A string can contain from 1 byte up to 64 Kbyte.

νPointer—A 16-bit or 32-bit quantity, composed of a 16-bit offset component or a 16-bit segment base component plus a 16-bit offset component.

In general, individual data elements must fit within defined segment limits. Figure 1-5 graphically represents the data types supported by the Am186 and Am188 microcontrollers.

Figure 1-5 Supported Data Types

Signed |

7 |

|

|

|

|

|

|

|

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

Byte |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

Sign Bit |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

Magnitude |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

Unsigned |

7 |

|

|

|

|

|

|

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

Byte |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

MSB |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

Magnitude |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

Signed |

1514 |

+1 |

8 7 |

0 |

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

Word |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

Sign Bit |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

MSB |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

Magnitude |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

Signed |

|

|

|

|

|

|

|

|

+3 |

|

|

|

|

|

+2 |

|

|

|

|

|

+1 |

|

|

|

|

0 |

|

|

|

|

|||||||||||

Double |

31 |

|

|

|

|

|

|

|

|

|

1615 |

|

|

|

|

0 |

|||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

Word |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

Sign Bit |

|

|

|

|

|

|

|

|

MSB |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Magnitude |

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

Signed |

+7 |

|

|

+6 |

|

+5 |

|

|

+4 |

|

|

+3 |

|

+2 |

+1 |

+0 |

|

||||||||||||||||||||||||

Quad |

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||

63 |

|

|

|

|

|

|

48 47 |

|

|

|

32 31 |

|

|

|

16 15 |

|

|

0 |

|||||||||||||||||||||||

Word |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Sign Bit |

|

|

|

|

|

|

|

|

|

MSB |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Magnitude |

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

Unsigned |

15 |

|

|

|

+1 |

|

|

|

|

|

0 |

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

Word |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

MSB |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

Magnitude |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

Binary 7 |

|

|

+N |

0 |

|

|

7 |

+1 |

|

|

0 7 |

|

0 |

|

|

0 |

|

|

||||||||||||||||||

Coded |

|

|

|

|

|

|

|

|

|

|

|

|

. . . |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

Decimal |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

BCD |

|

|

|

|

|

|

|

|

|

|

BCD |

|

|

|

|

BCD |

|

|

|

|||||||||||||

(BCD) |

Digit N |

|

|

|

|

|

|

Digit 1 Digit 0 |

|

|

|

|||||||||||||||||||||||||

7 |

|

|

+N |

0 |

|

|

7 |

+1 |

|

|

0 7 |

|

0 |

|

|

0 |

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

ASCII |

|

|

|

|

|

|

|

|

|

|

. . . |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

ASCII |

|

|

|

|

|

|

|

ASCII |

|

|

|

|

|

ASCII |

|||||||||||||||||

CharacterN |

|

|

|

Character1 Character0 |

||||||||||||||||||||||||||||||||

7 |

|

|

+N |

0 |

|

|

7 |

+1 |

|

|

0 7 |

|

0 |

|

|

0 |

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

Packed |

|

|

|

|

|

|

|

|

|

|

. . . |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

BCD |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

Most |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Least |

||||||||||||||

Significant Digit |

|

|

Significant Digit |

|||||||||||||||||||||||||||||||||

7 |

|

|

+N |

0 |

|

|

7 |

+1 |

|

0 7 |

|

0 |

|

|

0 |

|

|

|||||||||||||||||||

String |

|

|

|

|

|

|

|

|

|

|

. . . |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

Byte/WordN |

|

|

Byte/Word1 Byte/Word0 |

|||||||||||||||||||||||||||||||||

|

|

|

|

+3 |

|

|

|

|

|

+2 |

|

|

|

+1 |

|

|

|

|

|

0 |

|

|

|

|

|

|||||||||||

Pointer |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

Segment Base |

|

|

|

|

|

|

Offset |

|

|

|

||||||||||||||||||||||

1-6 |

Programming |

1.7ADDRESSING MODES

The Am186 and Am188 microcontrollers use eight categories of addressing modes to specify operands. Two addressing modes are provided for instructions that operate on register or immediate operands; six modes are provided to specify the location of an operand in a memory segment.

Register and Immediate Operands

1.Register Operand Mode—The operand is located in one of the 8- or 16-bit registers.

2.Immediate Operand Mode—The operand is included in the instruction.

Memory Operands

A memory-operand address consists of two 16-bit components: a segment value and an offset. The segment value is supplied by a 16-bit segment register either implicitly chosen by the addressing mode (described below) or explicitly chosen by a segment override prefix (see "Segment Override Prefix" on page 2-2). The offset, also called the effective address, is calculated by summing any combination of the following three address elements:

νDisplacement—an 8-bit or 16-bit immediate value contained in the instruction

νBase—contents of either the BX or BP base registers

νIndex—contents of either the SI or DI index registers

Any carry from the 16-bit addition is ignored. Eight-bit displacements are sign-extended to 16-bit values.

Combinations of the above three address elements define the following six memory addressing modes (see Table 1-2 for examples).

1.Direct Mode—The operand offset is contained in the instruction as an 8- or 16-bit displacement element.

2.Register Indirect Mode—The operand offset is in one of the BP, BX, DI, or SI registers.

3.Based Mode—The operand offset is the sum of an 8- or 16-bit displacement and the contents of a base register (BP or BX).

4.Indexed Mode—The operand offset is the sum of an 8- or 16-bit displacement and the contents of an index register (DI or SI).

5.Based Indexed Mode—The operand offset is the sum of the contents of a base register (BP or BX) and an index register (DI or SI).

6.Based Indexed Mode with Displacement—The operand offset is the sum of a base register’s contents, an index register’s contents, and an 8-bit or 16-bit displacement.

Table 1-2 |

Memory Addressing Mode Examples |

|

|

|

|

|

Addressing Mode |

Example |

|

|

|

|

Direct |

mov ax, ds:4 |

|

|

|

|

Register Indirect |

mov ax, [si] |

|

|

|

|

Based |

mov ax, [bx]4 |

|

|

|

|

Indexed |

mov ax, [si]4 |

|

|

|

|

Based Indexed |

mov ax, [si][bx] |

|

|

|

|

Based Indexed with Displacement |

mov ax, [si][bx]4 |

|

|

|

Programming |

1-7 |

1-8 |

Programming |

CHAPTER

2 INSTRUCTION SET OVERVIEW

2.1OVERVIEW