UTRON UT62L1024SC-70LLE, UT62L1024SC-70LE, UT62L1024SC-55LLE, UT62L1024SC-55LE, UT62L1024SC-35LLE Datasheet

...

UTRON |

UT62L1024(E) |

Rev. 1.1 |

128K X 8 BIT LOW POWER CMOS SRAM |

FEATURES

Access time : 35/55/70ns (max.) Low power consumption : Operating : 40/35/30 mA (typical) Standby : 1.0 A (typical) L-version

0.5 A (typical) LL-version Power supply range : 2.7V to 3.6V All inputs and outputs TTL compatible Fully static operation

Three state outputs

Data retention voltage : 2V (min.) Extended Temperature : -20 ~80 Package : 32-pin 600 mil PDIP

32-pin 450 mil SOP

32-pin 8x20mm TSOP-1

32-pin 8x13.4mm STSOP

GENERAL DESCRIPTION

The UT62L1024(E) is a 1,048,576-bit low power CMOS static random access memory organized as 131,072 words by 8 bits. It is fabricated using high performance, high reliability CMOS technology.

The UT62L1024(E) is designed for low power application. It is particularly well suited for battery back-up nonvolatile memory application.

The UT62L1024(E) operates from a single 2.7V ~ 3.6V power supply and all inputs and outputs are fully TTL compatible.

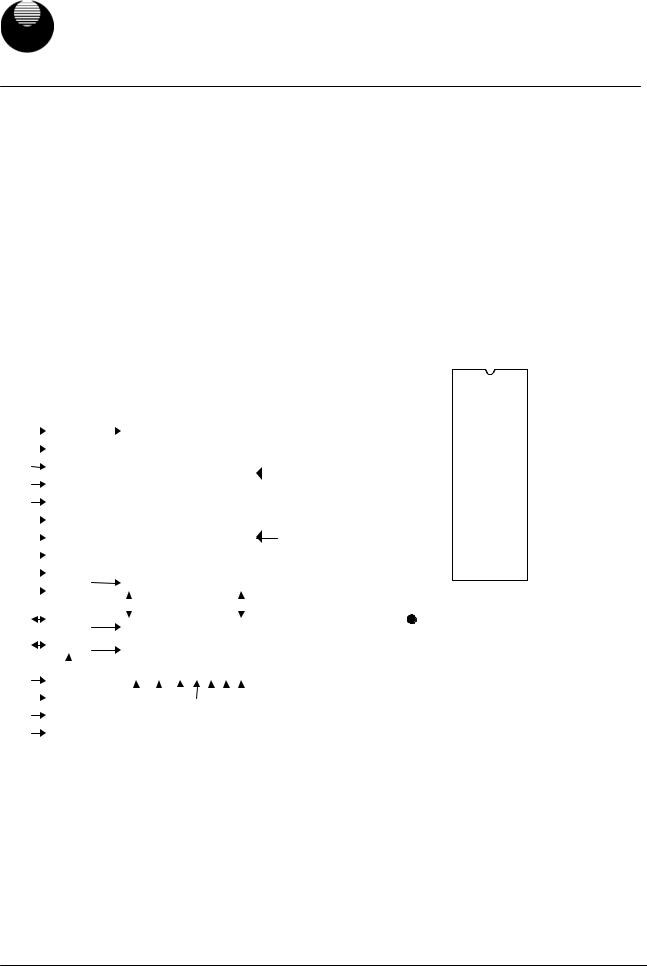

PIN CONFIGURATION

FUNCTIONAL BLOCK DIAGRAM

|

A16 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

A15 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

A13 |

|

|

|

|

|

. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VCC |

|||||||

|

A14 |

|

|

|

|

|

|

|

|

|

|

MEMORY ARRAY |

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

A12 |

|

|

|

|

|

. |

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

ROW |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

A7 |

|

|

|

|

|

|

|

|

1024 ROWS × 1024 COLUMNS |

|

|

||||||||||||||||||

|

|

|

|

|

|

DECODER |

|

|

|

|

|

VSS |

||||||||||||||||||

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

|

A6 |

|

|

|

|

|

. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

A5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

A4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

A8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

. . . |

|

|

|

|

|

|

|

|

|||||||||

|

I/O1 |

|

|

|

|

|

|

. |

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

. |

|

I/O |

|

|

|

|

|

|

COLUMN I/O |

|

|

|

|||||||||||||||||

. |

|

|

|

|

|

|

|

CONTROL |

|

. |

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

I/O8 |

|

|

|

|

|

|

|

|

|

|

COLUMN DECODER |

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CE 1 |

|

|

|

|

|

|

LOGIC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

CE2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

A10 A11 |

A9 A3 A2 A1 A0 |

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

CONTROL |

|

|

|

|

|||||||||||||||

|

|

WE |

|

|

|

|

|

|

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

OE |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PIN |

DESCRIPTION |

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|||||||||||||||||||||||

|

SYMBOL |

|

DESCRIPTION |

|

||||||||||||||||||||||||||

|

|

A0 - A16 |

|

Address Inputs |

|

|||||||||||||||||||||||||

|

|

I/O1 - I/O8 |

|

Data Inputs/Outputs |

|

|||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

,CE2 |

|

Chip enable 1,2 Inputs |

|

||||||||||||||||||

|

|

|

CE1 |

|

||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Write Enable Input |

|

|||||||||||||||

|

|

|

WE |

|

|

|

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Output Enable Input |

|

|||||||||||||||

|

|

|

OE |

|

|

|

|

|

|

|||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

VCC |

|

|

|

|

|

|

Power Supply |

|

||||||||||||||||||||

|

|

VSS |

|

|

|

|

|

|

Ground |

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

NC |

|

|

|

|

|

|

No Connection |

|

||||||||||||||||||||

NC |

|

1 |

32 |

|

Vcc |

A16 |

|

31 |

|

A15 |

|

|

2 |

|

|||

|

|

|

CE2 |

||

|

|

|

|

||

A14 |

|

3 |

30 |

|

|

|

|

|

|

|

A12 |

|

4 |

UT62L1024(E) |

29 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

WE |

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

A7 |

|

5 |

|

28 |

|

A13 |

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

A8 |

|

|

|

|

|||

|

|

|

|

|

A6 |

|

6 |

|

27 |

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

A9 |

|

|

|

|

|||

|

|

|

|

|

A5 |

|

7 |

|

26 |

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

A11 |

|

|

|

|

||||

|

|

|

|

|

A4 |

|

8 |

|

25 |

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A3 |

|

9 |

|

24 |

|

|

|

OE |

|

|

|

|

|

|

|

|

|

|

|

A2 |

|

|

23 |

|

A10 |

|

|

|

|

|||||

|

|

|

|

|

|

10 |

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A1 |

|

11 |

|

22 |

|

|

CE1 |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

I/O8 |

|

|

|

|

||||

|

|

|

|

|

A0 |

|

12 |

|

21 |

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

I/O1 |

|

13 |

|

20 |

|

|

I/O7 |

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

I/O6 |

|

|

|

|

||||

|

|

|

|

|

I/O2 |

|

14 |

|

19 |

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

I/O3 |

|

15 |

|

18 |

|

|

I/O5 |

|

|

|

|

|||

|

|

|

|

|

Vss |

|

|

17 |

|

|

I/O4 |

|

|

|

|

||||

|

|

|

|

|

|

16 |

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

PDIP / SOP |

|

|

|

|

|

|

|

|

|

|||

|

A11 |

|

1 |

|

|

|

|

|

|

32 |

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

OE |

|

||||||||

|

|

|

|

|

|

|

|

||||||||||||

|

A9 |

|

2 |

|

|

|

|

|

|

31 |

|

A10 |

|||||||

|

|

|

|

|

|

|

|

||||||||||||

|

A8 |

|

3 |

|

|

|

|

|

|

30 |

|

|

CE1 |

||||||

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

||||||||||||

|

A13 |

|

4 |

|

|

|

|

|

|

29 |

|

I/O8 |

|||||||

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

||||||||||||

|

WE |

|

|

5 |

|

|

|

|

|

|

28 |

|

I/O7 |

||||||

|

|

|

|

|

|

|

|

||||||||||||

CE2 |

|

6 |

|

|

|

|

|

|

27 |

|

|

I/O6 |

|||||||

|

|

|

|

|

|

|

|

||||||||||||

|

A15 |

|

7 |

UT62L1024(E) |

26 |

|

|

I/O5 |

|||||||||||

|

|

||||||||||||||||||

|

Vcc |

|

8 |

25 |

|

|

I/O4 |

||||||||||||

|

|

||||||||||||||||||

|

|

||||||||||||||||||

|

NC |

|

9 |

|

|

|

|

|

|

24 |

|

|

Vss |

||||||

|

|

|

|

|

|

|

|

||||||||||||

|

A16 |

|

10 |

|

|

|

|

|

|

23 |

|

|

I/O3 |

||||||

|

|

|

|

|

|

|

|

||||||||||||

|

A14 |

|

11 |

|

|

|

|

|

|

22 |

|

|

I/O2 |

||||||

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

||||||||||||

|

A12 |

|

12 |

|

|

|

|

|

|

21 |

|

|

I/O1 |

||||||

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

||||||||||||

|

A7 |

|

13 |

|

|

|

|

|

|

20 |

|

|

A0 |

||||||

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

||||||||||||

|

A6 |

|

14 |

|

|

|

|

|

|

19 |

|

|

A1 |

||||||

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

||||||||||||

|

A5 |

|

15 |

|

|

|

|

|

|

18 |

|

|

A2 |

||||||

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

||||||||||

|

A4 |

|

16 |

|

|

|

|

|

|

17 |

|

|

A3 |

||||||

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TSOP-1/STSOP

UTRON TECHNOLOGY INC. |

P80053 |

1F, No. 11, R&D Rd. II, Science-Based Industrial Park, Hsinchu, Taiwan, R. O. C. TEL: 886-3-5777882 FAX: 886-3-5777919

1

UTRON |

|

UT62L1024(E) |

|

Rev. 1.1 |

128K X 8 BIT LOW POWER CMOS SRAM |

||

|

|

|

|

ABSOLUTE MAXIMUM RATINGS* |

|

|

|

|

|

|

|

PARAMETER |

SYMBOL |

RATING |

UNIT |

Terminal Voltage with Respect to Vss |

VTERM |

-0.5 to +4.6 |

V |

Operating Temperature |

TA |

-20 to 80 |

|

Storage Temperature |

TSTG |

-65 to +150 |

|

Power Dissipation |

PD |

1 |

W |

DC Output Current |

IOUT |

50 |

mA |

Soldering Temperature (under 10 sec) |

Tsolder |

260 |

|

*Stresses greater than those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress rating only and functional operation of the device or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to the absolute maximum rating conditions for extended period may affect device reliability.

TRUTH TABLE

MODE |

|

|

|

CE2 |

|

|

|

|

|

|

I/O OPERATION |

SUPPLY CURRENT |

CE1 |

|

OE |

|

|

WE |

|||||||

Standby |

|

H |

X |

|

X |

|

|

X |

|

High - Z |

ISB,ISB1 |

|

Standby |

|

X |

L |

|

X |

|

|

X |

|

High -Z |

ISB,ISB1 |

|

Output Disable |

|

L |

H |

|

H |

|

|

H |

|

High - Z |

ICC, ICC1 |

|

Read |

|

L |

H |

|

L |

|

|

H |

|

DOUT |

ICC, ICC1 |

|

Write |

|

L |

H |

|

X |

|

|

L |

|

DIN |

ICC, ICC1, |

|

Note: H = VIH, L=VIL, X = Don't care.

DC ELECTRICAL CHARACTERISTICS (VCC = 2.7V ~ 3.6V, TA = -20 ~80 )

PARAMETER |

SYMBOL |

TEST CONDITION |

|

MIN. |

TYP. |

MAX. |

UNIT |

|||||||

Input High Voltage |

VIH |

|

|

|

|

|

|

|

|

|

2.0 |

- |

VCC+0.5 |

V |

Input Low Voltage |

VIL |

|

|

|

|

|

|

|

|

|

- 0.5 |

- |

0.6 |

V |

Input Leakage Current |

IIL |

VSS VIN VCC |

|

- 1 |

- |

1 |

µA |

|||||||

Output Leakage Current |

IOL |

VSS VI/O VCC |

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

=VIH or CE2 = VIL or |

|

- 1 |

- |

1 |

µA |

||

|

|

|

CE1 |

|

||||||||||

|

|

|

|

|

|

= VIH or |

|

= VIL |

|

|

|

|

|

|

|

|

|

OE |

WE |

|

|

|

|

|

|||||

Output High Voltage |

VOH |

IOH = - 1mA |

|

2.0 |

- |

- |

V |

|||||||

Output Low Voltage |

VOL |

IOL= 4mA |

|

- |

- |

0.4 |

V |

|||||||

Average Operating |

ICC |

Cycle time = Min.,100% Duty, |

35 |

- |

40 |

60 |

mA |

|||||||

Power Supply Courrent |

|

|

|

|

|

=VIL, CE2 = VIH, |

55 |

- |

35 |

50 |

mA |

|||

|

|

CE1 |

||||||||||||

|

|

II/O = 0mA |

70 |

- |

30 |

40 |

mA |

|||||||

|

ICC1 |

Cycle time = 1µs, 100% Duty, |

|

- |

- |

5 |

mA |

|||||||

|

|

. |

|

|

0.2V,CE2 VCC-0.2V, |

|

||||||||

|

|

CE1 |

|

|||||||||||

|

|

II/O = 0Ma |

|

|

|

|

|

|||||||

Standby Power |

ISB |

|

|

|

|

|

=VIH or CE2 = VIL |

|

- |

- |

1.0 |

mA |

||

|

CE1 |

|

||||||||||||

Supply Current |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ISB1 |

|

CE1 |

VCC-0.2V or |

- L |

- |

1.0 |

100 |

µA |

||||||

|

|

|||||||||||||

|

|

20* |

||||||||||||

|

|

.CE2 0.2V |

|

|||||||||||

|

|

- LL |

- |

0.5 |

50 |

µA |

||||||||

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

10* |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

*Those parameters are for reference only under 50 |

|

|

|

|

|

|||||||||

UTRON TECHNOLOGY INC. |

P80053 |

1F, No. 11, R&D Rd. II, Science-Based Industrial Park, Hsinchu, Taiwan, R. O. C. TEL: 886-3-5777882 FAX: 886-3-5777919

2

UTRON |

|

|

UT62L1024(E) |

||

Rev. 1.1 |

128K X 8 BIT LOW POWER CMOS SRAM |

||||

|

|

|

|

|

|

CAPACITANCE (TA=25 , f=1.0MHz) |

|

|

|

|

|

|

|

|

|

|

|

PARAMETER |

|

SYMBOL |

MIN. |

MAX. |

UNIT |

Input Capacitance |

|

CIN |

- |

6 |

pF |

Input/Output Capacitance |

|

CI/O |

- |

8 |

pF |

Note : These parameters are guaranteed by device characterization, but not production tested.

AC TEST CONDITIONS

Input Pulse Levels |

0.4V to 2.4V |

Input Rise and Fall Times |

5ns |

Input and Output Timing Reference Levels |

1.5V |

Output Load |

CL=50pF, IOH/IOL=-1mA/2mA |

AC ELECTRICAL CHARACTERISTICS (VCC = 2.7V ~ 3.6V , TA = -20 ~80 )

(1) READ CYCLE

PARAMETER |

SYMBOL |

UT62L1024(E)-35 |

UT62L1024(E)-55 |

UT62L1024(E)-70 |

UNIT |

|||

|

|

MIN. |

MAX. |

MIN. |

MAX. |

MIN. |

MAX. |

|

Read Cycle Time |

tRC |

35 |

- |

55 |

- |

70 |

- |

ns |

Address Access Time |

tAA |

- |

35 |

- |

55 |

- |

70 |

ns |

Chip Enable Access Time |

tACE1, tACE2 |

- |

35 |

- |

55 |

- |

70 |

ns |

Output Enable Access Time |

tOE |

- |

25 |

- |

30 |

- |

35 |

ns |

Chip Enable to Output in Low-Z |

tCLZ1*, tCLZ2* |

10 |

- |

10 |

- |

10 |

- |

ns |

Output Enable to Output in Low-Z |

tOLZ* |

5 |

- |

5 |

- |

5 |

- |

ns |

Chip Disable to Output in High-Z |

tCHZ1*, tCHZ2* |

- |

25 |

- |

30 |

- |

35 |

ns |

Output Disable to Output in High-Z |

tOHZ* |

- |

25 |

- |

30 |

- |

35 |

ns |

Output Hold from Address Change |

tOH |

5 |

- |

5 |

- |

5 |

- |

ns |

(2) WRITE CYCLE |

|

|

|

|

|

|

|

|

PARAMETER |

SYMBOL |

UT62L1024(E)-35 |

UT62L1024(E)-55 |

UT62L1024(E)-70 |

UNIT |

|||

|

|

MIN. |

MAX. |

MIN. |

MAX. |

MIN. |

MAX. |

|

Write Cycle Time |

tWC |

35 |

- |

55 |

- |

70 |

- |

ns |

Address Valid to End of Write |

tAW |

30 |

- |

50 |

- |

60 |

- |

ns |

Chip Enable to End of Write |

tCW1, tCW2 |

30 |

- |

50 |

- |

60 |

- |

ns |

Address Set-up Time |

tAS |

0 |

- |

0 |

- |

0 |

- |

ns |

Write Pulse Width |

tWP |

25 |

- |

40 |

- |

45 |

- |

ns |

Write Recovery Time |

tWR |

0 |

- |

0 |

- |

0 |

- |

ns |

Data to Write Time Overlap |

tDW |

20 |

- |

25 |

- |

30 |

- |

ns |

Data Hold from End of Write-Time |

tDH |

0 |

- |

0 |

- |

0 |

- |

ns |

Output Active from End of Write |

tOW* |

5 |

- |

5 |

- |

5 |

- |

ns |

Write to Output in High-Z |

tWHZ* |

- |

15 |

- |

20 |

- |

25 |

ns |

*These parameters are guaranteed by device characterization, but not production tested.

UTRON TECHNOLOGY INC. |

P80053 |

1F, No. 11, R&D Rd. II, Science-Based Industrial Park, Hsinchu, Taiwan, R. O. C. TEL: 886-3-5777882 FAX: 886-3-5777919

3

UTRON |

UT62L1024(E) |

Rev. 1.1 |

128K X 8 BIT LOW POWER CMOS SRAM |

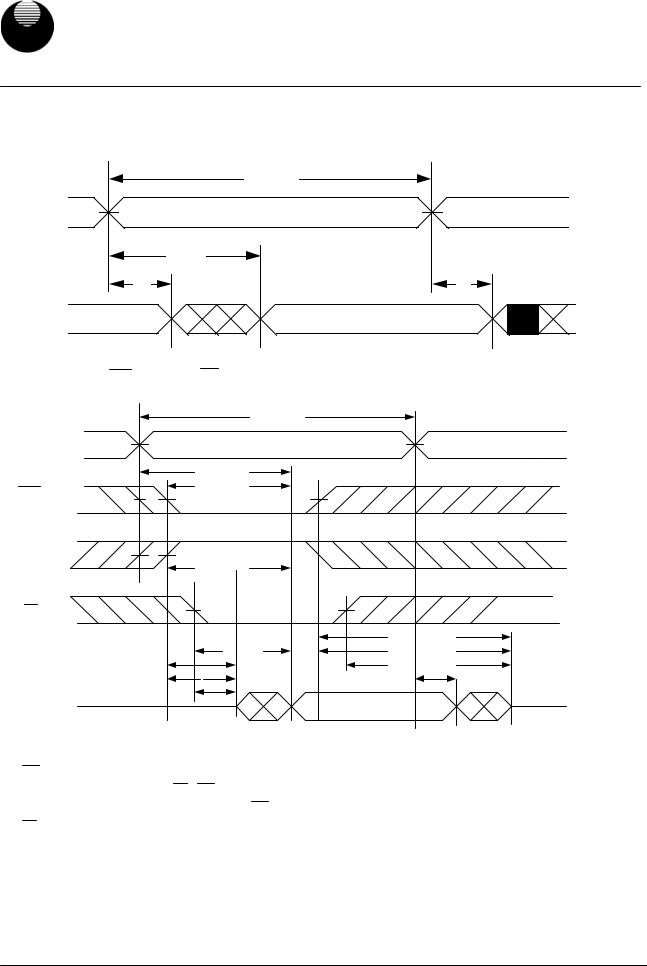

TIMING WAVEFORMS

READ CYCLE 1 (Address Controlled) (1,2,4)

tRC

Address

|

tAA |

tOH |

tOH |

DOUT |

Data Valid |

READ CYCLE 2 ( CE1 , CE2 and OE Controlled) (1,3,5,6)

t RC

Address

|

|

|

t AA |

|

CE1 |

|

|

t ACE1 |

|

CE2 |

|

|

t ACE2 |

|

|

|

|

|

|

OE |

|

|

|

t CHZ1 |

|

|

|

t OE |

|

|

t CLZ1 |

|

t CHZ2 |

|

|

|

|

||

|

t CLZ2 |

|

|

t OHZ |

Dout |

t OLZ |

|

t OH |

|

HIGH-Z |

|

HIGH-Z |

||

|

|

|

|

Data Valid |

Notes :

1.WE is HIGH for a read cycle.

2.Device is continuously selected OE , CE1 =VIL and CE2=VIH.

3.Address must be valid prior to or coincident with CE1 low and CE2 high transition; otherwise tAA is the limiting parameter.

4.OE is low.

5.tCLZ1, tCLZ2, tOLZ, tCHZ1, tCHZ2 and tOHZ are specified with CL=5pF. Transition is measured ± 500mV from steady state.

6.At any given temperature and voltage condition, tCHZ1 is less than tCLZ1, tCHZ2 is less than tCLZ2, tOHZ is less than tOLZ.

UTRON TECHNOLOGY INC. |

P80053 |

1F, No. 11, R&D Rd. II, Science-Based Industrial Park, Hsinchu, Taiwan, R. O. C. TEL: 886-3-5777882 FAX: 886-3-5777919

4

Loading...

Loading...