赤外線空間デジタルオーディオ伝送用送信デジタル信号処理

CXD4016R

概要・用途

CXD4016R

処理

は,民生機器向けの赤外線空間デジタルオーディオ伝送

ICで,RF用D/A

コンバータ,

PLL

を内蔵しています。全デジタル信号処理により無調整で安定した動作

が可能です。

特長・機能

1チップで送信デジタル信号処理をすべて処理

赤外線空間デジタルオーディオ伝送方式の民生用フォーマットに対応

3つのオーディオサンプリング周波数 (32kHz, 44.1kHz, 48kHz) に対応

D/Aコンバータ内蔵によりRFを直接出力できる

外付けRAM, PLL不要

<Audio I/Fブロック>

各種オーディオ用A/Dコンバータとインタフェース可能

<Parity Generatorブロック>

赤外線空間デジタルオーディオ伝送方式フォーマットのリードソロモンパリティを自動生成

<Modulatorブロック>

全デジタル処理により直接赤外線空間デジタルオーディオ伝送方式フォーマットの送信RF信号を生成

デジタルフィルタおよびRF用D/Aコンバータ内蔵により外部アナログ回路の簡易化可能

デジタル処理による安定したサブキャリアの生成が可能

(IEC61603-8-1準拠)

用の送信デジタル信号

<Controllerブロック>

簡易ピン設定モード

シリアルバスによるシリアルデータインタフェース

<PLLブロック>

パッケージ

赤外線空間デジタルオーディオ伝送方式フォーマットに必要なクロック生成

PLL

内蔵

(640fs)

のためのアナログ

64 pin LQFP (Plastic)

本資料に記載されております規格等は, 改良のため予告なく変更することがありますので, ご了承ください。

また本資料によって, 記載内容に関する工業所有権の実施許諾や, その他の権利に対する保証を認めたものではありません。

なお資料中に, 回路例が記載されている場合, これらは使用上の参考として, 代表的な応用例を示したものですので, これら回路

の使用に起因する損害について, 当社は一切責任を負いません。

- 1 -

J03Z16D64

構造

シリコンゲートCMOS IC

CXD4016R

絶対最大定格

電源電圧

入力電圧

出力電圧

保存周囲温度

推奨動作条件

電源電圧

D/A電源電圧

PLL電源電圧

動作温度

サンプリング周波数精度 ± 0.1%以内

入/出力容量

DD

V

V

I

– 0.5~ + 3.0

– 0.5~VDD + 0.5

V

V

( ≦ 3.0V)

V

O

– 0.5~VDD + 0.5

V

( ≦ 3.0V)

Tstg

DD 2.5 ± 0.2 V

V

DA 2.5 ± 0.2 V

V

V

PLL 2.5 ± 0.2 V

Topr

– 55~ + 125

– 40~ + 85

°

C

°

C

IN

入力端子

出力端子

入出力端子 CI/O 16 (最大)

C

OUT

C

16 (最大)

16 (最大)

注) 測定条件 : Tj = 25°C, VDD = VI = 0V, f = 1MHz

pF

pF

pF

- 2 -

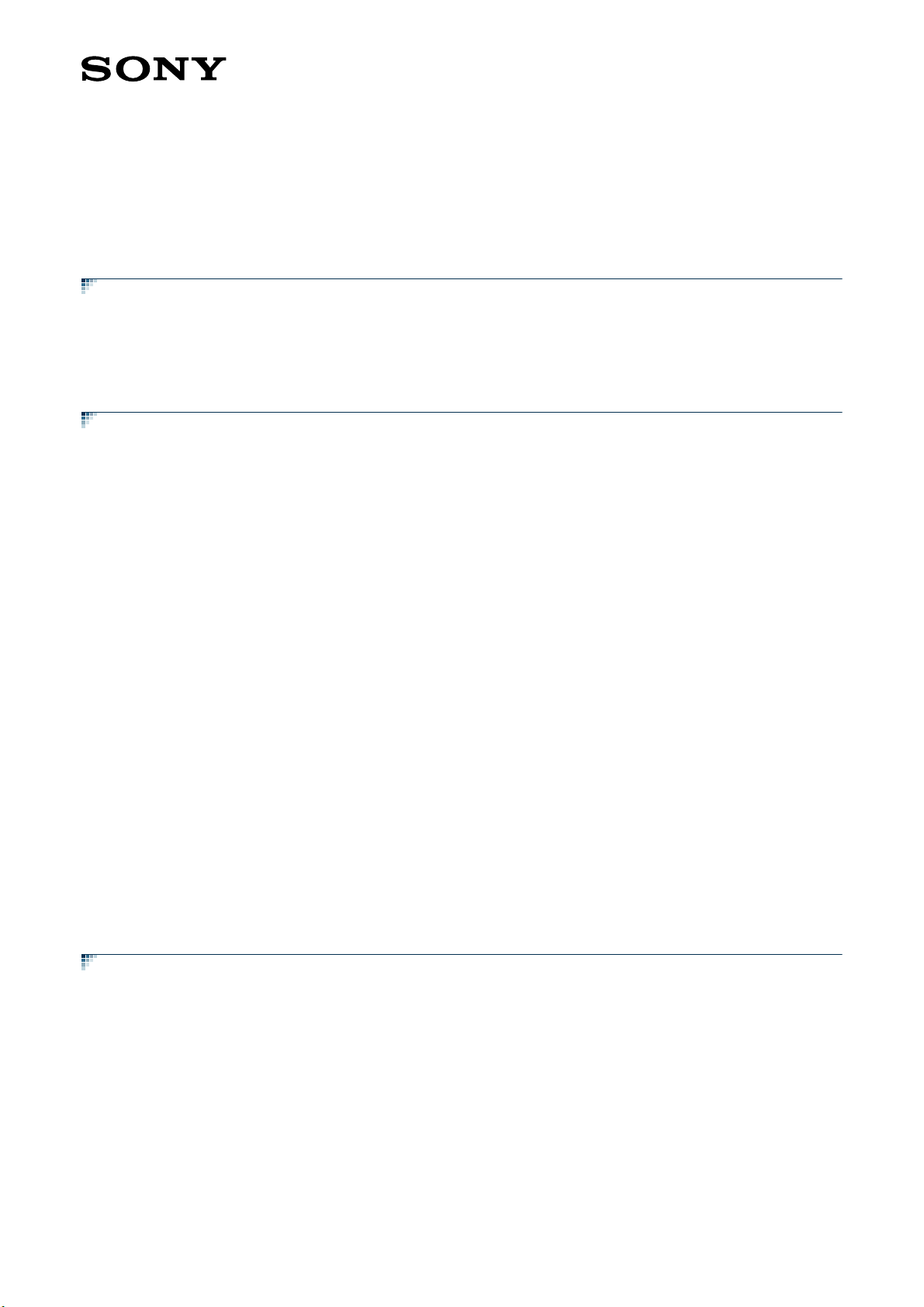

ブロック図

OSCI

OSCO

CK12

XRST

LRCK

BCK

DTIN

BCKOUT

LRCKOUT

CXD4016R

PLREF36PLVAR37APS41APVGS42APCPO

43

APAVD

44

57

59

53

64

49

50

48

51

52

Clock

Generator

Audio I/F

ReedSolomon

Parity

Generator

Buffer RAM Modulator

PLL

D/A

Converter

Controller

Clock

Selector

APAVS

45

APX

38

VCOT

46

DAAOUT

21

DAAVD

22

DAAVS

23

DAVREF

24

DAVRO

25

IFEXMD

3

IIFSEL1

4

IIFSEL0

5

EXCKSEL

6

CHNM_BL

7

DIVCODE

8

PCMID

9

EMPIN

10

XSCEN

14

SCLK

13

SWDT

15

CSOD

16

* TEST用端子を除く

12

VSS

VSS20VSS27VSS40VSS55VSS

58

VDD11VDD19VDD26VDD39VDD

56

- 3 -

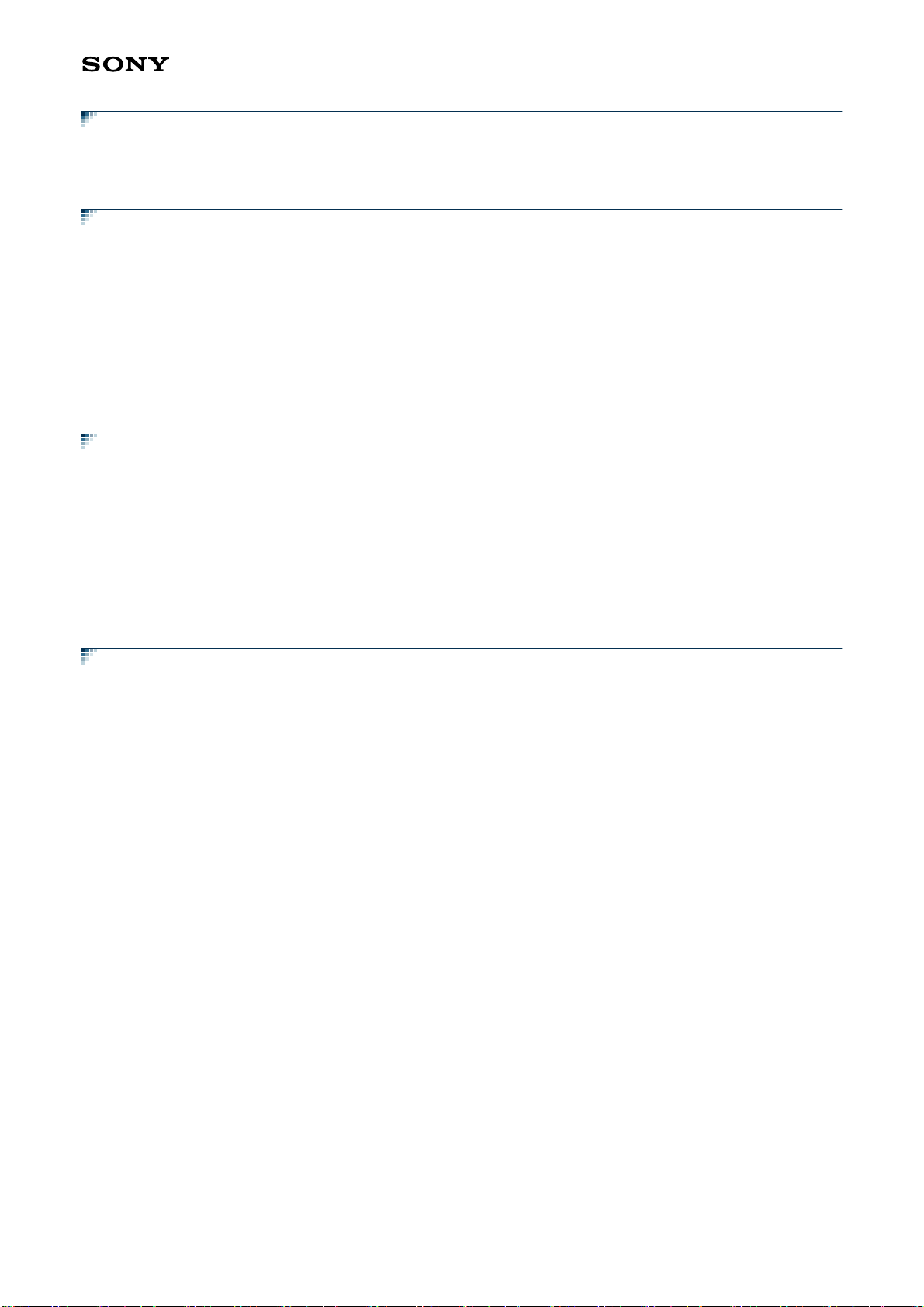

CXD4016R

端子配列図

BCKOUT

LRCKOUT

OSCO

LRCK

BCK

CK12

CSST

SS

V

V

DD

OSCI

V

SS

49

50

51

52

53

54

55

56

57

58

59

DTIN

VCOT

DT2_INF

48 47 46 45

APAVS

APAVD

44

APVGS

APCPO

APS

43 42 41 40 39 38 37

SS

V

DD

V

APX

PLVAR

PLREF

36

TEST6

TEST7

35 34 33

TEST5

32

31

30

29

28

27

26

25

24

23

22

TEST4

TEST3

TEST2

TEST1

TEST0

SS

V

V

DD

DAVRO

DAVREF

DAAVS

DAAVD

XTCK4

XSM

MST

XTST

XRST

60

61

62

63

64

1 2 3 4

SMCK

TESTMD

IFEXMD

6 9 10 11 12

IIFSEL0

EXCKSEL

7 8

DIVCODE

CHNM_BL

5

IIFSEL1

EMPIN

PCMID

VDD

SS

V

14 15 16

13

SCLK

SWDT

XSCEN

CSOD

21

20

19

18

17

DAAOUT

SS

V

V

DD

DACK

DAPD

- 4 -

CXD4016R

端子説明

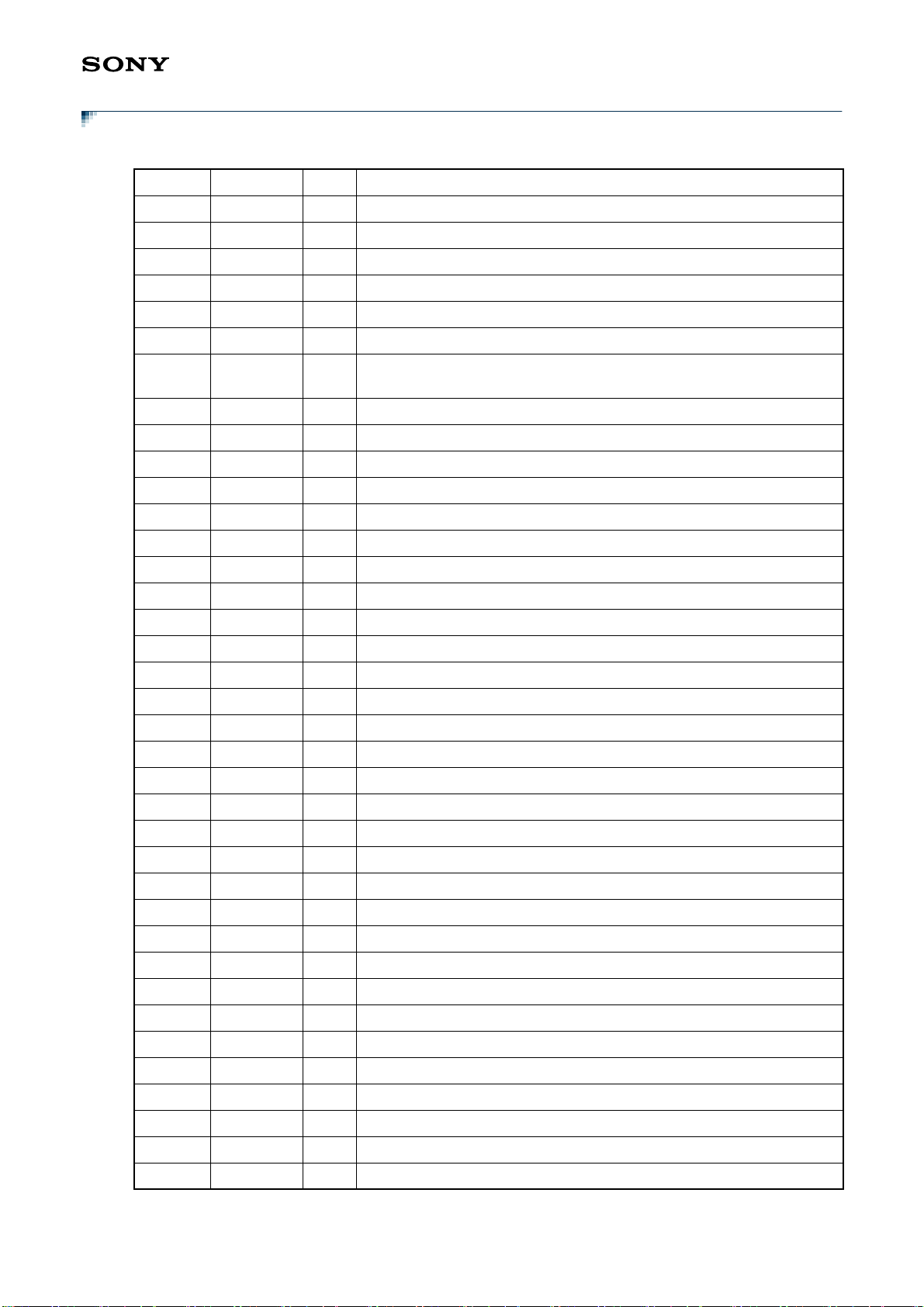

端子番号 端子記号 I/O 端子説明

1 TESTMD I

2SMCK I

3IFEXMD I

4 IIFSEL1 I

5 IIFSEL0 I

6EXCKSELI

7CHNM_BLI

8DIVCODEI

9PCMID I

10 EMPIN I

11 V

12 V

DD —

SS —

13 SCLK I

14 XSCEN I

15 SWDT I

16 CSOD O

17 DAPD O

18 DACK O

19 V

20 V

DD —

SS —

21 DAAOUT O

22 DAAVD —

23 DAAVS —

24 DAVREF I

25 DAVRO

26 V

27 V

DD —

SS —

I/ORF DAC用内部電流設定

28 TEST0 O

29 TEST1 O

30 TEST2 O

31 TEST3 O

32 TEST4 O

33 TEST5 O

34 TEST6 O

35 TEST7 O

36 PLREF O

37 PLVAR O

テストモード選択端子,通常 “L” に固定

SCAN用テスト端子,通常 “H” に固定

IIF拡張モード (L : Normal mode, H : Extension mode)

オーディオ入力モード選択

オーディオ入力モード選択

変調用クロック選択 (L : APX内部接続,H : VCOT端子入力)

Half-band : チャネル番号選択 (L : 0ch, H : 1ch)

Full-band : ビット長制限 (L : Full bit, H : 16 bit limited)

フル/ハーフバンドモード選択 (L : Full-band, H : Half-band)

Source_info pcm_id入力,通常 “L” に固定 (L : PCM data)

Source_info emphasis入力 (L : No emphasis, H : Emphasis)

デジタル電源

デジタルGND

シリアルインタフェースデータクロック入力

シリアルインタフェースイネーブル入力 (負論理)

シリアルインタフェースデータ書き込み入力

チャプタースタート遅延出力

テスト用端子

テスト用端子

デジタル電源

デジタルGND

RF DAC出力

RF DAC用アナログ電源

RF DAC用アナログGND

RF DAC基準電圧入力,1.1V (typ.) を印加する

デジタル電源

デジタルGND

テスト用出力端子

テスト用出力端子

テスト用出力端子

テスト用出力端子

テスト用出力端子

テスト用出力端子

テスト用出力端子

テスト用出力端子

PLLリファレンス出力

PLL分周出力 (APX出力またはVCOT入力の640分周)

- 5 -

端子番号 端子記号 I/O 端子説明

38 APX O

39 V

40 V

DD —

SS —

41 APS I

42 APVGS —

43 APCPO O

44 APAVD —

45 APAVS —

46 VCOT I

47 DT2_INF I

48 DTIN I

49 LRCK I

50 BCK I

51 BCKOUT O

52 LRCKOUT O

53 CK12 O

54 CSST I

55 V

56 V

SS —

DD —

57 OSCI I

58 V

SS

59 OSCO O

60 XTCK4 I

61 XSM I

62 MST I

63 XTST I

64 XRST I

PLL VCO出力,640fs

デジタル電源

デジタルGND

PLLリセット端子

PLLガードバンド用GND

PLLチャージポンプ出力

PLL用電源

PLL用GND

変調用外部クロック入力

テスト用端子,通常 “L” に固定

オーディオデータ入力

LRクロック入力

ビットクロック入力

ビットクロック出力 (3.072MHz)

LRクロック出力 (48kHz)

マスタクロックの分周クロック出力 (12.288MHz)

テスト用端子,通常 “L” に設定

デジタルGND

デジタル電源

マスタクロック用水晶発振回路入力 (24.576MHz)

デジタルGND

マスタクロック用水晶発振回路出力 (24.576MHz)

テスト用端子,通常 “L” に固定

SCAN用テスト端子,通常 “H” に固定

SCAN用テスト端子,通常 “L” に固定

SCAN用テスト端子,通常 “H” に固定

非同期リセット入力,電源ON時には,電源安定後,必ず一度 “L” にし,

リセットを行って下さい。

CXD4016R

- 6 -

CXD4016R

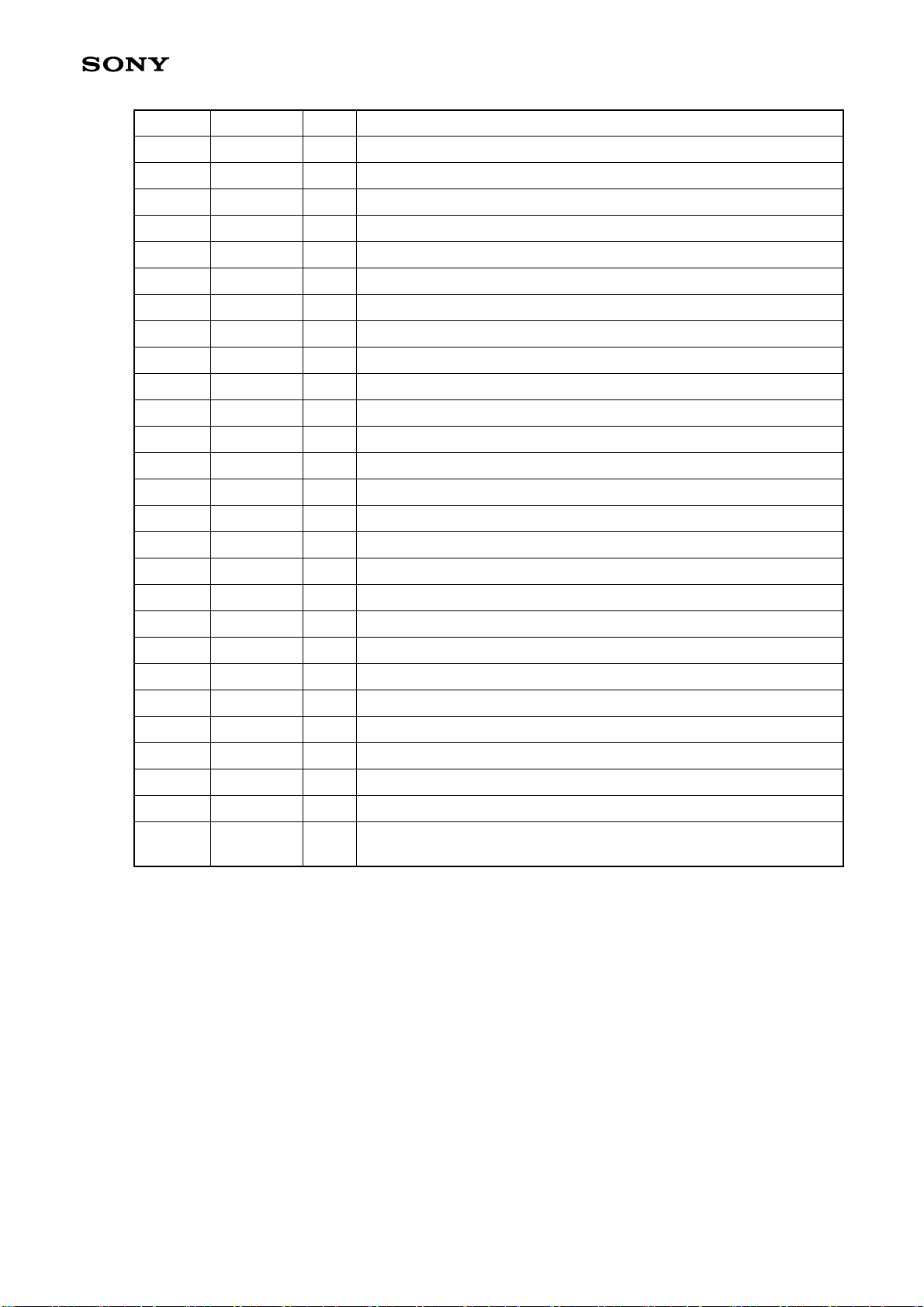

電気的特性

1. 直流特性

(V

“H” レベル入力電圧

“L” レベル入力電圧

“H” レベル出力電圧

“L” レベル出力電圧

“H” レベル出力電流

“L” レベル出力電流

入力リーク電流

PLL電源電圧

PLLチャージポンプ

出力電流

D/Aコンバータ

電源電圧

D/Aコンバータ

基準電圧

D/Aコンバータ

Full-scale調整抵抗

D/Aコンバータ

出力電流

D/A負荷抵抗

デジタル部電源電流

D/A部電源電流

DD = 2.5 ± 0.2V, VSS = 0V, Topr = – 40~ + 85

°

C)

項目 記号 条件 最小値 標準値 最大値 単位 適応端子

V

IH 1.7

IL – 0.3

V

OH IOH = – 100µAVDD – 0.2

V

OL IOL = 100µA0

V

I

OH VOH = VDD – 0.4V – 4.0

IOL VOL = 0.4V 4.0

L

I

PLL 2.3 2.5 2.7 V

V

CPO 500 µA

I

DA 2.3 2.5 2.7 V

V

REF 1.05 1.10 1.15 V

V

REF

R

DAVRO – DAAVS間

--

2.4 2.7 kΩ

VDD + 0.3

-

-

-

-

0.7

VDD

0.2

--

--

± 5 µA

V

mA

*1

*2

*2

*2

*1

*3

*4

*5

*6

*7

VREF = 1.10V,

REF = 2.7kΩ

DAC

I

R

R

Full-scale

Zero-scale

LSB-scale

L

DAAOUT – DAAVS間

4.67

0

5.194

2

5.71

20

20.3

150 160 Ω

mA

µA

µA

*8

*8

VDD = 2.5V

DD

I

fs = 44.1kHz

12 mA

*9

Full-band mode

V (DAAVD) = 2.5V

DA

I

fs = 44.1kHz

6.5 mA

*5

Full-band mode

V (APAVD) = 2.5V

PLL部電源電流

I

PLL

fs = 44.1kHz

3.5 mA

Full-band mode

適応端子

*1

TESTMD, SMCK, IFEXMD, IIFSEL1, IIFSEL0, EXCKSEL, CHNM_BL, DIVCODE, PCMID, EMPIN, SCLK,

XSCEN, SWDT, APS, VCOT, DT2_INF, DTIN, LRCK, BCK, CSST, XTCK4, XSM, MST, XTST, XRST

*2

CSOD, DAPD, DACK, TEST0, TEST1, TEST2, TEST3, TEST4, TEST5, TEST6, TEST7, PLREF, PLVAR,

APX, BCKOUT, LRCKOUT, CK12

*3

APAVD

*4

APCPO

*5

DAAVD

*6

DAVREF

*7

DAVRO

*8

DAAOUT

*9

VDD (端子番号11, 19, 26, 39, 56)

- 7 -

*3

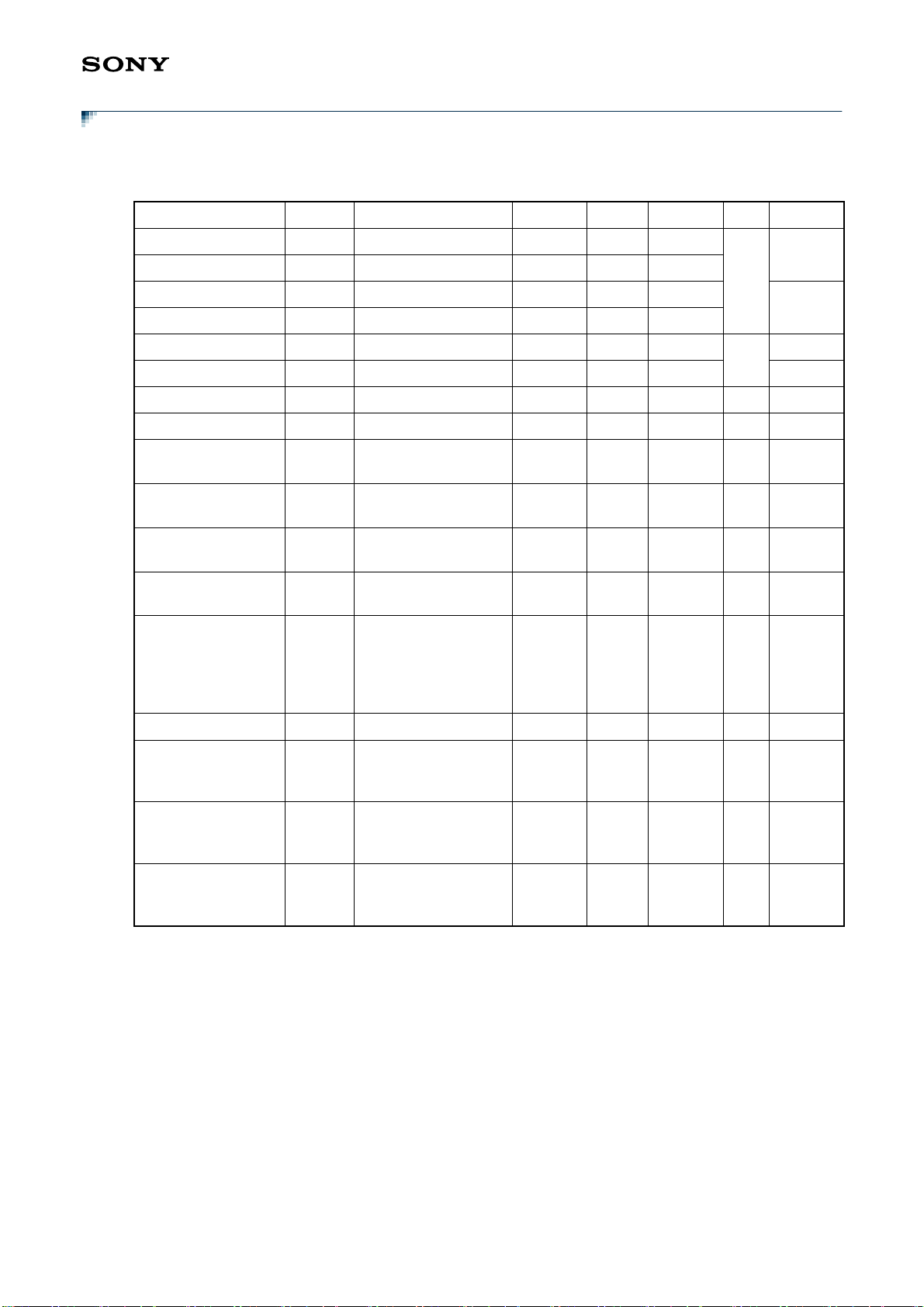

2. 交流特性

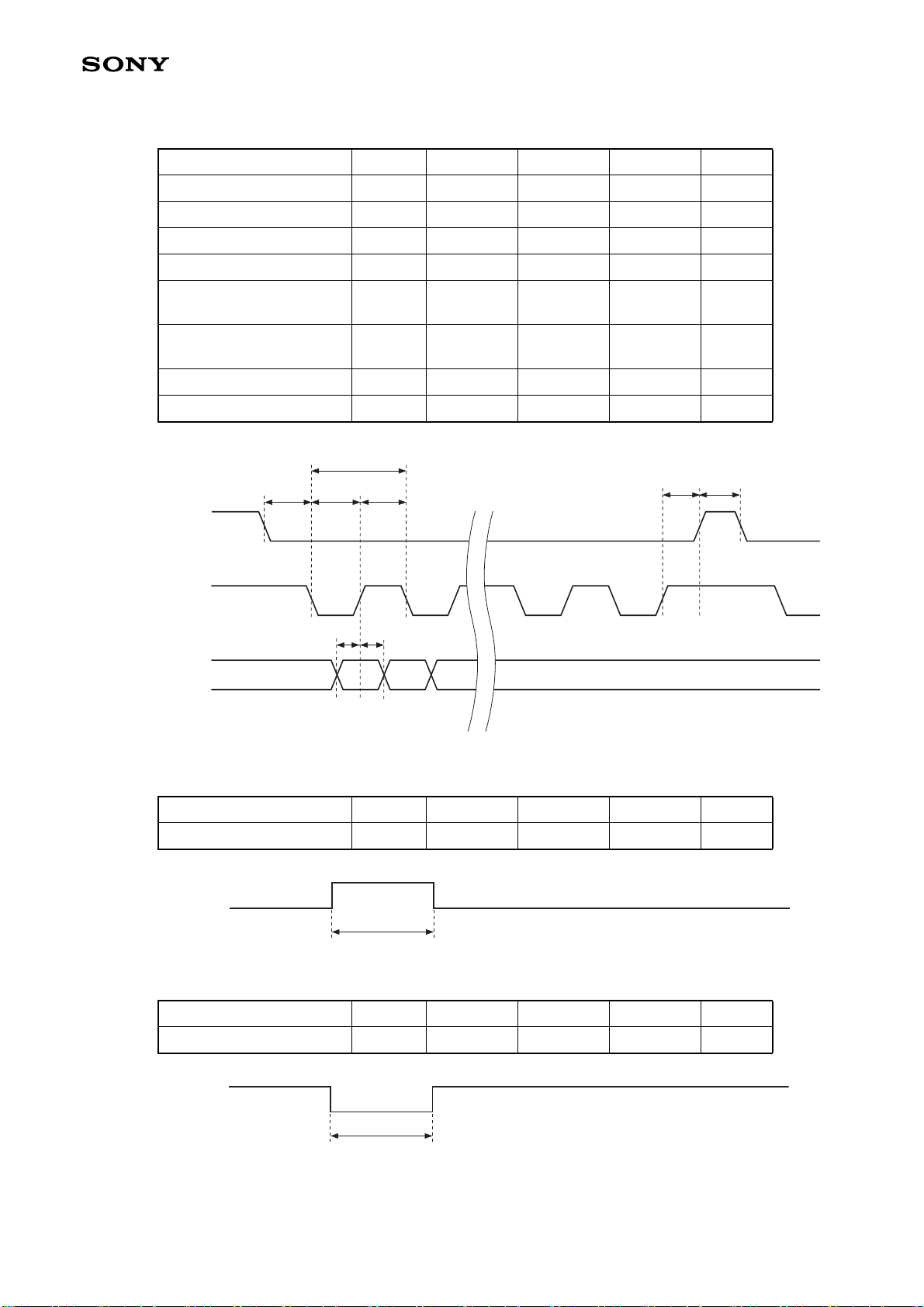

(1) OSCI端子,OSCO端子

CXD4016R

(a) 自励発振の場合

DD = 2.5 ± 0.2V, VSS = 0V, Topr = – 40~ + 85

(V

項目 記号 最小値 標準値 最大値 単位

f

発振周波数

SYS — 24.576 — MHz

(b) OSCI にパルスを入力する場合

(V

DD = 2.5 ± 0.2V, VSS = 0V, Topr = – 40~ + 85

項目 記号 最小値 標準値 最大値 単位

f

パルス周波数

“H” レベルパルス幅

“L” レベルパルス幅

立ち上がり時間/

立ち下がり時間

OSCI

SYS 24.330 24.576 24.600 MHz

t

WHX — 20.345 — ns

WLX — 20.345 — ns

t

t

R, tF 2ns

t

WHX tWLX

tCX (1/fSYS)

°

C)

°

C)

VIH

VIH × 0.9

DD/2

V

(2) VCOT端子

DD = 2.5 ± 0.2V, VSS = 0V, Topr = – 40~ + 85

(V

項目 記号 最小値 標準値 最大値 単位

パルス周波数

“H” レベルパルス幅

“L” レベルパルス幅

VCOT

V

IH × 0.1

IL

V

t

FtR

°

C)

f

CXR 20.275 — 31.027 MHz

WHXR 0.45 × tCXR — 0.55 × tCXR ns

t

WLXR 0.45 × tCXR — 0.55 × tCXR ns

t

tCXR (1/fCXR)

tWHXR tWLXR

VIH

VIH × 0.9

DD/2

V

V

IH × 0.1

V

IL

t

FtR

- 8 -

CXD4016R

(3) SCLK, XSCEN, SWDT, SRDT端子

DD = 2.5 ± 0.2V, VSS = 0V, Topr = – 40~ + 85

(V

項目 記号 最小値 標準値 最大値 単位

CW 200 — — ns

クロック周期

クロックパルス幅 “H”

クロックパルス幅 “L”

イネーブル信号パルス幅

イネーブル信号

セットアップ時間

イネーブル信号

ホールド時間

SWDTセットアップ時間

SWDTホールド時間

t

CSS tCWL tCWH

XSCEN

t

t

CWH 100 — — ns

CWL 100 — — ns

t

t

CSWH 170 — — ns

t

CSS 0——ns

t

CSH 100 — — ns

t

WSU 20——ns

t

WHD 100 — — ns

tCW

°

C)

tCSWHtCSH

SCLK

tWHD

tWSU

SWDT

(4) CSOD端子

DD = 2.5 ± 0.2V, VSS = 0V, Topr = – 40~ + 85

(V

項目 記号 最小値 標準値 最大値 単位

CSOD 260 — — µs

CSODパルス幅

CSOD

t

CSOD

t

(5) XRST端子

(VDD = 2.5 ± 0.2V, VSS = 0V, Topr = – 40~ + 85

項目 記号 最小値 標準値 最大値 単位

XRST 100.0 — — ns

XRSTパルス幅

t

An Example of DATA READ Phase

°

C)

°

C)

XRST

XRST

t

- 9 -

CXD4016R

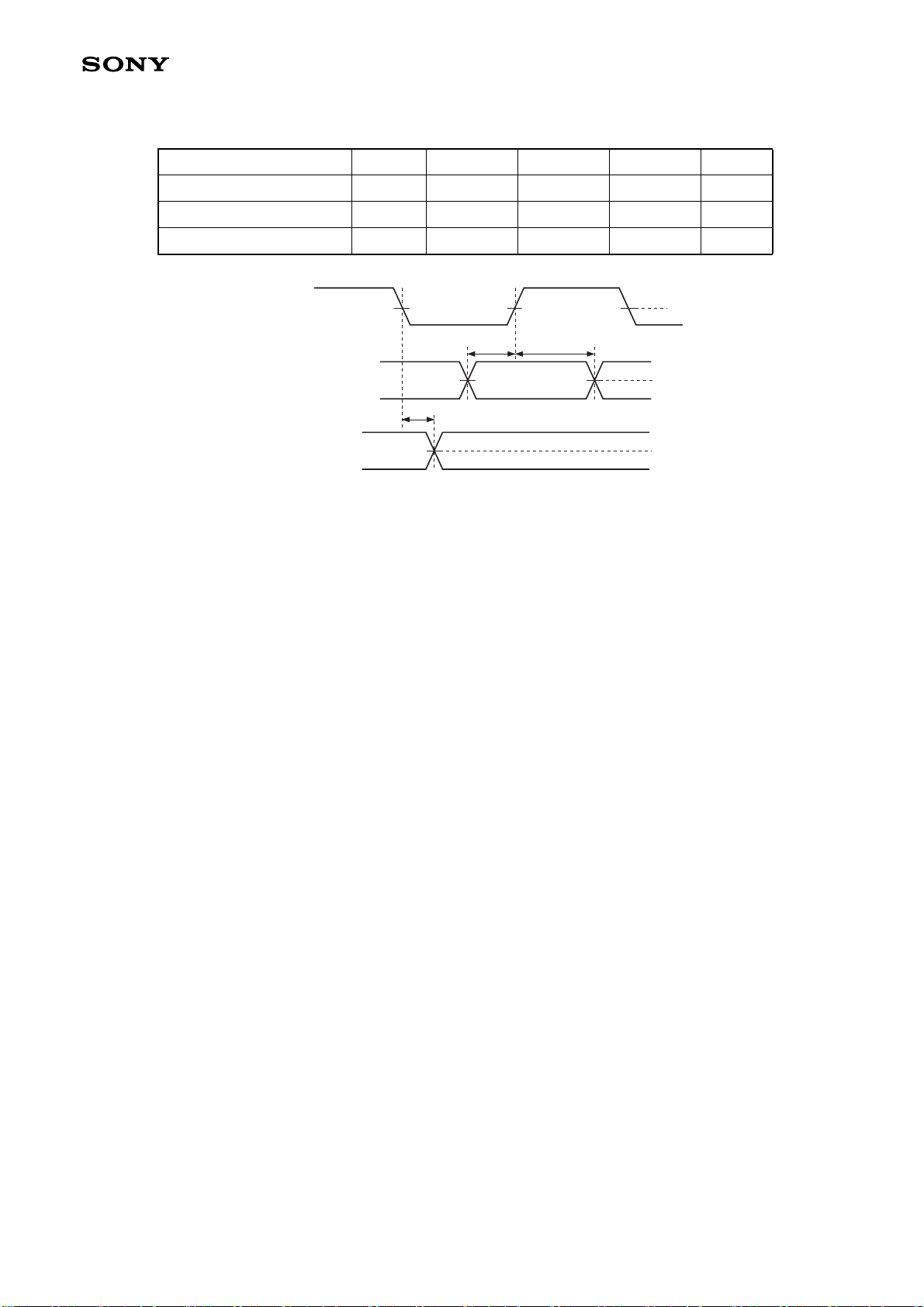

(6) BCK, DTIN, LRCK端子

DD = 2.5 ± 0.2V, VSS = 0V, Topr = – 40~ + 85

(V

項目 記号 最小値 標準値 最大値 単位

DTINセットアップ時間

DTINホールド時間

LRCKスキュー時間

BCK

DTIN

LRCK

°

C)

t

DTS 10——ns

t

DTH 100 — — ns

LRSK ——± 20 ns

t

VDD/2

t

DTH

V

DD

/2

V

DD

/2

LRSK

t

t

DTS

- 10 -

CXD4016R

機能説明

Clock Generatorの説明

1. 本

LSIはOSCI

生することができます。また,

端子,

OSCO

端子に

24.576MHz

OSCI

端子と

の水晶発振子を接続することにより,システムクロックを発

OSCO

端子との間には1MΩ (標準値) の帰還抵抗が内蔵されて

います。

OSCO

2.

端子を開放したまま,

OSCI

端子に

24.576MHz

の外部発振クロックを入力することにより,システム

クロックとすることができます。

3. システムクロックの周波数精度は,24.576MHz ± 100ppm以内として下さい。

PLL回路の説明

1.本LSIはOSCI

LSI

に内蔵のものを使用することができます。

は

2.

PLL

による変調用クロックの周波数は,入力デジタルオーディオ信号のサンプリング周波数をfsとすると,

640fs

です。

3.

PLL

回路として,

い。また,

端子によるシステムクロック供給のほかに,

LSI

に内蔵した

PLL

のチャージポンプ電流出力

PLL

を使用する場合,

APCPO

端子には,

PLL

による変調用クロックが必要です。

EXCKSEL

LSI

端子,

VCOT

端子に

“L”

を入力して下さ

外部にラグリードフィルタが必要です。

その際,配線がなるべく短くなるように十分考慮して下さい。

4. PLL回路として,LSI内蔵のPLLを使用しない場合,LSI外部にPLL回路が必要となります。EXCKSEL端

子に “H”,VCOT端子に変調用クロックを入力して下さい。クロックを生成するためのPLLの参照信号は

PLREF端子に出力され,その周波数はfsとなります。またこの時,VCOT端子に入力されたクロックは

LSI内部にて640分周され,PLVAR端子に出力されます。

PLL

回路

PIN設定/シリアルデータインタフェース

本

LSI

は大きく分け2つの設定モードがあります。1つは

PIN

設定モード,もう1つはシリアルデータインタフェース

モードです。シリアルデータインタフェースの設定により,ピン設定モードによるモード設定とシリアルデータ

インタフェースモードによるモード設定の切り換えが可能となります。例えば,シリアルデータインタフェース

01

の時,

モードのアドレス

SCEN01

データインタフェースが有効となります

ビットを

“0”

に設定すればピン設定が有効となり,

(

次頁シリアル設定コマンド表参照)。

“1”

に設定すればシリアル

LSIの端子のうちシリアルデータインタフェースモードでも設定できる端子は以下の通りです。

EXCKSEL端子,DIVCODE端子,CHNM_BL端子,IFEXMD端子,IIFSEL1端子,IIFSEL0端子,

PCMID端子,EMPIN端子

- 11 -

CXD4016R

シリアルデータインタフェースの説明

1. シリアルデータインタフェースタイミング

本LSIはSCLK端子,SWDT端子,XSCEN端子によってLSIの各種動作を変更することができます。以下

に各コード群のインタフェースのタイミングチャートを示します。なお,SCLK端子は他のデバイスと

共用しないで下さい。正しく通信を行うことができません。

2. XRST端子

XRST端子を “L” にしたリセットにて,内部レジスタはシリアルデータインタフェース設定コマンド表

に示されるDefault valueに初期化されます。

XSCEN

SCLK

D

SWDT

A7 A6 A5 A4 A3 A2 A1 A0

n – 1Dn – 2Dn – 3

D2 D3 D2 D1 D0

Internal

Registers

Valid

3. CXD4016RのFSLOCK信号を無効にする方法

CXD4016Rに入力するLRCKは,ジッタの無い安定したクロックであることが要求されます。CXD4016R

内部には,LRCKをリファレンスとしてPLLを構成し,640fsのクロックを生成していますが,PLLが

LOCKしているかどうかの信号 (FSLOCK) をLSI内部で生成しており,LOCKが外れるとRFの発生を一時

的に停止するように構成されています。このLOCK検出のロジックは条件として厳しいもので,LRCKの

ジッタが大きいとPLLで生成したクロックのジッタも大きくなり,LOCKが外れたと見なすことがあり

ます。

ジッタの大きいLRCKを使用することは推奨できませんが,どうしてもジッタの大きいLRCKを使用しな

ければならない場合,このFSLOCK信号を無効にしてRFの発生を一時停止する頻度を下げることが可能

なテストモードがあります。以下その方法について解説します。

シリアル設定コマンド表で示されるコマンドを送ることで,FSLOCKを有効にするか,無効にするかが

設定できます。デフォルトはFSLOCKがLOCK検出の論理に従い動作しています。

強制的にFSLOCK状態にするにはアドレス71h,データ0Fhをシリアル設定コマンドで送ります。

また,デフォルトに戻すにはアドレス71h,データ03hをシリアル設定コマンドで送ります。

この処理を施すことを強く推奨します。

- 12 -

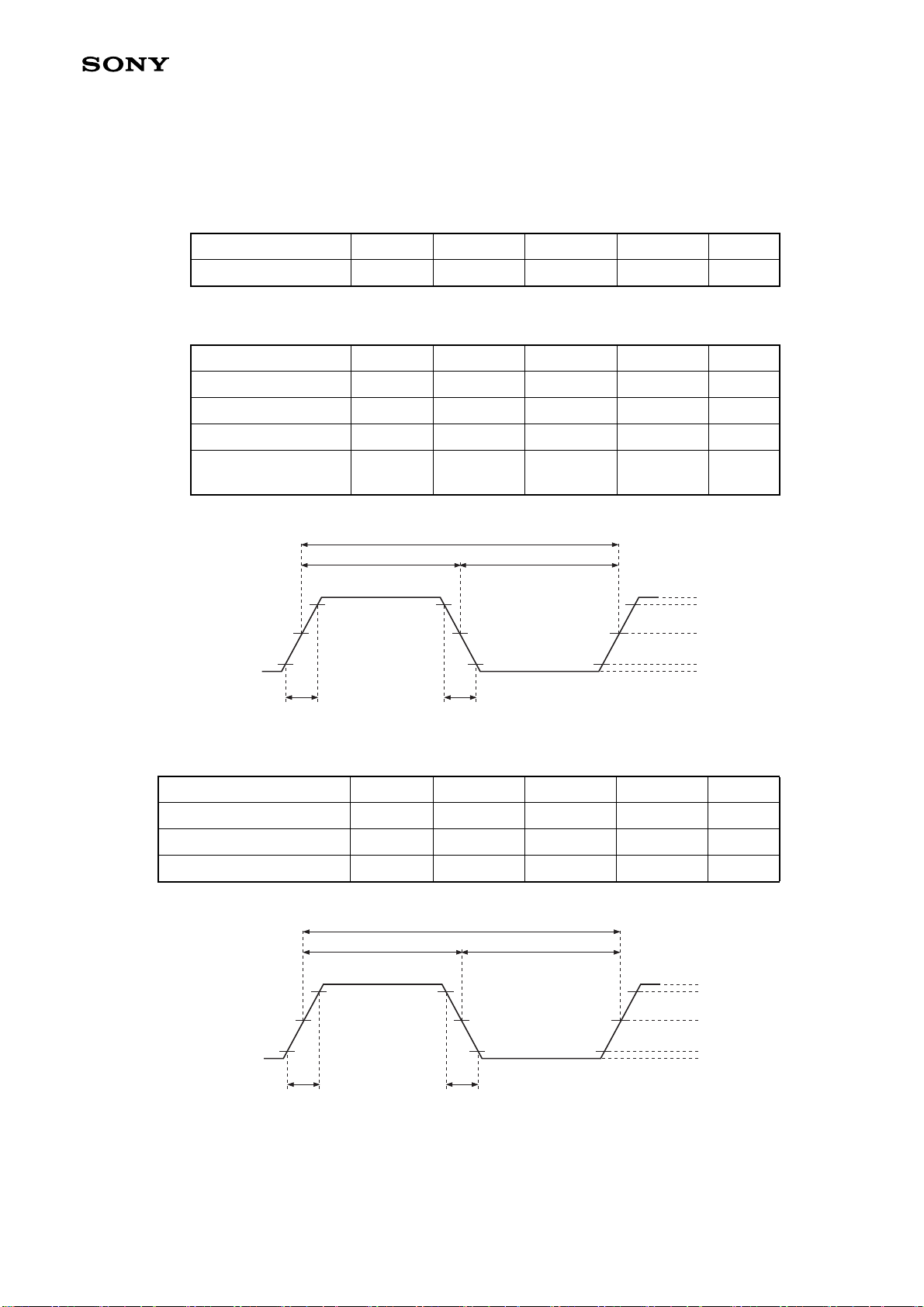

4. シリアル設定コマンド表

CXD4016R

Address

(HEX)

01h 00h 8

Default

value

Length

[bit]

Signal

Signal name

SCEN01 1

EXCKSEL 1

DIVCODE 1

CHNM_BL 1

IFEXMD 1

IIFSEL1 1 — Audio input interface mode select 1

IIFSEL0 1 — Audio input interface mode select 0

res. 1 0

SCEN02 1

CRC_FLG 1

length

[bit]

Va l u e E f fe c t

0

Address 01のシリアル設定を無効にする

1

Address 01のシリアル設定を有効にする

0

APX内蔵接続

1

VCOT端子入力

01Full-band mode

Half-band mode

0

0ch/full bit

1

1ch/16 bit limited

01Normal mode

Extension mode

必ず “0” とすること

0

Address 02のシリアル設定を無効にする

1

Address 02のシリアル設定を有効にする

01CRC off

CRC on (default)

VA L I D _ F L G 1

02h 40h 8

03h 69h 8 CATEGORY 8 —

71h 03h 8

PCM_ID 1

CPRGT_FLG 1

EMPHASIS 1

res. 2 00 Reserved

res. 4 0000

FSLOCK_EN 1

FSLOCK 1

res. 2 11

01Source_block is error free

Source_block contains some errors

01Data is Linear PCM

Data is used for other purposes

01Copyright is asserted

No copyright is asserted

01No emphasis

Emphasis

source_info Byte 3カテゴリコード

必ず “0000” とすること

0

FSLOCKのシリアル設定を無効にする

1

FSLOCKのシリアル設定を有効にする

0

強制的にLOCKしていない論理にする

1

強制的にLOCKしている論理にする

必ず “11” とすること

- 13 -

CXD4016R

Audio I/Fの説明

1. 本LSIは以下に示すような接続によりオーディオ用A/Dコンバータを直結することができます。

DTIN端子 : A/Dコンバータの出力データを接続

BCK端子 : A/Dコンバータが出力するビットクロックを接続 (64fs)

LRCK端子 : A/Dコンバータが出力するサンプルクロックを接続 (fs)

本

LSI

で対応可能なサンプリング周波数

(fs) は32kHz, 44.1kHz, 48kHzの3

つです。また,fsの精度は ±

1000ppm

以内です。この範囲を一瞬でも超えると正しい動作を行わないことがありますのでご注意下さい。

2. サンプルクロックおよびビットクロックを入力する必要があるようなオーディオA/Dコンバータを使用

する場合のために,本

LSIではLRCKOUT

端子,

BCKOUT

端子,

CK12

端子を用意しています。

LRCKOUT端子 : 48kHzのサンプルクロック

BCKOUT端子 : 48kHz × 64のビットクロック

CK12端子 : 12.288MHz (48kHz × 256) のマスタクロック

LRCKOUT

A/D

は

端子はA/Dコンバータのサンプルクロックおよび本

コンバータのビットクロック端子と本

LSIのBCK

LSIのLRCK

端子に接続し,

端子に接続して下さい。

BCKOUT

端子

3. LRCKの1サイクルの中にはBCKが64サイクル含まれます。

4. DTINの入力形式は,アドレス01hのレジスタによる設定,またはIFEXMD端子,IIFSEL1端子,IIFSEL0

端子によってそれぞれ変更できます。

iif_mode名

mode-0 0 00

mode-1 0 01 I

mode-2 0 10

mode-3 0 11

mode-4 1 00

mode-5 1 01

注)1.

Full-band mode

CHNM_BLが “1”

IFEXMD IIFSEL [1 : 0]

データの入力形式

MSB first,前詰め 24bit

2

S 24bit

LSB first,後詰め 24bit

MSB first,後詰め 24bit

MSB first,後詰め 20bit

MSB first,後詰め 16bit

の時,

CHNM_BL

端子またはシリアルデータインタフェースのアドレス

に設定された時には,上位16ビットのみが有効となります。

01h

によって

2. Half-band modeの時,上位16ビットのみが有効となります。

- 14 -

以上をまとめたタイミングチャートを以下に示します。

オーディオA/Dコンバータ I/F タイミングチャート

CXD4016R

LRCK

BCK

DAOUT

LRCK

BCK

DAOUT

LRCK

BCK

DAOUT

LRCK

BCK

DAOUT

Left Channel

MSB LSB

mode-0

Left Channel

MSB LSB

mode-1

Left Channel

LSB MSB

mode-2

Left Channel

MSB LSB

LRCK

BCK

DAOUT

LRCK

BCK

DAOUT

mode-3

Left Channel

MSB LSB

mode-4

Left Channel

MSB LSB

mode-5

- 15 -

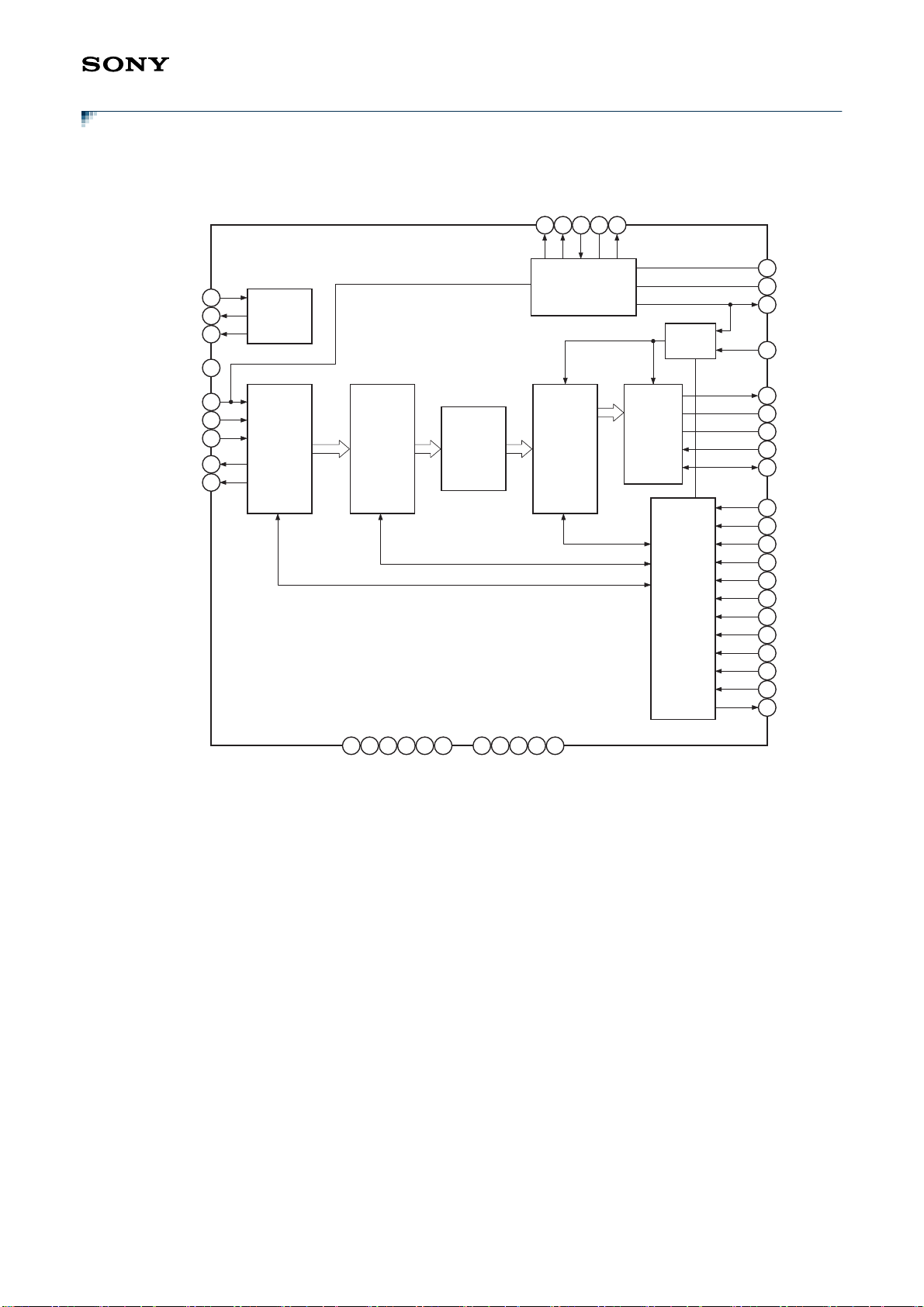

応用回路例

CXD4016R

RF

output

1 = 0.1µFR1 = 2.2kΩC2 = 4700pF

C

Rx = 4.7MΩ

1.1VၮḰ㔚

2.5VD

REF

32

TEST5

TEST4

TEST2

TEST3

TEST6

TEST7

35 34 33

PLREF

36

PLVAR

APX

V

DD

VSS

RxC2

C1

1

R

2.5VA

APS

APVGS

VCOT

DTIN

LRCK

49

APCPO

APAVD

APAVS

DT2_INF

BCK

50

43 42 41 40 39 38 37

44

48 47 46 45

TEST1

BCKOUT

LRCKOUT

52

51

TEST0

CK12

53

SS

V

CSST

54

DD

V

SS

V

55

DAVRO

DD

V

56

R

25

26

27

28

29

30

31

23

24

DAAVS

DAVREF

SS

OSCI

V

58

57

2.5VA

LPF

21

22

DAAVD

DAAOUT

OSCO

XTCK4

60

59

L

R

20

SS

V

XSM

61

19

DD

V

MST

62

18

DACK

DAPD

XTST

63

17

XRST

64

CSOD

SWDT

XSCEN

14 15 16

SCLK

13

V

SS

DD

V

EMPIN

PCMID

DIVCODE

CHNM_BL

7 8

EXCKSEL

6 9 10 11 12

IIFSEL0

5

IIFSEL1

IFEXMD

SMCK

TESTMD

1 2 3 4

ߎߩ⾗ᢱߩᔕ↪࿁〝ߪ㧘↪ߩෳ⠨ߣߒߡ㧘ઍ⊛ߥᔕ↪ࠍ␜

ߒߚ߽ߩߢ㧘ߎࠇࠄߩ࿁〝ߩ↪ߦ࿃ߔࠆ៊ኂࠆߪ╙⠪ߩᎿ

ᬺᚲᮭߩଚኂߩ㗴ߦߟߡ㧘ᒰ␠ߪ৻ಾߩ⽿છࠍ⽶߹ߖࠎޕ

circuit

Reset

Audio

A/D converter

- 16 -

X'tal

24.576MHz

使用上の注意

PLL部のループフィルタ部分は特性上重要です。そのため,ICピンに対し最短に配置し,かつ,周りは

AGNDでガードして下さい。また,ループフィルタのコンデンサ,抵抗は温度補償品を使用して下さい。

CXD4016R

192/fs [s]

場合,

側の

では,送信時に遅延が生じます。遅延時間はサンプリング周波数をfsとすると,

の遅延時間となります。例えば

384/fs [s]

の遅延時間となります。例えば

IC CXD4017R

覧下さい。

CXD4016R Evaluation Board

概要

CXD4016R Evaluation Board

評価できるように設計された専用基板です。入力オーディオ信号は光デジタルおよびアナログ

を装備しており,SWにて切り換えが可能になっています。

入力されたオーディオ信号は,CXD4016Rにて赤外線空間デジタルオーディオ伝送方式フォーマットRF信号

に変換され,SMBコネクタより出力されます。

fs = 48kHz

の場合,

fs = 48kHz

4ms

の遅延時間となります。また,

の場合,

8ms

の遅延時間となります。また,受信

でも受信時に遅延が生じますので注意が必要です。詳細は

は,赤外線空間デジタルオーディオ伝送の送信用に開発された

CXD4017R

CXD4016R

full-band

の場合,

half-band

の

のデータシートをご

CXD4016R

を簡易に

(

ピンジャック

)

特長

電源電圧 + 5V単一電源

アナログおよび光デジタルオーディオ入力選択可能

動作条件

電源電圧 + 5V (typ.)

消費電流 150mA (typ.)

入力信号 アナログまたは光デジタルオーディオ信号

使用方法

CXD4016R Evaluation Boardは,電源,アナログまたは光デジタルオーディオ信号を入力するだけで,簡単に

評価することができます。以下に手順を示します。

1. 電源接続端子J5に電源を接続します。(GND/+ 5V)

2. SW1はマニュアルリセットスイッチです。電源投入時は自動的にリセットがかかりますが,マニュアル

にてリセットを行いたい場合に使用します。

3. DIP SWのS2-1で,DIVCODE端子の設定が可能です。OFFで “L” に,ONで “H” に設定されます。

4. DIP SWのS2-2で,CHNM_BL端子の設定が可能です。OFFで “L” に,ONで “H” に設定されます。

5. DIP SWのS2-4で,IFEXMD端子の設定が可能です。OFFで “L” に,ONで “H” に設定されます。

6. DIP SWのS2-5で,IIFSEL1端子の設定が可能です。OFFで “L” に,ONで “H” に設定されます。

7. DIP SWのS2-6で,IIFSEL0端子の設定が可能です。OFFで “L” に,ONで “H” に設定されます。

DIP SWのS2-7

8.

で,オーディオ信号の選択が可能です。

OFF

で光デジタルオーディオ信号が,ONでアナログ

オーディオ信号が選択されます。

9. 光デジタルオーディオ信号は,U8の角型光コネクタに接続して下さい。

10. アナログオーディオ信号は,J1のピンジャックに接続して下さい。

11. DIP SWのS2-8で,アナログオーディオ信号を選択した場合のサンプリング周波数の変更が可能です。

OFFで48kHzが,ONで44.1kHzが設定されます。

- 17 -

CXD4016R

12. 上記以外の

S1 MODE

S2 MODE

DIP SW

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

は常に

OFF

に設定して下さい。以上の内容を以下の表にまとめたので参照して下さい。

常にOFF

常にOFF

常にOFF

常にOFF

常にOFF

常にOFF

常にOFF

常にOFF

OFF : DIVCODE = L/ON : DIVCODE = H

OFF : CHNM_BL = L/ON : CHNM_BL = H

常にOFF

OFF : IFEXMD = L/ON : IFEXMD = H

OFF : IIFSEL1 = L/ON : IIFSEL1 = H

OFF : IIFSEL0 = L/ON : IIFSEL0 = H

OFF : 光デジタル/ON : アナログ

OFF : 48kHz/ON : 44.1kHz (アナログオーディオ信号の時のみ)

13. 発光ダイオードD1は,DIVCODEが “L” の時消灯,DIVCODEが “H” の時点灯します。

14. 発光ダイオードD2は,CHNM_BLが “L” の時消灯,CHNM_BLが “H” の時点灯します。

15. 発光ダイオードD3およびD4は,オーディオ信号のサンプリング周波数を示します。その関係を以下の

表に示します。

D3, D4

消灯,消灯

消灯,点灯

点灯,点灯

点滅,点滅

16. 発光ダイオードD5~D8は使用していません。

17. SMBコネクタJ8から,赤外線空間デジタルオーディオ伝送方式フォーマットRF信号が出力されます。

18. J2およびJ3は使用しません。

サンプリング周波数

44.1kHz

48kHz

32kHz

UNLOCK

- 18 -

CXD4016R EVB半導体部品リスト

パーツNo. 製品名 メーカ

U1, 3 NJM2100M

U2 AK5353VT

U4, 21 TC74LCX541F

U5 CXD4016R SONY

新日本無線

旭化成マイクロシステム

東芝

CXD4016R

U6 TC74VHC04F

U7 CS8415A-CZ Cirrus Logic

U8 TORX141P

U9 FXO-31FL 24.576MHz

U10 EP1K100QI208-2 ALTERA

U11 EPC2LI20 ALTERA

U12 FXO-31FL 22.5792MHz

U13, 14, 15, 16, 17, 18 LM317A National Semiconductor

U19, 20 TL7705CP Texas Instruments

U22 AD8057ART Analog Devices

Q1 2SC2223L NEC

D1, 2 TLG124

D3, 4 TLY124

D5, 6 TLO124

D7, 8 TLR124

D9~20

1S1588

東芝

東芝

京セラキンセキ

京セラキンセキ

東芝

東芝

東芝

東芝

東芝

FPGAの動作について

1. S2-7で設定された光デジタルオーディオ信号,またはアナログオーディオ信号の選択を行います。

2. 選択されたオーディオ信号を,S2-4, S2-5, S2-6で設定されたDTIN端子の入力形式に変換します。

3. サンプリング周波数の検出を行います。

- 19 -

回路図

CXD4016R

DT2_INF

DTIN

LRCK

APS_XRST

BCKOUT

BCK

CSOD

CK12

LRCKOUT

CSST

XRST

IFEXMD

IIFSEL1

IIFSEL0

CHNM_BL

DIVCODE

EXCKSEL

PCMID

EMPIN

SCLK

RFOUT

XSCEN

DAPD

CXD4016R

DAAOUT

DAAOUT

SWDT

PLD1

AIF

SDTO_1

LRCK_AD

MCLK

(High-speed Signal)

MCLK

SDTO_1

LRCK_AD

DTIN

DT2_INF

SCLK_AD

PDN

PDN

SCLK_AD

(High-speed Signal)

BCK

LRCK

APS_XRST

DIF

CSOD

BCKOUT

LRCKOUT

COPY

EMPH

COPY

EMPH

(High-speed Signal)

CK12

XRST

CSST

IFEXMD

RST

RERR

RCBL

PRO

RST

PRO

RCBL

RERR

IIFSEL1

CHS

NVERR

CHS

NVERR

IIFSEL0

EXCKSEL

OSCLK

OLRCK

OSCLK

OLRCK

PCMID

DIVCODE

CHNM_BL

SDOUT

AUDIOUC

U

AUDIO

SDOUT

EMPIN

C

SCLK

ORIG

ORIG

(Middle-speed Signal)

DAPD

SWDT

XSCEN

RMCK

(High-speed Signal)

RMCK

PWXRST

XRSTPW1

XRSTPW2

XRSTPW1

XRSTPW2

CXD4016R EVB࿁〝࿑ TOP

POWER

- 20 -

SDTO_1

SCLK_AD

PDN

LRCK_AD

MCLK

CXD4016R

D

DGND

AINR1

TP2

AINL1

TP1

TP3

LC-2S-BK

VD5

1

LC-2S-R

1

LC-2S-W

1

C5

D

R9

2200p

10k

U2

A

131415

16

DIF

TTL

TST

PDN

SCLK

AINR

AINL

VREF

VCOM

C7

0.1µ

4.7µ/16V T

A

AGNDVAVD

C11

0.1µ

C10

4.7µ/16V T

1234567

C6

R19

100

D

101112

LRCK

MCLK

AK5353VT

DGND SDTO

89

C13

0.1µ

VA5

A

C12

10µ/16V T

A

MCLK

TP4

1

LC-2S-Y

C19

VD5

C18

C20

1011

A8

GNDY8

Y7Y6Y5Y4Y3Y2Y1G2V

U4

121314151617181920

SCLK

TP6

LC-2S-G

0.1µ

D

10µ/16V T

AGND

TP5

LC-2S-BK

2200p

AA

100

R21

100

R22

1

A5A6A7

R2322R24

1

A

100

123456789

A1A2A3

A4

G1

C23

CC

0.1µ

TC74LCX541F

VD33

VA5

R2

R1

C2

0.1µ

C1

22µ/16V

10k

20k

R6

470

C4

4.7µ/16V T

R5

330

7

4

A

R4

8

AA

R3

20k

C3

22µ/16V

10k

2

U1B

NJM2100M

6

5

1

3

U1A

NJM2100M

R10

4.7k

AAA

C9

4.7k

0.1µ

R8

VA5

C8

A

RV1A

3

J1

RCA JACK 2P

Rch_1

(RED)

22µ/16V

2

50k

3

2

Lch_1

(WHITE)

1

1

R7

330k

R12

R11

VA5

C15

C14

A

A

10k

20k

0.1µ

AA

22µ/16V

A

8

R13

C16

RV1B

R16

470

R15

330

4

6

R14

10k

1

2

20k

22µ/16V

5

50k

6

7

3

5

VA5

R17

4

C17

4.7µ/16V T

U3B

NJM2100M

U3A

NJM2100M

R18

4.7k

330k

A

CXD4016R EVB࿁〝࿑ AUDIO

R20

4.7k

C22

0.1µ

C21

22µ/16V

A

A A A

- 21 -

CXD4016R

PLREF

TP8

PLVAR

TP7

LC-2S-Y

LC-2S-BL

TP29

C36

LC-2S-Y

Q1

0.01µ

1

C38

2SC2223L

D

R43

100

C37

0.1µ

0.01µ

DAAOUT

CSOD

TP30

LC-2S-G

1

SCLK

1

R45

R44

TP31

1k

10k

XSCEN

LC-2S-Y

1

TP32

LC-2S-Y

A A

SWDT

TP33

1

LC-2S-Y

CSOD

SWDT

XSCEN

SCLK

CXD4016R EVB࿁〝࿑ MAIN

1

TP18

LC-2S-BK

DGND

A D

1

TP17

LC-2S-BK

AGND

VA5VA5

VR1

200

R38

2

1

DAVRO

DAVREF

CXD4016R

C31

0.1µ

910

13

A A

C32

0.1µ

DAAOUT

TP22

LC-2S-Y

1

VA25D

R39

150

C34

0.1µ

22232425262728

SS

V

DAAVS

DAAVD

DAAOUT

DAPD

R40

0

1718192021

DD

V

DAPD

DACK

R35

1.2k

VA25A

DAVREF

TP21

LC-2S-G

AAA

R36

2.7k

VD25D

C28

0.1µ

293031

32

TEST3

TEST4

TEST5

33

R31

1

1

APX

TP10

LC-2S-Y

APS

TP9

LC-2S-Y

100

R30

100

R29

0

1

C27

R28

VA25P

0.1µ

0

C26

0.1µ

A

R27

22

1

D

TEST6

34

TEST7

35

PLREF

36

PLVAR

37

APX

38

V

DD

39

V

SS

40

APS

41

APVGS

42

A

APCPO

43

APAVD

44

APAVS

45

VCOT

46

DT2_INF

47

DTIN

48

TEST2

TEST1

TEST0

SS

DD

V

V

U5

DAAOUT_Buf

C35

0.1µ

A

R42

4.7k

R41

0

1

TP24

DACK

LC-2S-Y

1

TP23

DAPD

LC-2S-Y

CSOD

16

SWDT

15

XSCEN

14

SCLK

13

V

SS

12

V

DD

11

EMPIN

10

PCMID

9

DIVCODE

8

CHNM_BL

7

EXCKSEL

6

IIFSEL0

5

IIFSEL1

4

IFEXMD

3

SMCK

2

TESTMD

1

LRCK

BCK

BCKOUT

LRCKOUT

CK12

CSST

VSSVDDOSCI

VSSOSCO

XTCK4

XSM

MST

XTST

27pF

XRST

64

DIVCODE

CHNM_BL

PCMID

EMPIN

1

TP37

CHNM_BL

LC-2S-Y

1

TP36

DIVCODE

LC-2S-Y

1

TP35

PCMID

LC-2S-BL

1

TP34

EMPIN

LC-2S-BL

1

EXCKSEL

TP28

LC-2S-BL

R37ᰳ⇟

XRST

IIFSEL0

TP27

IIFSEL1

TP26

IFEXMD

TP25

LC-2S-G

LC-2S-G

LC-2S-Y

1

1

1

IIFSEL1

IIFSEL0

IFEXMD

EXCKSEL

C25

0.1µ

R25

2.2k

C24

R26

4700p

4.7M

A

1

DT2_INF

TP11

LC-2S-BL

1

DTIN

TP12

LC-2S-Y

DTIN

APS_XRST

DT2_INF

495051525354555657585960616263

C29 0.1µ

TP20

R33 100

R34 22

CK12

LRCKOUT

CSST

1

1

TP19

LC-2S-Y

CSST

C30

18p

LC-2S-BL

CK12

LRCK

TP16

LC-2S-Y

BCK

TP15

LC-2S-Y

BCKOUT

TP14

LC-2S-BL

LRCKOUT

TP13

LC-2S-G

1

R32 100

1

1

1

BCK

LRCK

BCKOUT

Y1

C33

DD

CX-49G_24.576MHz

- 22 -

ORIGCU

AUDIO

SDOUT

NVERR

OSCLK

OLRCK

CXD4016R

VD33

VD33

C40

R46

D

0.01µ

R47

D

47k

D

28

VL3+

ORIG

U7

COPY

VL2+

123456789

100

R50

R49

100

U

C

H/S

EMPH

RXP0

RXN0

C42 0.01µ

D

VA5

C41

0.01µ

100

VL+

VA+

R51

47k

DGND

AGND

A

R53 100

D

DGND3

DGND2

AUDIOx

FILT

RSTx

RMCK

1011131214

R52 22

R57 100

R55 100

SDOUT

RERR

R56 100

100

R60 100

R59 100

15161718192021222324252627

OSCLK

OLRCK

PRO

RCBL

CHS NVERR

0

CS8415A-CZ

R61

1.2k

C45

4700p

C44

1000p

C43

0.1µ

C47

0.1µ

D

TP40

LC-2S-BK

1

DGND

AA

VD33

SPDIF

TP38

LC-2S-Y

C39

0.1µ

13

14

6A

CC

V

U6

1A1Y2A2Y3A3YGND 4Y

1234567

COPY

EMPH

1

4A

5Y6Y5A

89101211

D

R48

47k

D

74VHC04F

D

RST

VD33

R54

RERR

RMCK

R58

PRO

RCBL

L1

- 23 -

CHS

47µH

12345

OUT

U8

GND

CC

V

NC

C46

NC

0.1µ

TORX141P

CXD4016R EVB࿁〝࿑ DIGITAL INTERFACE

A

1

AGND

TP39

LC-2S-BK

D

A1

J2

10

U9

VD33

GNDA3GNDA5GNDA7GNDA9GND

123456789

IL-10P-S3EN2

1

2

3

4

5

6

7

8

9

IFdata6

IFdata7

IFdata9

IFdata10

IFdata8

VD25B

TH

TH6

TH

TH5

IFdata1

IFdata2

IFdata3

IFdata4

IFdata5

R62 22

OUT

GND

TH4

DD

V

43

C48

TH

INHX

TH3

TH

12

FXO-31FL_24.576MHz

D D

TH

TH2

0.1µ

IFdata6

IFdata7

IFdata8

IFdata9

IFdata10

TH

TH1

CXD4016R

A1

IFdata5

R64

1k

IFdata4

157

158

159

160

161

162

163

164

165

166

167

168

169

170

171

172

173

174

175

176

177

178

179

180

181

182

183

184

185

186

187

188

189

190

191

192

193

194

195

196

197

198

199

200

201

202

203

204

205

206

207

208

R63

IFdata3

10k

I_O

I_O

IO

I_O

I_O

I_O

I_O

I_O

IO

I_O

INT

I_O

I_O

I_O

I_O

I_O

I_O

IO

I_O

I_O

I_O

INT

I_O

CS

CC

CC

CC

nRS

nWS

nCS

V

GND

V

GND

CC

GND

V

CC

GNDA3GNDA5GNDA7GNDA9GND

123456789

IL-10P-S3EN2

D

1

2

3

4

5

6

7

8

9

IFdata2

IFdata1

R65 100

C54

0.1µ

150

151

152

153

154

155

156

INT

TDI

nCE

GND

CC

DCLK

DATA0

V

DATA1

DATA2

DATA3

DATA4

DATA5

DATA6

DATA7

IFdata1

IFdata2

IFdata3

IFdata4

IFdata5

DEV_CLRn

Ded_Input

CRYST24M

Ded_Input

V

DEV_OE

IFdata6

IFdata7

IFdata8

V

IFdata9

IFdata10

IO

CC

TCK

CONF_DONE

nCEO

TDO

V

GND

123456789

DD

TP46

TP45

BCK

BCKOUT

APS_XRST

100

R72

141

142

143

I_O

BCK

BCKOUT

APS_XRST

SCLK_AD

PDN

I_O

RDYnBUSY

LC-2S-BK

DGND

LC-2S-BK

DGND

CSOD

LRCKOUT

138

139

140

CSOD

LRCKOUT

I_O

COPY

1

1

CK12

100

R74

C57

0.1µ

134

135

136

137

IO

I_O

CC

GND

CK12

V

INT

IO

CC

CC

INIT_DONE

GND

V

V

CSST

133

CSST

GND

100

R76

132

I_O

EMPHx

IFEXMD

XRST

C59

0.1µ

128

129

130

131

INT

GND

CC

XRST

V

IFEXMD

U10

EP1K100QI208-2_1

RSTx

RERR

RCBL

PRO

IIFSEL1

IIFSEL0

127

IIFSEL0

IIFSEL1

I_O

CHS

CHNM_BL

EXCKSEL

124

125

126

EXCKSEL

CHNM_BL

NVERR

GND

C61

123

INT

CC

V

INT

CC

V

DIVCODE

0.1µ

121

122

GND

DIVCODE

IO

CC

V

GND

PCMID

120

I_O

PCMID

OSCLK

OLRCK

EMPIN

SCLK

XSCEN

DAPD

100

TH9

TH

R78

R79 100

C63

0.1µ

112

113

114

115

116

117

118

119

IO

I_O

I_O

CC

GND

SCLK

V

DAPD

EMPIN

XSCEN

IO

CC

I_O

SDOUT

I_O

AUDIOx

V

GNDUC

COM

R1

R2

R3

R4

R5

R6

R7

R8

RA2

M9-1-103J

DTIN

DT2_INF

LRCK

R71 0

R66 100

R68 100

C55

0.1µ

144

145

146

147

148

149

IO

CC

GND

DTIN

LRCK

V

DT2_INF

USER_IO

SDTO_1

I_O

LRCK_AD

CLKUSR_I_O

MCLK

I_O

10111213151416171819202122232425262728293031323334353637383940414243444546474849505152

R80 100

111

SWDT

110

SWDT

I_O

IO

CC

V

ORIG

C74

0.1µ

10k

2

1

SEL

CC

V

45678910

Vcc

GND

TCK

TDO

3

NCNCOE

C72

0.1µ

C71

0.1µ

C70

0.1µ

C69

0.1µ

C73

0.1µ

R81

22

C68

0.1µ

NCNCNC

NCNCNC

TMS

1415161718

VppSel

RA5

GND

TDI

RMCK

1

R8

LED4

LED3

LED2

LED1

J4

C75

LED8

LED7

LED6

LED5

0.1µ

LED8

LED7

LED6

LED5

LC-2S-Y

D

XG4C-1031

R91

1k

D

nInt_Conf

13

nCASC

12

TDI

11

GND

10

nCS

9

EPC2LI20

DSW2_8

DSW2_7

DSW2_6

DSW2_5

DSW2_4

DSW2_3

DSW2_2

DSW2_1

TP50

D

R90 100

R89 100

R88 100

R87 100

VD33

U12

XRSTPW2

RMCK

123456789

R1R2R3R4R5R6R7

COM

R86 100

R85 100

R84 100

R83 100

D8

D7

D6

D5

43

DD

V

OUT

8

7

6

5

4

3

2

1

M9-1-103J

D4

D3

D2

D1

C76

12

D

D

0.1µ

INHXGND

ON

A6E-8104

TLR124

STA_8

TLR124

STA_7

TLO124

STA_6

TLO124

STA_5

VD25B

D

FXO-31FL_22.5792MHz

D

9

10

11

12

13

14

15

16

S2

VD25B

TLY124

Fs_0

TLY124

Fs_1

TLG124A

CHNM_BL

TLG124A

FULL/HALF

CXD4016R EVB࿁〝࿑ PLD

VD33

R4

5

R3

4

R2

3

R1

2

COM

1

RA3

M5-1-102J

VD33

VPP

TMS

19

V

CC

20

TDO

1

DATA

2

TCK

3

DCLK

45678

U11

C65

0.1µ

C67

0.1µ

D

XRSTPW1

DSW2_8

104

I_O

103

DSW2_7

102

I_O

101

DSW2_6

100

I_O

99

V

98

DSW2_5

97

DSW2_4

96

I_O

95

DSW2_3

94

I_O

93

DSW2_2

92

V

91

DSW2_1

90

I_O

89

LED8

88

LED7

87

I_O

86

LED6

85

V

84

LED5

83

GND

82

GND_CLK

81

Ded_Input

80

GlobalCLK1

79

Ded_Input

78

V

77

GND

76

GL_CLK1

75

I_O

74

CRYST22M

73

V

72

RMCK

71

DSW1_8

70

DSW1_7

69

DSW1_6

68

DSW1_5

67

V

66

DSW1_4

65

I_O

64

DSW1_3

63

LOCK

62

DSW1_2

61

DSW1_1

60

GND

59

LED4

58

LED3

57

LED2

56

LED1

55

I_O

54

I_O

53

TH12

VD33

TH

TH

TH14

R82

LED4

LED3

LED2

LED1

TH

TH15THTH13

105

106

107

108

109

INT

GND

CC

MSEL1

MSEL0

V

nCONFIG

CC

IO

CC

INT

CC

IO

CC

_CKLK

CC

INT

CC

IO

INT

CC

V

GND

TMS

TRST

nSTATUS

J3

10

DDDDD

D

COM

R1

R2

R3

R4

R5

R6

R7

R8

RA1

M9-1-103J

VD33

VD33

C52

0.1µ

C51

0.1µ

C50

0.1µ

C49

0.1µ

TP44L

TP43

TP42

TP41

C-2S-Y

SDTO1

LC-2S-BL

LRCK_AD

LC-2S-Y

MCLK

LC-2S-G

SCLK_AD

VD25B

R1R2R3R4R5R6R7

123456789

COM

8

7

6

5

4

3

2

1

D

M9-1-103J

ON

S1

A6E-8104

9

10

11

12

13

14

15

16

VD25B

C64

0.1µ

C66

AUDIO

0.1µ

TH

TH11

U

C

ORIG

C53

1

1

1

1

0.1µ

100

R67

SDTO_1

TH7

22

R69

MCLK

LRCK_AD

TH

R70 100

SCLK_AD

C56

0.1µ

C58

0.1µ

R73 100

PDN

COPY

R75 100

EMPH

C60

0.1µ

C62

0.1µ

1

TH

TH

TH8

100

OSCLK

LC-2S-Y

TP49

TH10

1

R77

OLRCK

LC-2S-G

TP48

1

SDOUT

LC-2S-BL

TP47

RST

CHS

PRO

RCBL

RERR

NVERR

OSCLK

OLRCK

SDOUT

DSW2_8

DSW2_7

DSW2_6

DSW2_5

DSW2_4

DSW2_3

DSW2_2

DSW2_1

R8

RA4

- 24 -

CXD4016R

A2.5V_P

D1

1S15881

D10

1S1588

VA25P

RM3

L6

TP56

LC-2S-O

VD25D

RM2

L5

D2.5V_D

TP55

LC-2S-G

LM317A

0

SN3-200

1

2

VOUT

VIN

U15 LM317A

3

0

SN3-200

1

2

VOUT

VIN

U14

3

C88

C87

0.1µ

D14

1S1588

R94

ADJ

C86

47µ/16V

C85

0.1µ

D13

R93

240

ADJ

47µ/16V

C94

0.1µ

C93

240

1

C92

0.1µ

C91

1S1588

1

A A

47µ/16V

3

D D

47µ/16V

C97

R97

VR4

2

C96

R96

VR3

2

A A

10µ/16V

A

270

500

R103

270

1

R100

750

D D

10µ/16V

A

270

R102

270

500

13

R99

750

VA25A

RM6

0

C103

47µ/16V

A A

C102

0.1µ

L9

SN3-200

1

C109

2

3

VOUT

VIN

D20

R106

ADJ

1S1588

240

1

0.1µ

C108

47µ/16V

3

C112

R108

VR7

2

A A

10µ/16V

270

500

1

R110

A

R114

270

750

A A

A2.5V_A

TP59

LC-2S-O

D17

1S1588

U18 LM317A

A A

VA25D

RM5

0

C101

47µ/16V

A A

C100

0.1µ

L8

SN3-200

1

C107

2

3

VOUT

VIN

D19

R105

ADJ

C106

1S1588

240

1

0.1µ

47µ/16V

3

C111

R107

VR6

2

A A

10µ/16V

270

500

1

R109

A

R113

270

750

A A

CXD4016R EVB࿁〝࿑ POWER

A2.5V_D

TP58

LC-2S-O

D16

1S1588

U17 LM317A

A A

TP51

LC-2S-R

+5V

1

VD5

L2

SN3-200

C80

47µ/16V

C79

0.1µ

C78

0.1µ

C77

22µ/16V

J5

VA5

D D

L3

1

2

SN3-200

JP1

A D

IL-2P-S3EN2

C82

C81

47µ/16V

0.1µ

TP53

LC-2S-BK

TP52

LC-2S-BK

AA

AGND

AGND

D15

VD33

D3.3V

TP57

1S1588

RM4

0

L7

SN3-200

1

LC-2S-R

2

U16 LM317A

3

VOUT

VIN

C99

C98

D18

R104

ADJ

47µ/16V

0.1µ

C105

C104

1S1588

240

1

D D

0.1µ

47µ/16V

3

C110

VR5

2

D D

10µ/16V

50

1

R112

100

R111

270

A

A

VD25B

RM1

0

C84

47µ/16V

D D

C83

0.1µ

L4

SN3-200

1

C90

2

3

VOUT

VIN

D12

R92

ADJ

C89

1S1588

240

1

0.1µ

47µ/16V

D D

C95

10µ/16V

R95

270

VR2

500

13

2

R98

750

A

R101

270

AA

D2.5V_B

TP54

LC-2S-G

AA

1

D9

1S1588

1

U13 LM317A

- 25 -

TP61

LC-2S-Y

XRSTPW2

R117

10k

C114

0.1µ

8

CC

V

VsSENSE

Vref

RESINCtGND

U20

123

1

D

567

RESET

RESET

4

R119

10k

TL7705CP

C119

0.1µ

CXD4016R

D

TP60

LC-2S-Y

1

XRSTPW1

VD5VD5 VD5 VD5 VD5

C113

0.1µ

U19

R116

10k

8

CC

V

Vref

123

VD25B

C115

0.1µ

D

567

RESET

RESET

VsSENSE

RESINCtGND

4

C118

4.7µ/16V T

CC

G2

V

G1A1A2A3A4A5A6A7A8

U21

123456789

R118

10k

TL7705CP

XRSTPW1

td = 60ms

121314151617181920

D

XRSTPW2

Y7Y6Y5Y4Y3Y2Y1

GND Y8

TC74LCX541F

10 11

D

CXD4016R EVB࿁〝࿑ RESET

R115

10k

SW1

AB-15AH

C117

0.1µ

3

2

1

- 26 -

C116

4.7µ/16V T

td = 60ms

TP62

LC-2S-BK

AGND

2

1

J6

IL-2P-S3EN2

Emitter Voltage Source

C120

0.1µ

A

1

A

L10

A

J7

68µH

(Large Size)

TP63

LC-2S-Y

TX_LED

2

F-CONNECTOR

NF-R-2

1

C123

0.1µ

1

CXD4016R

RF OUT

A

J8

SMB

R124

75

A

C121

2

VR8

10k

1

3

3p

C122

3p

R120

1k

VA5

5

CC

V

EE

V

AD8057ART

IN+ IN–

U22

OUT

1234

A

VA5

C124

R121

0.1µ

2.2k

C125

2200p

C126

2200p

R123

A A

R125

2.2k

CXD4016R EVB࿁〝࿑ RFOUT

2

VR9

10k

13

0

C130

10p

TP64

LC-2S-BK

- 27 -

AGND

C129

120p

L12

12µH

A

L11

1

6.8µH

R122

300

C128

120p

C127

27p

A A A A A

A

DAAOUT

パターン図

CXD4016R

CXD4016R EVB A面パターン図

CXD4016R EVB B面パターン図

- 28 -

CXD4016R

CXD4016R EVB GND層パターン図

CXD4016R EVB 電源層パターン図

- 29 -

CXD4016R

CXD4016R EVB A面シルク図

CXD4016R EVB B面シルク図

- 30 -

CXD4016R

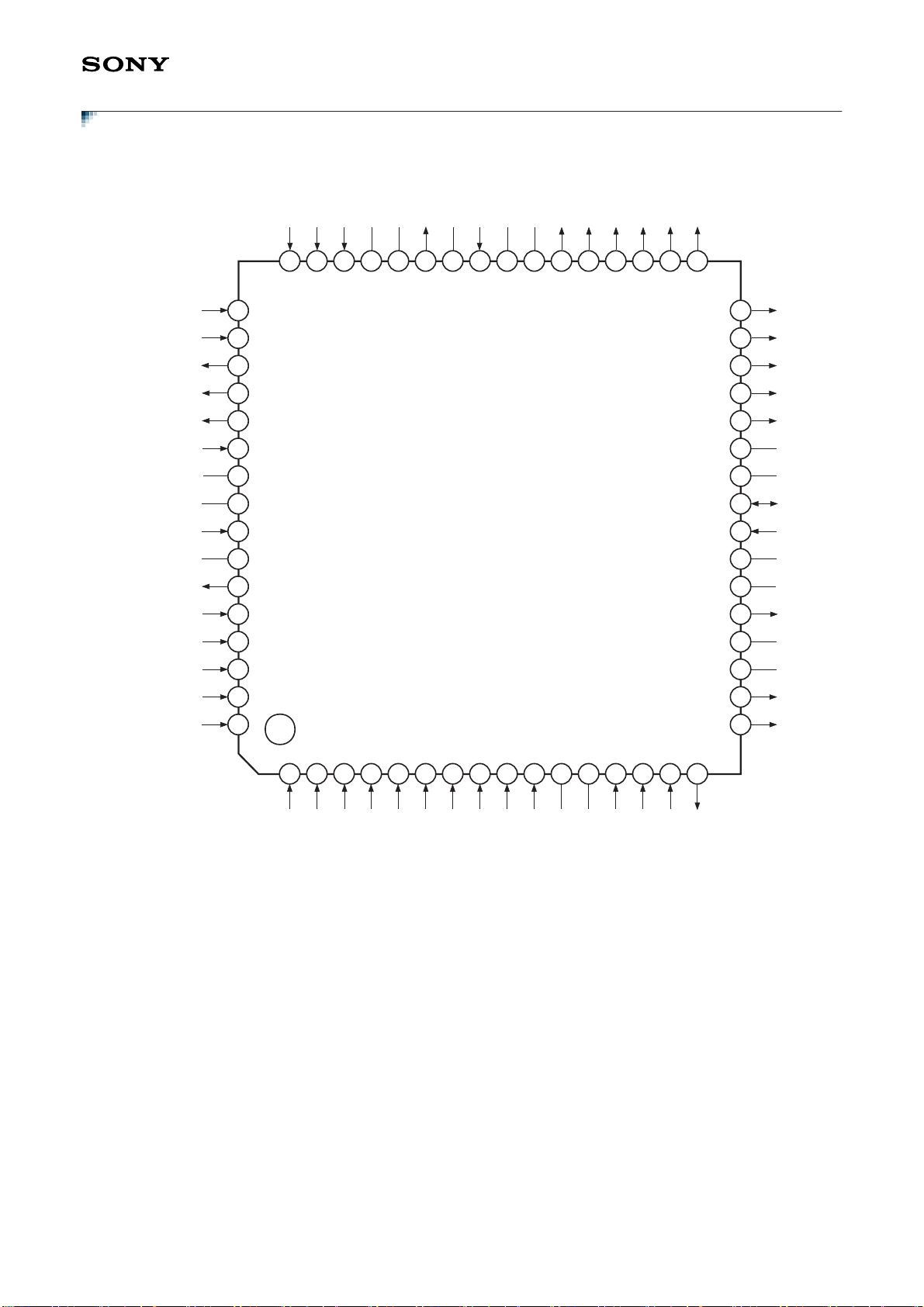

外形寸法図

(単位 : mm)

64PIN LQFP (PLASTIC)

12.0 ± 0.2

+ 0.2

1.5 – 0.1

A

49

64

48

10.0 ± 0.1

33

32

17

116

0° to 8°

SONY CODE

JEITA CODE

JEDEC CODE

0.5

DETAIL A

P-LQFP64-10X10-0.5

0.25

0.1 ± 0.1

0.6 ± 0.15

0.5 ± 0.2

LQFP-64P-L023

b

0.08

M

0.08

S

S

0.20 ± 0.05

0.145 ± 0.055

DETAIL B

PACKAGE STRUCTURE

PACKAGE MATERIAL

TERMINAL TREATMENT

TERMINAL MATERIAL

PACKAGE MASS

EPOXY RESIN

SOLDER PLATING

42 ALLOY

0.32g

- 31 -

LEAD PLATING SPECIFICATIONS

ITEM

SPEC.

LEAD MATERIAL 42 ALLOY

SOLDER COMPOSITION Sn-2%Bi

PLATING THICKNESS 5-20µm

Sony Corporation

Loading...

Loading...