5-1

FAST AND LS TTL DATA

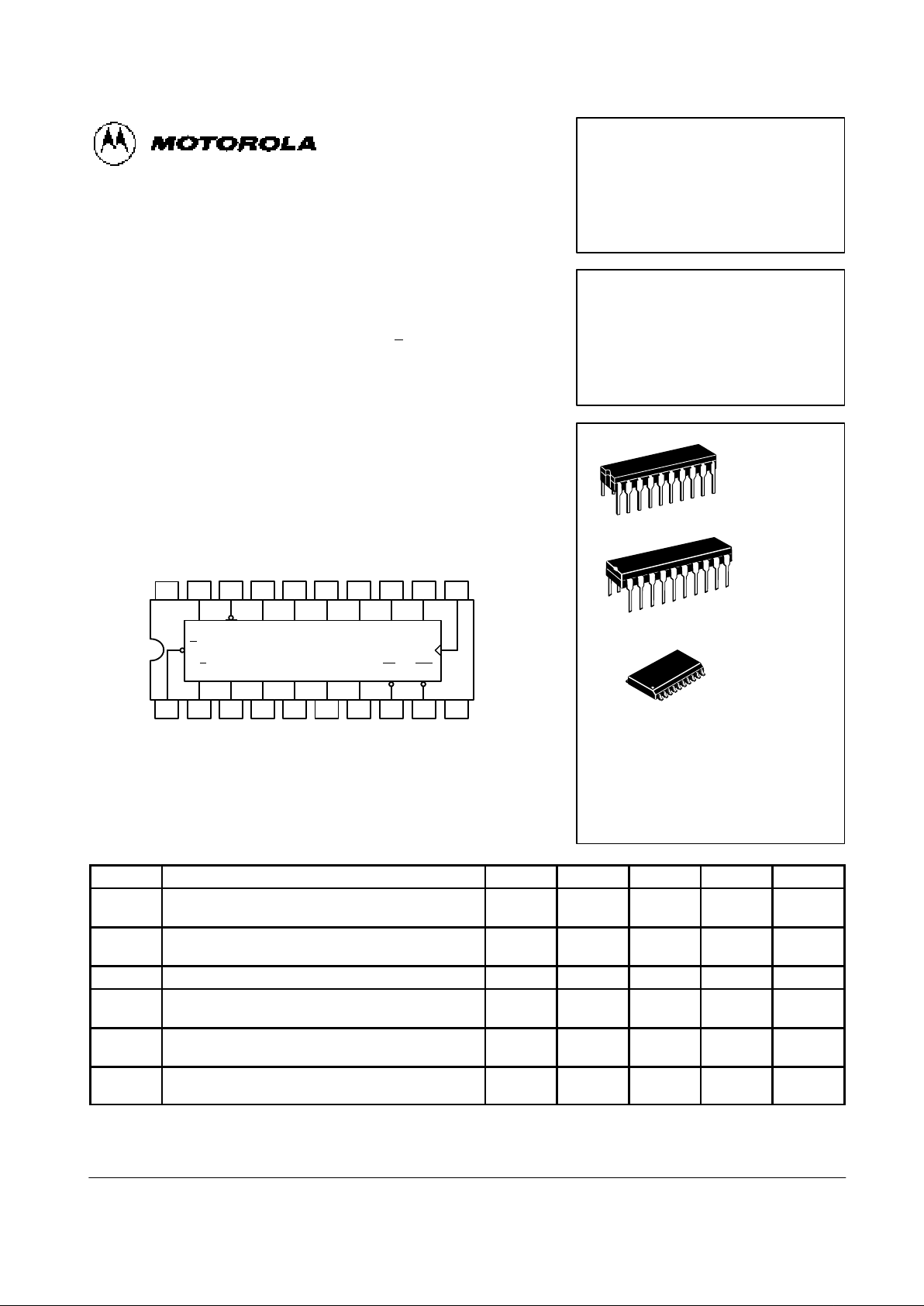

8-BIT SHIFT REGISTERS

WITH SIGN EXTEND

These 8-bit shift registers have multiplexed input/output data ports to

accomplish full 8-bit data handling in a single 20-pin package. Serial data may

enter the shift-right register through either D0 or D1 inputs as selected by the

data select pin. A serial output is also provided. Synchronous parallel loading

is achieved by taking the register enable and the S/P

inputs low. This places

the three-state input/output ports in the data input mode. Data is entered on

the low-to-high clock transition. The data extend function repeats the sign in

the QA flip-flop during shifting. An overriding clear input clears the internal

registers when taken low whether the outputs are enabled or off. The output

enable does not affect synchronous operation of the register.

• Multiplexed Inputs/Outputs Provide Improved Bit Density

• Sign Extend Function

• Direct Overriding Clear

• 3-State Outputs Drive Bus Lines Directly

V

CC

DATA

SELECT

SIGN

EXTEND

D1 B/QBD/QDF/QFH/QHQ/HCLOCK

D0 A/QAC/QCE/QEG/Q

G

S/P

REGISTER

ENABLE

OUTPUT

ENABLE

CLEAR GND

(TOP VIEW)

18 17 16 15 14 13

1 2 3 4 5 6 7

20

19

8 9 10

12 11

DS SE D1 B/QBD/QDF/QFH/GHQ/

H

G

CK

S/P D0 A/QAC/QCE/QEG/QGOE CLR

GUARANTEED OPERATING RANGES

Symbol Parameter Min Typ Max Unit

V

CC

Supply Voltage 54

74

4.5

4.75

5.0

5.0

5.5

5.25

V

T

A

Operating Ambient Temperature Range 54

74

–55

0

25

25

125

70

°C

I

OH

Output Current — High QH′ 54, 74 –0.4 mA

I

OL

Output Current — Low QH′

QH′

54

74

4.0

8.0

mA

I

OH

Output Current — High QA–Q

H

QA–Q

H

54

74

–1.0

–2.6

mA

I

OL

Output Current — Low QA–Q

H

QA–Q

H

54

74

12

24

mA

SN54/74LS322A

8-BIT SHIFT REGISTERS

WITH SIGN EXTEND

LOW POWER SCHOTTKY

ORDERING INFORMATION

SN54LSXXXJ Ceramic

SN74LSXXXN Plastic

SN74LSXXXDW SOIC

20

1

J SUFFIX

CERAMIC

CASE 732-03

20

1

N SUFFIX

PLASTIC

CASE 738-03

20

1

DW SUFFIX

SOIC

CASE 751D-03

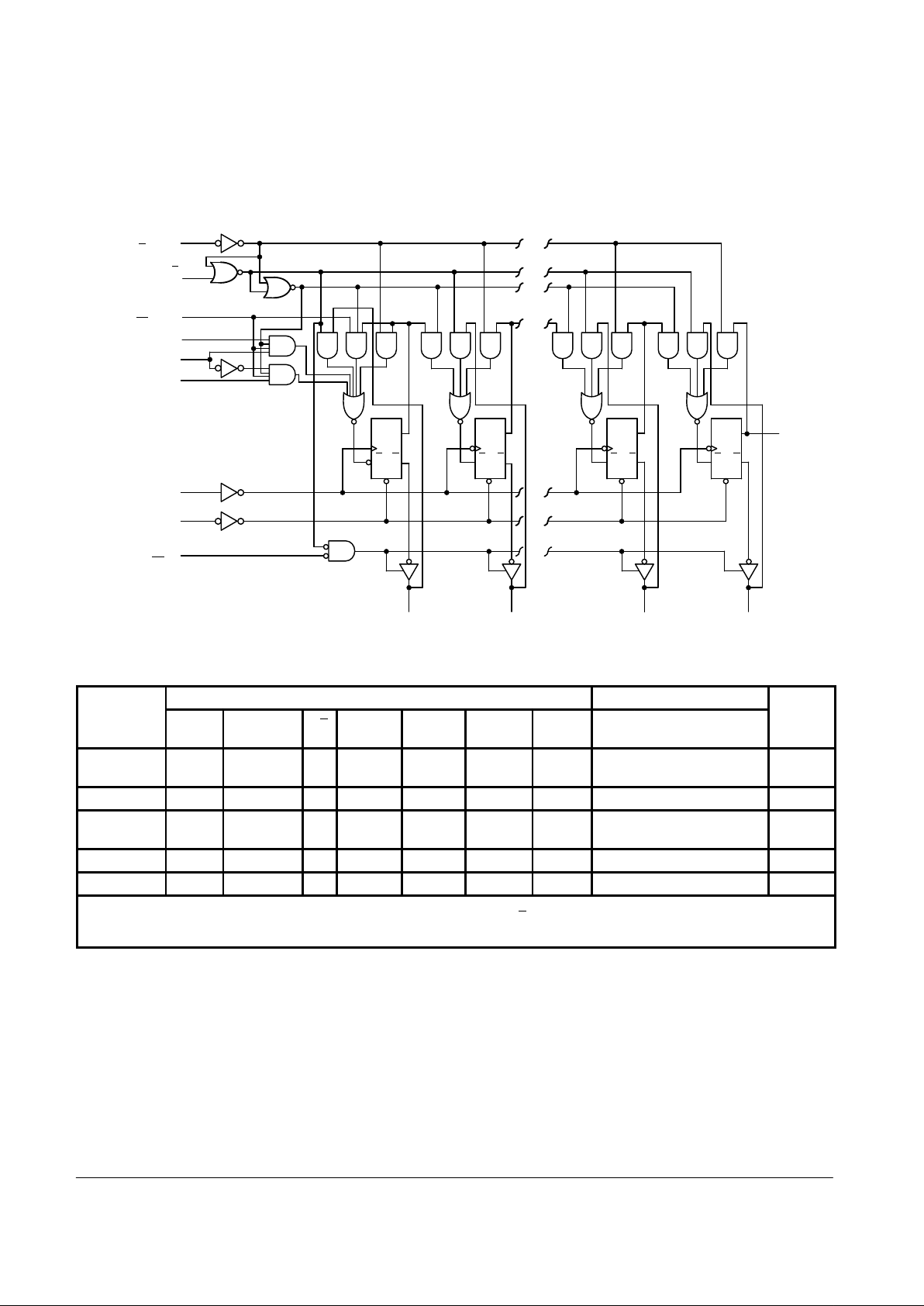

5-2

FAST AND LS TTL DATA

SN54/74LS322A

BLOCK DIAGRAM

REGISTER

ENABLE

G

S/P

SIGN

EXTEND

SE

D1

DATA

SELECT

DS

D0

CLOCK

CLEAR

OUTPUT

ENABLE

OE

(8)

(9)

(11)

(3)

(19)

(18)

(2)

(1)

(12)

(13)

(7)(16)

(4)

(17)

CK

D

Q

Q

CLR

CK

D

Q

Q

CLR

CK

D

Q

Q

CLR

CK

D

Q

Q

CLR

A/Q

A

B/Q

B

G/Q

G

H/Q

H

FOUR

IDENTICAL

CHANNELS

NOT

SHOWN

Q

H

FUNCTION TABLE

INPUTS INPUTS/OUTPUTS

OPERATION

CLEAR

REGISTER

ENABLE

S/P

SIGN

EXTEND

DATA

SELECT

OUTPUT

ENABLE

CLOCK A/QAB/QBC/QC H/Q

H

OUTPUT

QH′

Clear L H X X X L X L L L L L

L X H X X L X L L L L L

Hold H H X X X L X Q

A0QB0QC0QH0

Q

H0

H L H H L L ↑ D0Q

AnQBnQGn

Q

Gn

Shift Right

H L H H H L ↑ D1Q

AnQBnQGn

Q

Gn

Sign Extend H L H L X L ↑ Q

AnQAnQBnQGn

Q

Gn

Load H L L X X X ↑ a b c h h

When the output enable is high, the eight input/output terminals are disabled to the high-impedance state; however, sequential operation or

clearing of the register is not affected. If both the register enable input and the S/P

input are low while the clear input is low, the register is

cleared while the eight input/output terminals are disabled to the high-impedance state.

H = HIGH Level (steady state)

L = LOW Level (steady state)

X = Irrelevant (any input, including transitions)

↑ = Transition from LOW to HIGH level

Q

A0…QH0

= the level of QA through QH, respectively, before the indicated steady-state conditions were established

Q

An…QHn

= the level of QA through QH, respectively, before the most recent ↑ transition of the clock

D0, D1 = the level of steady-state inputs at inputs D0 and D1 respectively

a…h = the level of steady-state inputs at inputs A through H respectively

…

Loading...

Loading...