Samsung MZVLB256HAHQ-00000 User Manual

SAMSUNG CONFIDENTIAL

Rev. 1.1 Sep. 2017

MZVLB256HAHQ-00000/07

MZVLB512HAJQ-00000/07

MZVLB1T0HALR-00000/07

MZVLB2T0HMLB-00000/07

M.2 NVMe PCIe SSD specification

(PM981)

datasheet

SAMSUNG ELECTRONICS RESERVES THE RIGHT TO CHANGE PRODUCTS, INFORMATION AND

SPECIFICATIONS WITHOUT NOTICE.

Products and specifications discussed herein are for reference purposes only. All information discussed herein is provided on an "AS IS" basis, without warranties of any kind.

This document and all information discussed herein remain the sole and exclusive property of Samsung Electronics. No license of any patent, copyright, mask work, trademark or any other intellectual property right is granted by one party to the other party under this document, by implication, estoppel or otherwise.

Samsung products are not intended for use in life support, critical care, medical, safety equipment, or similar applications where product failure could result in loss of life or personal or physical harm, or any military or defense application, or any governmental procurement to which special terms or provisions may apply.

For updates or additional information about Samsung products, contact your nearest Samsung office.

All brand names, trademarks and registered trademarks belong to their respective owners.

2017 Samsung Electronics Co., Ltd. All rights reserved.

- 1 -

MZVLB256HAHQ-00000/07 |

|

|

|

SAMSUNG CONFIDENTIAL |

||||

MZVLB512HAJQ-00000/07 |

datasheet |

|

|

Rev. 1.1 |

||||

MZVLB2T0HMLB-00000/07 |

|

|

SSD |

|||||

MZVLB1T0HALR-00000/07 |

|

|

|

|

|

|

||

|

Revision History |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Revision No. |

|

History |

Draft Date |

Remark |

Created by |

Review by |

|

|

|

|

|

|

|

|

|

|

|

1.0 |

1. Initial issue |

|

Aug 07, 2017 |

Final |

K.W Shin |

|

|

|

|

|

|

|

|

|

|

|

|

1.1 |

1.Deleted 128GB and changed the part number of 256GB. |

Sep. 28, 2017 |

Final |

S.J Oh |

Elly. Shin |

|

|

|

|

|

|

|

|

|

|

|

IF THERE IS ANY OTHER OPERATION TO IMPLEMENT IN ADDITION TO SPECIFICATION

IN THE DATASHEET OR JEDEC STANDARD, PLEASE CONTACT EACH BRANCH OFFICE OR

HEADQUARTERS OF SAMSUNG ELECTRONICS.

- 2 -

MZVLB256HAHQ-00000/07 |

|

|

|

|

SAMSUNG CONFIDENTIAL |

||

MZVLB512HAJQ-00000/07 |

datasheet |

Rev. 1.1 |

|||||

MZVLB2T0HMLB-00000/07 |

SSD |

||||||

MZVLB1T0HALR-00000/07 |

|

|

|

|

|

|

|

|

PM981 Series |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PART NUMBER |

Capacity1) |

|

LBA2) |

|||

|

MZVLB256HAHQ-00000/07 |

256GB |

500,118,192 |

|

|||

|

MZVLB512HAJQ-00000/07 |

512GB |

1,000,215,216 |

|

|||

|

MZVLB1T0HALR-00000/07 |

1TB |

2,000,409,264 |

|

|||

|

MZVLB2T0HMLB-00000/07 |

2TB |

4,000,797,360 |

|

|||

|

|

|

|

|

|

|

|

|

FEATURES |

|

|

Environmental Specifications |

|

|

|

|

|

|

|

|

|

|

|

PCIe Gen3 8Gb/s Interface, up to 4 Lanes

Compliant with PCI Express Base Specification Rev. 3.0

Compliant with PCI Express M.2 Specification Rev. 1.1

Compliant with NVMe Express specification Rev. 1.2a

Power Saving Modes:

-Supporting APST

-Supporting L1.2 Mode

Support Admin & NVM Command Set

RoHS Compliant

Hardware based AES-XTS 256-bit Encryption Engine for SED

TCG OPAL (v2.0) Compliant for SED

Drive Configuration

Capacity |

256/512GB/1/2TB |

From Factor |

M.2 |

Interface |

PCI Express Gen3 x4 |

Bytes per Sector |

512Byte |

|

|

Performance Specifications 3) |

|

Data Transfer Rate (128KB) |

|

Sequential Read |

(1TB) Up to 3,200 MB/s |

|

(512GB) Up to 3,000 MB/s |

|

(256GB/2TB) Up to TBD MB/s |

Sequential Write |

(1TB) Up to 2,400 MB/s |

|

(512GB) Up to 1,800 MB/s |

|

(256GB/2TB) Up to TBD MB/s |

Data I/O Speed (4KB) |

|

Random Read |

(1TB) Up to 380K IOPS |

|

(512GB) Up to 270K IOPS |

|

(256GB/2TB) Up to TBD IOPS |

Random Write |

(1TB) Up to 440K IOPS |

|

(512GB) Up to 420K IOPS |

|

(256GB/2TB) Up to TBD IOPS |

|

|

Reliability Specifications |

|

|

|

Temperature |

|

Operating4 |

0°C to 70°C |

Non-operating |

-40°C to 85°C |

Humidity (non-condensing) |

|

Non-operating |

5 ~ 95% |

Linear Shock (0.5ms duration with 1/2 sine wave) |

|

Non-operating |

1,500 Gpeak |

Vibration |

|

Non-operating (20 ~ 2,000 Hz, Sinusoidal) |

20 Gpeak |

|

|

POWER SPECIFICATIONS7 |

|

Supply Voltage / Tolerance |

3.3V ± 5% |

Voltage Ripple/Noise (max.) |

100mV p-p |

Active5 (Typ, RMS) |

|

- Read |

5.9W |

- Write |

5.7W |

Idle6 (Typ.) |

30mW |

L1.2 (Typ) |

5mW |

|

|

PHYSICAL DIMENSION |

|

|

|

Width |

22.00 ± 0.15 mm |

Length |

80.00 ± 0.15 mm |

Height |

|

- Single Side |

Max. 2.38 mm |

Weight |

Max. 9.0g |

Specifications are subject to change without notice.

1)1MB = 1,000,000 Bytes, 1GB = 1,000,000,000 Bytes, Unformatted Capacity. User accessible capacity may vary depending on operating environment and formatting.

2)1 Sector = 512Bytes, Max. LBA represents the total user addressable sectors in LBA mode and calculated by IDEMA rule

3)Actual performance may vary depending on use conditions and environment. Performance measurements based on TurboWrite technology.

4)Measured by SMART Temperature. Proper airflow recommended.

UBER |

< 1 sector per 1015 bits read |

5) |

Active power is measured on sequential write and read. |

|

6) |

Idle Power is measured on Idle status with L1.2+APST/ASPM on. |

|||

|

|

|||

MTBF |

1.5 Million Hours |

7) |

Active/Idle/L1.2 Power are measured up to 1TB. |

IF THERE IS ANY OTHER OPERATION TO IMPLEMENT IN ADDITION TO SPECIFICATION

IN THE DATASHEET OR JEDEC STANDARD, PLEASE CONTACT EACH BRANCH OFFICE OR HEADQUARTERS OF SAMSUNG ELECTRONICS.

- 3 -

MZVLB256HAHQ-00000/07 |

|

SAMSUNG CONFIDENTIAL |

|

MZVLB512HAJQ-00000/07 |

|

Rev. 1.1 |

|

MZVLB2T0HMLB-00000/07 |

datasheet |

SSD |

|

MZVLB1T0HALR-00000/07 |

|

|

|

Table Of Contents |

|

|

|

1.0 INTRODUCTION ........................................................................................................................................................ |

|

5 |

|

1.1 |

General Description................................................................................................................................................ |

|

5 |

1.2 |

Product List.............................................................................................................................................................. |

|

5 |

1.3 |

Ordering Information................................................................................................................................................ |

|

5 |

2.0 PRODUCT SPECIFICATION...................................................................................................................................... |

|

6 |

|

2.1 |

Capacity................................................................................................................................................................... |

|

6 |

2.2 |

Performance1).......................................................................................................................................................... |

|

6 |

2.3 |

Power ...................................................................................................................................................................... |

|

6 |

2.4 |

Reliability ................................................................................................................................................................. |

|

7 |

2.4.1 MTBF ................................................................................................................................................................ |

|

7 |

|

2.4.2 UBER ................................................................................................................................................................ |

|

7 |

|

2.5 |

Environmental Specification .................................................................................................................................... |

|

7 |

3.0 MECHANICAL SPECIFICATION............................................................................................................................... |

|

8 |

|

3.1 |

Physical dimensions and Weight............................................................................................................................. |

|

8 |

3.2 |

Form Factor ............................................................................................................................................................. |

|

8 |

4.0 INTERFACE SPECIFACION ...................................................................................................................................... |

|

9 |

|

4.1 |

Connector Dimension and Pin Location .................................................................................................................. |

|

9 |

4.2 |

Pin Assignments and Definition............................................................................................................................... |

|

9 |

5.0 PCI and NVM Express registers ................................................................................................................................. |

|

11 |

|

5.1 |

PCI Express Registers ............................................................................................................................................ |

|

11 |

5.1.1 PCI Register Summary ..................................................................................................................................... |

|

11 |

|

5.1.2 PCI Configuration Header Space Registers Detail ........................................................................................... |

11 |

||

|

5.1.2.1 PCI Configuration Header Space Registers ............................................................................................... |

11 |

|

5.1.3 PCI Capability Registers Detail ......................................................................................................................... |

|

14 |

|

|

5.1.3.1 PCI Power Management Capability |

............................................................................................................ |

14 |

|

5.1.3.2 Message Signaled Interrupt (MSI) Capability ............................................................................................. |

15 |

|

|

5.1.3.3 PCI Express Capability ............................................................................................................................... |

|

17 |

|

5.1.3.4 MSI-X Capability ......................................................................................................................................... |

|

21 |

5.1.4 PCI Extended Capability Details ....................................................................................................................... |

|

22 |

|

|

5.1.4.1 Advanced Error Reporting Registers .......................................................................................................... |

22 |

|

|

5.1.4.2 Device Serial Number Capability ................................................................................................................ |

|

25 |

|

5.1.4.3 Power Budgeting Capability........................................................................................................................ |

|

26 |

|

5.1.4.4 Secondary PCI Express Capability............................................................................................................. |

|

27 |

|

5.1.4.5 Latency Tolerance Reporting Capability Registers....................................................................... |

.............. 28 |

|

|

5.1.4.6 L1 Substates Extended Capability.............................................................................................................. |

|

29 |

5.2 |

NVM Express Registers .......................................................................................................................................... |

|

30 |

5.2.1 Register Summary ............................................................................................................................................ |

|

30 |

|

5.2.2 Controller Registers .......................................................................................................................................... |

|

30 |

|

6.0 Supported Command Set ........................................................................................................................................... |

|

34 |

|

6.1 Admin Command Set .............................................................................................................................................. |

|

34 |

|

6.1.1 Identify Command ............................................................................................................................................. |

|

35 |

|

6.2 NVM Express I/O Command Set............................................................................................................................. |

|

41 |

|

6.3 |

SMART/Health Information...................................................................................................................................... |

|

42 |

7.0 PRODUCT COMPLIANCE ......................................................................................................................................... |

|

43 |

|

7.1 |

Product regulatory compliance and Certifications ................................................................................................... |

43 |

|

8.0 References.................................................................................................................................................................. |

|

44 |

|

IF THERE IS ANY OTHER OPERATION TO IMPLEMENT IN ADDITION TO SPECIFICATION

IN THE DATASHEET OR JEDEC STANDARD, PLEASE CONTACT EACH BRANCH OFFICE OR

HEADQUARTERS OF SAMSUNG ELECTRONICS.

- 4 -

MZVLB256HAHQ-00000/07 |

|

SAMSUNG CONFIDENTIAL |

MZVLB512HAJQ-00000/07 |

datasheet |

Rev. 1.1 |

MZVLB1T0HALR-00000/07 |

SSD |

|

MZVLB2T0HMLB-00000/07 |

1.0INTRODUCTION

1.1General Description

This document describes the specification of PM981 SSD which uses PCIe interface.

The PM981 is fully consist of semiconductor device and using NAND Flash Memory which has a high reliability and a high technology in a small form factor for using a SSD and supporting Peripheral Component Interconnect Express (PCIe) 3.0 interface standard up to 4 lanes shows much faster performance than previous SATA SSDs.

The PM981 provides 256GB, 512GB, 1TB and 2TB capacities. It’s sequential performance is up to 3,200MB/s for read operation and 2,400MB/s for write operation by 4 lanes. It’s random performance is up to 380k IOPS for read and 440k IOPS for write operation by 4 lanes. It could also provide rugged features with an extreme environment with a high MTBF.

1.2 Product List

[Table 1] Product Line-up

Type |

Capacity |

Part Number |

|

|

256GB |

MZVLB256HAHQ-00000/07 |

|

|

|

|

|

M.2 |

512GB |

MZVLB512HAJQ-00000/07 |

|

|

|

||

1TB |

MZVLB1T0HALR-00000/07 |

||

|

|||

|

|

|

|

|

2TB |

MZVLB2T0HMLB-00000/07 |

|

|

|

|

1.3 Ordering Information

M Z X X X X X X X X X X - X X X X X

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

11 |

12 |

13 |

14 |

15 |

16 |

17 |

18 |

1. Memory (M) |

|

|

|

|

|

|

|

|

10. Flash Generation |

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

M: 1st Generation |

|

|

|

|

|||

2. Module Classification |

|

|

|

|

|

|

|

|

|

A: 2nd Generation |

|

|

|

|

|||

Z: SSD |

|

|

|

|

|

|

|

|

11~12. NAND Density |

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

3. Form Factor |

|

|

|

|

|

|

|

|

|

HQ: 1T QDP 4CE |

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

JQ: 2T ODP 4CE |

|

|

|

|

||||

V: PCIeM.2 (22*80, PCIe x4) |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

LR: 4T HDP 4CE |

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

4. Line-Up |

|

|

|

|

|

|

|

|

|

LB: 8T HDP 4CE |

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

L: Client/SV (VNAND 3bit MLC) |

|

|

|

|

|

|

|

|

13. "-" |

|

|

|

|

|

|

|

|

5. SSD CTRL |

|

|

|

|

|

|

|

|

14. Default |

|

|

|

|

|

|

||

B: Phoenix |

|

|

|

|

|

|

|

|

|

"0" |

|

|

|

|

|

|

|

6~8. SSD Density |

|

|

|

|

|

|

|

|

15. HW revision |

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

0: No revision |

|

|

|

|

|

|||

256: 256GB |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

512: 512GB |

|

|

|

|

|

|

|

|

16. Packaging type |

|

|

|

|

||||

1T0: 1TB |

|

|

|

|

|

|

|

|

|

0: Bulk |

|

|

|

|

|

|

|

2T0: 2TB |

|

|

|

|

|

|

|

|

17~18. Customer |

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

9. NAND PKG + NAND Voltage |

|

|

|

|

|

|

|

|

|

00: World wide (non-SED) |

|

|

|||||

H: BGA (LF,HF) |

|

|

|

|

|

|

|

|

|

07: World wide (SED) |

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IF THERE IS ANY OTHER OPERATION TO IMPLEMENT IN ADDITION TO SPECIFICATION

IN THE DATASHEET OR JEDEC STANDARD, PLEASE CONTACT EACH BRANCH OFFICE OR

HEADQUARTERS OF SAMSUNG ELECTRONICS.

- 5 -

MZVLB256HAHQ-00000/07 |

|

SAMSUNG CONFIDENTIAL |

MZVLB512HAJQ-00000/07 |

datasheet |

Rev. 1.1 |

MZVLB1T0HALR-00000/07 |

SSD |

|

MZVLB2T0HMLB-00000/07 |

2.0PRODUCT SPECIFICATION

2.1Capacity

[Table 2] User Addressable Sectors

Capacity |

Max LBA |

256GB1) |

500,118,192 |

512GB1) |

1,000,215,216 |

1TB |

2,000,409,264 |

|

|

2TB |

4,000,797,360 |

|

|

NOTE:

1)Gigabyte (GB) = 1,000,000,000 Bytes, 1 Sector = 512Bytes

2)Max. LBA shown in Table 1 represents the total user addressable sectors in LBA mode and calculated by IDEMA rule.

2.2 Performance1)

[Table 3] Drive Performance

Gen3

Parameter |

Unit |

Queue Depth |

256GB |

512GB |

1TB |

2TB |

|

Sequential Read2) |

MB/s |

QD = 32 |

TBD |

3,000 |

3,200 |

TBD |

|

(Up to) |

|||||||

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

Sequential Write2) |

MB/s |

QD = 32 |

TBD |

1,800 |

2,400 |

TBD |

|

(Up to) |

|||||||

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

Random Read3) |

IOPS |

QD = 1 |

TBD |

12K |

12K |

TBD |

|

(Up to) |

IOPS |

QD = 32 |

TBD |

270K |

380K |

TBD |

|

|

|

|

|

|

|

|

|

Random Write3) |

IOPS |

QD = 1 |

TBD |

50K |

50K |

TBD |

|

(Up to) |

IOPS |

QD = 32 |

TBD |

420K |

440K |

TBD |

|

|

|

|

|

|

|

|

NOTE:

1)Performance measured using CDM 5.0.2 on Windows 10 64bit. Actual performance may vary depending on use conditions and environment.

2)Sequential performance measured using 128KB data size. (QD=32 by Thread=1)

3)Random performance measured using 4KB data size. (QD=32 by Thread 4, QD=1 by Thread 1)

4)Performance measurements based on TurboWrite technology

2.3 Power

[Table 4] Maximum Ratings

|

Parameter |

|

|

|

Specifications |

|

||

Supply Voltage |

|

Allowable voltage |

|

3.3V ± 5% |

|

|||

|

|

|

|

|

|

|

||

|

Allowable noise/ripple |

|

100mV p-p or less |

|

||||

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

[Table 5] Power Consumption for M.2 (3.3V Supply) |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

Parameter |

|

|

Specifications |

|

||

|

|

Active1 |

(Typical, RMS) |

|

Read |

|

5.9W |

|

|

|

|

|

|

|

|

||

Power Consumption4 |

|

|

Write |

|

5.7W |

|

||

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

||

|

|

Idle2 (Typical) |

|

|

30mW |

|

||

|

|

|

|

|

|

|||

|

|

|

L1.23 (Typical) |

|

|

5mW |

|

|

NOTE:

1)Active power is measured on sequential write and read.

2)Idle Power is measured on Idle status with L1.2+APST/ASPM on.

3)If L1.2 time logging option is enabled, L1.2 Power could be 5mW.

4)Active/Idle/L1.2 Power are measured up to 1TB.

IF THERE IS ANY OTHER OPERATION TO IMPLEMENT IN ADDITION TO SPECIFICATION

IN THE DATASHEET OR JEDEC STANDARD, PLEASE CONTACT EACH BRANCH OFFICE OR

HEADQUARTERS OF SAMSUNG ELECTRONICS.

- 6 -

MZVLB256HAHQ-00000/07 |

|

SAMSUNG CONFIDENTIAL |

MZVLB512HAJQ-00000/07 |

datasheet |

Rev. 1.1 |

MZVLB1T0HALR-00000/07 |

SSD |

|

MZVLB2T0HMLB-00000/07 |

2.4 Reliability

This chapter provides the information for the reliability features of the SSD.

2.4.1 MTBF

MTBF is Mean Time Between Failure, and is the predicted elapsed time between inherent failures of a system during operation. As same word, AFR (annual failure ratio) is 0.4%. MTBF can be calculated as the arithmetic average time between failures of a system.

[Table 6] MTBF Specifications

Capacity |

MTBF |

|

256GB |

|

|

|

|

|

512GB |

1,500,000 Hours |

|

|

||

1TB |

||

|

||

|

|

|

2TB |

|

|

|

|

2.4.2 UBER

UBER is Uncorrectable Bit Error Rate.

[Table 7] UBER Specifications

Parameter |

Specification |

UBER |

< 1 sector per 1015 bits read |

2.5 Environmental Specification

[Table 8] Temperature, Humidity, Shock, Vibration

Parameter |

Mode |

Specification |

|

Temperature |

Operating1) |

0 C to 70 C |

|

Non-operating |

-40 C to 85 C |

||

|

|||

|

|

|

|

Humidity2) |

Non-operating |

5% to 95% |

|

Shock3) |

Non-operating |

1500G |

|

Vibration4) |

Non-operating |

20G |

NOTE:

1)Temperature is measured by SMART Temperature. Proper airflow recommended

2)Humidity is measured in non-condensing

3)Test condition for shock: 0.5ms duration with half sine wave

4)Test condition for vibration: 10Hz to 2000Hz

IF THERE IS ANY OTHER OPERATION TO IMPLEMENT IN ADDITION TO SPECIFICATION

IN THE DATASHEET OR JEDEC STANDARD, PLEASE CONTACT EACH BRANCH OFFICE OR

HEADQUARTERS OF SAMSUNG ELECTRONICS.

- 7 -

MZVLB256HAHQ-00000/07 |

|

SAMSUNG CONFIDENTIAL |

MZVLB512HAJQ-00000/07 |

datasheet |

Rev. 1.1 |

MZVLB1T0HALR-00000/07 |

SSD |

|

MZVLB2T0HMLB-00000/07 |

3.0MECHANICAL SPECIFICATION

3.1Physical dimensions and Weight

[Table 9] Physical dimensions and Weight

|

Parameter |

Value |

|

|

Width |

22.00 ± 0.15 mm |

|

|

|

|

|

|

Length |

80.00 ± 0.15 mm |

|

|

|

|

|

|

Thickness |

Max. 2.38 mm |

|

|

|

|

|

Weight |

|

256/512GB/1/2TB |

Max 9.0g |

|

|

|

|

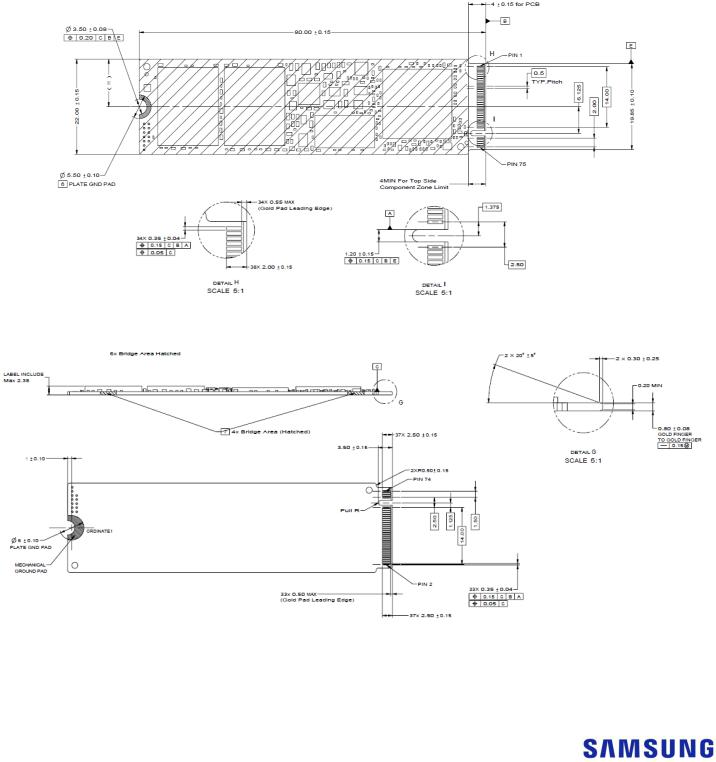

3.2 Form Factor

[Figure 1] M.2 Package

IF THERE IS ANY OTHER OPERATION TO IMPLEMENT IN ADDITION TO SPECIFICATION

IN THE DATASHEET OR JEDEC STANDARD, PLEASE CONTACT EACH BRANCH OFFICE OR

HEADQUARTERS OF SAMSUNG ELECTRONICS.

- 8 -

MZVLB256HAHQ-00000/07 |

|

SAMSUNG CONFIDENTIAL |

MZVLB512HAJQ-00000/07 |

datasheet |

Rev. 1.1 |

MZVLB1T0HALR-00000/07 |

SSD |

|

MZVLB2T0HMLB-00000/07 |

4.0INTERFACE SPECIFACION

4.1Connector Dimension and Pin Location

[TOP VIEW] |

[BOTTOM VIEW] |

[Figure 2] M.2 Signal and Power pins

4.2 Pin Assignments and Definition

[Table 10] Signal Assignments

Pin# |

Assignment |

Description |

Pin# |

Assignment |

Description |

|

1 |

GND |

Return current path |

2 |

3.3V |

3.3V source |

|

|

|

|

|

|

|

|

3 |

GND |

Return current path |

4 |

3.3V |

3.3V source |

|

|

|

|

|

|

|

|

5 |

PETn3 |

PCIe TX |

6 |

N/C |

N/C |

|

|

|

|

|

|

|

|

7 |

PETp3 |

PCIe TX |

8 |

N/C |

N/C |

|

|

|

|

|

|

|

|

9 |

GND |

Return current path |

10 |

LED1# |

Device Active Signal (Refer to [Table 11]) |

|

|

|

|

|

|

|

|

11 |

PERn3 |

PCIe Rx |

12 |

3.3V |

3.3V source |

|

|

|

|

|

|

|

|

13 |

PERp3 |

PCIe Rx |

14 |

3.3V |

3.3V source |

|

|

|

|

|

|

|

|

15 |

GND |

Return current path |

16 |

3.3V |

3.3V source |

|

|

|

|

|

|

|

|

17 |

PETn2 |

PCIe TX |

18 |

3.3V |

3.3V source |

|

|

|

|

|

|

|

|

19 |

PETp2 |

PCIe TX |

20 |

N/C |

N/C |

|

|

|

|

|

|

|

|

21 |

GND |

Return current path |

22 |

N/C |

N/C |

|

|

|

|

|

|

|

|

23 |

PERn2 |

PCIe Rx |

24 |

N/C |

N/C |

|

|

|

|

|

|

|

|

25 |

PERp2 |

PCIe Rx |

26 |

N/C |

N/C |

|

|

|

|

|

|

|

|

27 |

GND |

Return current path |

28 |

N/C |

N/C |

|

|

|

|

|

|

|

|

29 |

PETn1 |

PCIe TX |

30 |

N/C |

N/C |

|

|

|

|

|

|

|

|

31 |

PETp1 |

PCIe TX |

32 |

N/C |

N/C |

|

|

|

|

|

|

|

|

33 |

GND |

Return current path |

34 |

N/C |

N/C |

|

|

|

|

|

|

|

|

35 |

PERn1 |

PCIe Rx |

36 |

N/C |

N/C |

|

|

|

|

|

|

|

|

37 |

PERp1 |

PCIe Rx |

38 |

N/C |

N/C |

|

|

|

|

|

|

|

|

39 |

GND |

Return current path |

40 |

ALTER#(O)1) |

DNU (Do Not Use) |

|

41 |

PETn0 |

PCIe TX |

42 |

SMB_DATA (I/O)2) |

DNU (Do Not Use) |

|

43 |

PETp0 |

PCIe TX |

44 |

SMB_CLK (I/O)2) |

DNU (Do Not Use) |

|

45 |

GND |

Return current path |

46 |

N/C |

N/C |

|

|

|

|

|

|

|

|

47 |

PERn0 |

PCIe Rx |

48 |

N/C |

N/C |

|

|

|

|

|

|

|

|

49 |

PERp0 |

PCIe Rx |

50 |

PERST# |

PCIe Reset |

|

|

|

|

|

|

|

|

51 |

GND |

Return current path |

52 |

CLKREQ# |

PCIe Device Clock Request |

|

|

|

|

|

|

|

|

53 |

REFCLKN |

PCIe Reference Clock |

54 |

PEWake# |

N/C |

|

|

|

|

|

|

|

|

55 |

REFCLKP |

PCIe Reference Clock |

56 |

Reserved for |

N/C |

|

MFG_Data |

||||||

|

|

|

|

|

||

|

|

|

|

|

|

|

57 |

GND |

Return current path |

58 |

Reserved for |

N/C |

|

MFG_CLOCK |

||||||

|

|

|

|

|

||

|

|

|

|

|

|

|

67 |

N/C |

N/C |

68 |

SUSCLK |

DNU (Do Not Use) |

|

|

|

|

|

|

|

|

69 |

PEDET |

N/C |

70 |

3.3V |

3.3V source |

|

|

|

|

|

|

|

|

71 |

GND |

Return current path |

72 |

3.3V |

3.3V source |

|

|

|

|

|

|

|

IF THERE IS ANY OTHER OPERATION TO IMPLEMENT IN ADDITION TO SPECIFICATION

IN THE DATASHEET OR JEDEC STANDARD, PLEASE CONTACT EACH BRANCH OFFICE OR

HEADQUARTERS OF SAMSUNG ELECTRONICS.

- 9 -

MZVLB256HAHQ-00000/07 |

|

|

|

|

SAMSUNG CONFIDENTIAL |

|||

MZVLB512HAJQ-00000/07 |

datasheet |

Rev. 1.1 |

||||||

MZVLB2T0HMLB-00000/07 |

SSD |

|||||||

MZVLB1T0HALR-00000/07 |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

73 |

GND |

Return current path |

74 |

3.3V |

3.3V source |

|||

|

|

|

|

|

|

|

|

|

75 |

GND |

Return current path |

|

|

|

|

|

|

NOTE:

1)Not support: open drain with pull-up on platform (1.8V), active low.

2)Not support: open drain with pull-up on platform (1.8V).

[Table 11] Simple Indicator Protocol for SSD LED States (Optional)

|

ASPM1) |

LED Status |

|

Active State (Host send CMD to SSD) |

Blinking |

|

|

|

Idle |

Low Power standby |

OFF |

|

|

|

State |

Deep Sleep Power savings |

OFF |

|

|

|

NOTE:

1) ASPM (Active State Power Management)

IF THERE IS ANY OTHER OPERATION TO IMPLEMENT IN ADDITION TO SPECIFICATION

IN THE DATASHEET OR JEDEC STANDARD, PLEASE CONTACT EACH BRANCH OFFICE OR

HEADQUARTERS OF SAMSUNG ELECTRONICS.

- 10 -

MZVLB256HAHQ-00000/07 |

|

SAMSUNG CONFIDENTIAL |

MZVLB512HAJQ-00000/07 |

datasheet |

Rev. 1.1 |

MZVLB1T0HALR-00000/07 |

SSD |

|

MZVLB2T0HMLB-00000/07 |

5.0PCI and NVM Express registers

5.1PCI Express Registers

5.1.1 PCI Register Summary

[Table 12] PCI Register Summary

Start Address |

End Address |

Name |

Type |

00h |

3Fh |

PCI Header |

PCI Configuration Header Space |

|

|

|

|

40h |

47h |

PCI Power Management Capability |

PCI Capability |

|

|

|

|

50h |

67h |

MSI Capability |

PCI Capability |

|

|

|

|

70h |

A3h |

PCI Express Capability |

PCI Capability |

|

|

|

|

B0h |

BBh |

MSI-X Capability |

PCI Capability |

|

|

|

|

100h |

12Bh |

Advanced Error Reporting Capability |

PCI Extended Capability |

|

|

|

|

148h |

153h |

Device Serial Number Capability |

PCI Extended Capability |

|

|

|

|

158h |

167h |

Power Budgeting Capability |

PCI Extended Capability |

|

|

|

|

168h |

17Bh |

Secondary PCI Express Capability |

PCI Extended Capability |

|

|

|

|

188h |

18Fh |

Latency Tolerance Reporting Capability |

PCI Extended Capability |

|

|

|

|

190h |

19Fh |

L1 Substates Capability |

PCI Extended Capability |

|

|

|

|

5.1.2 PCI Configuration Header Space Registers Detail

5.1.2.1 PCI Configuration Header Space Registers

[Table 13] PCI Header Space Summary

Start Address |

End Address |

Symbol |

Description |

00h |

03h |

IDTF |

Identifiers |

|

|

|

|

04h |

05h |

CMD |

Command Register |

|

|

|

|

06h |

07h |

STS |

Status Register |

|

|

|

|

08h |

08h |

REVID |

Revision ID |

|

|

|

|

09h |

0Bh |

CC |

Class Codes |

|

|

|

|

0Ch |

0Ch |

CLS |

Cache Line Size |

|

|

|

|

0Dh |

0Dh |

MLT |

Master Latency Timer |

|

|

|

|

0Eh |

0Eh |

HTYPE |

Header Type |

|

|

|

|

0Fh |

0Fh |

BIST |

Built in Self Test |

|

|

|

|

10h |

13h |

MLBAR (BAR0) |

Memory Register Base Address (lower 32-bit) |

|

|

|

|

14h |

17h |

MUBAR (BAR1) |

Memory Register Base Address (upper 32-bit) |

|

|

|

|

18h |

1Bh |

IDBAR (BAR2) |

Reserved |

|

|

|

|

1Ch |

1Fh |

BAR3 |

Reserved |

|

|

|

|

20h |

23h |

BAR4 |

Reserved |

|

|

|

|

24h |

27h |

BAR5 |

Reserved |

|

|

|

|

28h |

2Bh |

CCPTR |

CardBus CIS Pointer |

|

|

|

|

2Ch |

2Fh |

SS |

Subsystem Identifiers |

|

|

|

|

30h |

33h |

EXPROM |

Expansion ROM Base Address |

|

|

|

|

34h |

34h |

CAP |

Capabilities Pointer |

|

|

|

|

35h |

3Bh |

R |

Reserved |

|

|

|

|

3Ch |

3Dh |

INTR |

Interrupt Information |

|

|

|

|

3Eh |

3Eh |

MGNT |

Minimum Grant |

|

|

|

|

3Fh |

3Fh |

MLAT |

Maximum Latency |

|

|

|

|

IF THERE IS ANY OTHER OPERATION TO IMPLEMENT IN ADDITION TO SPECIFICATION

IN THE DATASHEET OR JEDEC STANDARD, PLEASE CONTACT EACH BRANCH OFFICE OR

HEADQUARTERS OF SAMSUNG ELECTRONICS.

- 11 -

MZVLB256HAHQ-00000/07 |

|

|

|

SAMSUNG CONFIDENTIAL |

||||

MZVLB512HAJQ-00000/07 |

datasheet |

Rev. 1.1 |

||||||

MZVLB2T0HMLB-00000/07 |

SSD |

|||||||

MZVLB1T0HALR-00000/07 |

|

|

|

|

|

|||

|

[Table 14] Identifier Register |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Bits |

|

Type |

Default Value |

|

Description |

|

|

|

31:16 |

|

RO |

A808h |

|

Device ID |

|

|

|

|

|

|

|

|

|

|

|

|

0:15 |

|

RO |

144Dh |

|

Vendor ID |

|

|

|

|

|

|

|

|

|

|

|

|

[Table 15] Command Register |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Bits |

|

Type |

Default Value |

|

Description |

|

|

|

15:11 |

|

RO |

0h |

|

Reserved |

|

|

|

|

|

|

|

|

|

|

|

|

10 |

|

RW |

0 |

|

|

Interrupt Disable |

|

|

|

|

|

|

|

|

|

|

|

9 |

|

RO |

0 |

|

|

Fast Back-to-Back Enable (N/A) |

|

|

|

|

|

|

|

|

|

|

|

8 |

|

RW |

0 |

|

|

SERR# Enable |

|

|

|

|

|

|

|

|

|

|

|

7 |

|

RO |

0 |

|

|

IDSEL Stepping/Wait Cycle Control (N/A) |

|

|

|

|

|

|

|

|

|

|

|

6 |

|

RW |

0 |

|

|

Parity Error Response Enable |

|

|

|

|

|

|

|

|

|

|

|

5 |

|

RO |

0 |

|

|

VGA Palette Snooping Enable (N/A) |

|

|

|

|

|

|

|

|

|

|

|

4 |

|

RO |

0 |

|

|

Memory Write and Invalidate Enable (N/A) |

|

|

|

|

|

|

|

|

|

|

|

3 |

|

RO |

0 |

|

|

Special Cycle Enable (N/A) |

|

|

|

|

|

|

|

|

|

|

|

2 |

|

RW |

0 |

|

|

Bus Master Enable |

|

|

|

|

|

|

|

|

|

|

|

1 |

|

RW |

0 |

|

|

Memory Space Enable |

|

|

|

|

|

|

|

|

|

|

|

0 |

|

RW |

0 |

|

|

I/O Space Enable |

|

|

|

|

|

|

|

|

|

|

|

[Table 16] Status Register |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Bits |

|

Type |

Default Value |

|

|

Description |

|

|

|

|

|

|

|

|

|

|

|

15 |

|

RW1C |

0 |

|

|

Detected Parity Error |

|

|

|

|

|

|

|

|

|

|

|

14 |

|

RW1C |

0 |

|

|

Signaled System Error |

|

|

|

|

|

|

|

|

|

|

|

13 |

|

RW1C |

0 |

|

|

Received Master Abort |

|

|

|

|

|

|

|

|

|

|

|

12 |

|

RW1C |

0 |

|

|

Received Target Abort |

|

|

|

|

|

|

|

|

|

|

|

11 |

|

RW1C |

0 |

|

|

Signaled Target Abort (N/A) |

|

|

|

|

|

|

|

|

|

|

|

10:9 |

|

RO |

0h |

|

|

DEVSEL Timing (N/A) |

|

|

|

|

|

|

|

|

|

|

|

8 |

|

RW1C |

0 |

|

|

Master Data Parity Error Detected |

|

|

|

|

|

|

|

|

|

|

|

7 |

|

RO |

0 |

|

|

Fast Back-to-Back Transaction Capable (N/A) |

|

|

|

|

|

|

|

|

|

|

|

6 |

|

RO |

0 |

|

|

Reserved |

|

|

|

|

|

|

|

|

|

|

|

5 |

|

RO |

0 |

|

|

66MHz Capable (N/A) |

|

|

|

|

|

|

|

|

|

|

|

4 |

|

RO |

1 |

|

|

Capabilities List |

|

|

|

|

|

|

|

|

|

|

|

3 |

|

RO |

0 |

|

|

Interrupt Status |

|

|

|

|

|

|

|

|

|

|

|

2:1 |

|

RO |

0h |

|

|

Reserved |

|

|

|

|

|

|

|

|

|

|

|

0 |

|

RO |

0 |

|

|

Reserved |

|

|

|

|

|

|

|

|

|

|

|

[Table 17] Revision ID Register |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Bits |

|

Type |

Default Value |

|

|

Description |

|

|

7:0 |

|

RO |

00h |

|

|

Controller Hardware Revision ID |

|

|

|

|

|

|

|

|

|

|

|

[Table 18] Class Code Register |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Bits |

|

Type |

Default Value |

|

|

Description |

|

|

23:16 |

|

RO |

1h |

|

|

Base Class Code |

|

|

|

|

|

|

|

|

|

|

|

15:8 |

|

RO |

8h |

|

|

Sub Class Code |

|

|

|

|

|

|

|

|

|

|

|

7:0 |

|

RO |

2h |

|

|

Programming Interface |

|

|

|

|

|

|

|

|

|

|

IF THERE IS ANY OTHER OPERATION TO IMPLEMENT IN ADDITION TO SPECIFICATION

IN THE DATASHEET OR JEDEC STANDARD, PLEASE CONTACT EACH BRANCH OFFICE OR

HEADQUARTERS OF SAMSUNG ELECTRONICS.

- 12 -

MZVLB256HAHQ-00000/07 |

|

|

SAMSUNG CONFIDENTIAL |

||||

MZVLB512HAJQ-00000/07 |

datasheet |

Rev. 1.1 |

|||||

MZVLB2T0HMLB-00000/07 |

SSD |

||||||

MZVLB1T0HALR-00000/07 |

|

|

|

|

|||

|

[Table 19] Cache Line Size Register |

|

|

|

|

||

|

|

|

|

|

|

|

|

|

Bits |

|

Type |

Default Value |

|

Description |

|

|

7:0 |

|

RW |

0h |

|

Cache Line Size (N/A) |

|

|

|

|

|

|

|

|

|

|

[Table 20] Master Latency Timer Register |

|

|

|

|

||

|

|

|

|

|

|

|

|

|

Bits |

|

Type |

Default Value |

|

Description |

|

|

7:0 |

|

RO |

0h |

|

Master Latency Timer (N/A) |

|

|

|

|

|

|

|

|

|

|

[Table 21] Header Type Register |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Bits |

|

Type |

Default Value |

|

Description |

|

|

|

|

|

|

|

|

|

|

7 |

|

RO |

0 |

|

Multi-Function Device (N/A) |

|

|

|

|

|

|

|

|

|

|

6:0 |

|

RO |

0h |

|

Reserved |

|

|

|

|

|

|

|

|

|

|

[Table 22] Built In Self Test Register |

|

|

|

|

||

|

|

|

|

|

|

|

|

|

Bits |

|

Type |

Default Value |

|

Description |

|

|

|

|

|

|

|

|

|

|

7:0 |

|

RO |

0h |

|

Built In Self Test (N/A) |

|

|

|

|

|

|

|

|

|

|

[Table 23] Memory Register Base Address Lower 32-bits (BAR0) Register |

|

|

||||

|

|

|

|

|

|

|

|

|

Bits |

|

Type |

Default Value |

|

Description |

|

|

|

|

|

|

|

|

|

|

31:14 |

|

RW |

0h |

|

Base Address |

|

|

|

|

|

|

|

|

|

|

13:4 |

|

RO |

0h |

|

Reserved |

|

|

|

|

|

|

|

|

|

|

3 |

|

RO |

0 |

|

Pre-Fetchable |

|

|

|

|

|

|

|

|

|

|

2:1 |

|

RO |

2h |

|

Address Type (64-bit) |

|

|

|

|

|

|

|

|

|

|

0 |

|

RO |

0 |

|

Memory Space Indicator (MEMSI) |

|

|

|

|

|

|

|

|

|

|

[Table 24] Memory Register Base Address Upper 32-bits (BAR1) |

|

|

||||

|

|

|

|

|

|

|

|

|

Bits |

|

Type |

Default Value |

|

Description |

|

|

31:0 |

|

RO |

0h |

|

Base Address |

|

|

|

|

|

|

|

|

|

|

[Table 25] Index/Data Pair Register Base Address (BAR2) Register |

|

|

||||

|

|

|

|

|

|

|

|

|

Bits |

|

Type |

Default Value |

|

Description |

|

|

31:0 |

|

RO |

0h |

|

N/A |

|

|

|

|

|

|

|

|

|

|

[Table 26] BAR3 Register |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Bits |

|

Type |

Default Value |

|

Description |

|

|

31:0 |

|

RO |

0h |

|

N/A |

|

|

|

|

|

|

|

|

|

|

[Table 27] Vendor Specific BAR4 Register |

|

|

|

|

||

|

|

|

|

|

|

|

|

|

Bits |

|

Type |

Default Value |

|

Description |

|

|

31:0 |

|

RO |

0h |

|

N/A |

|

|

|

|

|

|

|

|

|

|

[Table 28] Vendor Specific BAR5 Register |

|

|

|

|

||

|

|

|

|

|

|

|

|

|

Bits |

|

Type |

Default Value |

|

Description |

|

|

31:0 |

|

RO |

0h |

|

N/A |

|

|

|

|

|

|

|

|

|

|

[Table 29] Cardbus CIS Pointer Register |

|

|

|

|

||

|

|

|

|

|

|

|

|

|

Bits |

|

Type |

Default Value |

|

Description |

|

|

31:0 |

|

RO |

0h |

|

N/A |

|

|

|

|

|

|

|

|

|

IF THERE IS ANY OTHER OPERATION TO IMPLEMENT IN ADDITION TO SPECIFICATION

IN THE DATASHEET OR JEDEC STANDARD, PLEASE CONTACT EACH BRANCH OFFICE OR

HEADQUARTERS OF SAMSUNG ELECTRONICS.

- 13 -

MZVLB256HAHQ-00000/07 |

|

|

|

SAMSUNG CONFIDENTIAL |

||||

MZVLB512HAJQ-00000/07 |

datasheet |

Rev. 1.1 |

||||||

MZVLB2T0HMLB-00000/07 |

SSD |

|||||||

MZVLB1T0HALR-00000/07 |

|

|

|

|

|

|

||

|

[Table 30] Subsystem Identifier Register |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Bits |

Type |

Default Value |

|

Description |

|

|

|

|

31:16 |

RO |

A801h |

|

Subsystem ID |

|

|

|

|

|

|

|

|

|

|

|

|

|

15:0 |

RO |

144Dh |

|

Subsystem Vendor ID |

|

|

|

|

|

|

|

|

|

|

|

|

|

[Table 31] Expansion ROM Register |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Bits |

Type |

Default Value |

|

|

Description |

|

|

|

31:17 |

RW |

0h |

|

|

Expansion ROM Base Address |

|

|

|

|

|

|

|

|

|

||

|

16:1 |

RO |

0h |

|

|

Reserved |

|

|

|

|

|

|

|

|

|

|

|

|

0 |

RW |

0 |

|

|

Expansion ROM Enable/Disable |

|

|

|

|

|

|

|

|

|

|

|

|

[Table 32] Capabilities Pointer Register |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Bits |

Type |

Default Value |

|

|

Description |

|

|

|

7:0 |

RO |

40h |

|

|

Capability Pointer |

|

|

|

|

|

|

|

|

|

|

|

|

[Table 33] Interrupt Information Register |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Bits |

Type |

Default Value |

|

|

Description |

|

|

|

15:8 |

RO |

01h |

|

|

Interrupt Pin |

|

|

|

|

|

|

|

|

|

||

|

7:0 |

RW |

FFh |

|

|

Interrupt Line |

|

|

|

|

|

|

|

|

|

|

|

|

[Table 34] Minimum Grant Register |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Bits |

Type |

Default Value |

|

|

Description |

|

|

|

7:0 |

RO |

0h |

|

|

Minimum Grant |

|

|

|

|

|

|

|

|

|

|

|

|

[Table 35] Maximum Latency Register |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Bits |

Type |

Default Value |

|

|

Description |

|

|

|

7:0 |

RO |

0h |

|

|

Maximum Latency |

|

|

|

|

|

|

|

|

|

|

|

5.1.3 PCI Capability Registers Detail

5.1.3.1 PCI Power Management Capability

[Table 36] PCI Power Management Capability Summary

Start Address |

End Address |

Symbol |

Description |

40h |

40h |

PCIPM_ID |

PCI Power Management Capability ID |

|

|

|

|

41h |

41h |

NEXTCAP |

Next Capability Pointer |

|

|

|

|

42h |

43h |

PCIPM_CAP |

PCI Power Management Capabilities |

|

|

|

|

44h |

45h |

PCIPM_CS |

PCI Power Management Control and Status |

|

|

|

|

46h |

46h |

PCIPM_CSR_BSE |

PMCSR_BSE Bridge Extensions |

|

|

|

|

47h |

47h |

PCIEPM_DATA |

Data |

|

|

|

|

[Table 37] PCI Power Management Capability ID Register

Bits |

Type |

Default Value |

Description |

15:8 |

RO |

50h |

Next Capability |

|

|

|

|

7:0 |

RO |

1h |

Capability ID |

|

|

|

|

IF THERE IS ANY OTHER OPERATION TO IMPLEMENT IN ADDITION TO SPECIFICATION

IN THE DATASHEET OR JEDEC STANDARD, PLEASE CONTACT EACH BRANCH OFFICE OR

HEADQUARTERS OF SAMSUNG ELECTRONICS.

- 14 -

Loading...

Loading...