Motorola SN54LS323J, SN74LS323DW Datasheet

5-1

FAST AND LS TTL DATA

8-BIT SHIFT/STORAGE REGISTER

WITH 3-STATE OUTPUTS

The SN54/74LS323 is an 8-Bit Universal Shift/Storage Register with

3-state outputs. Its function is similar to the SN54/74LS299 with the exception

of Synchronous Reset. Parallel load inputs and flip-flop outputs are

multiplexed to minimize pin count. Separate inputs and outputs are provided

for flip-flops Q0 and Q7 to allow easy cascading.

Four operation modes are possible: hold (store), shift left, shift right, and

parallel load. All modes are activated on the LOW-to-HIGH transition of the

Clock.

• Common I/O for Reduced Pin Count

• Four Operation Modes: Shift Left, Shift Right, Parallel Load and Store

• Separate Continuous Inputs and Outputs from Q

0

and Q7 Allow Easy

Cascading

• Fully Synchronous Reset

• 3-State Outputs for Bus Oriented Applications

• Input Clamp Diodes Limit High-Speed Termination Effects

• ESD > 3500 Volts

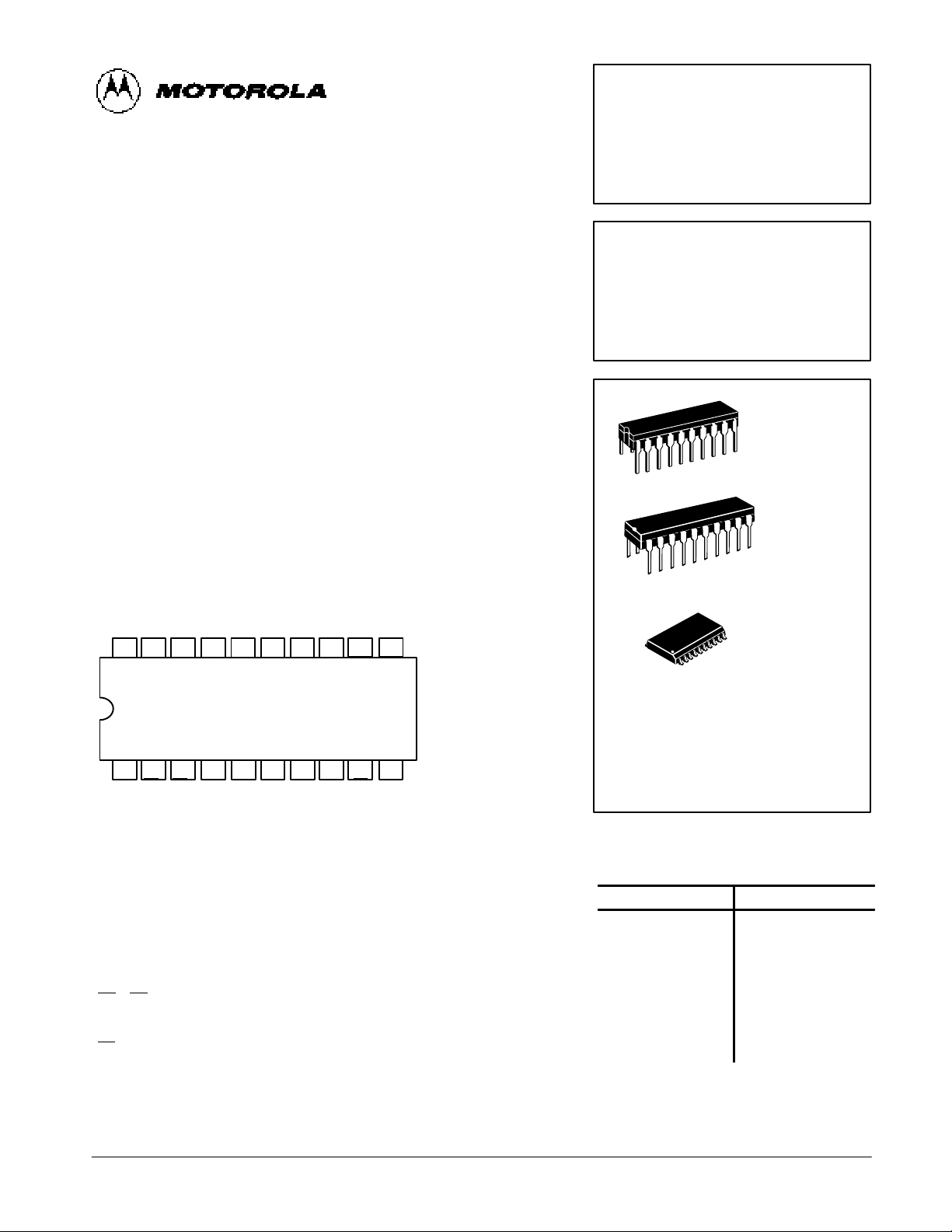

CONNECTION DIAGRAM DIP (TOP VIEW)

NOTE:

The Flatpak version

has the same pinouts

(Connection Diagram) as

the Dual In-Line Package.

18 17 16 15 14 13

1 2 3 4 5 6

7

20 19

8

V

CC

S

0

S1DS7Q7I/O

7

I/O

3

I/O

5

I/O

1

OE

1OE2

I/O6I/O4I/O2I/O0Q

0

9 10

SR GND

12 11

CP DS

0

PIN NAMES LOADING (Note a)

HIGH LOW

CP Clock Pulse (active positive going edge) Input 0.5 U.L. 0.25 U.L.

DS

0

Serial Data Input for Right Shift 0.5 U.L. 0.25 U.L.

DS

7

Serial Data Input for Left Shift 0.5 U.L. 0.25 U.L.

I/O

n

Parallel Data Input or

Parallel Output (3-State) (Note c)

1.0 U.L.

65 (25) U.L.

0.5 U.L.

15 (7.5) U.L.

OE

1

, OE

2

3-State Output Enable (active LOW) Inputs 0.5 U.L. 0.25 U.L.

Q0, Q

7

S0, S

1

Serial Outputs (Note b)

Mode Select Inputs

10 U.L.

1 U.L.

5 (2.5) U.L.

SR Synchronous Reset (active LOW) Input 0.5 U.L. 0.25 U.L.

NOTES:

a) 1 TTL LOAD = 40 µA HIGH/1.6 mA LOW.

b) The output LOW drive factor is 2.5 U.L for Military (54) and 5 U.L. for Commercial Temperature Ranges.

c) The output LOW drive factor is 7.5 U.L for Military (54) and 15 U.L. for Commercial Temperature Ranges.

The output HIGH drive factor is 25 U.L. for Military (54) and 65 U.L. for Commercial Temperature Ranges.

SN54/74LS323

8-BIT SHIFT/STORAGE REGISTER

WITH 3-STATE OUTPUTS

LOW POWER SCHOTTKY

ORDERING INFORMATION

SN54LSXXXJ Ceramic

SN74LSXXXN Plastic

SN74LSXXXDW SOIC

20

1

J SUFFIX

CERAMIC

CASE 732-03

20

1

N SUFFIX

PLASTIC

CASE 738-03

20

1

DW SUFFIX

SOIC

CASE 751D-03

5-2

FAST AND LS TTL DATA

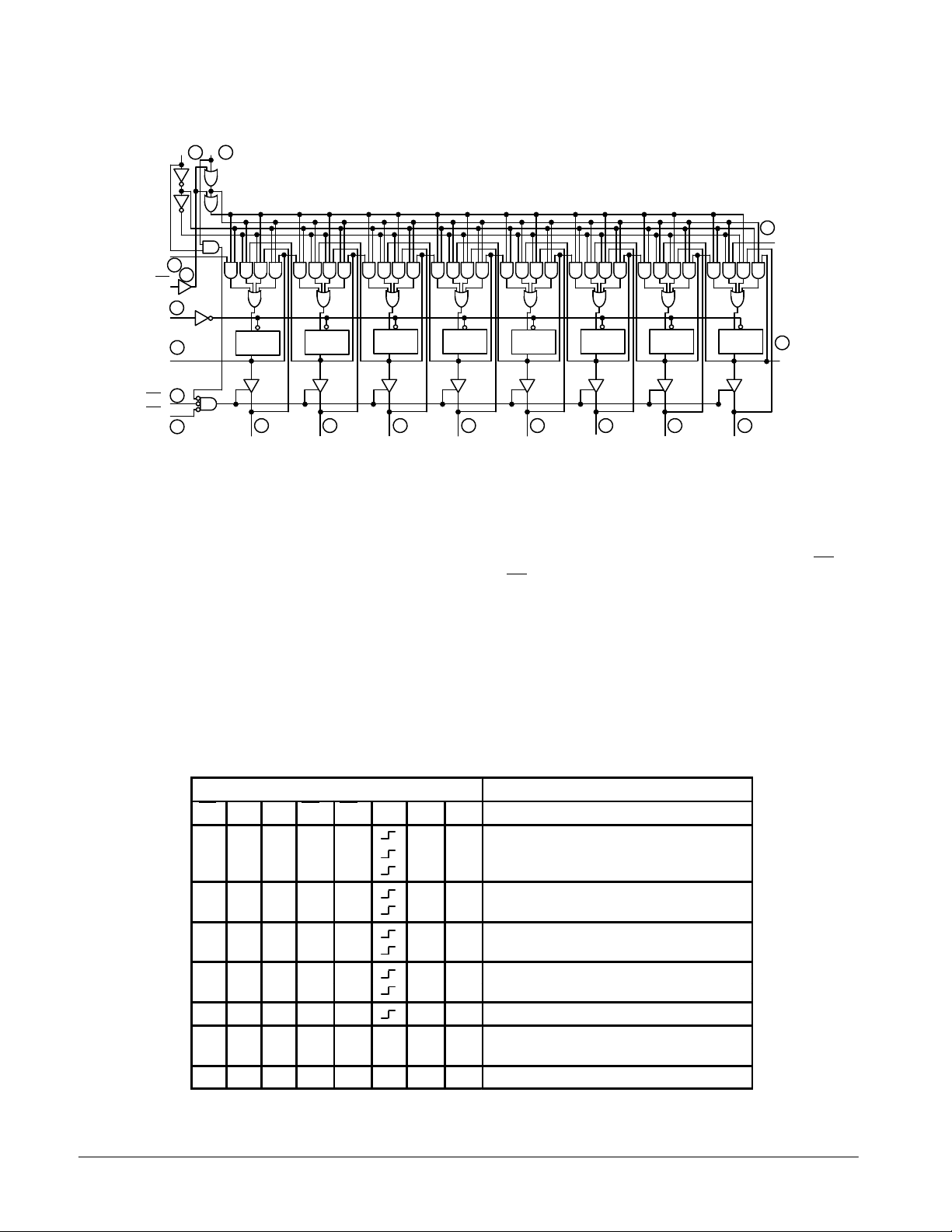

SN54/74LS323

LOGIC DIAGRAM

S1S

0

DS

0

SR

Q

0

OE

1

OE

2

D

Q

CP

I/O

0

I/O

1

I/O

2

I/O

3

I/O

4

I/O

5

I/O

6

I/O

7

DS

7

Q

7

14

1

2

67

3

8

45

9

11

12

13 15 16

17

18

19

D

Q

CP

D

Q

CP

D

Q

CP

D

Q

CP

D

Q

CP

D

Q

CP

D

Q

CP

CP

FUNCTIONAL DESCRIPTION

The logic diagram and truth table indicate the functional

characteristics of the SN54/74LS323 Universal Shift/Storage

Register. This device is similar in operation to the

SN54/74LS299 except for synchronous reset. A partial list of

the common features are described below:

1. They use eight D-type edge-triggered flip-flops that respond only to the LOW-to-HIGH transition of the Clock

(CP). The only timing restriction, therefore, is that the mode

control (S0, S1) and data inputs (DS0, DS7, I/O0–I/O7) may

be stable at least a setup time prior to the positive transition

of the Clock Pulse.

2. When S0 = S1 = 1, I/O0–I/O7 are parallel inputs to flip-flops

Q0–Q7 respectively, and the outputs of Q0–Q7 are in the

high impedance state regardless of the state of OE

1

or

OE

2

.

An important unique feature of the SN54/74LS323 is a fully

Synchronous Reset that requires only to be stable at least one

setup time prior to the positive transition of the Clock Pulse.

TRUTH TABLE

INPUTS RESPONSE

SR S1S0OE1OE2CP DS0DS

7

L X X H X X X

L X X X H X X

Synchronous Reset; Q0 = Q7 = LOW

L H H X X X X

I/O voltage undetermined

L L X L L X X Synchronous Reset; Q0 = Q7 = LOW

L X L L L X X I/O voltage LOW

H L H X X D X Shift Right; Dº Q0; Q0º Q1; etc.

H L H L L D X Shift Right; Dº Q0 & I/O0; Q0º Q1 & I/O1; etc.

H H L X X X D Shift Left; Dº Q7; Q7º Q6; etc.

H H L L L X D Shift Left; Dº Q7 & I/O7; Q7º Q6 & I/O6; etc.

H H H X X X X Parallel Load I/Onº Q

n

H L L H X X X X

H L L X H X X X

Hold; I/O Voltage Undetermined

H L L L L X X X Hold; I/On = Q

n

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

Loading...

Loading...